# Multiple Diode-Like Conduction in Resistive Switching SiO<sub>x</sub>-based MIM Devices

E. Miranda, Senior Member, IEEE, A. Mehonic, J. Blasco, J. Suñé, Fellow, IEEE, and A.J. Kenyon, Senior Member, IEEE

Abstract—Filamentary conduction in resistive switching metalinsulator-metal (MIM) devices is often modeled from the circuital viewpoint using diode-like structures with series resistances. We show in this Research Letter which arrangement of diodes and resistances is compatible with experimental multilevel set and reset I-V characteristics in electroformed TiN/SiO<sub>x</sub>/TiN structures. The proposed model is based on the solution of the generalized diode equation corresponding to N diodes arranged in parallel with a single series resistance. The model is simple yet accurate and it is able to capture the essential features exhibited by the I-V curves in the low and high bias regimes, revealing that a single equation can deal with both the low and high resistance states. An exact expression for the differential conductance suitable for small-signal analysis and circuit simulators is also provided.

Index Terms—MIM, Resistive switching, SiO<sub>x</sub>

# I. INTRODUCTION

THE observation of the resistive switching (RS) I phenomenon in a wide variety of oxide films has attracted a great deal of attention in the last years because of its implications for the field of nonvolatile memory devices [1]. The change in the resistance state of MIM structures caused by the application of pulsed or ramped voltage has been ascribed to the formation and dissolution of filamentary conductive pathways of atomic dimensions spanning the oxide layer. The physical mechanism behind this property is thought to be a redox process that involves the displacement of oxygen vacancies. Remarkably, the effect has been recently shown to occur in silicon-rich silica (SiO<sub>x</sub>) films demonstrating the feasibility of producing Si-based RRAM devices [2]. A number of conduction models have been proposed to account for the *I-V* characteristic after the initial forming of the oxide layer. These are mainly based on Poole-Frenkel, trap assisted

This work was funded in part by the project PANACHE, co-funded by grants from Spain (Project Nos. PCIN2013-076 and TEC2012-32305 of the Spanish Ministerio de Economía y Competitividad), the ENIAC Joint Undertaking and the DURSI of the Generalitat de Catalunya (2014SGR384). Project TEC2012-32305 was co-funded by the EU under the FEDER program. AJK and AM are grateful for financial support from the Engineering and Physical Sciences Research Council under grant number EPK01739X/1.

E. Miranda, J. Blasco, and J. Suñé are with the Departament d'Enginyeria Electrònica, Universitat Autònoma de Barcelona, 08193 Cerdanyola del Valles, Barcelona, Spain (e-mail: enrique.miranda@uab.cat)

A. Mehonic and A.J. Kenyon are with the Department of Electronic and Electrical Engineering, University College London, Torrington Place, London WC1E 7JE, United Kingdom (e-mail: a.kenyon@ucl.ac.uk).

tunneling, Schottky emission, space charge limited and point-contact conduction [1,3]. Other approaches rely on circuital descriptions including linear and nonlinear devices [4,5]. Interestingly, none of them explains the distinctive shapes of the *I-V* curves in the high (HRS) and low (LRS) resistance states by means of a single equation model driven by the magnitude of the current flowing through multiple leakage paths. It has been shown that the HRS *I-V* exhibits a linear dependence with the voltage at low biases and exponential or power-law at high biases [6]. On the other hand, the LRS *I-V* is mainly Ohmic, though some deviations have been reported [5,7]. In this *Letter*, we propose an equivalent electric circuit which consists of an appropriate combination of multiple diode-like conducting structures and series resistances that is able to capture all the above mentioned features.

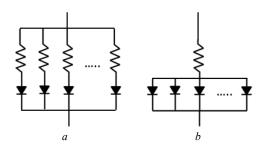

**Fig. 1.** Equivalent circuit models for the resistive switching device. a) Multiple diodes with series resistances. b) Multiple diodes with a single series resistance.

# II. EXPERIMENTAL DETAILS

The MIM structures investigated in this work were fabricated on Si substrates with a pre-processed thermal 4  $\mu m$ -thick SiO\_2 layer. The bottom electrode of the devices consisted of a uniform 100 nm-thick layer of TiN deposited by sputtering at room temperature. The SiO\_x layers (30 nm thick) were deposited by magnetron cosputtering at 250 °C using two confocal cathodes: SiO\_2 and Si under pure Ar plasma. The excess silicon content of the films was 11at%. Samples were annealed at 600 °C post deposition in an Ar atmosphere. A top layer of TiN, identical to the one used for the bottom electrode, was deposited to form the top contacts (125  $\mu m$  x 125  $\mu m$ ), which were defined using standard lift-off techniques. The devices were initially electroformed with a maximum voltage ramp to around 7-8 V and 10-3 A current

compliance. The top electrode was positively biased during the unipolar set/reset processes. More details about the electrical behaviour of the devices can be found in [2].

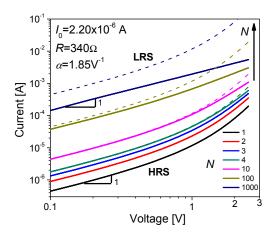

Fig. 2. Model results using eqns. (2) (dashed lines) and (4) (solid lines). HRS and LRS are the high and low resistance states, respectively. N is the number of diodes.

# III. MODEL DESCRIPTION AND DISCUSSION

Figures 1.a and 1.b show two possible arrangements of N diodes in parallel in combination with series resistances. In the case of Fig. 1.a, the corresponding equation for the current flow reads:

$$I = \sum_{i=1}^{N} I_i = \sum_{i=1}^{N} I_{0i} \{ \exp[\alpha_i (V - I_i R_i)] - 1 \}$$

(1)

where  $\alpha_i$  and  $I_{0i}$  are constants that characterize each diode and  $R_i$  is the series resistance for the branch i.  $I_i$  is the current that flows through a single diode. The solution for N identical diodes with parameters  $\alpha$ ,  $I_0$ , and R reads [8]:

$$I = \frac{N}{\alpha R} W \{ \alpha I_0 R \exp[\alpha (V + I_0 R)] \} - N I_0$$

(2)

where W is the Lambert function [9], *i.e.* the solution of the transcendental equation  $we^w = x$ . Since (2) is nothing but N times the current flowing through a single branch of the circuit, the shape of the I-V curve for a single diode-series resistance system is always preserved (see the dashed lines in Fig. 2). This is at variance with the expected behaviour for RS. However, let's consider the arrangement shown in Fig. 1.b in which a single resistance drives the current that flows through each diode. Now, the circuit equation reads:

$$I = \sum_{i=1}^{N} I_{0i} \{ \exp[\alpha_i (V - IR)] - 1 \}$$

(3)

whose solution for N identical diodes is given by the expression:

$$I = \frac{1}{\alpha R} W \{ \alpha N I_0 R \exp[\alpha (V + N I_0 R)] \} - N I_0$$

(4)

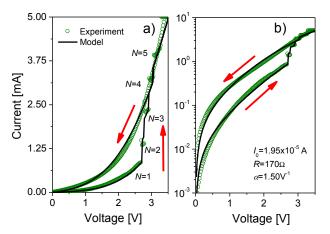

**Fig. 3.** Typical set *I-V* characteristic in a) linear-linear and b) log-linear axis. The solid line was calculated using (4). *N* is the number of diodes.

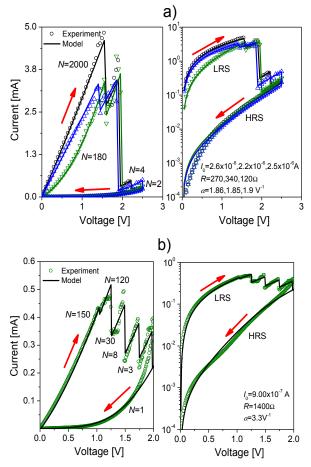

**Fig. 4.** Typical reset I-V characteristics in linear-linear and log-linear axis. The solid lines were calculated using (4). a) Several I-V curves with large N and deviation from linear behaviour. b) I-V curve with several reset jumps. N is the number of diodes.

Figure 2 shows the effect of increasing the number of diodes on the shape of the I-V curve (solid lines): as the current increases a gradual transition from the exponential to the linear regime at the highest biases occurs. This is a consequence of the increasing potential drop across R. As in Hur's model, R can be attributed to the presence of an oxygenvacancy doped region within the device [4]. The slope increase in the HRS I-V curves at the highest biases (see Fig. 2) is often attributed to space charge limited conduction [10]. Figure 3.a and 3.b show typical set *I-V* characteristic both in linear-linear and log-linear axis plots, respectively. The solid lines were obtained using (4). The curves show multiple steps associated with the formation of parallel leakage paths (up to N=5). Remarkably, the amplitude of the steps is compatible with the generation of identical diode-like structures. Notice also that, after the formation of the diode array, the I-V curve remains nonlinear. This means that for this particular example, R plays a secondary role and the exponential behaviour is preserved. Figures 4.a and 4.b show several cases corresponding to reset I-V characteristics. As can be seen from these figures. (4) is able to capture not only the exponential HRS mode after complete reset but also the Ohmic (N=2000) and non-Ohmic LRS regimes (N=180 and N=150) [6]. Notice that the use of identical diodes is of course an oversimplification of the problem since the same arguments hold for dissimilar conductive structures (mainly with different  $I_{0i}$ ). Under this circumstance, N just indicates the relative current increase with respect to the lower I-V curve modeled (N=1). This explains why large values of N are obtained in some cases, particularly for the LRS I-V characteristics in Fig. 4. Even if a single filament dominates, the change from exponential-like to Ohmic-type conduction is determined by how the applied bias drops across the different parts of the structure.

Finally, it is worth mentioning that (4) can be analytically derived so that an exact expression for the differential conductance g of the model can be obtained. Thanks to the property of the Lambert function dW/dx = W(x)/[x(W(x)+1)] [9], g can be expressed for the arrangement of N diodes in parallel with a single series resistance as:

$$g = \frac{dI}{dV} = \frac{1}{R} \left\{ 1 + \left[ \alpha R (I + NI_0) \right]^{-1} \right\}^{-1}$$

(5)

where I as a function of the applied voltage V can be calculated from (4). According to (5), as expected, when the number of diodes is very large, g reduces to  $R^{-1}$ . Having a continuous and derivable analytic expression for the differential conductance is not only essential for small-signal analysis but also for the computational algorithms implemented in circuit simulators like SPICE [11].

## IV. CONCLUSION

A simple circuital representation for the multilevel I-V characteristics in resistive switching  $SiO_x$ -based MIM devices was reported. The solution to the equivalent circuit is expressed in terms of the Lambert W function. The proposed approach gives a natural explanation for the shape of the I-V characteristics both for the low and high resistance states using a single-equation description. An analytic expression for the differential conductance was also provided.

## ACKNOWLEDGMENT

EM acknowledges the Royal Academy of Engineering, United Kingdom for a Distinguished Visiting Fellowship Award 2013.

# REFERENCES

- R. Waser, R. Dittmanm, G. Stakov., K. Szot, "Redox-based resistive switching memories - nanoionic mechanisms, prospects, and challenges," Adv. Mat. 21, 2632 (2009).

- [2] A. Mehonic, PhD Thesis, Resistive switching in Si-rich SiO<sub>2</sub>, University College London, 2014, http://discovery.ucl.ac.uk/1420436/

- [3] E. Miranda, A. Mehonic, J. Suñé, and A.J. Kenyon, "Multi-channel conduction in redox-based resistive switch modelled using quantum point contact theory," *Appl. Phys. Lett.* 103, 222904 (2013).

- [4] J. Hur, M. Lee, C. Lee, Y. Kim, C. Kim, "Modeling for bipolar resistive memory switching in transition-metal oxides," *Phys. Rev. B* 82, 155321 (2010).

- [5] J. Blasco, N. Ghenzi, J. Suñé, P. Levy, E. Miranda, "Modeling of the hysteretic I-V characteristics of TiO<sub>2</sub>-based resistive switches using the generalized diode equation," *IEEE Electron. Dev. Lett.* 35, pp. 390-392 (2014).

- [6] B. Choi, D. Jeon, S. Kim, C. Rohde, S. Choi, J. Oh, H. Kim, C.. Hwang, K. Szot, R. Waser, B. Reichenbert, S. Tiedke, "Resistive switching mechanism of TiO<sub>2</sub> thin films grown by atomic-layer deposition," *J. Appl. Phys.* 98, 033715 (2005).

- [7] A. Mehonic, A. Vrajitoarea, A., S. Cueff, S Hudziak, H. Howe, C. Labbé, R. Rizk, M. Pepper, A.J. Kenyon, "Quantum conductance in silicon oxide resistive memory devices," *Sci. Rep.* 3, 2708 (2013).

- [8] A. Ortiz-Conde, F. Garcia-Sánchez, J. Muci, "Exact analytical solutions of forward non-ideal diode equation with series and shunt parasitic resistances," *Solid-St. Electron.* 44, pp. 1861-1864 (2000).

- [9] R. Corless, G. Gonnet, D. Hare, D. Jeffrey, D. Knuth, "On the Lambert W function," Adv. Comput. Math. 5, pp. 329-359, (1996).

- [10] S. Tui, A. Baikalov, J. Cmaidalka, Y. Sun, Y. Wang, Y. Xue, X. Chu, L. Chen, A. Jacobson, "Field-induced resistive switching in metal-oxide interfaces," *Appl. Phys. Lett.* 85, 317, (2004).

- [11] W. Liu, in Mosfet Models for Spice Simulation: Including Bsim3v3 and Bsim4, Ed. John Wiley & Sons, 2001.