DOI: 10.1002/ ((please add manuscript number)) Article type: Progress Report

### Silicon Oxide (SiO<sub>x</sub>) - A Promising Material for Resistance Switching?

Adnan Mehonic<sup>1,\*</sup>, Alexander L. Shluger<sup>2</sup>, David Gao<sup>2</sup>, Ilia Valov<sup>3</sup>, Enrique Miranda<sup>4</sup>, Daniele Ielmini<sup>5</sup>, Alessandro Bricalli<sup>5</sup>, Elia Ambrosi<sup>5</sup>, Can Li<sup>6</sup>, J. Joshua Yang<sup>6</sup>, Qiangfei Xia<sup>6</sup>, and Anthony J. Kenyon<sup>1,\*</sup>

Dr. A. Mehonic, Prof. A. J. Kenyon Department of Electronic & Electrical Engineering, UCL, Torrington Place, London WC1E 7JE, UK E-mail: a.mehonic@ee.ucl.ac.uk, a.kenyon@ucl.ac.uk Prof. A. L. Shluger, Dr. D. Gao Department of Physics and Astronomy, UCL, Gower Street, London WC1E 6BT, UK Prof. I. Valov Institut für Werkstoffe der Elektrotechnik II, RWTH Aachen University, 52074 Aachen, Germany Prof. E. Miranda Departament d'Enginveria Electronica, Universitat Autonoma de Barcelona, Bellaterra, Spain Prof. D. Ielmini, E. Ambrosi, A. Bricalli Dipartimento di Elettronica e Informazione, Politecnico di Milano, Milan 20133, Italy Dr C. Li, Prof. J.J. Yang, Prof. Q. Xia Department of Electrical and Computer Engineering, University of Massachusetts, Amherst, MA, 01003, USA

Keywords: silicon oxide, ReRAM, memristor, resistance switching

### Abstract

Interest in resistance switching is currently growing apace. The promise of novel high density, low power, high speed non-volatile memory devices is appealing enough, but beyond that there are exciting future possibilities for applications in hardware acceleration for machine leaning and artificial intelligence, and neuromorphic computing. A very wide range of material systems exhibit resistance switching, a number of which – primarily transition metal oxides – are currently being investigated as CMOS-compatible technologies. Here we make the case for silicon oxide, perhaps the most CMOS-compatible dielectric, yet one that has had comparatively little attention as a resistance switching material. We present a taxonomy of switching mechanisms in silicon oxide, and summarise the current state of the art in

modelling, understanding fundamental switching mechanisms, and exciting device applications. We conclude that silicon oxide is an excellent choice for resistance switching technologies, offering a number of compelling advantages over competing material systems.

### 1. Introduction

Silicon oxide (SiO<sub>x</sub>) has long played a vital role in semiconductor microelectronics. The dominance of silicon as the universal semiconductor has been driven in no small part by its ability to form readily a stable, wide-bandgap insulating oxide (SiO<sub>2</sub>) with a near-perfect interface with Si, which enables the fabrication of field effect transistors (FETs) monolithically integrated onto silicon substrates. Silicon dioxide offers numerous technical advantages over other insulators, including a low density of interface states at the Si/SiO<sub>2</sub> interface, relatively low electron and hole trapping rates, large conduction band offset with silicon (3.1eV), and extreme compatibility with CMOS processing. While in recent years high-  $\kappa$  dielectrics such as HfO<sub>2</sub> have offered advantages in enabling devices with smaller effective oxide thicknesses (overcoming difficulties with gate oxide breakdown in ultra-thin SiO<sub>2</sub>), silicon dioxide remains at the heart of CMOS technology. Despite decades of research, we are still uncovering hidden complexities and subtleties in the physics and electronic behaviour of silicon dioxide and related sub-oxides of silicon (SiO<sub>x</sub>, x<2), including some complex structural and compositional dynamics under electrical stress that can lead to resistance switching<sup>[1]</sup>.

Resistance switching describes the phenomenon of the reversible change in resistance state of electronic materials by the application of electrical stimuli. Importantly, this change is not necessarily simply permanent dielectric breakdown, but in many cases is reversible between at least two, typically non-volatile, states. There is a wide range of different device structures and materials that exhibit resistance switching, which can be governed by various physical

processes, ranging from phase change between amorphous and crystalline states<sup>[2]</sup>, magnetoresistive effects<sup>[3,4]</sup>, nanomechanical effects<sup>[5]</sup>, pure electrical effects<sup>[6]</sup>, to ionic redox processes<sup>[7]</sup>. Such effects are commonly exploited in non-volatile Resistive Random Access Memory (RRAM) devices, and show great promise for next-generation semiconductor memory technology. Redox-based Resistive Random Access Memory (ReRAM), which we will be mostly concerned with in this review, represents a subclass of broader Resistive RAM (RRAM)<sup>[8]</sup>, in which resistance switching is governed by nanoionic redox processes and by correlation between electron and ion dynamics. In terms of applications, while resistance switching technology is principally investigated for use in memory devices<sup>[9]</sup>, ongoing studies extend its application to a variety of functions beyond pure memory: computing<sup>[10]</sup>, switches in integrated circuits<sup>[111]</sup>, random number generators<sup>[12,13]</sup>, and novel non-Von Neumann and neuromorphic architectures <sup>[14,15,16]</sup>.

A ReRAM cell consists typically of a simple metal-insulator-metal (MIM) structure, though many variations are possible (either or both electrodes could be semiconducting, or the sandwiched insulating/switching material could consist of multiple layers). The pristine state of an as-fabricated cell is typically highly insulating. However, with application of suitable voltage bias, it is possible to induce soft breakdown, where the cell exhibits much higher electrical conduction post voltage stimulus. This process, with respect to ReRAM operation, is termed electroforming. An initial electroforming step is generally, though not always, needed to enable cell operation. Following electroforming, the ReRAM cell can be switched between at least two stable (typically non-volatile) resistance states: the Low Resistance State (LRS) and the High Resistance State (HRS). Under appropriate conditions, devices can be made to cycle between resistance states many times, while each state can be stable for a long time (more than 10 years) even at an elevated temperature (e.g., 85 °C) until the next electrical stimulus is applied. This makes devices particularly attractive for non-volatile memory

applications. While electrically-driven changes in resistance can be the result of many different physical processes, broadly speaking, they can be classified into two types: filamentary resistance switching, in which the resistance of a single filament bridging the insulating layer is changed, and homogeneous switching, in which the resistance of a continuous volume of material between electrodes varies. We shall discuss the former type, which is much more common.

Most materials used for ReRAM devices lack full compatibility (or are costly) with the dominant silicon complementary metal-oxide-semiconductor (CMOS) fabrication technology. In this report, we focus on silicon oxide (SiO<sub>x</sub>, x≤2), historically one of the most studied oxide materials, as the switching material. Although one of the most widely deployed materials in modern electronics, we are still discovering its novel, remarkably rich, dynamics, which reveal many interesting electronic phenomena. While resistance changes in silicon oxide, other than destructive dielectric breakdown, have been somewhat neglected, it is in most cases a fully foundry-compatible material. Furthermore, SiO<sub>x</sub> ReRAM devices have been the subject of differences of opinion - some literature suggests that resistance switching in metal-free silicon oxide is not possible <sup>[17]</sup>. On the contrary, it is very much possible and could potentially provide many advantages over other ReRAM material systems, as we shall demonstrate below.

Studies of resistance switching in silicon oxide date back to the 1960s and 1970s<sup>[18,19,20]</sup> at which time the focus was firmly on irreversible electrical breakdown. However, there has been a resurgence in interest in reversible soft breakdown (resistance switching) in silicon oxide in recent years<sup>[21,22,23,24,25,26]</sup>. Switching can result from a number of very different processes, and it can be diverse in terms of performance and device structures.

Here we aim to provide an overview, classification, and taxonomy of different physical mechanisms of silicon oxide resistance switching in Section 2. Details of electrochemical models of resistance switching are discussed in Section 3. We discuss the existing atomistic models that describe generation of mobile ionic species and early stages of oxide breakdown as well as physical and circuit models of breakdown and resistance switching in silicon oxides in Section 4. Performance comparison of silicon oxide-based ReRAMs with hafnium oxide-based ReRAMs is given in Section 5, and compatibility with fabrication processes and system integration is discussed in Section 6.

# 2. Phenomenological Classification and Taxonomy of Resistance Switching in Silicon Oxide

As mentioned above, resistance switching in silicon oxide can result from a number of very different processes. To bring some order to the different phenomena, we can begin by classifying the switching processes broadly into those that are intrinsic properties of the pure oxide – *intrinsic* switching – and those that require the indiffusion of conductive species such as metal ions, typically from one of the metallic electrodes, or for the oxide to be directly doped with metals – *extrinsic* switching<sup>[27]</sup>. We describe extrinsic switching in SiO<sub>x</sub> in more detail in section 3, but here we will spend some time considering intrinsic switching, which is a term that describes several mechanisms. We can subdivide the classification depending on whether the switching occurs only in a non-oxidising (typically vacuum) ambient, or also in an oxygen-rich environment. The first type we shall term *air sensitive*, and the second one *air stable* resistance switching. The former typically although not exclusively, occurs in devices with an exposed oxide surface, and only occasionally in the bulk of the oxide. Regardless of the device structure, which could have exposed oxide edges<sup>[21]</sup>, internal pores<sup>[28]</sup>, or bulk oxide between electrodes<sup>[23]</sup>, air sensitive switching is only possible in vacuum or in devices that have been hermetically sealed/encapsulated to avoid oxidation of conductive filaments

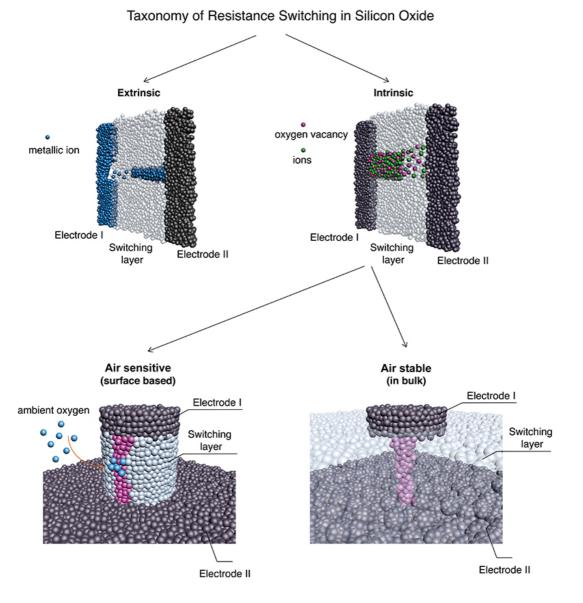

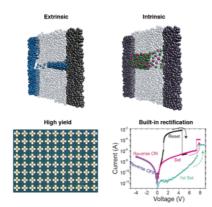

generated during the electroforming that drives the initial chemical reduction of the oxide. On the other hand, air stable switching is possible in both oxygen-rich and vacuum environments, and can be seen as "true bulk switching", occurring well away from exposed edges, and critically depends on oxide microstructure<sup>[22,29,30,31]</sup>. Clearly, the two switching mechanisms are fundamentally different, and driven by different physics. Air sensitive switching is generally thought to be governed by phase changes and crystallisation of silicon in oxygen deficient regions<sup>[32]</sup>, although different mechanisms have also been proposed<sup>[33]</sup>. It is found to be exclusively unipolar; that is to say, the transitions between resistance states always occur in the same polarity, indicating a fundamental role for current-driven Joule heating in the process. Air stable switching, on the other hand, is driven by the generation of oxygen vacancies within the bulk of the oxide, and may be bipolar, unipolar or both<sup>[29]</sup>. Crucially, there is no evidence for the formation of crystalline inclusions in the oxide during the switching mechanism. The classification of silicon oxide-based ReRAM devices is summarised in **Figure 1**.

**Figure 1.** Taxonomy of resistance switching in silicon oxide. Upper LHS: schematic of extrinsic resistance switching. Upper RHS: Schematic of intrinsic resistance switching. Lower LHS: Air sensitive resistance switching: typically, electroforming and resistance switching occurs only in devices with an exposed oxide surface and not in bulk devices. This is attributed to re-oxidation of surface-based silicon filaments by an oxidising ambient. Lower RHS: Air stable resistance switching. This type of switching occurs in ambient (oxidising) conditions and is defined by the microstructure of the oxide material. Switching voltages are typically lower compared to air sensitive switching.

Extrinsic resistance switching in silicon oxide, more commonly known as Electrochemical Metallization (ECM) or Conductive Bridge (CBRAM), is shown schematically in Figure 1 (upper left panel). This type of switching is governed by the electrodeposition of mobile metallic ions (typically Ag or Cu) from an electrochemically active electrode onto a passive (electrochemically stable) electrode and formation of conductive filaments bridging the oxide

under application of a positive electrical bias (with respect to the electrochemically active electrode); a bias of the opposite polarity (negative electrical bias) triggers the dissolution of the conductive filament by removing metal ions from the oxide. This is clearly revealed by insitu TEM analysis of planar SiO<sub>2</sub> ReRAM devices<sup>[34]</sup> where the abrupt current increase with the application of positive bias corresponds to the formation of a clearly distinguished silver conductive filament (or multiple partly formed filaments). Subsequent to this, application of a negative bias leads to the dissolution of the filament and a corresponding current drop. The conductive filament could also be non-continuous and consist of multiple metallic nanoclusters, where movement of metallic ions and clustering is governed by ion mobility and redox rates<sup>35</sup>. Extrinsic switching is exclusively bipolar, in the sense that the SET process (transition from HRS to LRS) and the RESET process (transition from LRS to HRS) always occur in opposite polarities. Further detailed discussion about ECM switching will be provided in the following sections.

Turning to intrinsic switching (**Figure 1** upper RHS) we note that air sensitive switching is only possible in non-oxidising atmospheres (**Figure 1** lower LHS). In most cases, for successful set and reset processes, devices must be operated in vacuum (<1mTorr). The device structure may be such that it accommodates filament formation on the exposed surface of silicon oxide – either the edge of a mesa structure, or the surface of planar devices<sup>[21,32]</sup>. However, it has been reported that bulk silicon oxide devices – ones with continuous silicon oxide layer – may also exhibit this behaviour<sup>[23]</sup>, though in this case there must still be some indiffusion of oxygen into the oxide film. In both cases, the resistance switching exhibits unusual unipolar switching curves; the set voltage is higher than the reset voltage, which is the opposite to the case of the majority of other unipolar metal oxide ReRAM devices. While the switching mechanism is still under debate, here we mention two prominent models. The first model assumes that the electrically driven formation of silicon-rich regions is followed

by crystallisation and formation of silicon nanocrystals, as suggested by TEM analysis<sup>[32]</sup>. Significantly, the observed silicon nanocrystals are proposed to be semi-metallic Si-III and Si-VII phases rather than the conventional Si-I semiconducting phase. The reset process is governed by thermally induced amorphisation of silicon and shrinking of nanocrystals. The second model is based around a proton exchange reaction<sup>[33]</sup>. It is suggested that, during the fabrication process (e.g. plasma-enhanced deposition), hydrogen is incorporated into SiO<sub>x</sub> to form stable (SiH)<sub>2</sub> defects. The SET process is modelled as proton release from (SiH)<sub>2</sub> to form conductive hydrogen bridge Si-H-Si defects, while the RESET process involves proton recapture to recover non-conductive (SiH)<sub>2</sub>. Both models explain the observed unipolar switching I-V curves.

Air stable switching (**Figure 1** lower RHS) is phenomenologically different, and occurs in either oxygen-rich atmospheres or vacuum, although it seems that only oxygen-rich environments lead to a full reset process<sup>[24]</sup>. Switching could be either unipolar (typical unipolar, with set voltages higher than reset voltages) or bipolar; with the possibility of both types coexisting in the same ReRAM cell. The switching is critically defined by the microstructure of the oxide material<sup>[11]</sup>, and typically exhibits much lower programming voltages (especially the electroforming voltages) than air sensitive intrinsic switching<sup>[36]</sup>. The switching mechanism is governed by breakage of silicon-oxygen bonds, followed by the creation of Frenkel pairs, consisting of oxygen vacancies and interstitial oxygen ions. Interstitial oxygen ions can easily drift in the oxide under applied field, as they experience low migration barriers of around 0.2 eV<sup>[37]</sup>. Oxygen vacancies are conductive sites that enable the formation of conductive channels or filaments<sup>[38]</sup>. The proposed atomistic mechanism of bond breakage is discussed in Section 4. Importantly, there is no evidence of crystallisation of silicon in samples that exhibit this mode of switching, but there is a clear indication of field-driven oxide segregation into silicon-rich and oxygen-rich regions <sup>[11]</sup>.

As mentioned above, microstructure plays an important role in enabling and defining the properties of resistance switching. It has been reported that thermal oxide does not easily electroform and that resistance switching is generally not observed<sup>[21]</sup>. However, in amorphous oxide films that exhibit columnar growth the defect-rich edges of internal columns can provide favourable sites for filament formation. This explains the observed low electroforming and switching voltages. Columnar growth may be promoted by increasing the roughness between bottom electrode and oxide – rougher interfaces resulting in an atomic shadowing effect and formation of columns<sup>[39]</sup>. Air stable switching is typically seen in moderately thick oxides (30-40nm), although it can be observed in even thinner, chemically produced oxides<sup>[31,40]</sup> if the microstructure is appropriate.

### 2.1. Summary of performance of intrinsic silicon oxide ReRAM devices

Intrinsic resistance switching, with no movement of metallic ions, has better compatibility with CMOS processing technologies than extrinsic switching, as there is no risk of ionic diffusion into surrounding electronics. Moreover, there has been significant progress in recent years to achieve excellent silicon oxide device performance, with metrics in many cases exceeding those reported for other metal oxide ReRAM devices. Table 1. summarises the current state of the art switching metrics, including electroforming voltage, operational voltages (both sweeping and pulsing), endurance, retention and resistance contrast ratio, for various instances of SiO<sub>x</sub> ReRAM devices. Additional functionalities, such as high-temperature retention (250°C or more)<sup>[36]</sup>, multiple stable resistance states<sup>[28]</sup>, high self-rectification<sup>[31]</sup>, in-built nonlinearity<sup>[29]</sup>, suitability for flexible and transparent electronics<sup>[41]</sup>, quantised conductance<sup>[42]</sup>, neuromorphic functionalities<sup>[33,43,44]</sup>, and optically driven switching<sup>[45]</sup> have all been reported. This table highlights the suitability of intrinsic silicon oxide for non-volatile memories. For comparison, we include two highly studied metal oxides

(TaO<sub>x</sub> and HfO<sub>x</sub>), that have shown the best switching properties. Performance metrics of other

metal oxide ReRAM devices could be found in [46].

**Table 1.** Performance comparison of intrinsic silicon oxide ReRAM devices: electroforming voltage, set voltage (both in sweep and pulsing mode), reset voltage (both in sweep and pulsing mode), endurance, retention, contrast ratio between the resistance states and classification of the switching mechanism.

| Structure                                                    | Electroforming<br>voltage (V) | Set<br>voltage<br>sweep<br>(pulse)<br>(V) | Reset<br>voltage<br>sweep<br>(pulse)<br>(V) | Endurance<br>(cycles) | Retention<br>(s) | Contrast<br>ratio        | Class         |

|--------------------------------------------------------------|-------------------------------|-------------------------------------------|---------------------------------------------|-----------------------|------------------|--------------------------|---------------|

| Edge SiOx [21]                                               | >20                           | 8(13)                                     | 3.5( 6)                                     | >10 <sup>5</sup>      | >10 <sup>5</sup> | Up to<br>10 <sup>5</sup> | air sensitive |

| Porous SiOx [28]                                             | 1.7 (breaking voltage)        | 3 (5)                                     | 8 (15)                                      | >10 <sup>5</sup>      | >10 <sup>5</sup> | Up to<br>10 <sup>7</sup> | air sensitive |

| Ta/SiOx/n-Si [47]                                            | 17                            | 6                                         | 12                                          | Up to 10 <sup>7</sup> | 10 <sup>4</sup>  | 10 <sup>6</sup>          | air sensitive |

| Au/Ti/SiOx/Zr<br>[48]                                        | -5                            | -3 (-5)                                   | 3.5 (5)                                     | >104                  | -                | Up to<br>10 <sup>4</sup> | air stable    |

| TiN/SiO₂/p-Si<br>[49]                                        | 5                             | 1.2 (4)                                   | -1.5 (-3)                                   | >10 <sup>5</sup>      | >10 <sup>4</sup> | >10 <sup>2</sup>         | air stable    |

| Mo/SiOx/Au<br>[36]                                           | -2.7                          | -1.2<br>(-1.7)                            | 1.2 (2.5)                                   | >10 <sup>7</sup>      | >10 <sup>4</sup> | Up to<br>10 <sup>4</sup> | air stable    |

| Mo/SiO <sub>x</sub> (HSQ)/Pt<br>[40]                         | -1.6                          | -0.8<br>(-1.05)                           | 1 (1.1)                                     | >10 <sup>7</sup>      | >104             | Up to<br>10 <sup>4</sup> | air stable    |

| p-Si/SiO₂/n-Si<br>[31]*                                      | 7.5                           | 7.5 (10)                                  | 4.5 (7)                                     | >100                  | >10 <sup>5</sup> | Up to<br>10 <sup>4</sup> | air stable    |

| Ta <sub>2</sub> O <sub>5-x</sub> /TaO <sub>2-x</sub><br>[50] | 2.5-3V                        | 1.1<br>(4.5)                              | 1.9 (6)                                     | >10 <sup>12</sup>     | >10 <sup>5</sup> | ~10                      | air stable    |

| HfO <sub>2</sub> [51,52,53]                                  | 3V                            | 0.8<br>(1.5)                              | 1 – 1.5<br>(1.4)                            | >10 <sup>10</sup>     | >105             | >100                     | air stable    |

\*In the case of system reported in [31], the devices are tested in crossbar arrays, thus the switching voltages include the voltage drop on the crossbar wires. The listed metrics for other systems are obtained from single devices.

### 3. Extrinsic switching: electrochemical reactions and electrochemical metallisation

### (ECM) resistance switching in SiO<sub>2</sub>

We shall now turn our attention to extrinsic resistance switching, and the electrochemical origins of the governing processes.

SiO<sub>2</sub> is one of the mostly studied electronic materials when considered from both fundamental and applications points of view. Reasons for such interest in SiO<sub>2</sub> as a resistance switching medium include its chemical robustness and CMOS compatibility, making device integration easy<sup>[54,55]</sup>. As discussed above, ReRAM cells using SiO<sub>2</sub> as a switching layer show two different types of switching mechanism, depending on the electrode material - intrinsic and extrinsic ECM/CBRAM. Intrinsic switching is observed for inert electrodes (mainly symmetric) such as Pt, TiN, doped-Si etc.<sup>[31,56]</sup>. Devices and processes based on intrinsic switching mechanisms are discussed more thoroughly elsewhere in this review. Extrinsic switching (ECM or CBRAM) requires electrochemically active electrodes such as Ag or Cu, and is based on the formation and rupture of a silver or copper metallic filament. SiO<sub>2</sub> is used either as a pure host medium<sup>[57,58,59]</sup> or is in some cases doped by thermal annealing<sup>[60,61]</sup>, with a thickness typically between 5 nm and 20 nm. The counter electrode is an inert electrode such as Pt, Ir, TiN etc. and should not be able to dissolve and electrochemically react during the switching processes. In addition, SiO<sub>2</sub> is often used as a barrier (or second layer), significantly improving the device characteristics<sup>[62,63,64]</sup>. SiO<sub>2</sub>-based ECM devices were reported to switch at very low currents and low power<sup>[65,66]</sup>, to be fast<sup>[67]</sup>, extremely stable against radiation<sup>[68]</sup> and can operate at temperatures as low as 7K<sup>[61]</sup>.

### **3.1. Electrode redox reactions**

Electrode reactions with Ag and Cu precede resistance switching in ReRAMs. SiO<sub>2</sub>, as many other oxides, is a high band gap material that can be expected to show insulating properties. However, nanoscale effects, extreme electrochemical conditions and the presence of protons blur the borders between insulators and electronic/mixed conductors, allowing macroscopically insulating oxides to transport ions/electrons and allow electrode redox

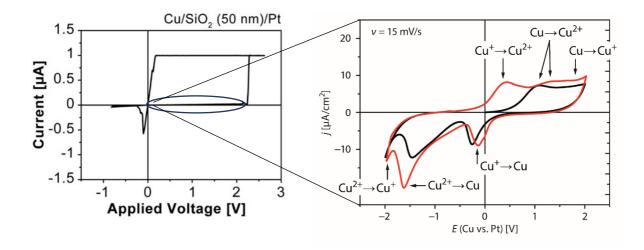

reactions<sup>[69,70]</sup>. Redox reactions preceding resistance switching were first reported for the Cu/SiO<sub>2</sub> system<sup>[57,71]</sup>. **Figure 2** shows the redox peaks of a Cu<sup>x+</sup>/Cu (x=1, 2) half-cell during cyclic voltammetry using Cu/SiO<sub>2</sub>/Pt cells.

**Figure 2.** I-V sweep for a switching cycle (left) and cyclic voltammetry (right) for the system performed in a voltage window that does not allow formation of a filament/switching. The figure is adapted from [57].

From the I-V sweep one cannot immediately conclude that there is any electrochemical reaction, because the increase of the current at positive voltages is directly related to the short circuit due to the formed metallic filament. However, increasing the instrument sensitivity and limiting the positive vertex potential we ensure conditions where the electrochemical reactions responsible for the resistance switching can be detected and characterized. Therefore, this was the first direct evidence that electrochemical reactions of the active electrode precede, and are responsible for, the subsequent process of resistance switching. Nevertheless, it is not always easy to find the proper experimental parameters to resolve the redox peaks. Several parameters should be carefully considered, such as the oxide material, the partial electronic conductivity, film thickness, voltage sweep rate, density and ambient. In some cases the sweep rate must be low e.g. <sup>[71,72,73,74]</sup>, but in others it should be very high e.g.<sup>[75]</sup>. Thus, finding the proper conditions is material-specific.

Silver and copper behave differently regarding redox reactions and transport. From a thermodynamic point of view the half-cell potentials and polarizability of both metals is different as well as their oxidation states, predetermining different numbers of exchanged electrons. For these reasons the overvoltage and also the switching voltages using Ag active electrodes are in generally lower than those for Cu electrodes<sup>[58]</sup>. The diffusion and stability of Ag and Cu ions is also different. Whereas Ag forms weaker bonds to the SiO<sub>2</sub> matrix, Cu ions form stronger bonds, resulting in higher activation energies for transport, and a correspondingly lower diffusion coefficient<sup>[76]</sup>.

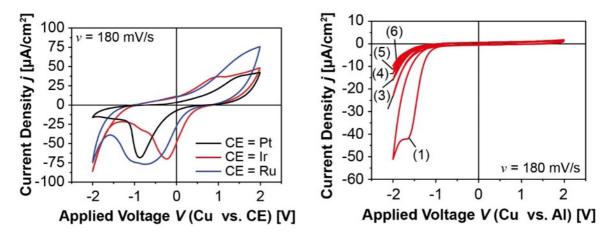

In addition, it has been recently observed that metals considered as inert, such as Pt and Pd, can behave and act as active electrodes, allowing for electrochemical reactions and even filament formation/rupture <sup>[77,78]</sup>. Moreover, ions such as Ta and Ti were also found mobile within SiO<sub>2</sub> <sup>[79,80]</sup>, showing even superior performance compared to Cu and Ag<sup>[80]</sup>. Not only is the active electrode important, but also the choice of the counter electrode is crucial<sup>[72]</sup>. The reason for this strong influence is the electrochemical nature of the process of filament formation. Formation of the filament begins at the counter electrode (negatively biased during the SET process) and its catalytic activity towards reduction reactions is extremely important. It has been found that several reactions can compete at the counter electrode, such as reactions of moisture and of the active ions<sup>[58]</sup>. Cyclic voltammograms for different counter electrode materials are presented in **Figure 3**.

**Figure 3.** Cyclic voltammograms for the Cu/SiO<sub>2</sub>/Me system. Me denotes different counter electrodes. Characteristics of noble metal electrodes (left) and Al electrode (right). The figure is adapted from <sup>[72]</sup>.

As can be seen, the noble metal electrodes show different catalytic activities; the most catalytically active appears to be Ir, followed by Ru (close to Ir) and Pt. Thus, from an electrochemical point of view devices using Ir or Ru electrodes should demonstrate better performance, at least regarding switching time. Electrodes with a high affinity to oxygen such as Al or Ta passivate easily and block further reactions. The obtained results have shown that in fact the counter electrode reaction has a lower reaction rate (compared to that of the active electrode), and therefore determines the reaction rate of the whole system. Thus, increasing the counter electrode reaction rate will lead to a higher reaction rate also of the active electrode and thus, a shorter switching time. Experiments on the switching kinetics in Cu/SiO<sub>2</sub>/Me devices using different counter electrodes have clearly confirmed these conclusions <sup>[59]</sup>.

Knowledge of the processes occurring prior to and during resistance switching were implemented in a physical based model including all possible rate limiting steps during SET and RESET such as nucleation, growth, dissolution and Joule heating<sup>[81,82,83]</sup>. The model shows that the strongest influence on the switching time is the process of phase formation (nucleation). Moreover, the type of switching and the form and direction of growth of the

metallic filament is determined by a combination of fundamental properties such as ion mobility and reaction rates<sup>[77]</sup>.

The electrochemical nature of ReRAM devices also has another implication, namely the nanobattery effect<sup>[84]</sup>. The nanobattery effect is in fact an electromotive force generated by factors such as chemical asymmetry of the electrodes (Nernst potential), inhomogeneous distribution and mobility of ions (diffusion potential), or in the case of nano-size particles/filaments also the increased surface energy effect (Gibbs-Thomson potential). The different contributions can occur individually or together, influencing the ON and OFF states and also the SET and RESET kinetics<sup>[84,85]</sup>. The nanobattery effect is often modulated by interface interactions between the electrode and SiO<sub>2</sub>. It has been found that, irrespective of the macroscopic thermodynamic predictions, oxide thin films always form at the interface between active metals and SiO<sub>2</sub> <sup>[58,86]</sup>. This oxide film, for example in the case of Cu/SiO<sub>2</sub>, provides an important source of Cu ions.

### 3.2. Influence of moisture and device performance

Both electrochemical reactions and device performance in SiO<sub>2</sub>-based memristive cells are strongly influenced by moisture. It has been found that moisture can easily penetrate into SiO<sub>2</sub>, but also can be evaporated easily in vacuum<sup>[87]</sup>. Cells and devices without any moisture within the oxide are not able to be formed at all<sup>[58]</sup>. The switching itself was also found much more reliable in the presence of moisture. The role of the moisture is twofold – firstly, it provides the necessary counter charge reaction that is essential for the proper operation of the whole cell, but it also influences the nanobattery effect, which impacts the stability of the device<sup>[58]</sup>. It has also been demonstrated that, in fact, the influence of the counter electrode material is mainly due to enhanced reaction rate, enabling higher reaction rate of the active electrode and the corresponding formation of a larger number of active ions that can

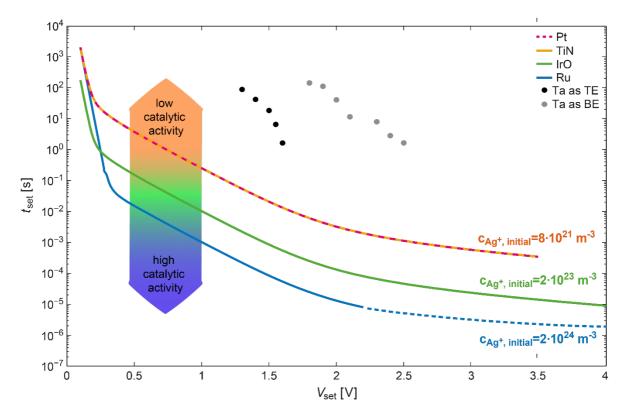

participate in the process of filament formation<sup>[59]</sup>. The moisture is absorbed within the nanoporous oxide matrix and can also serve as "dissolving agent", enhancing ion mobility. **Figure 4** shows the SET kinetics for Ag/SiO<sub>2</sub>/Me devices using different counter electrode materials.

**Figure 4.** SET kinetics for Ag/SiO<sub>2</sub>/Me devices, using various counter electrodes. The figure is reproduced from<sup>[59]</sup>.

The results demonstrate the correlation between the catalytic activity of the counter electrode, the number of generated active ions and the switching kinetic, SET time. Thus, the device kinetics and performance are inherently related to the presence of some residual moisture/protons that can be incorporated either during the preparation processes/steps or from the local environment.

ECM (extrinsic) devices based on  $SiO_2$  still suffer from large variability that hinders their commercialization. This variability is caused on one hand by the changing properties of  $SiO_2$  during cycling (enrichment with Ag/Cu ions), and on the other hand due to their

inhomogeneous distribution and variable concentration of moisture/protons being also sensitive to temperature, particular encapsulation, local structure, operating voltages/currents. Further improvements may include doping of SiO<sub>2</sub> with selected elements in order to eliminate the dependence on moisture and to stabilize the filament. In addition, different combinations of active/counter electrode materials can be tested for optimal device performance. Interface engineering is also expected to significantly modulate the kinetics, endurance and retention <sup>[88]</sup>. More recently, there has been a lot of interest in using silicon oxide ECM devices in volatile type switching for select devices in crossbar arrays<sup>[80, 89, 90]</sup>. Both Ag and Cu have been used as top electrodes, and it has been shown that by controlling current compliance it is possible to induce either non-volatile or volatile switching. In the case of Ag/SiOx devices, current compliance lower than 80  $\mu$ A produces volatile switching with very high resistance contrast ratios (more than eight orders of magnitude) and virtually infinite transition slope<sup>[80]</sup>. Furthermore, it is possible to utilise defect engineering of a graphene layer (between the SiO<sub>x</sub> and the Ag electrode) to obtain both highly desirable low operational current (~10 $\mu$ A) memory and high driving current (~1mA) selector devices<sup>[90]</sup>.

This remains a fertile field of research, and further significant improvements in extrinsic (ECM) device performance can be expected in the coming years.

#### 4. Physical and circuit models of breakdown and resistance switching in silicon oxide

We now turn from an electrochemical description of resistance switching to models that take inspiration from the underlying physics to generate circuit models that can be used to develop circuit- and system-level design rules.

### 4.1 Phenomenological models of oxide degradation and breakdown

Since the earliest observations of resistance switching in silicon oxide (SiO<sub>x</sub>), the phenomenon has been unquestionably linked to filamentary-type conduction, *i.e.* to electron transport through an oxide layer that has locally lost its insulating capability. The filament we are dealing with is often thought to consist of a chain of oxygen vacancies (VCM) or metal atoms (ECM) that allows the transit of electrons from one electrode to the opposite one in a variety of ways depending on the material bulk properties and its interfaces. The formation and dissolution of a gap region along this filament caused by the movement of atomic species determines whether the system is in the low (LRS) or high (HRS) resistance state. Depending on the lateral size of the conducting pathway, the magnitude of the current in both states can be lower or higher, which in turn determines the modelling framework.

In order to understand the evolution of the ideas concerning physical and circuital models for resistance switching in SiO<sub>x</sub>, it is important to realize that two lines of research developed almost in parallel starting some sixty years ago until recently. First, one related to the investigation of the resistance switching phenomenon itself from a pure materials science perspective and, second, a more practical and focused approach related to thin oxide reliability issues in the context of conventional electron devices such as MOS capacitors and transistors. In this latter case, the switching property of the oxide layer was not specifically pursued but instead the mechanisms leading to the filament formation (oxide breakdown) and its final consequence on the output characteristic of the devices (post-breakdown conduction mode) were extensively investigated<sup>[91, 92]</sup>. Understandably, because of the aims of microelectronics industry, the focus of research was initially placed on the driving forces behind the wear-out and breakdown phases of thermally grown SiO<sub>2</sub><sup>[93,94,95,96,97]</sup>. Later on, the interest shifted to high- $\kappa$  films and to their potential use as switching elements in non-volatile memories<sup>[98,99,100,101]</sup>. Stress conditions and degradation are connected through acceleration laws that depend on the electric field or voltage applied to the structure <sup>[102]</sup>. The use of MOS

devices for the study of the SiO<sub>2</sub> wear-out and breakdown is widely accepted. A central difference with MIM devices is the potential drop in the semiconductor substrate.

Different measurement techniques contribute to the understanding of the physics involved: constant current or voltage <sup>[103]</sup>, dynamical stress<sup>[104]</sup>, or radiation-induced degradation<sup>[105]</sup>. In the past, the SiO<sub>2</sub> degradation process was attributed to dipole flipping<sup>[106]</sup>, hole injection<sup>[107]</sup> and hydrogen release <sup>[108]</sup>. In general, electron traps, hole traps and interface states have been linked to oxide breakdown <sup>[109,110]</sup>. During degradation traps or defects are generated until a critical density is reached and a percolation path formed. This final step is identified with the breakdown of the oxide layer <sup>[111, 112, 113]</sup>. Remarkably, percolation models are able to explain the area and thickness dependence of the failure statistical distributions (Weibull plot). Percolation mechanisms have been considered for resistance switching devices as well<sup>[114]</sup>. Electron conduction in SiO<sub>2</sub> during the degradation stage has also received extensive attention. In thick oxides ( $t_{0x}$ >10 nm), Fower-Nordheim conduction is affected by charge trapping<sup>[115, 116]</sup>. In thin oxides ( $t_{0x}$ <7 nm), stress induced leakage current (SILC) is the dominant mechanism at low biases<sup>[117,118, 119]</sup>. Fowler-Nordheim tunneling as well as SILC have been used to sense the degradation level of MOS devices<sup>[120,121,122]</sup>.

On the contrary, the physics of SiO<sub>2</sub> post-breakdown conduction has been much less investigated. Many of the breakdown models proposed in the past remain to be more deeply explored in this regard, but others have survived and evolved and now form part of the battery of models available for explaining resistance switching in SiO<sub>x</sub>. Abrupt or gradual changes of the conductance occur in a damaged oxide depending on the thickness of the dielectric, the area of the device and the stress magnitude<sup>[123, 124]</sup>. The first post-breakdown studies in SiO<sub>2</sub> were carried out by Klein *et al.*<sup>[125,126,127]</sup>, who explored the transitions of the films to the "high-conduction" state. Shatzkes *et al.*<sup>[128]</sup> further investigated this issue confirming that conduction was filamentary and mainly governed by the applied voltage and not the electric

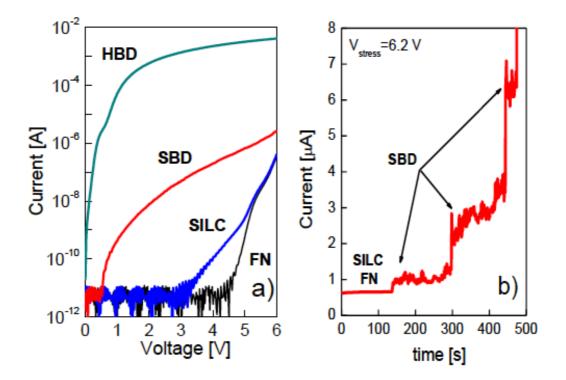

field. Oxide thickness and device area were found to play a minor role<sup>[23]</sup>. Hickmott<sup>[129]</sup>, Dearnaley et al.<sup>[130]</sup>, and Buden et al.<sup>[131]</sup> investigated filamentary conduction in materials such as SiO<sub>x</sub>, TiO<sub>x</sub>, LiF, CaF<sub>2</sub>, and Ta<sub>2</sub>O<sub>5</sub>. Reports about the reversibility of the conduction state of electroformed  $SiO_x$  started to appear in the literature<sup>[132,133]</sup>. Measurements at that time were based on thick ( $t_{ox}\approx 20-100$  nm) oxides, so important thermal damage in the devices was commonly observed. In addition, these devices only exhibited linear conduction characteristics typical of a resistor<sup>[134,135]</sup>. In the 90s, the growth of thinner oxides ( $t_{ox} \approx 5-7$ nm) allowed to explore the signature of the dielectric breakdown mechanism<sup>[136,137]</sup>. Fukuda et  $al.^{[138]}$  drawn the attention on the existence of a new failure mode in SiO<sub>2</sub> with a current several orders of magnitude lower than that observed before. This new breakdown mode was termed B-SILC<sup>[139]</sup>, quasi<sup>[140]</sup>, partial<sup>[141]</sup>, or soft breakdown<sup>[142, 143]</sup> (SBD). This is what we call today the high resistance state (HRS). The final, catastrophic, or hard breakdown (HBD) mode is referred to as the low resistance state (LRS). Figure 5a shows the occurrence of SBD and HBD failure events in a thin SiO<sub>2</sub> film (4.3 nm). Fowler-Nordheim and SILC are also included in the plot. As shown in **Figure 5b**, multiple failure events can occur in the same device. Each jump in the conduction characteristic corresponds to a new filamentary pathway spanning the dielectric film.

**Figure 5.** a) Different conduction modes observed in the *I-V* curve of a thin oxide layer ( $t_{ox}$ =4.3 nm): Fowler-Nordheim, SILC, SBD and HBD. b) Observation of successive SBD events occurring in the same device. Each jump reveals the appearance of a new breakdown path.

Most of the mechanisms considered for electron transport in dielectrics have been invoked to explain the post-breakdown conduction in SiO<sub>x</sub>. In general, they are used to account for the SBD mode exclusively. HBD is often assumed to be Ohmic-type conduction. Unfortunately, the term Ohmic is indiscriminately used to describe linear conduction (many conduction mechanisms are linear at low biases). One of the most considered approaches to describe filamentary conduction in SiO<sub>2</sub> consists in the diode equation with series resistance<sup>[136,144,145,146]</sup>. According to Umeda *et al.*<sup>[147]</sup>, the post-breakdown *I-V* curve is consistent with the current in a pn-junction diode affected by the spreading resistance effect. Multilevel conduction in SiO<sub>x</sub> can also be modelled using an array of diodes with series resistance<sup>[148]</sup> and more recently diode-like conduction was also proposed for SiO<sub>x</sub>-based RS devices<sup>[31]</sup>. Okada *et al.* showed that variable-range hopping (VRH) can be used to represent

the SBD *I-V* curve<sup>[149, 150]</sup>. In VRH, conduction is mediated by traps and interface states with different energies. In this case, the *I*-V characteristic is described by a sinh(x)-based expression<sup>[151]</sup>. More recently, Chang *et al.* have also considered hopping in combination with proton exchange reactions for SiO<sub>x</sub> RS devices<sup>[152]</sup>. Houssa *et al.* considered a nonlinear conductor network with percolation thresholds for SBD<sup>[153,154]</sup>. In this model, traps in the SiO<sub>2</sub> lattice form a conducting backbone from one electrode to the other. Electron scattering accounts for the temperature dependence<sup>[152]</sup> and Lévy flights describe the current fluctuations<sup>[155]</sup>. Lee *et al.*<sup>[140]</sup> proposed that SBD can be represented using a direct tunneling (DT) model (trapezoidal potential barrier) with degradation effects localized in the anodic region. The idea is that the impact of electrons causes a local reduction of the oxide thickness or thinning process. Yoshida et al. proposed a similar mechanism<sup>[156]</sup>. Houssa et al. found that a tunneling model of this kind requires unphysical barrier height values<sup>[154]</sup>. HBD has also been explained using thinned potential barriers<sup>[157]</sup>. Lowering of the SiO<sub>2</sub> barrier height has been proposed for SBD as well <sup>[158,159]</sup>. In this case, hole trapping would reduce the insulator band gap affecting the insulating capability of the material. Resonant (RT) and trap-assisted (TAT) tunneling are also among the candidates for SBD and HBD conduction in SiO<sub>2</sub> and SiO<sub>x</sub> <sup>[23,160, 161, 162]</sup>. Ting<sup>[163]</sup> suggested that crowding effects of the electron wave functions into nanoscale wires in the oxide layer could explain both SBD and HBD. Nigam et al.[164,165] claimed that single electron tunneling could deal with both the temperature and voltage dependencies of the SBD current. According to this model, the breakdown path can be represented by isolated islands distributed along the oxide layer. The transit of electrons from one electrode to the other would follow uncorrelated tunnel events determined by the local electrostatic potentials caused by the trapped charges. Both SBD and HBD were modeled using a quantum point-contact (QPC) approach in [166]. In this model, the breakdown path is ideally treated as an atom-sized constriction with adiabatic shape<sup>[167]</sup>. The confinement of the electron wavefunction induces the quantization of the transverse momentum giving rise to

conduction subbands acting as potential barriers for the injected electrons. Remarkably, these are not material barriers but barriers that appear as a consequence of the low dimensionality of the filamentary path, like the discrete energy levels occurring in a quantum well<sup>[168]</sup>. The difference between the right- and left-going conduction modes that arise from the relative position of the quasi-Fermi levels at the electrodes and the barrier height is reflected in the conductance of the filament. The barrier profile was obtained using inverse modeling<sup>[169]</sup>. The QPC model was initially invoked to explain the heavy ion-induced conduction<sup>[170]</sup>, the *I-V* curves in hyperthin oxides<sup>[171]</sup>, the noise figure after HBD<sup>[172]</sup>, and the effects of temperature on the leakage current<sup>[173,174,175]</sup>.

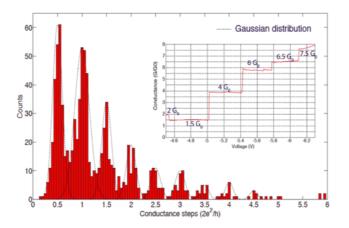

In recent years, Degraeve et al. proposed an extension of the model to account for the RS dynamics in HfO<sub>2</sub><sup>[176]</sup>. Discrete conductance steps of the order of the quantum conductance unit  $G_0=2e^2/h$  have been reported to occur in Ta<sub>2</sub>O<sub>5</sub> layers by Tsuruoka *et al.*<sup>[177]</sup> and by Chen et al.<sup>[178]</sup>. Long et al. reported similar results for the reset transitions of Pt/HfO<sub>2</sub>/Pt devices<sup>[179]</sup>. The conductance jumps were associated with atomic-size modifications of the filament cross-section. Zhu et al. showed conductance quantization in Nb/ZnO/Pt and ITO/ZnO/ITO devices<sup>[180]</sup>, Miranda et al. in CeO<sub>x</sub>/SiO<sub>2</sub>-based RS devices<sup>[181]</sup>, and Mehonic et  $al.^{[42]}$  reported similar effects in SiO<sub>x</sub> resistive switches (see Figure 6). Gao *et al.* considered quantization in Ag/SiO<sub>2</sub>/In occurring at integer and half integer values of  $G_0$  <sup>[182]</sup>. Results pointing out in the same direction were also presented by a number of authors<sup>[183,184,185,186,187,188]</sup> indicating that the idea of quantum conduction is more than a reasonable hypothesis. More conventional mechanisms such as Poole-Frenkel conduction<sup>[189,190,23,191]</sup> and Schottky emission<sup>[192]</sup> are also frequently invoked to model the high resistance state of SiO<sub>x</sub> films. Unfortunately, in the vast majority of the cases, the consistency with the temperature and bias dependence expected for these mechanisms is not demonstrated. This requires deeper understanding of the atomistic processes during resistance

switching and soft breakdown. 3D atomistic simulations of resistance switching and soft breakdown in  $SiO_x$  combining field and temperature-assisted electron and ion transport were carried out in [193]. They used atomistic models of oxide degradation processes to describe resistance switching and soft breakdown in  $SiO_x$  and provide a new insight into the mechanisms of these processes. These models are considered in more detail below.

**Figure 6.** a) Histogram of conductance changes during ~1,000 conductance steps. Clear peaks are evident at half-integer multiples of  $G_0$ , which have been fitted with a series of Gaussian distributions as a guide to the eye (dotted lines). b) Conductance-voltage curves for a device showing linear behaviour in the voltage range between -4.5V and -6.1V. Several level conductance plateaux can be seen at half-integer multiples of  $G_0$ . Reproduced with permission.<sup>[42]</sup> Copyright 2018, The Authors.

### 4.2. Atomistic models of early stages of degradation of SiO<sub>x</sub>

As discussed above, the soft breakdown and hard breakdown of complementary metal-oxidesemiconductor (CMOS) devices<sup>[194]</sup> and resistance switching in ReRAM devices<sup>[1, 21, 22, 24, 32]</sup> are often attributed to the aggregation of oxygen vacancies as a result of electrically stressing amorphous SiO<sub>x</sub> (x = 1.3-2) films. In spite of the intuitive appeal of these models, the atomistic mechanisms behind vacancy aggregation processes remain unclear. They are attributed to the creation of additional oxygen vacancies<sup>[1,32,37]</sup> near pre-existing vacancies and diffusion and attraction of vacancies<sup>[21,22]</sup>. Recent simulations<sup>[195]</sup> shed some light on the feasibility of such mechanisms. Using computational modelling, the structures and binding energies of vacancy dimers and trimers in a-SiO<sub>2</sub>, the energy barriers for individual vacancy

diffusion, as well as the effects of trapping extra electrons at vacancies on their mobility have been investigated. These calculations demonstrated the existence of favourable sites for diand tri-vacancy cluster aggregation in a-SiO<sub>2</sub> with maximum binding energies of approximately 0.13 eV and 0.18 eV, respectively. The calculated barriers for neutral O vacancy diffusion range between 3.2 eV and 5.6 eV, with the average value about 4.6 eV. This shows that effective clustering of randomly distributed neutral O vacancies via diffusion at room temperature is unfeasible. When the system's Fermi level is above 6.4 eV with respect to the top of the SiO<sub>2</sub> valence band, oxygen vacancies can trap up to two extra electrons from Si substrate or metal electrode. Average diffusion barriers for doubly charged vacancies are reduced to about 2.0 eV. However, the relatively high probability of losing the trapped electrons into the SiO<sub>2</sub> conduction band strongly reduces the efficiency of this diffusion channel.

These results suggest that clustering of oxygen vacancies in a-SiO<sub>2</sub> via thermally activated diffusion of vacancies is inefficient and that alternative mechanisms for aggregation of O vacancies under electrical bias should be considered. Here one can turn to existing models of SDB and HDB. In particular, according to the thermochemical E model the generation of defects within the dielectric is caused by weakening of the inter-atomic bonds due to the interaction with an external electric field<sup>[196,197]</sup>. The probability of breaking a Si-O bond depends exponentially on the bond strength,  $\Delta$ H<sub>0</sub>, as well as on the strength of the field, E. Increasing the latter lowers the energy barrier for bond breaking and creating a stable pair of defects in the amorphous network. The thermochemical E model predicts an exponential dependence of time to breakdown on the field strength E. Although this behavior has been observed experimentally in thin dielectric films at low stress voltages, the E-model does not explain the field polarity dependence of dielectric breakdown. The experimental results also show different breakdown times for the same field in devices of different dielectric

thicknesses<sup>[198]</sup>. Describing oxide degradation as a purely field driven process is therefore an over-simplification<sup>[199]</sup>.

More recent results suggest that the generally accepted time-dependent DB (TDDB) observations can be better explained when field-induced polar bond weakening is facilitated by current-induced processes in the dielectric<sup>[197]</sup>. However, the products of bond breaking in an oxide film are difficult to detect directly. Recent experiments combining *in situ* electrical biasing measurements with residual gas analysis using a secondary ion mass spectrometer revealed the ejection of oxygen molecules from a TiN/a-SiO<sub>x</sub>/TiN stack<sup>[1]</sup>. Furthermore, surface deformation of the top electrode correlated with oxygen ejection has been observed using atomic force microscopy (AFM) and transmission electron microscopy (TEM) measurements. The occurrence of such deformations in titanium and silicon oxides<sup>[24, 200]</sup> has been attributed to oxygen gas emission. The detection of oxygen emission during electrical stressing shows that mobile interstitial oxygen is produced in the film. However, the mechanism of oxygen generation is still poorly understood due to the luck of experimental data and atomistic modelling.

A mechanism proposed in [37] suggests that oxygen vacancy aggregation and oxygen gas generation can be facilitated by electron injection into the oxide from an electrode during electrical stress. It has been demonstrated recently that extra electrons injected into a-SiO<sub>2</sub> can be trapped at intrinsic sites in a-SiO<sub>2</sub> network and create deep states in the band gap<sup>[201]</sup>. These intrinsic trapping sites are formed by wide O-Si-O angles (>132°) in the otherwise continuous random network and can accommodate up to two electrons, accompanied by strong network distortion. The structure, optical absorption and EPR signatures of these intrinsic electron traps are described in refs. 1, 201 and 202. As a result of trapping two electrons, the energy barrier to break one of the Si-O bonds adjacent to the trap is lowered to

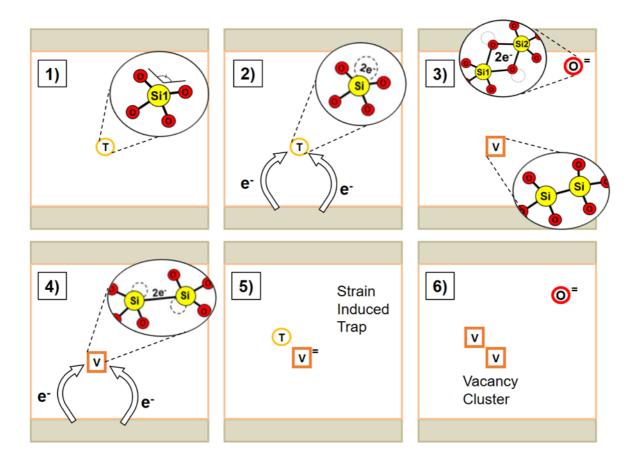

around 0.7 eV on average, with barriers in some locations being as low as 0.4 eV<sup>[37]</sup>. Electrical stress can reduce this barrier even further, leading to the formation of a pair of neutral O vacancy,  $V_0^0$ , and negatively charged interstitial  $O^{2-}$  ion. Unlike other types of defect pairs, e.g.  $V_0^{2+}$  and  $O^{2-}$  interstitial ions, neutral  $V_0^0$  and negatively charged  $O^{2-}$  ions created by this mechanism cannot recombine easily as  $V_0^0$  is occupied by two electrons. After they separate, interstitial  $O^{2-}$  ions can diffuse in a-SiO<sub>2</sub> by an efficient pivot mechanism<sup>[1]</sup> characterized by a low energy barrier of about 0.3 eV, and drift in the electric field towards a positive electrode. This mechanism is illustrated in **Figure 7 (1-3)**. It can explain the formation of both  $V_0^0$ , required to support electron current through the a-SiO<sub>2</sub> film, and mobile O ions. However, a more detailed understanding of the mechanism of O<sub>2</sub> gas release observed experimentally<sup>[1]</sup> requires further analysis of the interaction of  $O^{2-}$  ions with the top electrode and oxygen diffusion through the electrode, which is still missing.

Thus the key component of this mechanism is the electron trapping at intrinsic trapping sites in a-SiO<sub>2</sub>, which are absent in crystalline SiO<sub>2</sub>. The concentration of these sites in a-SiO<sub>2</sub> has been estimated at about  $4 \times 10^{19}$  cm<sup>-3</sup> <sup>[201]</sup>. To further relate this mechanism to HDB and electroforming processes one needs to demonstrate that it can explain the growth of leakage current and eventual catastrophic breakdown process and predict the experimentally observed voltage and temperature dependence of time to DB. Calculations <sup>[203]</sup> have demonstrated that neutral O vacancies can support electron transport via TAT through the oxide. Further simulations <sup>[204]</sup> have demonstrated that they can be responsible for TAT and leakage current in the SiO<sub>2</sub> and SiO<sub>2</sub>/HfO<sub>2</sub> gate dielectric stacks. The HDB mechanism of thin a-SiO<sub>2</sub> films based on creation of V<sub>0</sub><sup>0</sup> caused by electron injection under electrical stress and electron current through the oxide via TAT has been explored in ref. 205. This work developed a multiscale model that combines the atomistic mechanisms of O vacancy generation described above with the electron transport models through an oxide film, including direct tunneling,

defect assisted tunneling in the framework of the multi-phonon TAT model <sup>[204]</sup>, and carrier drift across either the conduction/valence bands or defect sub-bands. The TDDB distributions were simulated at different stress voltages. The basic events leading to initial oxide degradation are shown schematically in **Figure 7**.

Wide O-Si-O bond angle intrinsic electron trapping sites were randomly generated for every simulated sample with a uniform spatial distribution and described by the energy parameters within the ranges reported in refs. 37, 203 and 204. Initially, the electrons injected into the a-SiO<sub>2</sub> film are trapped at intrinsic trapping sites in the film and new defects are generated almost uniformly across the oxide volume. Due to the local perturbation of the electric field induced by their charge state, the probability of generating  $V_0^0$  is slightly higher close to the pre-existing ones. Electron transport through TAT mechanism increases as more new vacancies are generated. This, in turn, causes power dissipation and local temperature increases. The temperature increase further enhances the defect generation rate in the proximity of the higher temperature oxide regions. This process culminates in the random formation of a dominant  $V_0^0$  cluster (comprised of around 25 vacancies with a mutual distance of no more than 0.6 nm) leading to a substantial increase of the local power dissipation, and a temperature increase of 20K. Enhanced defect generation in the surroundings of the hot spot triggers a thermally driven positive feedback between current, temperature, and  $V_0^0$  generation rates that quickly leads to the creation of a breakdown spot formed at a highly oxygen deficient region. This results in the current runaway, which can be controlled only by limiting the maximum current flowing through the film, i.e., the current compliance, as is common for electroforming in ReRAM devices. The good agreement with the experimentally observed time to breakdown dependence on applied bias obtained in simulations <sup>[205]</sup> supports the atomistic mechanism of  $V_0^0$  generation described above.

A more accurate model accounting for correlation in defect creation, i.e. processes by which pre-existing vacancies affect the formation of new vacancies was suggested in [206]. This is particularly important for the reduced samples used in refs. 22 and 1. The cost of creating an oxygen vacancy depends greatly on the local environment. Not only is there a spread of formation energies owing to disorder, but pre-existing vacancies can affect both the position and the barrier for forming a new vacancy. This mechanism is shown schematically in **Figure** 7. It can explain why electroforming in strongly reduced SiO<sub>x</sub> films is much more efficient than in high quality thermal oxide films: the probability of creating new O vacancies near preexisting vacancies upon electron trapping is higher than in pristine structure.

**Figure 7**. A schematic of the electron injection facilitated defect creation mechanism in a-SiO<sub>2</sub>. (1) Naturally occurring wide O-Si-O angles can act as electron traps in the amorphous structure. (2) The intrinsic trap (T) captures two electrons from the substrate, reducing the barrier for forming Frenkel defects. (3) A neutral O vacancy (V) and a rapidly diffusing O<sup>2-</sup> ion are formed. (4) Two electrons can trap on the newly created O vacancy. (5) The strain resulting from this a new intrinsic trap. (6) Another O vacancy and interstitial O<sup>2-</sup> ion are formed, resulting in a di-vacancy. Further electron trapping results in the formation of more O vacancies nearby.

### 4.3 Circuit models of resistance switching

Besides physical models for stable filamentary conduction in SiO<sub>x</sub>, the transitions HRS $\leftrightarrow$ LRS typical of resistance switching devices have also captured the attention of the circuit modeling community. Applications for both the analog<sup>[31, 207]</sup> and digital<sup>[208,209]</sup> worlds have been presented. The use of SiO<sub>x</sub> for selector devices in crossbar-type configurations has also raised significant interest<sup>[80]</sup>. To our knowledge, there is no specific circuit model for SiO<sub>x</sub> since the existing models are general and interchangeable for a wide variety of materials. As such these models do not attempt to deal with the physics of the device at the microscopic level, but deal with the implementation of dynamical behaviors. In order to include physical considerations, the model needs to be edited and addressed to the particular features of the system under study. In what follows, we will only refer to bipolar resistance switching devices, but the discussion can be extended to unipolar devices as well.

The hysteretic loop in the *I-V* characteristic of thin oxides has been interpreted in the last years in terms of memristors or memristive systems. Leon Chua proposed in 1971 the corresponding theory. Basically, Chua's theory links charge and flux linkage through a new circuit element called memristance <sup>[210, 211]</sup>. This is a resistor with memory. The theory was extended to ReRAMs in 2011<sup>[212]</sup>. Memristive devices are two-terminal structures whose behavior is determined by two coupled equations: one for the electron transport (short response time) and one for the displacement of atomic species within the device (long response time) <sup>[213,214,215]</sup>. The first equation is often expressed as an Ohmic-type relationship between voltage and current and the second equation is generally written as an incremental relationship for an internal parameter or state variable. Strukov's <sup>[216]</sup> model for the dopant drift in TiO<sub>2</sub> layers represented a breakthrough in this field. The model has been widely explored<sup>[217,218]</sup>, but requires the introduction of additional constraints in the memory

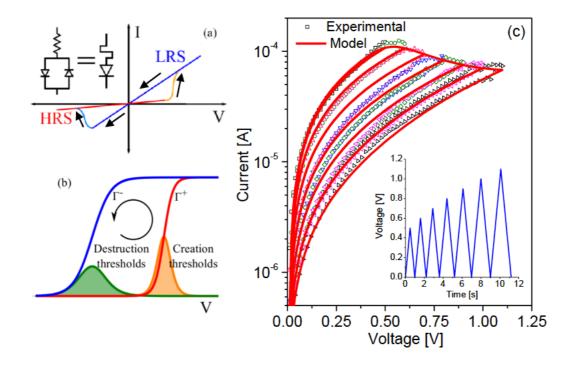

equation: the so-called window functions<sup>[213,219,220]</sup>. Concerning equivalent circuit modeling, Szot *et al.*<sup>[221]</sup> attributed the LRS-HRS transitions to a change in the transmission properties of dislocations. According to Szot's model the switching process is basically a consequence of the local modulation of the oxygen content in the material. The electrical behavior of such system is compatible with a network formed by resistors and diodes. Yang et al.<sup>[222]</sup> also considered equivalent circuit modeling. The hysteretic *I-V* characteristics are modelled using memristors and rectifying structures that define a family of reconfigurable circuit elements<sup>[223]</sup>. The device behavior is explained in terms of changes in the potential barrier heights at the metal/dielectric interfaces caused by the field-induced displacement of oxygen vacancies. Borghetti et al.<sup>[224]</sup> considered linear conduction for LRS and exponential conduction for HRS. HRS was ascribed to a tunneling mechanism and the switching to changes in the concentration of vacancies in the gap region. Pickett et al.<sup>[225]</sup> considered modifications of the tunneling barrier width. Hur et al.<sup>[226]</sup> proposed a modulation of a Schottky barrier originated in the movement of oxygen vacancies. Miranda et al.<sup>[227]</sup> have also considered diode-like conduction in combination with the hysteron structure for the memory state (see Figure 8). The memdiode model was recently written for circuit simulation environments such as LTspice<sup>[228]</sup> and is able to represent the intermediate states exhibited by many RS devices.

**Figure 8.** a) The memdiode model consists of two opposite biased diodes and a single series resistance. b)The model parameters are driven by a hysteron map that accounts for the creation and destruction of conducting channels. c) This figure shows some experimental and simulation results for the reset characteristics of SiOx using the memdiode model. Notice the control of the intermediate memory states. The inset shows the input signal. The devices were fabricated at UCL.

Interestingly, the HRS current in electroformed devices is often described using a *sinh(x)* dependence. This specific dependence with the applied voltage is consistent with the pinched current loops, with the symmetry of the *I-V* characteristics for opposite voltages, with the Ohmic-type behavior at low applied voltages, and with the exponential dependence at large applied voltages. In many cases, this choice was mainly motivated for practical reasons<sup>[221, 229]</sup>. A physics-based explanation was first given by Simmons and Verderber<sup>[230]</sup>. Guan *et al.*<sup>[231]</sup> also considered a *sinh(x)* expression for their tunneling model with variable barrier width. Finally, it is worth pointing out that the quantum point-contact (QPC) model <sup>[232]</sup> has also been used to model the resistance switching effect. The approach is consistent with a *sinh(x)* dependence too. In this case, the barrier height or width is used as the state variable of the model.

### 5. Comparison of silicon oxide ReRAMs to metal oxide ReRAMs (e.g. HfO<sub>2</sub>)

Our opening contention was that silicon oxide offers some advantages as a resistance switching material over competing, mainly transition metal oxide, systems.

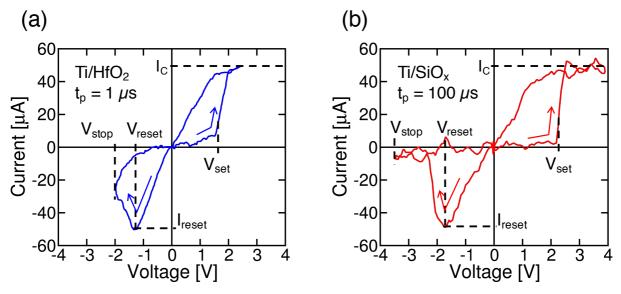

Given the large band gap and high resistivity of SiO<sub>2</sub>, ReRAM devices based on this material usually benefit from a relatively high resistance of the high resistance state (HRS), and a relatively large resistance window, compared to other metal oxide ReRAM technologies (see Table 1). In this section, we will compare SiO<sub>2</sub>-based ReRAM devices and HfO<sub>2</sub>-based ReRAM devices in more detail, because these two material systems have the most complete comparitive data. In the HfO<sub>2</sub> ReRAM device, the Si-doped HfO<sub>2</sub> dielectric layer was deposited in an amorphous phase on top of a TiN bottom electrode. The bottom electrode size was 40 nm, and the HfO<sub>2</sub> thickness was 10 nm<sup>[233]</sup>. In the SiO<sub>x</sub> ReRAM device, the 3-nm thick SiO<sub>x</sub> layer was deposited by e-beam evaporation on a C-based bottom electrode of 70 nm size. In both cases, Ti electrode are used. We make a comparison between devices without discussing the switching mechanism in detail, but rather as viable technologies. However, we note that the two types of device have very similar structures. Although, in most cases, only Ag and Cu electrodes are considered as electrochemically diffusive, we cannot dismiss the diffusion of Ti in this case, as even platinum group metals have been reported to diffuse in sputtered SiO<sub>x</sub><sup>[234]</sup>. Figure 9 shows the measured I-V curves of ReRAM devices based on HfO<sub>2</sub> (a) and SiO<sub>x</sub> (b), with x around  $1^{[235,236]}$ . The I-V curves were collected by the application of triangular pulses of positive and negative voltage, while the current was measured by an oscilloscope. The pulse width was  $t_P = 1 \mu s$  and 100  $\mu s$  for HfO<sub>2</sub> (a) and SiO<sub>x</sub> (b), respectively. In both cases, an integrated field effect transistor (FET) was connected to the ReRAM device to limit the maximum current during the set transition, i.e., the compliance current  $I_C = 50 \mu A$ . In both cases, devices were measured after an initial forming operation,

consisting of a positive voltage sweep leading to soft breakdown of the dielectric layer, where the current was limited to the same  $I_C$  as in the figure.

**Figure 9.** Current-voltage characteristics of the  $HfO_2$  and  $SiO_x$  ReRAM devices described in the text. (a) Measured I-V curves of the  $HfO_2$  ReRAM [235] and (b) the  $SiO_x$  ReRAM [236]. The two devices show similar set and reset transitions with bipolar switching operation and LRS resistance controlled by the compliance current  $I_C = 50 \ \mu$ A. However, the  $SiO_x$  ReRAM shows a larger resistance window due to the higher resistance of the HRS. Reprinted with permission from [235] and [236]. Copyright IEEE (2014) and (2018).

Both devices show comparable bipolar switching operation, with the exception of the relatively larger resistance of the HRS for SiO<sub>x</sub>, and a correspondingly higher set voltage V<sub>set</sub>, which is slightly higher than 2 V for SiO<sub>x</sub> and slightly lower than 2 V for HfO<sub>2</sub>. Detailed DC measurements on the same devices confirm that the resistance window is about 1 order of magnitude for HfO<sub>2</sub><sup>[237]</sup>, compared to about 4 orders of magnitude for SiO<sub>x</sub><sup>[236]</sup>. Such a significant change of the resistance window can be attributed to the larger band gap of the SiO<sub>x</sub> dielectric layer and the corresponding high resistivity. On the other hand, the HRS in HfO<sub>2</sub> is severely affected by the first forming operation, where the generation of defects, such as oxygen vacancies, causes the presence of a low-resistivity conductive path across the HfO<sub>2</sub> layer even in the HRS. Negligible degradation seems to take place in the SiO<sub>2</sub> layer, possibly due to the higher temperature stability and stronger bonding between silicon and oxygen in SiO<sub>x</sub>. ReRAMs based on other metal oxides, such as TiO<sub>x</sub><sup>[238]</sup> and TaO<sub>x</sub><sup>[239]</sup>, behave similarly

to  $HfO_x$  in this respect, thus evidencing the inherent advantages of  $SiO_x$ -based ReRAM with respect to metal oxide technology.

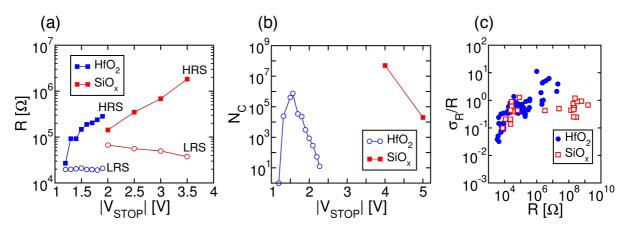

**Figure 10.** Programming and reliability characteristics of  $HfO_2$  and  $SiO_x$  ReRAM devices. a) Measured resistance for the LRS and HRS, b) cycling endurance and c) relative standard deviation  $\sigma_R/R$  for  $HfO_2$  and  $SiO_x$  ReRAM devices.  $SiO_x$  ReRAM shows higher resistance window, higher endurance, and lower resistance variability compared to  $HfO_2$  ReRAM. Reprinted with permission from [236]. Copyright IEEE (2018).

**Figure 10a** shows the average resistance for the low resistance state (LRS) and the high resistance state (HRS) for HfO<sub>2</sub> ReRAM<sup>[235]</sup> and SiO<sub>x</sub> ReRAM<sup>[236]</sup>. Both LRS and HRS were measured under triangular pulse conditions with pulse widths  $t_P = 1 \mu s$  for HfO<sub>2</sub> ReRAM and  $t_P = 100 \mu s$  for SiO<sub>x</sub> ReRAM. A compliance current  $I_C = 50 \mu A$  was used for the set transition. Data in the figure are shown as a function of V<sub>stop</sub>, namely the maximum negative voltage in the reset pulse. Increasing V<sub>stop</sub> results in a deeper HRS thanks to the gradual reset transition (see e.g., **Figure 9a**), which reflects the increasing depleted width at increasing V<sub>stop</sub><sup>[240]</sup>. As a result, the average value of HRS increases with V<sub>stop</sub>, thus broadening the resistance window between LRS and HRS. For SiO<sub>x</sub> ReRAM, V<sub>stop</sub> also affects LRS, which decreases at increasing V<sub>stop</sub> due to the higher average field across the depleted band gap<sup>[236]</sup>. From data in **Figure 10a**, it appears that SiO<sub>x</sub> ReRAM displays a higher resistance window, which reaches about a factor 50 for the maximum V<sub>stop</sub> considered in the figure, compared to a factor of 15 for the HfO<sub>2</sub> ReRAM in **Figure 10a**.

It should be noted that the value of V<sub>stop</sub> is larger for SiO<sub>2</sub> than HfO<sub>2</sub>, which might be due to the higher energy barrier for defect migration in SiO<sub>2</sub>, which thus requires higher Joule heating and a higher electric field to induce a similar migration rate in the two materials. However, it was shown that V<sub>stop</sub> drives the ReRAM reliability degradation, resulting in window reduction and dielectric breakdown<sup>[241]</sup>. To study the cycling reliability of the two ReRAM technologies, Figure 10b shows the endurance, namely the number of cycles to final failure, as a function of V<sub>stop</sub> for HfO<sub>2</sub> and SiO<sub>x</sub> ReRAM devices. As a general trend, the endurance decreases for increasing  $V_{stop}$ , due to the increasing voltage stress affecting the bottom electrode interface<sup>[241,242]</sup>. The failure event for HfO<sub>2</sub> ReRAM was evaluated as the set process under negative voltage, where the reset process was expected instead<sup>[242]</sup>. For SiO<sub>x</sub> ReRAM, on the other hand, endurance failure was assumed to correspond to window closure below a factor of 2 between the LRS and HRS, the latter resistance decreasing at increasing cycles as a result of the increasing degradation of the  $SiO_x$  layer<sup>[236]</sup>. Data in Figure 10b shows that endurance is higher for SiO<sub>x</sub> ReRAM, despite the larger V<sub>stop</sub> in the reset sweep. The larger immunity to stress and the greater endurance can be attributed to the strong covalent bond in SiO<sub>2</sub> and to the inert nature of the graphitic carbon used as bottom electrode in the silicon oxide ReRAM<sup>[236]</sup> described here. In fact, the negative set that indicates endurance failure is generally due to a breakdown of the bottom electrode interface, resulting in an injection of electrode atoms from the bottom electrode. Therefore, to prevent negative set and improve the cycling endurance in ReRAM technology, it is recommended to adopt inert bottom electrode materials such as carbon<sup>[236]</sup>, Pt<sup>[243]</sup> and Ru<sup>[244]</sup>.

The higher immunity to voltage stress is also reflected by a greater stability of the SiO<sub>2</sub> ReRAM devices against high temperature annealing. In general, ReRAM devices suffer from resistance changes in both LRS and HRS due to temperature-induced rediffusion of defects, causing disruption of the conductive filament in the LRS, or closure of the depleted gap in the HRS, both resulting in a variation of the resistance<sup>[245]</sup>. Size dependent retention effects were

demonstrated in unipolar switching NiO ReRAM devices<sup>[246]</sup> and bipolar switching GdO<sub>x</sub> devices<sup>[247]</sup>. Here, LRS shows decreasing retention time for increasing resistance, as a result of the thinner conductive filament and the consequently weaker stability against atomic diffusion. From this respect, SiO<sub>2</sub> ReRAM shows relatively good stability at elevated temperature, e.g., LRS programmed at various resistance between 10 k $\Omega$  and 100 k $\Omega$  showed negligible resistance variation up to 260°C for 1 hour, suggesting no significant sizedependent resistance loss<sup>[236]</sup>. On the other hand, the LRS resistance was shown to increase by about a factor of 5 after 1 hour at 250°C in HfO<sub>2</sub> ReRAM<sup>[245]</sup>. Also, random variations of resistance can affect HfO<sub>2</sub> ReRAM even at room temperature<sup>[248]</sup>, resulting in distribution broadening and consequent retention loss<sup>[249]</sup>.

Another strong requirement for memory reliability is the switching uniformity against deviceto-device and cycle-to-cycle variations, which are known to affect ReRAM and constitute a serious challenge in the development of large size arrays<sup>[250]</sup>. Cycle-to-cycle variability is generally assessed by the standard deviation of resistance,  $\sigma_R$ , divided by the average value of resistance R, namely  $\sigma_R/R^{[237]}$ , which is shown in **Figure 10c** as a function of R for SiO<sub>x</sub> ReRAM and HfO<sub>2</sub> ReRAM for both LRS and HRS<sup>[236]</sup>. Different LRS and HRS states were obtained by changing the programming conditions, e.g., I<sub>C</sub> during set process or V<sub>stop</sub> during the reset process. Data show that resistance variations are comparable for the two ReRAM technologies in LRS, indicating that Ti migration might be responsible for resistance switching in both cases. The variability is controlled by the shape variation of the CF<sup>[251]</sup>. On the other hand, HRS variation is much lower in SiO<sub>2</sub> ReRAM compared to HfO<sub>2</sub> ReRAM. The lower variability, combined with the higher resistance window of SiO<sub>2</sub> and the better immunity to temperature and voltage stress, makes SiO<sub>2</sub> a promising material for ReRAM compared to conventional ReRAM technologies based on metal oxides.

38

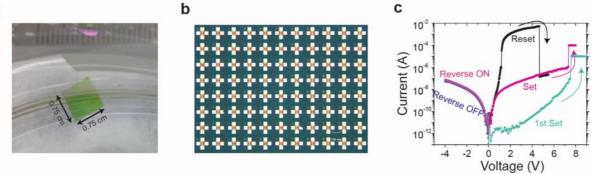

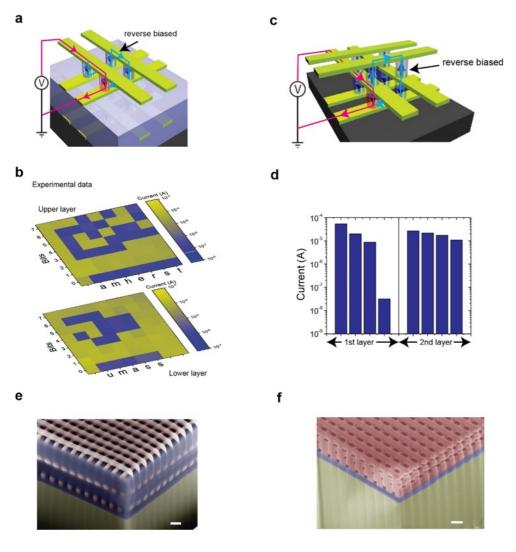

#### 6. Fabrication, system integration and CMOS compatibility