Università di Modena e Reggio Emilia Facoltà di Ingegneria - Sede di Modena Corso di Laurea in Ingegneria Elettronica

## Design of two digital radiation tolerant Integrated Circuits for High Energy Physics experiments data readout.

Titolo italiano:

## Progetto di due circuiti integrati digitali resistenti a radiazione per la lettura di dati da esperimenti di fisica delle alte energie.

Relatore: Prof. Ing. Giovanni Verzellesi Tesi di: Sandro Bonacini

Correlatori: Dr. Alessandro Marchioro Dr. Kostas Kloukinas

Controrelatore: Prof. Ing. Fausto Fantini

Anno Accademico 2001/2002

ii

A mio padre

iv

# Contents

| $\mathbf{A}$                 | bstra | nct                                                                       | ix             |  |  |  |

|------------------------------|-------|---------------------------------------------------------------------------|----------------|--|--|--|

| Riassunto in lingua italiana |       |                                                                           |                |  |  |  |

|                              | I. Da | all'esperimento CMS al preshower                                          | 2              |  |  |  |

|                              | II. I | Dispositivi a semiconduttore e circuiti integrati resistenti a ra-        |                |  |  |  |

|                              |       | diazione                                                                  | 2              |  |  |  |

|                              | III.  | Il Kchip                                                                  | 4              |  |  |  |

|                              | IV. I | Una RAM statica in tecnologia $0.13~{\rm micron}$ resistente a radiazione | 5              |  |  |  |

| 1                            | Intr  | roduction                                                                 | 7              |  |  |  |

|                              | 1.1   | CERN and High Energy Physics                                              | $\overline{7}$ |  |  |  |

|                              |       | 1.1.1 Accelerators and detectors                                          | $\overline{7}$ |  |  |  |

|                              |       | 1.1.2 The Large Hadron Collider                                           | 8              |  |  |  |

|                              | 1.2   | The Compact Muon Solenoid experiment                                      | 9              |  |  |  |

|                              |       | 1.2.1 The Trigger and Data Acquisition System                             | 12             |  |  |  |

|                              |       |                                                                           | 13             |  |  |  |

|                              |       | 1.2.3 The preshower                                                       | 14             |  |  |  |

|                              | 1.3   | Notation                                                                  | 15             |  |  |  |

|                              |       |                                                                           |                |  |  |  |

| <b>2</b>                     |       | liation tolerant semiconductor devices and integrated cir-                |                |  |  |  |

|                              | cuit  |                                                                           | 17             |  |  |  |

|                              | 2.1   |                                                                           | 17             |  |  |  |

|                              |       |                                                                           | 17             |  |  |  |

|                              |       | 1                                                                         | 18             |  |  |  |

|                              |       | 2.1.3 Radiation tolerant ICs                                              | 20             |  |  |  |

|                              | 2.2   | Radiation effects                                                         | 21             |  |  |  |

|                              |       | 2.2.1 Radiation effects on matter                                         | 21             |  |  |  |

|                              |       | 2.2.2 Radiation effects on electrical parameters of MOS tran-             | 00             |  |  |  |

|                              |       |                                                                           | 22             |  |  |  |

|                              | 0.0   | 8                                                                         | 26             |  |  |  |

|                              | 2.3   | 0 0                                                                       | 27             |  |  |  |

|                              |       | J 1                                                                       | 28             |  |  |  |

|                              |       | 2.3.2 Circuit and system techniques                                       | 29             |  |  |  |

|   | 2.4         | A radi  | ation tolerant digital standard cells library $\ldots \ldots 33$ |

|---|-------------|---------|------------------------------------------------------------------|

|   |             | 2.4.1   | The CMOS $0.25\mu m$ library $\ldots \ldots \ldots 33$           |

| 3 | The         | Kchip   | 35                                                               |

|   | 3.1         | The C   | MS preshower front-end system                                    |

|   |             | 3.1.1   | The control logic                                                |

|   |             | 3.1.2   | Fast timing control signals                                      |

|   |             | 3.1.3   | The silicon detector                                             |

|   |             | 3.1.4   | The PACE chipset                                                 |

|   |             | 3.1.5   | The AD41240 ADC                                                  |

|   |             | 3.1.6   | The Gigabit Optical Link chip 42                                 |

|   |             | 3.1.7   | The $I^2C$ interface                                             |

|   | 3.2         | The K   | chip                                                             |

|   |             | 3.2.1   | Functionalities                                                  |

|   |             | 3.2.2   | Design tools and techniques                                      |

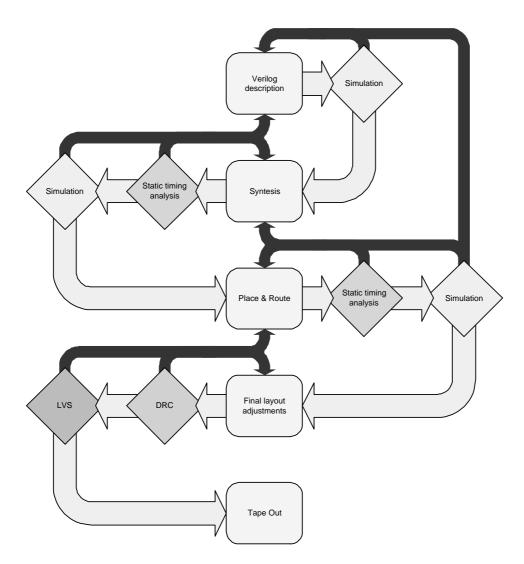

|   |             | 3.2.3   | Design flow                                                      |

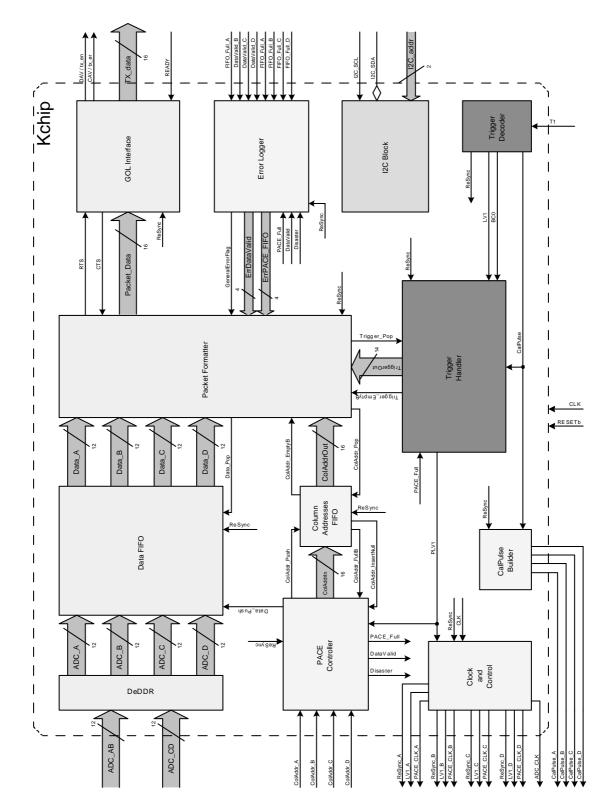

|   |             | 3.2.4   | Top-level block diagram                                          |

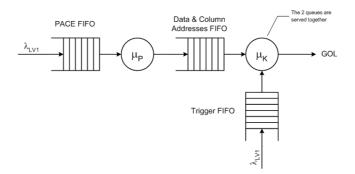

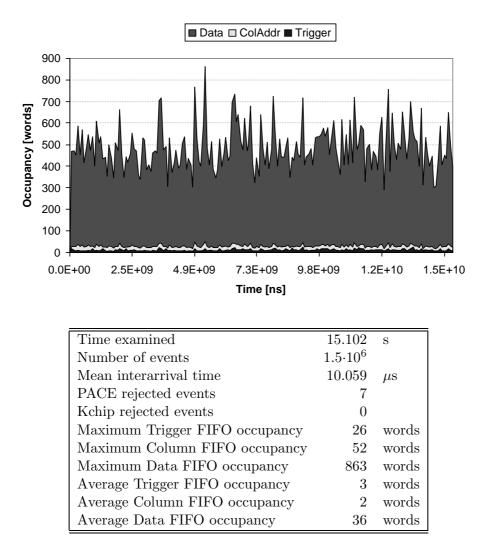

|   |             | 3.2.5   | Buffers size                                                     |

|   |             | 3.2.6   | The Clock and Control block and synchronization goals 54         |

|   |             | 3.2.7   | The Trigger Decoder                                              |

|   |             | 3.2.8   | The Trigger Handler                                              |

|   |             | 3.2.9   | The PACE Controller                                              |

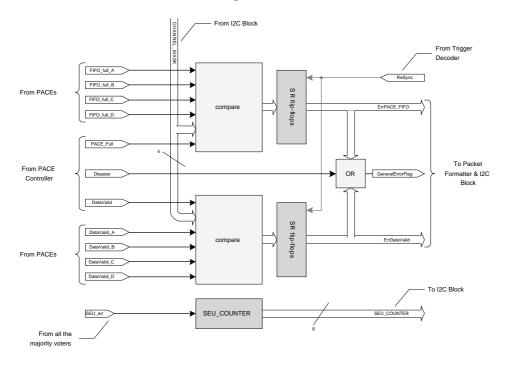

|   |             | 3.2.10  | The Error Logger                                                 |

|   |             | 3.2.11  | The DeDDR                                                        |

|   |             | 3.2.12  | The Data FIFO                                                    |

|   |             | 3.2.13  | The Column Addresses FIFO                                        |

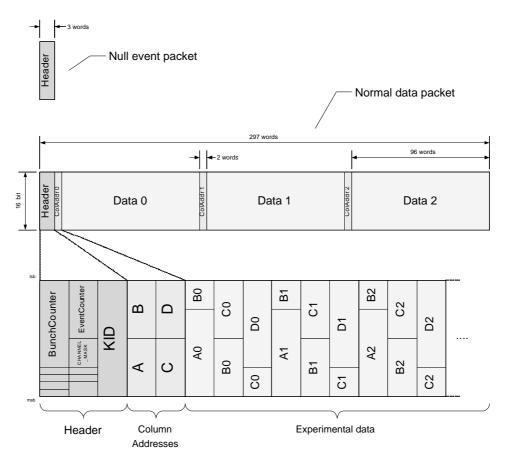

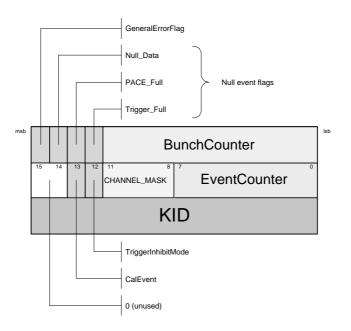

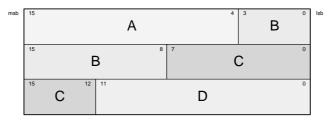

|   |             | 3.2.14  | The Packet Formatter                                             |

|   |             | 3.2.15  | The GOL Interface         73                                     |

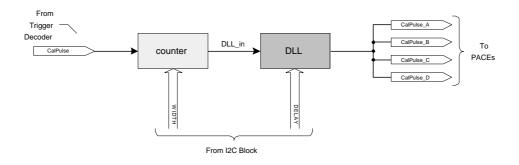

|   |             | 3.2.16  | The CalPulse Builder                                             |

|   |             | 3.2.17  | The I2C Block                                                    |

|   |             | 3.2.18  |                                                                  |

|   |             | 3.2.19  | Synthesis                                                        |

|   |             |         | Input/output pads                                                |

|   |             |         | Floorplanning                                                    |

|   |             |         | Place & Route         86                                         |

|   | 3.3         |         | chip prototype                                                   |

| 4 | Δrs         | adiatio | n tolerant CMOS 0.13 micron Static RAM 89                        |

| Ŧ | <b>A</b> 10 |         | ecture                                                           |

|   | 4.2         |         | emory cell                                                       |

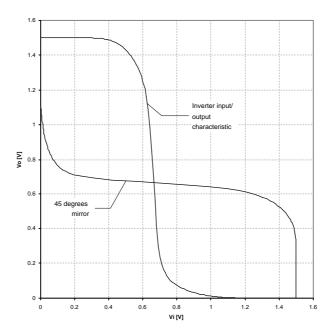

|   | -1.4        | 4.2.1   | Sizing the cell                                                  |

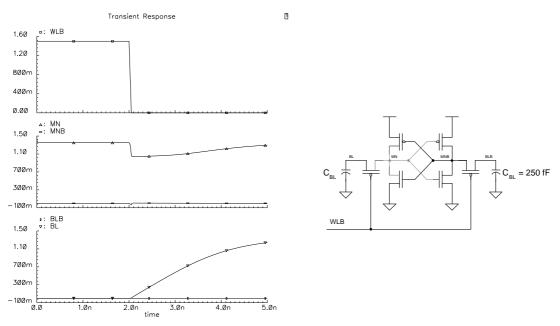

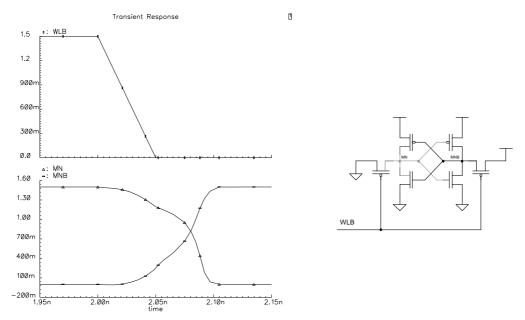

|   |             | 4.2.2   | SPICE simulations                                                |

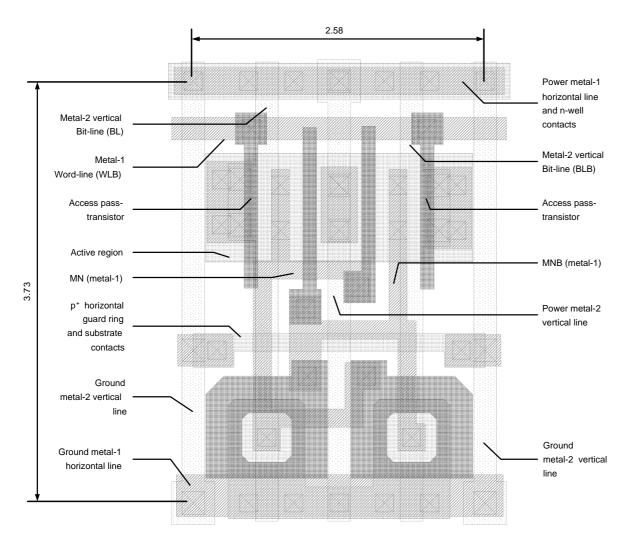

|   |             | 4.2.2   | Cell layout                                                      |

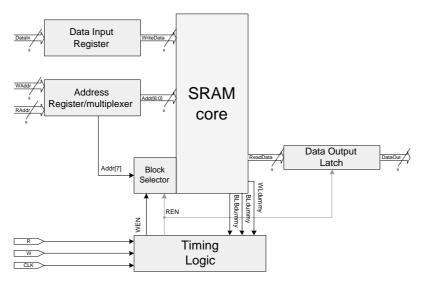

|   | 4.3         |         | RAM core                                                         |

|   | т.0         | THE J   | Will core                                                        |

vi

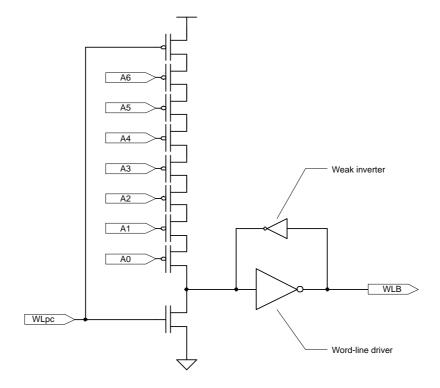

|              |                                          | 4.3.1       The Word-line Decoder  | 97  |

|--------------|------------------------------------------|------------------------------------|-----|

|              |                                          | 4.3.3 The Read Logic               | 99  |

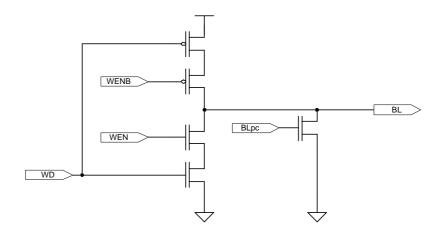

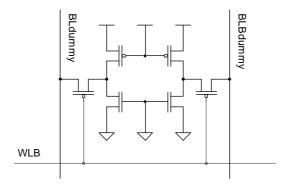

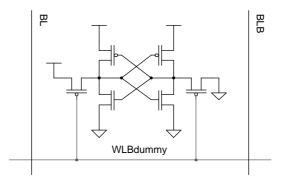

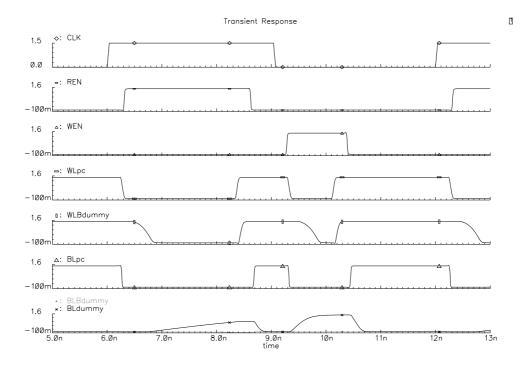

|              | 4.4                                      | Self-timing technique              | 99  |

|              | 4.5                                      | Input/output blocks                | .03 |

|              | 4.6                                      | Final layout                       | .04 |

|              | 4.7                                      | Future development and improvement | .07 |

| $\mathbf{A}$ | e Delay Locked Loop 1                    | 09                                 |     |

| в            | riplicated parameterized CRC generator 1 | 11                                 |     |

| Bi           | graphy 1                                 | 17                                 |     |

vii

viii

## Abstract

High Energy Physics research (HEP) involves the design of readout electronics for its experiments, which generate a high radiation field in the detectors. The several integrated circuits placed in the future Large Hadron Collider (LHC) experiments' environment have to resist the radiation and carry out their normal operation.

In this thesis I will describe in detail what, during my 10-months participation in the digital section of the Microelectronics group at CERN, I had the possibility to work on:

- The design of a radiation-tolerant data readout digital integrated circuit in a 0.25  $\mu$ m CMOS technology, called "the Kchip", for the CMS preshower front-end system. This will be described in Chapter 3.

- The design of a radiation-tolerant SRAM integrated circuit in a 0.13  $\mu$ m CMOS technology, for technology radiation testing purposes and future applications in the HEP field. The SRAM will be described in Chapter 4.

All the work has carried out under the supervision and with the help of Dr. Kostas Kloukinas and the section leader Dr. Alessandro Marchioro.

x

## Riassunto in lingua italiana

Il lavoro per questa tesi è stato svolto in circa 10 mesi presso il gruppo di microelettronica del CERN, l'Organizzazione Europea per la Ricerca Nucleare situata a Ginevra (Svizzera). Un nuovo acceleratore di particelle è tuttora in fase di costruzione al CERN: si tratta del Large Hadron Collider (LHC), il cui completamento è previsto per l'anno 2007. Questo acceleratore sarà in grado di creare collisioni protone-protone altamente energetiche fino a 14 TeV, un traguardo mai raggiunto finora, che permetterà di rispondere a domande fondamentali sulla fisica.

Quattro grandi esperimenti saranno costruiti per sfruttare questa risorsa: CMS, ATLAS, LHCb ed ALICE. Essi sorgeranno in quattro distinti punti lungo l'acceleratore, ove le collisioni di particelle avranno luogo. Ciascun esperimento sarà composto da più rivelatori con differenti caratteristiche e finalità, ma ciascun rivelatore conterrà, almeno in parte, elettronica necessaria per la lettura e trassmissione dei dati al di fuori dell'esperimento. Poichè l'ambiente in cui questi circuiti saranno inseriti diverrà, a seguito delle innumerevoli collisioni di particelle, altamente radioattivo, si rende necessario concepire circuiti elettronici capaci di sopportare tali radiazioni per tutta la durata prevista di funzionamento di LHC, il che vale a dire 10 anni.

Vista l'altissima quantità di informazione da estrarre da ogni rivelatore, l'utilizzo di circuiti integrati dedicati risulta indispensabile. Questi dispositivi devono essere sviluppati con accorgimenti particolari per rispondere ai suddetti vincoli. Il lavoro svolto per questa tesi è il progetto di due circuiti integrati digitali resistenti a radiazione, rispettivamente in due differenti tecnologie CMOS:

- un dispositivo per lettura dei dati dal preshower, uno dei rivelatori dell'esperimento CMS, realizzato in una tecnologia 0.25  $\mu$ m e chiamato "Kchip";

- una RAM statica, realizzata in una tecnologia 0.13  $\mu$ m, per misure di resistenza a radiazione ed eventuale successivo impiego come macrocella in altri circuiti integrati da inserire in ambiente altamente radioattivo.

## I. Dall'esperimento CMS al preshower

L'esperimento chiamato Compact Muon Solenoid (CMS) [7], è formato essenzialmente da una parte interna, più vicina al punto di collisone delle particelle, con compiti di tracciamento delle traiettorie, da una parte intermedia con compiti calorimetrici, in altre parole di misurazione dell'energia, ed infine da una parte esterna di rivelazione dei muoni. Il calorimetro più interno è un calorimetro elettromagnetico (ECAL) [8] basato su cristalli di scintillazione in tungstenato di piombo (PbWO<sub>4</sub>), in grado di traferire l'energia di elettroni incidenti sotto forma di luce rilevabile da fotodiodi e fototriodi posti sulla superfice esterna. Un sottile rivelatore, detto preshower, adiacente ai cristalli, ma più interno rispetto ad essi, si fa carico di misurare con buona accuratezza la posizione di entrata dell'elettrone convertito per ottenere una misura della sua energia.

Il preshower è composto da rivelatori a strisce in silicio, contenenti ciascuno 32 diffusioni  $p^+$  su substrato n che corrono lungo tutta la lunghezza del dispositivo. Le giunzioni sono poste in polarizzazione inversa in modo che una particella carica entrante nella regione di svuotamento che abbia sufficente energia ionizzi gli atomi del reticolo, scalzando elettroni dalla banda di valenza e creando lacune. Tali portatori saranno catturati dal campo elettrico e costituiranno quindi una corrente nel dispositivo. Un banco di preamplificatori posti nelle immediate vicinanze del rivelatore si fa carico di misurare la carica raccolta da ciascuna striscia. I dati così raccolti devono, attraverso vari stadi, infine raggiungere un veloce collegamento in fibra ottica uscente dall'esperimento per arrivare ad un potente sistema di calcolo e raccolta di informazioni chiamato *counting room*. Il sistema, posto nelle vicinanze del rivelatore e dentro l'esperimento, che si fa carico di misurare e inviare i dati al link ottico è chiamato *sistema di front-end*.

## II. Dispositivi a semiconduttore e circuiti integrati resistenti a radiazione

Gli effetti dovuti a radiazione nei semiconduttori si possono riassumere in due classi principali [5]: ionizzazione e spostamento. Il primo effetto consiste nella creazione di coppie elettrone-lacuna, ed il numero di coppie generate è direttamente proporzionale alla dose totale assorbita<sup>1</sup>. Lo spostamento è invece un danno diretto al reticolo del cristallo in cui uno degli atomi viene mosso dalla sua sede, spesso per finire in una posizione interstiziale (difetto di Frenkel). I transistor MOS sono poco sensibili ai difetti di spostamento,

<sup>&</sup>lt;sup>1</sup>La dose è una grandezza fisica che misura l'assorbimento di energia per unità di superficie irradiata. L'unità di misura S.I. è il *Gray*, ove 1 Gy = 1 J/Kg. Ciò nonostante, nell'ambiente della fisica delle alte energie, la vecchia unità *rad* è ancora usata: 1 rad =  $10^{-2}$  Gy = 100 erg/g.

#### II. Dispositivi a semiconduttore e circuiti integrati resistenti a radiazione 3

poichè la conduzione avviene su un sottile strato in prossimita della superfice del semiconduttore e non in profondità, dove la maggior parte dei danni si addensa<sup>2</sup>.

L'ossido di silicio presente in ogni transistore MOS ed usato anche come isolante fra dispositivi nelle tecnologie integrate è tuttavia molto sensibile agli effetti di ionizzazione [1]: mentre gli elettroni generati dalla radiazione incidente hanno una mobilità sufficente ad essere velocemente espulsi dall'ossido, le lacune rimangono in gran parte intrappolate. In particolare, nel caso di un transistore a canale n con gate polarizzato positivamente, le lacune raggiungono lentamente l'interfaccia ossido-semiconduttore e lì si fermano, abbassando la tensione di soglia del dispositivo. Allo stesso tempo le radiazioni inducono la formazione di trappole all'interfaccia, le quali invece tendono ad alzare la tensione di soglia. Il bilancio diventa positivo per tecnologie moderne con ossido di gate sottile. Per un transistore a canale p, eventuali lacune intrappolate nell'ossido abbassano la tensione di soglia, che viene però alzata in modulo, e l'effetto delle trappole all'interfaccia è dello stesso segno. In conclusione, in seguito a irradiazione la tensione di soglia si alza in modulo per tutti i dispositivi MOS.

Tuttavia, nelle tecnologie commerciali moderne come la 0.25  $\mu$ m, in cui l'ossido di gate è molto sottile, le variazioni della tensione di soglia indotte da radiazione sono contenute ed accettabili fino ed oltre a 30 Mrad di dose totale assorbita. Il vero problema risulta invece essere causato dalla degradazione dell'ossido di campo e dell'ossido laterale<sup>3</sup>, i quali, essendo spessi accumulano quantità maggiori di carica, pregiudicando in certe zone la loro capacità di isolamento elettrico. Infatti, quando cresciuto al di sopra di un substrato p, l'ossido contenente carica positiva può invertire la popolazione del semiconduttore sottostante creando un percorso conduttivo. Ciò pregiudica il funzionamento dei transistori a canale n, aumentando con la dose totale assorbita la corrente di perdita tra drain e source.

Accorgimenti particolari di layout e di circuito possono risolvere queste problematiche senza dovere ricorrere a tecnologie specializzate con processi dedicati, che ai fini pratici sono meno avanzate ed hanno un costo elevato ed una resa inferiore alle tecnologie commerciali.

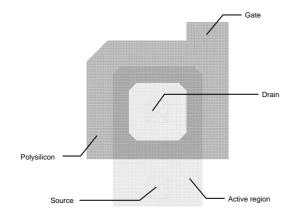

Questi accorgimenti risultano in pratica nel modificare la forma di tutti i transistori MOS a canale n, eliminando il bordo del canale e così l'ossido laterale, ed in più aggiungere ad essi un anello di guardia p<sup>+</sup> circostante per isolarli da altri dispositivi. Il gate, che diviene di forma circolare, circonda quindi completamente il drain, posto al suo interno, mentre il source rimane

$<sup>^{2}</sup>$ Altri dispositivi, come ad esempio i transistori bipolari, sono più sensibili a questo tipo di difetti proprio perché basati su una conduzione verticale.

$<sup>^{3}</sup>$ L'ossido laterale risiede ai bordi del canale e sotto il gate. Nelle tecnologie moderne la tecnica Shallow Trench Isolation (STI) è utilizzata al posto della più anziana LOCOS. L'accezione ossido di campo è qui utilizzata riferendosi all'ossido di isolamento tra dispositivi differenti, indipendentemente dalla tecnica utilizzata.

all'esterno (si veda la fig. 2.7 a pag. 28). Tutto questo si traduce ovviamente in una riduzione della massima densita di componenti per unità di area.

Una libreria di standard cells [19] per il veloce sviluppo automatico di parti digitali di circuiti integrati è stata preparata dal gruppo di microelettronica del CERN, rispettando le considerazioni precedenti.

Un ulteriore difficoltà nel disegno di circuiti digitali per ambiente radioattivo è la vulnerabilità ai Single Event Upset (SEU) da parte della logica: una particella carica può interagire con un dispositivo in modo da cambiare temporaneamente il livello logico della sua uscita. Ne segue che il contenuto di qualsiasi dispositivo integrato di memorizzazione può subire cambiamenti e va quindi protetto con un opportuna ridondanza a livello di circuito. Ciò è maggiormente importante per i registri utilizzati nelle macchine a stati finiti, utilizzate sovente nelle logiche di controllo dei circuiti integrati: un dato errato in uno di tali registri può indurre comportamenti errati da parte dell'intero circuito, e quindi del sistema. La soluzione utilizzata è di triplicare ciascuna macchina a stati finiti ed introdurre una logica di voto sui tre dati in uscita da esse: il dato scelto da almeno 2 macchine su 3 verrà posto in uscita. Lo stesso ragionamento è applicato per lo stato memorizzato, che viene votato e ricaricato in ognuna delle tre macchine a stati finiti con accorgimenti particolari (si veda la sezione 2.3.2 a pag. 29).

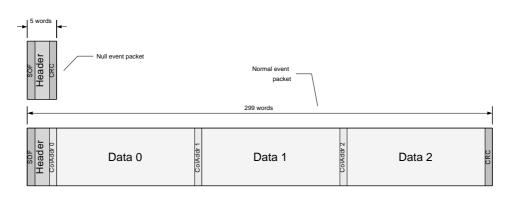

## III. Il Kchip

Il sistema di front-end del preshower [18] è costituito da una parte analogica connessa con il rivelatore a microstrisce di silicio, una parte di conversione analogico/digitale ed una parte digitale dedicata alla trasmissione dei dati ed al controllo del sistema. Il sistema di acquisizione lavora campionando i dati ad una frequenza di 40.08 MHz, che corrisponde esattamente al numero di scontri tra particelle per unità di tempo. I dati provenienti da un particolare scontro sono detti *evento*.

I dati, nel loro percorso dalla sorgente (il rivelatore) alla destinazione (il link ottico), attraversano nell'ordine:

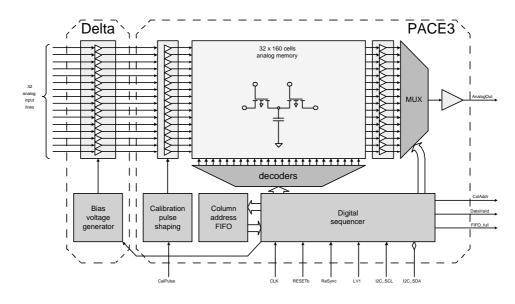

- un chipset analogico, chiamato PACE, composto da un amplificatore charge-sensitive ed una memoria analogica organizzata a pipeline;

- un convertitore analogico/digitale (ADC);

- il Kchip, incaricato di memorizzare e formattare i dati in un pacchetto opportuno per la trasmissione;

- il Gigabit Optical Link (GOL) chip, che serializza i dati e pilota il laser per il link.

Ci sono quindi due stadi di memorizzazione consecutivi nel sistema di frontend: uno in forma analogica residente nel PACE chipset ed uno in forma digitale nel Kchip. Il primo stadio si rende necessario poichè non tutti gli eventi aquisiti devono essere trasferiti al di fuori dell'esperimento: la quantità di informazione che sarebbe infatti necessario trasmettere richiederebbe un infrastruttura ancora più imponente e costosa. Ciò che avviene è invece una selezione degli eventi, basata su un insieme limitato di dati e semplici algoritmi, scartando i dati meno interessanti e riducendo il numero di eventi inviati per unità di tempo a 100 kHz. Chiaramente la decisione sulla selezione o meno di un evento richiede un certo intervallo di tempo per essere valutata, e durante questo intervallo i dati devono essere memorizzati.

Il Kchip unisce i dati provenienti da un massimo di 4 rivelatori in un unico pacchetto, al fine di massimizzare l'utilizzo del canale. In questo modo però, il collegamento ottico risulta essere più lento dell'insieme di 4 sorgenti in termini di massime prestazioni. Ne segue la necessità del secondo stadio di memorizzazione, che pone i dati digitalizzati provenienti da 4 PACE chipsets in code FIFO, in attesa di essere inviati nel canale.

Oltre ai menzionati principali incarichi, il Kchip svolge svariate altre funzioni: controlla i 4 chipset PACE ad esso connessi e ne verifica la sincronizzazione ed il corretto funzionamento, interagisce con il chip GOL effettuando un controllo ad alto livello del link, segnala eventuali errori alla counting room, ecc. (si veda la sezione 3.2 a pag. 46 per una lista completa delle funzionalità).

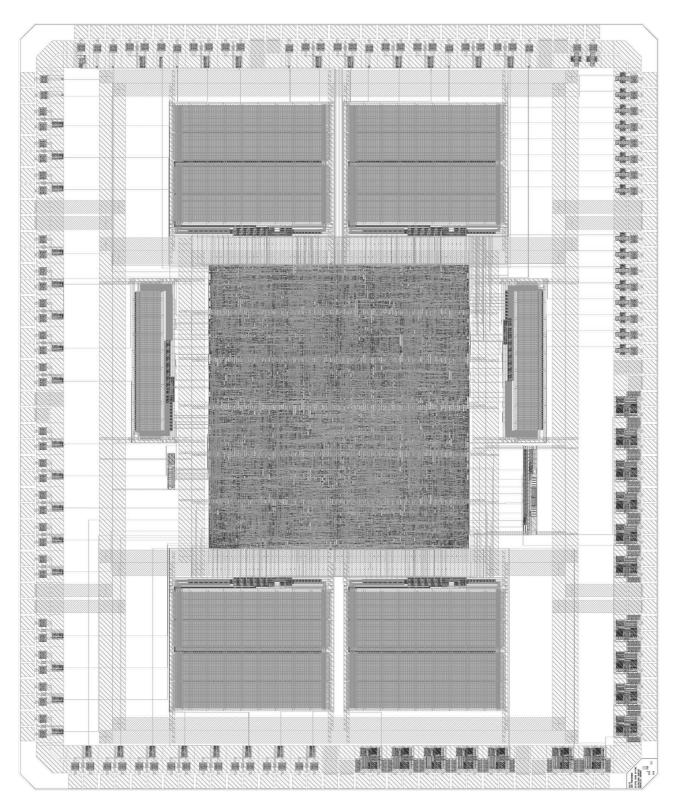

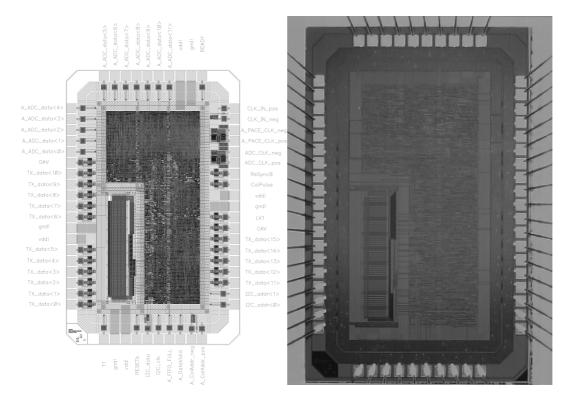

L'integrato è stato progettato utilizzando tecniche CAD di sintesi e layout automatiche, facendo uso della libreria di porte logiche standard cells in tecnologia CMOS 0.25  $\mu$ m disponibile. Tutto il circuito è stato perciò descritto in Verilog, un linguaggio di descrizione dell'hardware (HDL), per poi essere passato ai tool di sintesi e place & route. Ad ogni stadio di progettazione, verifiche intensive tramite simulazione sono state effettuate grazie alle potenzialità offerte dal Verilog. Alla fine, gli usuali controlli di rispetto delle regole di layout (DRC) e corrispondenza tra layout e schematic (LVS) sono stati compiuti.

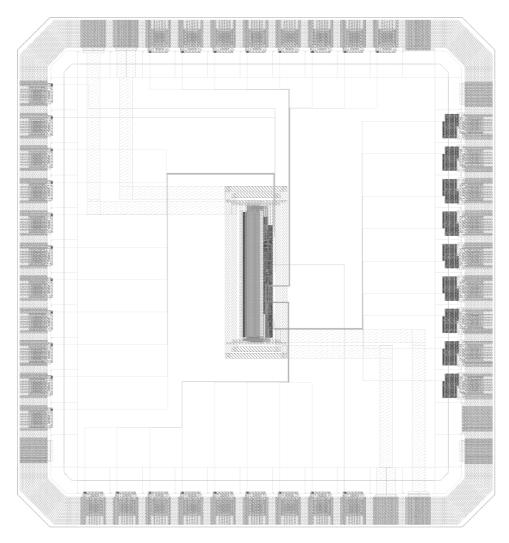

Il risultato è un chip di dimensioni  $6 \times 5 \text{ mm}^2$ , contentente 13000 porte logiche più circa 80 kbit di memoria statica (SRAM), che formano insieme un totale di circa 660000 transistori. Il chip sta per iniziare la prima fase di fabbricazione a scopo di test.

# IV. Una RAM statica in tecnologia 0.13 micron resistente a radiazione

La tecnologia 0.13  $\mu$ m risulta relativamente nuova per le applicazioni in ambiente altamente radioattivo, ed è ancora in fase di sperimentazione. Numerose misure dovranno essere compiute per qualificarla come adatta, nonostante le promesse siano molto buone: infatti l'ossido di gate è ancora più sottile della già assestata tecnologia 0.25  $\mu$ m, e gli isolamenti sono di migliore qualità. Tra le misure necessarie compare la sensibilità ai SEUs, destinata ad aumentare rispetto a tecnologie precedenti: diminuendo le dimensioni dei dispositivi, si abbassano conseguenza anche le capacità associate, e quindi una particella carica interagente con esse indurra variazioni di tensione più elevate.

Per effettuare questi test è richiesta, una memoria statica resistente agli altri effetti di radiazione. La SRAM così ottenuta potrà poi essere utilizzata come macrocella in altri circuiti integrati per ambiente radioattivo, entrando a far parte di una libreria di celle resistenti a radiazione già parzialmente preparata al CERN.

Il progetto è basato su un disegno esistente nella precedente tecnologia [20], mantenendo la medesima architettura, ma chiaramente cambiando i dimensionamenti ed i layout. In particolare il layout della SRAM è fatto in gran parte manualmente usando solo per alcuni blocchi le standard cells, che comunque sono piazzate e connesse ancora una volta manualmente.

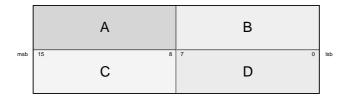

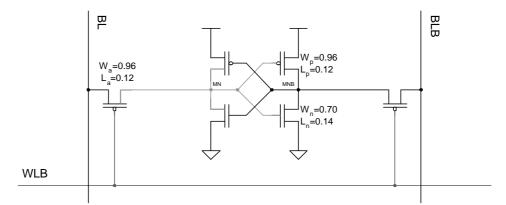

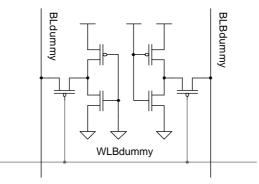

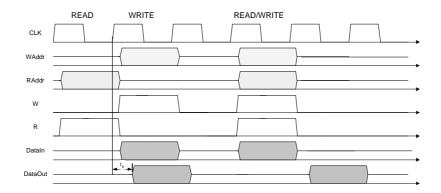

L'architettura scelta prevede l'utilizzo di una cella di memoria a 6 transistori single-ported in modo da risparmiare area, ma allo stesso tempo di avere un comportamento dual-ported visto dall'esterno. Ciò implica il portare a termine le due operazioni di lettura e scrittura una dopo l'altra ma nel medesimo ciclo di clock.

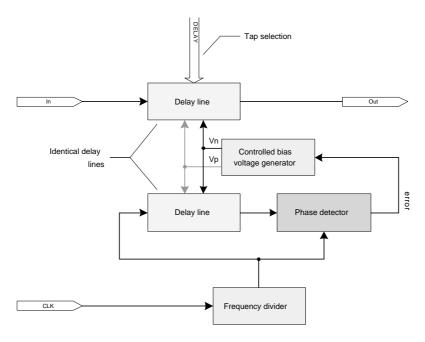

In più, visto il possibile riutilizzo del blocco inserito in altri integrati, la dimensione della SRAM deve essere facilmente riconfigurabile: ciò è ottenuto costruendo una memoria modulare in modo che replicando blocchi di base tante volte quanto necessario si raggiungere la grandezza di memoria voluta. La temporizzazione della memoria deve adattarsi di conseguenza alla nuova dimensione, per cui tecniche di self-timing sono state sfruttate.

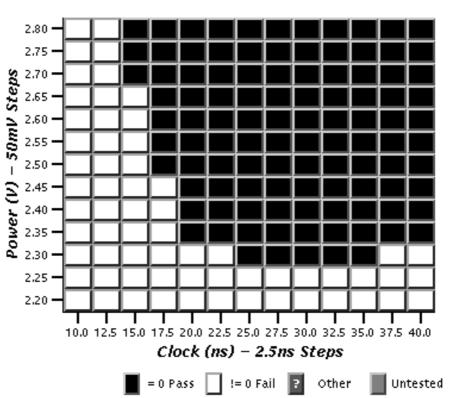

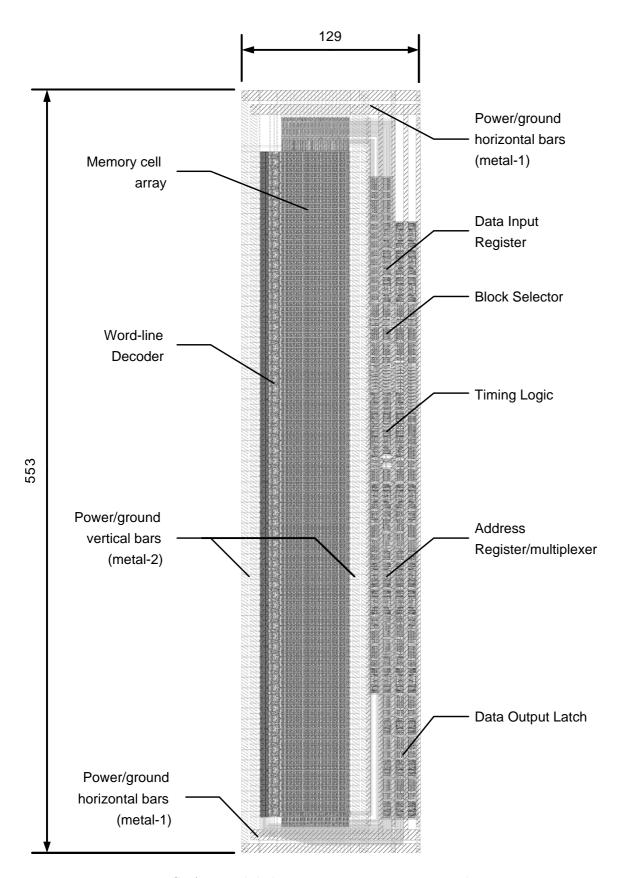

Tra gli strumenti utilizzati per il progetto risalta il grande impiego di simulazioni SPICE, sia per il dimensionamento che per la verifica. Il risultato ottenuto è un blocco di dimensioni  $553 \times 129 \ \mu\text{m}^2$  posto in un chip di  $1.84 \times 1.96 \ \text{mm}^2$ , dimensione imposta dal numero di pad input/output necessari. Si stima che la SRAM possa lavorare senza problemi fino ad una frequenza di 140 MHz (nel caso peggiore). Il chip è attualmente in fase finale di fabbricazione in un numero limitato di pezzi, grazie allo spazio concesso in un Multi-Project Wafer (MPW).

## Chapter 1

## Introduction

## 1.1 CERN and High Energy Physics

High Energy Physics (HEP) explores the innermost basic constituents of matter and their mutual interactions.

CERN<sup>1</sup>, the European Laboratory for Particle Physics, was founded in 1954 in Geneva (Switzerland) as a joint European effort to provide a major scientific facility for particle physicists. It is today one of the world's largest and most successful scientific laboratories, as well as an outstanding example of international collaboration between its 19 member states<sup>2</sup>.

### 1.1.1 Accelerators and detectors

Particle physics studies are based on particle collisions at high kinetic energy, which means that the particles used in the experiments should have high speed. Particle accelerators, like a synchrotron, are used to reach the speed needed.

Inside particle accelerators, beams of charged particles are pushed by high frequency electrodes into a vacuum pipe. The pipe can be linear or circular: in the second case, beam bending is performed by dipole magnets accordingly to the Lorentz force law. Quadrupole magnets are used to focus the beam.

The results of a collision have then to be observed through a detector. A detector is usually composed by many sub-detectors with different capabilities and goals, and all of them are connected to a computer system for analysis and event reconstruction. The goal is to identify, count and trace, as many particles coming out from the collision point as possible.

<sup>&</sup>lt;sup>1</sup>Once called Conseil Européen pour la Recherche Nucléaire, now is officially named as Organisation Européen pour la Recherche Nucléaire.

<sup>&</sup>lt;sup>2</sup>Member states are Austria, Belgium, Bulgaria, Czech Republic, Denmark, Finland, France, Germany, Greece, Hungary, Italy, The Netherlands, Norway, Poland, Portugal, Slovak Republic, Spain, Sweden, Switzerland and the United Kingdom.

A detector togheter with its infrastructure is called *experiment*.

#### 1.1.2 The Large Hadron Collider

In year 2000 the biggest CERN's accelerator, the Large Electron Positron collider (LEP), was dismantled in order to leave place for a new, more powerful, machine: the Large Hadron Collider (LHC). While the LEP was able to reach electron-positron collisions with a centre of mass energy of 200 GeV, the LHC is designed to collide protons, going further up to 14 TeV.

The challenge, in modern particle physics research, is to probe at higher and higher collision energies, either because the basic constituents to be studied are only present at those energies, or because they are normally tied in complex aggregates and need those energies to split apart. Reaching high energy densities means also recreating the earliest universe conditions during the big bang. Thus, the higher collision energy we manage to create, the smaller dimension we study, and the earlier back in time we can observe.

The LEP was built in a 100 m underground tunnel, with the earth shielding its radiation, following a 27 km long ring. Such a big circumference was necessary because of the energy loss by bremsstrahlung: electrons and positrons emit photons when accelerated, therefore the same happens bending their trajectory; the less the trajectory is bent, the less energy they lose.

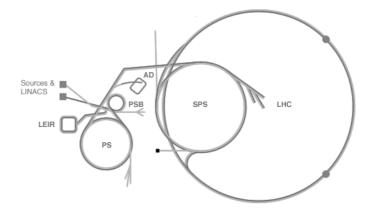

Figure 1.1: Plan of accelerators at CERN.

In these days the LEP is being replaced with the LHC, which employs the same existing cavern. The LHC is planned to be fully operational from year 2007 onward.

LHC will make use of superconducting magnets cooled at 1.9 K, spread all along the ring to bend the beams, with nominal field of 8.33 T, allowing the storage at the desired energy of 7 TeV of two proton beams. The two beams will run in opposite directions, but colliding only in four points, where the experiments take place. LHC is designed to be able to accelerate also lead ions, much more massive than protons, to attain collision energies of 1148 TeV, but this will happen only later in the accelerator planned schedule.

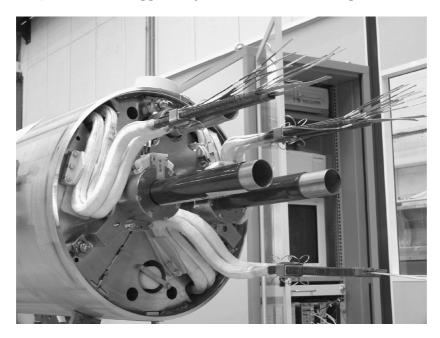

Figure 1.2: LHC accelerator section photograph.

The beams will also be segmented in 2835 bunches of  $1.1 \cdot 10^{11}$  particles per bunch. This will make two bunches running in opposite directions to meet in the interaction points every 24.95 ns at the nominal speed. In other words the collision frequency will be 40.08 MHz.

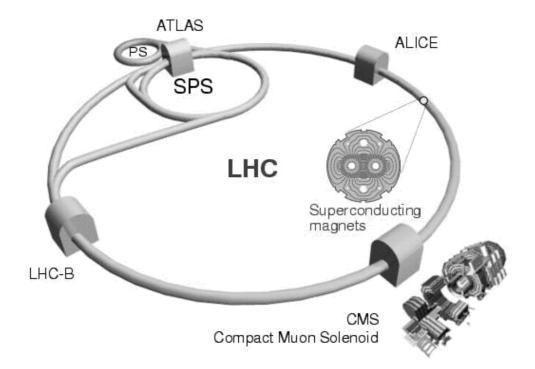

The four experiments designed to make use of LHC are:

- the Compact Muon Solenoid (CMS);

- A Toroidal Lhc ApparatuS (ATLAS);

- A Large Ion Collider Experiment (ALICE);

- LHCb.

Only the CMS experiment will be treated in detail, since most of this work has been developed to be part of it.

## 1.2 The Compact Muon Solenoid experiment

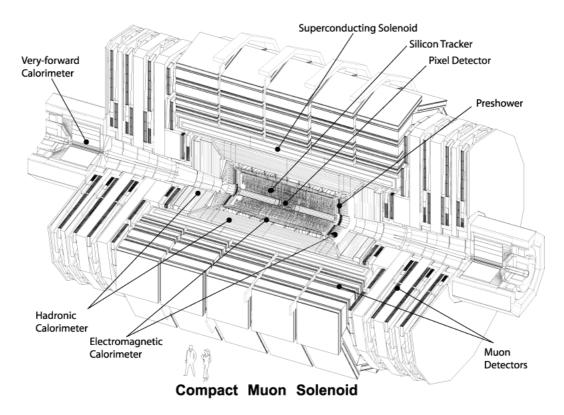

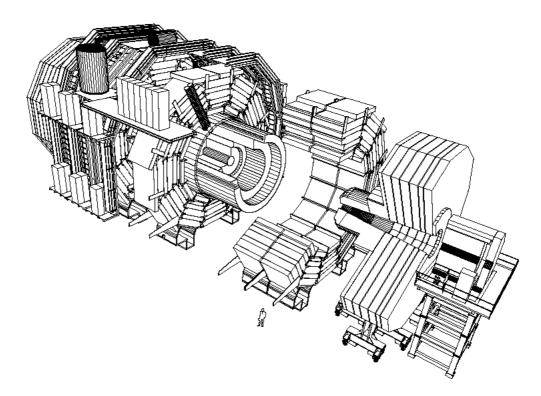

Figures 1.4 and 1.5 show representations of the CMS. As can be seen, it has a cylinder's shape with a diameter of 14.6 m and 21.6 m long, excluding the

Figure 1.3: Underground view of LHC and its experiments.

very forward calorimeter. Its total weight is about 14500 tonnes. The beams run along the axis entering from the two sides, and collide in the center of the detector, the point also referred as *vertex*. The physics performance is guaranteed by its almost  $4\pi$  solid angle coverage. CMS is optimized for the Higgs boson discovery.

The detector is divided into three main sections: the middle barrel and the two side identical endcaps. A 13 m long superconducting solenoid magnet generates a uniform 4 T field inside the barrel region, which bends the charged particles' trajectory in order to identify them by their mass and charge. A return path for the magnetic flux is guaranteed by a huge iron structure, covering the whole machine, called "the return yoke". Inside the return yoke the magnetic field is of about 2 T.

The CMS is composed by several sub-detectors, which, from the inside to the outside are:

- The tracker composed by silicon pixel detectors in the inner part, and silicon strip detectors in the outer. It traces the trajectory of charged particles with an accuracy of about 100  $\mu$ m;

- The electromagnetic calorimeter (ECAL) which measures the energies of electrons and photons through  $PbWO_4$  crystals. The ECAL con-

Figure 1.4: View of CMS with its parts and sub-detectors.

tains also a small silicon strip detector situated in the endcaps' inner part called the *preshower*;

- **The hadronic calorimeter** (HCAL) made with thick layers of copper as absorber and thin layers of plastic scintillator, it measures the energies of hadrons;

- **The muon chambers** used for detecting muons, which are highly penetrating. The muon chambers are interleaved with the iron return yoke and are made with gaseous particle detectors.

- The very forward calorimeter placed along the axis only in the outer barrel region, it is made with an iron/gas detector.

Most of the work presented here will be part of the ECAL sub-detector preshower, thus it will be treated with more detail later.

Figure 1.5: 3d split view of the CMS detector.

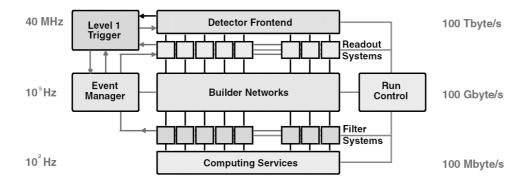

### 1.2.1 The Trigger and Data Acquisition System

As mentioned before, the bunch crossing frequency is about 40.08 MHz, with an average of 20 inelastic events<sup>3</sup> occurring each time. This means that a rate of about 800 MHz interactions will produce an enormous amount of data coming out from the experiment. Nevertheless, only a small fraction of the collisions will be interesting from the physics point of view, therefore a filtering of the data has to be performed. It is also necessary to do this in real-time, reducing the rate to 100 Hz, which is the maximum rate that should be archived for off-line analysis [7].

All these jobs are carried out by the Trigger and Data Acquisition System (TriDAS) of the experiment, which selects the useful events<sup>4</sup>, rejecting the rest, by evaluating a subset of the data. This operation is done in two steps, or, in other words, two subsequent selections will take place. Figure 1.6 shows the DAS block diagram.

For the first selection, the TriDAS calculates a Level-1 trigger signal indicating if the data has to be kept or not. The Level-1 trigger decision

$<sup>^{3}</sup>$ An inelastic event is collision in which the interaction involves other forces than the electromagnetic and gravitational forces.

<sup>&</sup>lt;sup>4</sup>All the data relative to one bunch crossing is referred as an *event*.

Figure 1.6: CMS Data Acquisition System block diagram.

latency is about 3.2  $\mu$ s, therefore the data coming out of the detectors has to be stored in a set of memories, waiting for it. The Level-1 trigger maximum rate is 100 kHz, thus the rejection ratio is about 400.

After the first selection, the events are reconstructed, joining together the data from different sub-detectors but relative to the same collision. Then, a Level-2 selection will be performed, obtaining the desired event rate of 100 Hz. Despite this large reduction the final experiment data rate is still over 1 Tbyte/day, which is huge for an experiment planned to last 10 years.

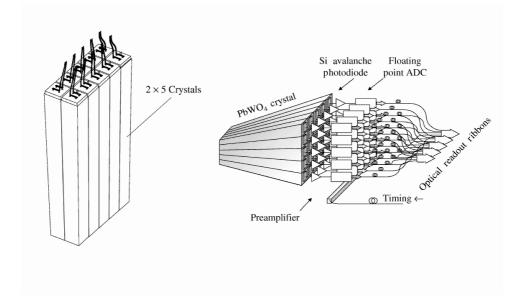

### 1.2.2 The Electromagnetic Calorimeter

As described before, the ECAL provides a precise measurement of the energy of photons and electrons. It has a small spatial resolution but it's designed to have an excellent energy resolution. A scintillating crystal calorimeter offer the best performance for this parameter, and, moreover, high density crystals allow a very compact calorimeter system [8].

In scintillating crystals, decelerating electrons will emit Bremsstrahlung. The generated photons will again interact with the lattice, ionizing the atoms and creating new energetic electrons and so on. This chain interaction is called *electron shower* and the resulting photons can be observed using photoetectors.

Following successful beam irradiation tests in 1994,  $PbWO_4$  (lead tungstate) crystals were chosen as the scintillating medium. The ECAL will contain 80,000 of them arranged into the barrel and endcap sections. Figure 1.7 shows a submodule unit.

The outer side of each crystal will be covered with photodetectors in order to observe the scintillation light. Silicon avalanche photodiodes (APDs<sup>5</sup>)

<sup>&</sup>lt;sup>5</sup>APDs are diodes with a reverse biased buried pn junction at a very high electric field of sufficient strength such that photoelectrons arriving in the junction are accelerated and multiplied, by impact ionization, in an avalanche process.

#### 1. Introduction

Figure 1.7: Lead tungstate crystal submodule and associated readout electronics.

have been chosen for use in the barrel region, after proving to be suitable to the high radiation and magnetic environment. Nevertheless, in the endcap regions, where the radiation environment is more harsh, vacuum phototriodes (VPTs) are used instead. The photodetectors signals are sampled by a set of ADCs and sent to the readout electronics.

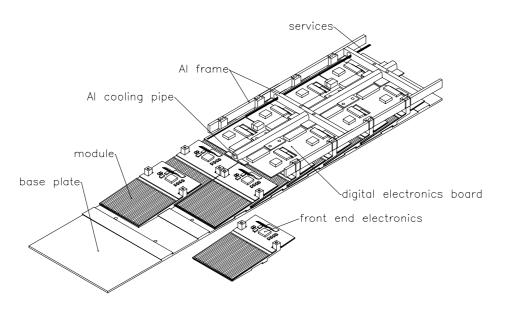

#### 1.2.3 The preshower

The ECAL will contain a preshower detector in the endcap regions, whose main function is to provide  $\gamma - \pi^0$  separation. In fact an overlap between two showers, due to a neutral pion  $\pi^0$  decay into two photons, can be confused with a single shower from an energetic gamma ray  $\gamma$ .

The preshower measures the impact position of the shower using two orthogonal silicon strips detectors with a 1.9 mm pitch. The operating temperature of the preshower is -5 °C to maintain the performance of the silicon strips after irradiation [22]. The total area covered by silicon detectors in the preshower is large: 16.4 m<sup>2</sup>; thus a simple classical arrangement of p<sup>+</sup> strips on n bulk structure has been chosen (the same choice has been done for the CMS tracker detector).

Each  $63 \times 63 \text{ mm}^2$  silicon detector, subdivided into 32 strips 61 mm long, is mounted on a *micromodule* together with its front end analog electronics. A various number of micromodules form a *ladder*, which has two columns of adjacent detectors with their digital electronics mounted on top. A ladder is

#### 1.3 Notation

Figure 1.8: A ladder with its micromodule units.

shown in Figure 1.8. The digital electronics boards are called *motherboards* and each one of them is connected to 4 micromodules.

The data is sent out of the experiment through an 800 Mbit/s optical link. A more detailed description of the preshower's front end electronics will be given later.

## 1.3 Notation

In the following chapters a special notation will be used:

- Verbatim text will be used to indicate electrical or optical signals or buses;

- Sans serif characters will be used when referring Functional Blocks or Circuits;

- Small capital letters will be used to name STATE MACHINE'S STATES.

1. Introduction

## Chapter 2

# Radiation tolerant semiconductor devices and integrated circuits

## 2.1 Introduction

### 2.1.1 Radiation environment in the LHC

In order to maximize the number of interesting events obtained from the experiments, the LHC accelerator is designed to reach a very high peak luminosity<sup>1</sup>:  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> for protons and  $1.95 \cdot 10^{27}$  cm<sup>-2</sup>s<sup>-1</sup> for lead ions. This will bring, in the case of protons, to an average production of  $8 \cdot 10^8$  inelastic proton-proton collisions per second, creating an extremely hostile radiation environment.

In addition, at LHC the high beam energy combined with the very high luminosity results in numerous intense cascades, which will end up in an immense number of low-energy particles. In fact, particles energies exceeding 10 GeV are expected to be very rare in the detectors' barrel, and also in the major part of the endcap. Therefore the radiation studies focussed on the energy range around 1 GeV and below.

While induced radioactivity was negligible in electron-positron colliders Induced radioactivity (like the LEP), it will be a major concern at LHC. It can be assumed that each inelastic hadronic interaction results in a residual nucleus, which can have almost any mass and charge smaller than that of the target. Roughly 30% of the inelastic hadronic interactions create long-lived radionuclides

$<sup>^{1}</sup>$ The luminosity can be thought as the number of particles per unit area in the interaction point of the two beams.

[14, 28] which contribute to the dose rate from induced activity in the experimental area. This activity decreases relatively slowly after the end of irradiation, so that even long cooling times do not significantly improve the situation. Activation can also occur through neutron interactions, especially in the thermal regime. However, except for a few special materials, this is usually a minor contribution.

#### 2.1.2 Radiation environment in the CMS experiment

As resumed in Table 2.1 total  $dose^2$  values in the CMS experiment could be high, in the worst case conditions, up to 50 Mrad. The detectors' front-end electronics has then to stand this enormous amount of radiation, especially in the inner tracker and in the ECAL endcaps, where the levels are higher.

| Sub-detector        |                     | Total<br>dose<br>[Mrad] | $Neutron \\ fluence \\ [10^{14} \text{ cm}^{-2}]$ | $Charged\ hadron\ fluence\ [10^{14}\ cm^{-2}]$ |

|---------------------|---------------------|-------------------------|---------------------------------------------------|------------------------------------------------|

| Tracker             | at 7cm              | 35.                     | 1.                                                | 10.                                            |

|                     | at $22 \mathrm{cm}$ | 6.5                     | .35                                               | 1.5                                            |

|                     | at $75 \mathrm{cm}$ | .7                      | .15                                               | .25                                            |

| ECAL                | barrel              | .5                      | .5                                                | .005                                           |

|                     | endcaps             | 20.                     | 10.                                               | .6                                             |

| HCAL                | barrel              | .02                     | .1                                                | -                                              |

|                     | endcaps             | 2.5                     | 5.                                                | -                                              |

| Muon chambers       |                     | .005                    | .025                                              | -                                              |

| Forward calorimeter |                     | 500.                    | 250.                                              | -                                              |

| Experimental hall   |                     | .0005                   | .001                                              | -                                              |

Table 2.1: CMS sub-detectors' radiation environment in the 10 years experiment lifetime [12], equivalent to  $5 \cdot 10^7$  s. The reported doses and fluences are the maxima inside each sub-detector.

Electromagnetic calorimeter

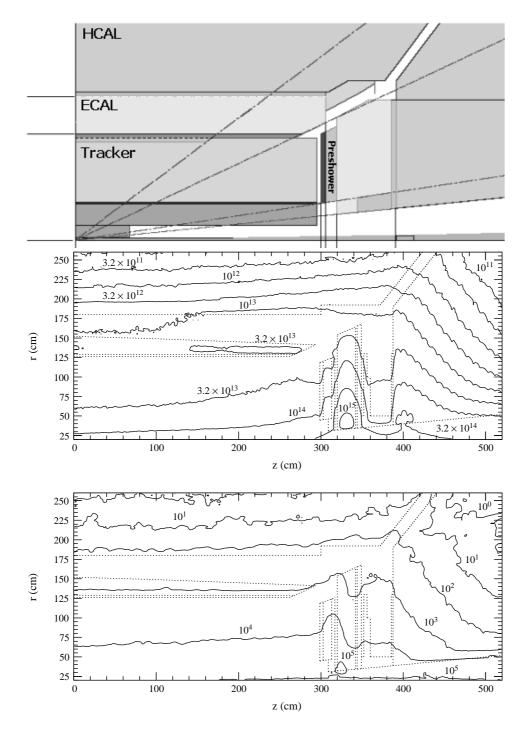

The silicon layer of the preshower detector will be exposed to the neutron albedo from the electromagnetic calorimeter, while charged hadrons do not contribute significantly at any preshower position. Dose rates drop rapidly when moving from the shower maximum deeper into the calorimeter. Figure 2.1 shows total doses and particle fluences in the calorimeters' region;

<sup>&</sup>lt;sup>2</sup>Total dose is defined as the total absorbed energy per unit mass. Although the S.I. unit for total dose is the *Gray* (Gy), where 1 Gy = 1 J/Kg, in the high energy physics community the old unit *rad* is still used: 1 rad =  $10^{-2}$  Gy = 100 erg/g.

Figure 2.1: Fluence of neutrons (with energy above 100 keV) and charged hadrons in  $\text{cm}^{-2}$  (upper plot) and radiation dose in Gy (lower plot), in the region inside the solenoid [8]. The dotted lines in the graphs indicate the geometry shown above.

it also clearly demonstrates that the ECAL's crystals are the most intense source of fast neutrons inside the CMS.

Without any moderators separating it from the crystals, the preshower would be directly exposed to that neutron flux. The most effective shielding method is based on elastic scattering of the neutrons from hydrogen nuclei. Studies have shown that a few centimeters of polyethylene are sufficient to lower the energy of the neutrons below the 100 keV limit. Thus, sandwiching the preshower between two 4 cm layers of polyethylene, this fluence can be reduced by a factor of 3 [13].

An even better protection would be obtained by using a larger moderator but because of space limitations, the thickness of the moderator is crucial.

The preshower still receives a significant amount of radiation (about 3 Mrad in 10 years): this rules out every possibility of using commercial solutions for its design.

#### 2.1.3 Radiation tolerant ICs

It is then clear that the integrated circuits used for the front-end<sup>3</sup> electronics of the detectors must be resistant to radiation. The need of these kind of circuits for the various applications mentioned above led, in the past, to the development of special technologies, called "radiation hardened", where particular processing methods are used in order to improve their radiation tolerance. Modifying the *process* steps is one of the three ways to improve the radiation tolerance of an integrated circuit. The two other possibilities are to use special *layout* techniques or special *circuit and system* architectures.

The gate oxide

Commercial vs rad-hard In a metal-oxide-semiconductor (MOS) transistor, the part most sensitive to radiation effects is the gate oxide. One way to reduce those effects is to reduce the gate's thickness, which is the natural trend in modern technologies. The market of memories, microprocessors and, in general, digital integrated circuits, has driven a very fast technological evolution in the past 20 years, which has led to today's deep submicron devices with less than 2 nm gate oxide thickness.

This suggests the possibility of using modern commercial CMOS (complementary MOS) technologies in radiation environment without introducing or modifying any particular process step. Hardening a technology by introducing special processing steps is generally not convenient for us since the foundries would not modify their processes for such a small market without increasing considerably the prices.

<sup>&</sup>lt;sup>3</sup>Usually, in the CERN experiments context, the electronics inside the experiments is referred as *front-end* (FE). The detectors and their immediately close analog equipment is instead called *very front-end* (VFE).

#### 2.2 Radiation effects

Having a radiation tolerant gate oxide does not resolve all the possible problems when irradiating an integrated circuit made in a standard deep submicron technology. To solve these problems one can still adapt the layout and the architecture of the circuits and of the system.

The use of deep submicron CMOS technologies has several beneficial aspects, such as speed, reduced power consumption, high level of integration, high volume production. Moreover commercial technologies do not suffer from the problems of radiation hardened technologies, which are more expensive and less advanced (usually a couple of generations behind). Last but not least, the availability of some radiation hardened technologies in the future is not certain, and cases have already been experienced of foundries stopping the production of their radiation hardened processes due to the drop of demand.

For this reason, in 1996, CERN's microelectronics group started to investigate the possibility of using a commercial CMOS technology to integrate the circuits to be used in the detectors. The very promising results obtained led, at the end of the same year, to the proposal of a Research and Development project<sup>4</sup> which was approved in March 1997. The aim of the project was to assess the improved radiation tolerance of submicron CMOS technologies and to study the use of design and layout techniques to increase it further. At that time, 0.7  $\mu$ m technology was the state of the art, but since then the evolution has been followed characterizing 0.5, 0.35 and 0.25  $\mu$ m technologies.

As confirmed in the RD49 status reports [16, 17], the results were very successful, and allowed the design of integrated circuits which could stand doses of 30 Mrad and beyond [27, 15]. At the present time a 0.13  $\mu$ m technology is being studied, while a rich 0.25  $\mu$ m digital library is commonly used for design.

## 2.2 Radiation effects

### 2.2.1 Radiation effects on matter

The manner in which radiation interacts with solid materials depends on many factors, but the three main criteria of classification are charge, mass and energy of the incident particle. Protons and electrons are charged particles, while neutrons and photons are neutral particles. From the mass point of view, instead, protons and neutrons are heavy particles, while electrons are light particles.

Charged particles interact through the Coloumb force with the target

CERN RD49

$<sup>^4\,{\</sup>rm ``CERN}$  RD49 – Study of the radiation tolerance of ICs for LHC"

22 2. Radiation tolerant semiconductor devices and integrated circuits

material atoms inducing ionization or atomic excitation. Neutral particles instead do not exibilit this kind of behavior.

- Massive particles can collide with the nuclei of the target material causing displacement, excitation or nuclear reactions if the energy is enough.

- **Electrons** also generate Bremsstrahlung (X-rays) when decelerating into the target.

- **Photons** have zero mass and no charge, therefore they have a special behavior with respect to other particles. They can interact, ordered by energy of the photon:

- by photoelectric effect, in which an electron of the target atom changes energy state, possibly ionizing the atom, and the photon is completely absorbed;

- by Compton effect, in which an electron of the target atom is set free and a residual photon is emitted;

- by electron-positron pair creation (above 1.024 MeV).

Semiconductors and In practice, the effects of radiation on the materials involved in miinsulators croelectronic devices production can be grouped in two classes: ionization effects and nuclear displacement [5].

- **Ionization** creates electron-hole pairs. The number of pairs created is directly proportional to the total absorbed dose. For this reason, the studies on the effects of ionization refer only to this quantity and not to the type of particle chosen.

- **Displacement** gives origin to crystal defects, most of which are Frenkel pairs. In  $SiO_2$  at room temperature, 90% of the Frenkel pairs recombine within a minute after the end of irradiation. MOS transistors are almost entirely insensitive to displacement damage, since they are device whose conduction is based on the flow of majority carriers below the silicon-oxide interface, a region which does not extend deeply in the bulk. This phenomenon has therefore a limited importance.

### 2.2.2 Radiation effects on electrical parameters of MOS transistors

As mentioned above, MOS transistors are more sensitive to ionization than to displacement damage. In the gate (metal or polysilicon) and in the substrate the electron-hole pairs generated quickly disappear, since these are materials with small resistance. On the other side, in the oxide, which is

Positive charge trapped in SiO<sub>2</sub>

#### 2.2 Radiation effects

an insulator, electrons and holes have a different behavior, as their mobility differ by  $10^5$  to  $10^{10}$  times<sup>5</sup>.

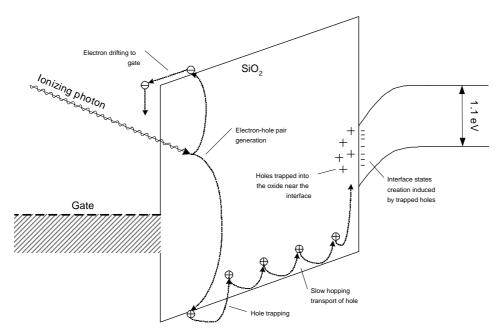

Only a fraction of the induced electron-hole pairs will recombine immediately after being generated, while the rest will be separated by the electric field. In the case of a positive bias applied to the gate, the electrons drift to the gate electrode in a very short time whereas the holes move towards the Si–SiO<sub>2</sub> interface with a very different slower transport phenomenon<sup>6</sup>. Then, close to the interface, but still in the oxide, some holes may be trapped, giving origin to a fixed positive oxide charge  $Q_{ox}$ .

Figure 2.2: Band diagram showing the transport and trapping of holes in the oxide.

The amount of trapped charge is proportional to the number of defects in the silicon dioxide: depending on the oxide quality and on the electric field, the fraction of trapped holes varies from 1% to 100% [3, 1]. The non trapped holes which reach the interface, will recombine with electrons coming from the silicon. Moreover these electrons may tunnel from the silicon surface into the oxide and recombine with trapped holes, giving origin to a *tunneleffect-based annealing* [25]. This effect makes the trapped charge quantity to vary with the absorbed dose rate and its history.

<sup>&</sup>lt;sup>5</sup>Typical SiO<sub>2</sub> electron mobility at room temperature is 20 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, while for holes it depends strongly on the temperature and on the electric field, and ranges between  $10^{-4}$ – $10^{-11}$  cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>.

<sup>&</sup>lt;sup>6</sup>The transport of holes in  $SiO_2$  is based on the concept of *small polaron hopping* [4, 24], which will not be discussed in this thesis.

#### 24 2. Radiation tolerant semiconductor devices and integrated circuits

The positive oxide charge lowers the threshold voltage  $V_T$  in n-channel transistors, since it attracts more electrons to form the silicon inversion. In p-channel transistors the threshold voltage absolute value is increased, or, in other words,  $V_T$  is more negative.

Radiation induced traps at the Si–SiO<sub>2</sub> interface

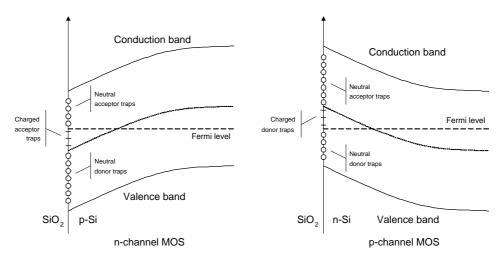

Ionizing radiation also induces the creation of interface traps. These traps have an energy laying in the silicon energy gap. Experiments indicate that the major part of the traps present above midgap are acceptors, while traps below are donors<sup>7</sup> [29, 1]. Filling those states gives rise to a interface trapped charge  $Q_{it}$ .

For this reason, in both p- and n-channel MOS transistors, the threshold increases (in absolute value), after irradiation, due to the creation of new interface traps<sup>8</sup>. Again, radiation induced trap generation is strongly dependent on the processing steps of MOS devices. Thus one of the fundamental steps for the fabrication of radiation hardened devices is the control of the gate oxide quality.

Figure 2.3: Band diagram showing the behavior of interface states for an n-channel and a p-channel transistors. The gate bias is positive for the n-channel while negative for the p-channel.

<sup>&</sup>lt;sup>7</sup>A donor trap releases an electron when it passes from below to above the Fermi level. Donor traps are neutral when full and positively charged when empty. An acceptor trap captures an electron when it passes from above to below the Fermi level. Acceptor traps are neutral when empty, negatively charged when full.

<sup>&</sup>lt;sup>8</sup>Considering an n-channel MOS transistor working in inversion, the acceptor traps in the upper part of the gap, being below the Fermi level, will be filled by electrons and then negatively charged, making necessary an higher gate voltage to have the same channel inversion.

#### 2.2 Radiation effects

The two phenomena described above cause the threshold voltage to vary with irradiation. While p-channel transistor experience only an increase of  $V_T$ , in n-channel transistors it can decrease, increase, or even be stable, depending of which is the major effect between the positive oxide charge and interface traps. Moreover the  $Q_{ox}$  is influenced by the thickness of the oxide an the dose rate: in oxides thinner than 7 nm, at low dose rates,  $Q_{ox}$ is in general negligible in respect to  $Q_{it}$ .

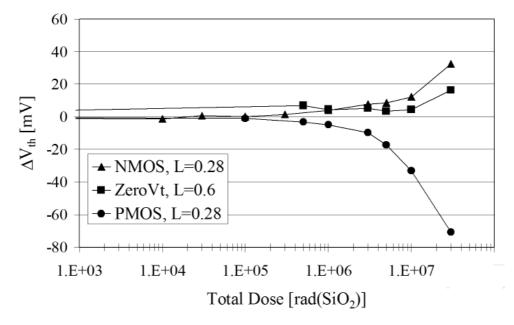

Thus, in modern technologies, like 0.25  $\mu$ m and below, where the gate oxide is thin, the threshold voltage shows only an increase with irradiation [1], while in the past technologies it had more complex behavior related to the balance between  $Q_{it}$  and  $Q_{ox}$ . The absolute value  $V_T$  increase, as Figure 2.4 shows for a 0.25  $\mu$ m technology, is anyway less than 80 mV after 30 Mrad irradiation.

Figure 2.4: Threshold voltage shift of enclosed NMOS, enclosed Zero-V<sub>T</sub> NMOS, and normal PMOS transistors in 0.25  $\mu$ m technology as a function of the total dose [10].

In MOS devices, a thick oxide is used to isolate between different devices and, within the same device, between the source and the drain [21]. Usually the first is referred to as field oxide, while the second as lateral oxide. In many technologies these oxides are made in the same process step, like, for example, the LOCal Oxidation of Silicon (LOCOS). In deep submicron Leakage current increase

Threshold voltage shift

25

processes, the thick oxide is often made with the Shallow Trench Isolation (STI) technique, that guarantees a better quality than the LOCOS.

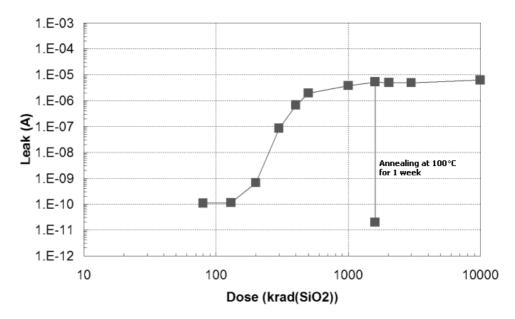

Since the lateral oxide is much thicker than the gate oxide, it suffers more of radiation-induced positive trapped charge. This can form a parasitic path near the gate's sides connecting the drain to the source, increasing, in practice, the leakage current. As mentioned before, positive  $Q_{ox}$  lowers the threshold only in n-channel transistors, thus only in those transistors a postirradiation leakage current is observed. In a 0.25  $\mu$ m technology this current can grow up to the order of 1  $\mu$ A after 10 Mrad irradiation, an unsuitable value for the fabrication of any chip! As Figure 2.5 shows, this technology can be used without any special layout technique up to 200 krad, but not

Figure 2.5: Leakage current for normal devices in 0.25  $\mu$ m technology. The measurement was taken with  $V_{DS} = V_{DD}$ . [2].

### 2.2.3 Single Event Effects (SEE)

Single event effects are phenomena generated by one single highly energetic particle passing through a device.

Single Event Latch-up (SEL)

Latch-up is a destructive effect which can occur because of the parasitic thyristor formed by the complex junction structure built in every CMOS IC. This phenomenon is usually avoided with process and layout techniques, like for example placing well contacts very close to the devices' source. Even though, it can happen that a ionizing energetic particle passing through the device deposits charge inside the parasitic thyristor, causing it to turn on. This effect is called "single event latch-up" (SEL). Its importance is limited in deep-submicron technologies since the presence of trench isolation between wells deteriorates the parasitic thyristor.

Figure 2.6: Cross-section of a CMOS inverter showing the parasitic thyristor (left) and its circuit (right).

Ionizing particles can also change the state of a circuit node and cause false information to be stored inside: this phenomenon is called "single event upset" (SEU). Unlike many other radiation-induced effects, SEU sensitivity increases with the scaling down of VLSI technologies: in fact, the minimum charge collection needed to generate the upset is proportional to the node capacitance and the supply voltage. From the circuit level point of view, dynamic logic is more sensible to SEU than static logic. SEU are dangerous in registers and memories, where the data content can be unrecoverably changed. Data redundancy is therefore needed in radiation environment applications.

Studies on SEU sensibility of D flip-flops [11], made in the 0.25  $\mu$ m technology in use at CERN, have demonstrated that, under the CMS outer tracker's conditions, the expected average SEU rate ranges between  $2.5 \cdot 10^{-11} - 9.5 \cdot 10^{-11}$  errors/(cell  $\cdot$  s). The preshower's corresponding values are very close to the outer tracker ones, since these two sub-detectors are adjacent.

# 2.3 Hardening against radiation

The choice of using a deep submicron technology guarantees itself a radiation hardened gate oxide. What is therefore necessary is to solve the problems related to the n-channel devices' field and lateral oxide degradation after irradiation. Single Event Upset (SEU)

#### 2.3.1 Layout techniques

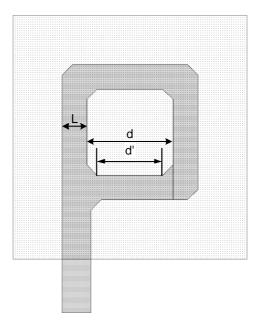

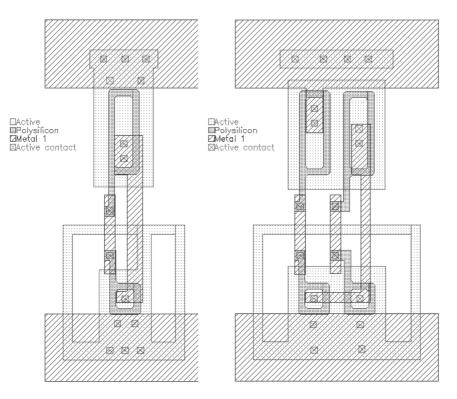

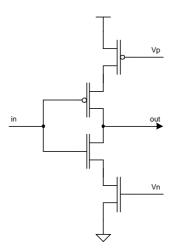

Enclosed Layout Transistors (ELTs) The primary problem which has to be addressed is the leakage current inside n-channel devices. The solution adopted in CERN's microelectronics group is to use "enclosed layout transistors" (ELTs, also called edgeless). As shown in Figure 2.7, in this case the parasitic path between the source and the drain is eliminated, as well as the lateral oxide.

Figure 2.7: Enclosed Layout Transistor. The drain is conventionally in the center while the source is outside the circular gate.

The major disadvantages of this layout style are larger area and increase in capacitances. Moreover, the choice on the W/L ratio is limited, since W has to be enough big to allow the inner active contact to be placed.

ELTs have been used in the early days of CMOS [9] and their effectiveness in preventing leakage currents in irradiated integrated circuits is well known. Their intensive use in CERN's applications lead to the investigation of many issues important for a designer, such as modelling the effective W/L ratio<sup>9</sup>. There is a wide range of possible enclosed shapes: squared,

$$\left(\frac{W}{L}\right)_{eff} = 4\frac{2\alpha}{\ln\frac{d'}{d'-2\alpha L_{eff}}} + 2K\frac{1-\alpha}{1.13\cdot\ln\frac{1}{\alpha}} + 3\frac{\frac{d-d'}{2}}{L_{eff}}$$

where  $\alpha$  is constant usually set to 0.05, while K = 7/2 for short channel transistors  $(L \leq 0.5 \ \mu \text{m})$ , otherwise K = 4. To derive this expression, the enclosed transistor is

$<sup>^{9}</sup>$ As described in [12], the model for the effective W/L of enclosed transistor, if applied to the shape in Figure 2.7, leads to the following expression for the aspect ratio:

octagonal, squared with corners cut at 45 degrees and all of them can have a different behavior and require a separate model. To simplify the problem, one specific shape was chosen, compatible with the design rules of the process: square with corners cut at 45 degrees so that the size of the cut is constant for all the gate lengths (see Figure 2.7).

The second problem which can be solved with a layout technique is the leakage between different devices [1]. This is done surrounding each nchannel device with a p+ guard ring. This method has been verified to be very effective but the drawback is again the big consumed area. Moreover, guard rings avoid the generation of SEL by lowering the gain of the parasitic NPN bipolar transistor.

#### 2.3.2 Circuit and system techniques

While designing circuits for radiation environment applications, one must take into account and foresee the drift of the circuit's operating point due to absorbed total dose. For digital circuits, the synchronous mode of operation limits the sensitivity to electrical parameters' variation [1].

SEU tolerance has also to be implemented at this level of hierarchy: as mentioned before, static logic is indeed less sensible to SEU, but its use is not enough to guarantee immunity. In fact, SRAM and flip-flop contents can be changed and have to be protected if crucial for the application.

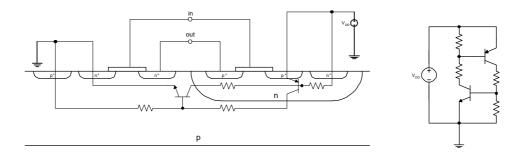

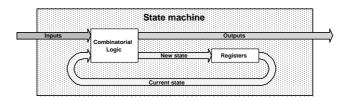

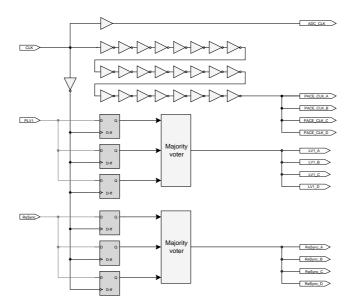

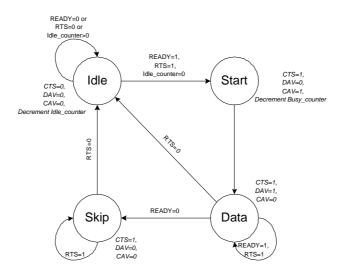

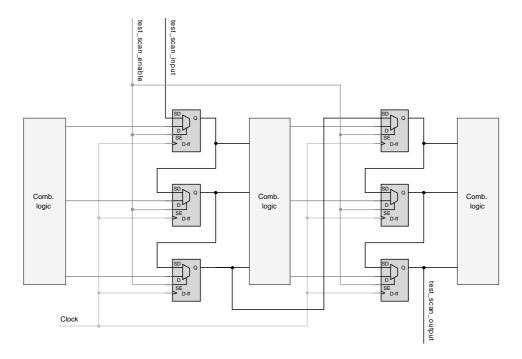

Of course data redundancy is more important in state machines, where a wrong stored information can be very harmful, than in data paths. An error in a control logic state machine can damage the whole system behavior, while in data paths it is usually confined to the corrupted data segment. For this reason, state machines are *triplicated* in radiation environment applications, and therefore in this work.

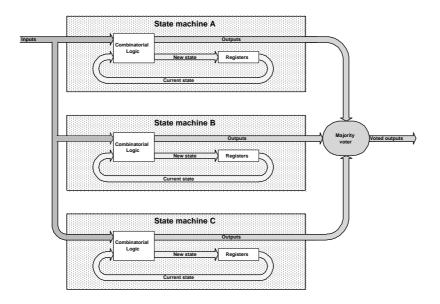

Triplication can be done in a few ways. Three of them are shown in Figures 2.9, 2.10, 2.11, while Figure 2.8 resembles a standard state machine.

State machines are usually composed by a combinatorial logic block and a set of flip-flops or registers. The more general case of Mealy state machine only will be analyzed, since Moore machines are a subset of the others<sup>10</sup>. These memory devices store the current state vector, while the logic evaluates the next clock cycle's state and the outputs. Guard rings

Synchronous operation

Static logic & data redundancy

> State machines triplication

decomposed into three parts. The first corresponds to the linear edges of the transistor, the second to the corners without the 45 degrees cut, which then is taken into account in the third part. It can be shown that the minimum reachable aspect ratio is around 2.26 with this geometry.

<sup>&</sup>lt;sup>10</sup>In Moore state machines the output depends only on the state vector. In Mealy machines the output depends on the state vector and on the input vector.

Figure 2.8: Standard state machine.

In triplicated state machines a new block is necessary: a so called "majority voter", purely combinatorial. In our case, it has three inputs and one output which is 1 if at least two of the inputs are 1, while it is 0 if at least two of the inputs are 0. The voter's output is never undefined, as can be seen from the truth table in Table 2.2.

| I2 | I1 | IO | Out |

|----|----|----|-----|

| 0  | 0  | 0  | 0   |

| 0  | 0  | 1  | 0   |

| 0  | 1  | 0  | 0   |

| 0  | 1  | 1  | 1   |

| 1  | 0  | 0  | 0   |

| 1  | 0  | 1  | 1   |

| 1  | 1  | 0  | 1   |

| 1  | 1  | 1  | 1   |

Table 2.2: 3-Input majority voter truth table.

Since a state machine is repeated three times, one or more majority voters take care of deciding the right state and output when a disagreement takes place. In principle, the three machines could run independently with a voter connected to their output, as shown in 2.9.

This configuration is not suitable for application requiring a long operation time without reset: after a SEU occurred in one of the state machines, a second SEU in another machine will make the output to be wrong. This can be avoided if the state machines evaluate the voted state instead of their own stored state.

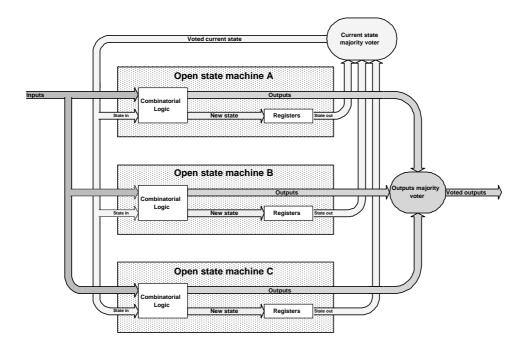

In order to do that, the stored state loop back to the combinatorial logic has to be broken in each state machine, creating an *open state machine* with state vector input and output. Then, the voter must be placed to connect them: three registers will drive the voter, which will decide the correct current state and send it to the combinatorial parts. Figure 2.10 shows the simplest triplication scheme with feedback of the voted state.

A problem arises from this second approach: a SEU on the voter output

Figure 2.9: Triplicated state machine with no feedback.

Figure 2.10: Triplicated state machine with shared feedback.

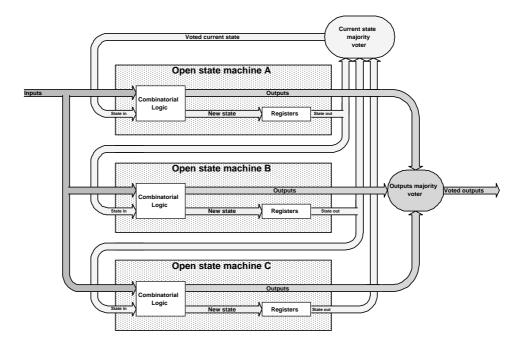

could cause a bad state vector to be loaded in all the three machines at the same time! Even if this is very unlikely, to resolve it, one can let the voted state vector feedback to be given only to the first state machine, and then make it propagate down to the other two in the next 2 clock cycles. Figure 2.11 shows this new solution.

Figure 2.11: Triplicated state machine with state propagation.

As can be seen, the second state machine's input state vector is the previous machine's output state vector, and the same happens for the third machine. If no more than one SEU occur within three clock cycles, an eventual bad state vector will propagate through the state machine chain and die in the last one, while the correct state vector will always be restored in the first.

This last one is the solution adopted in this work during the design of all the state machines.

Clock nets' SEU

An especially harmful kind of SEU can happen on the clock nets. In that case two false digital signal transitions are inserted where they shouldn't be. Flip-flops connected to that net will sample the input data in the wrong moment, corrupting their content. Anyway clock nets have usually a large capacitance and a powerful driver connected, thus they are intrinsically immune to SEUs.

# 2.4 A radiation tolerant digital standard cells library

In order to help in the design of complex digital ICs, a digital library has been designed and tested in a 0.25  $\mu$ m technology [23, 19], while a new library in 0.13  $\mu$ m technology is under development. Both these two libraries exploit radiation hardening techniques.

#### **2.4.1** The CMOS $0.25\mu m$ library

The basic features of the technology are given in Table 2.3.

Figure 2.12: Inverter gate (left) and 2-input NOR gate (right).

The standard cells are designed to be abutted one to the other in horizontal rows. Figure 2.12 shows two library cells.

The power rails are routed in the first metal layer horizontally all along the rows; great effort was spent to keep intracell interconnections on the first metal layer, leaving the rest of the metal layers for global routing. For that purpose the salicided polysilicon layer was used as a local intracell interconnect, but since polysilicon cannot be allowed to cross the guardrings, this layer was used only for horizontal routing.

| Minimum lithography  | 0.24 μm                                       |

|----------------------|-----------------------------------------------|

| $L_{eff}$            | $0.18 \ \mu \mathrm{m}$                       |

| V <sub>DD</sub>      | 2.5 V                                         |

| Gate oxide thickness | 5.0 nm                                        |

| Process              | Twin well CMOS                                |

| Device isolation     | Shallow trench (STI)                          |

| Ti salicidation      | On $n^+$ and $p^+$ polysilicon and diffusions |

| Interconnectivity    | 2 to 5 metal layers                           |

Table 2.3: 0.25  $\mu$ m technology features.

The area penalty paid for ELT style and the guardrings is anyway mitigated by the small feature size of the technology: the only alternative to this approach would be to use process radiation hardened technologies which offer overall a much smaller device density.

The library contains combinatorial logic gates, like NANDs and NORs, as well as flip-flops and latches. A set of I/O pads is also available.

# Chapter 3 The Kchip

The primary objective of this thesis has been to develop a digital radiationtolerant ASIC for data readout from the CMS preshower, which is called the "Kchip". In the introduction, the goal and the basic concepts of the CMS preshower have been explained. In the next sections the electronic equipment concerning the preshower front-end (FE) system will be described with more detail. Later in this chapter the design requirements needed, the techniques employed and the internal operation of the Kchip will be exposed.

## 3.1 The CMS preshower front-end system

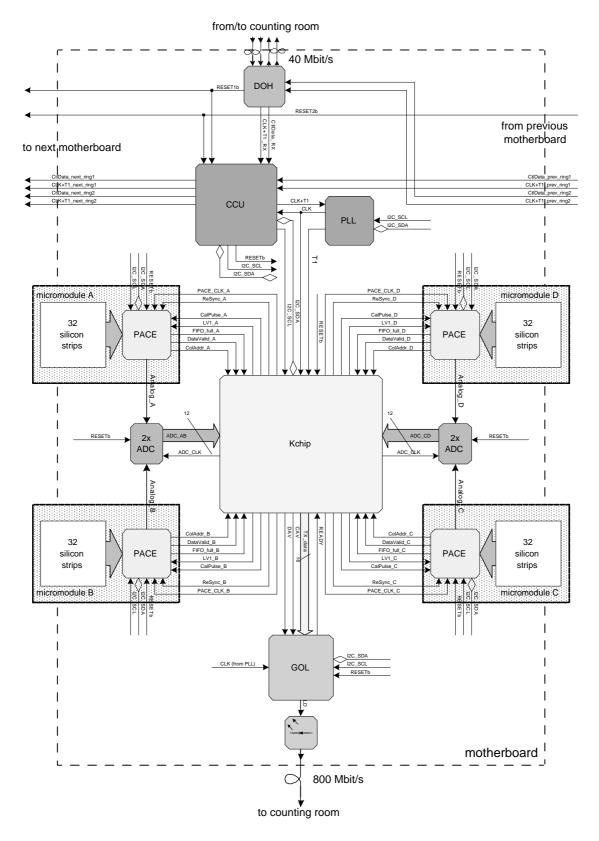

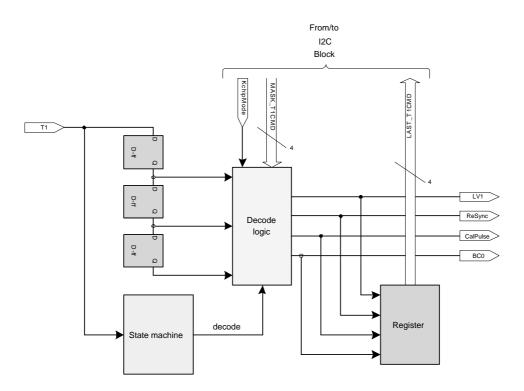

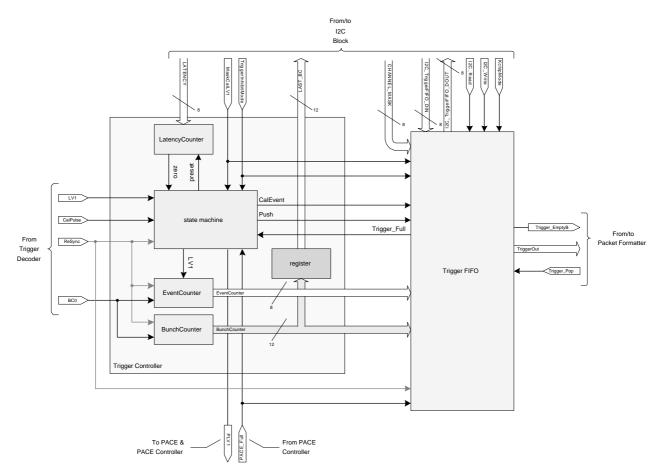

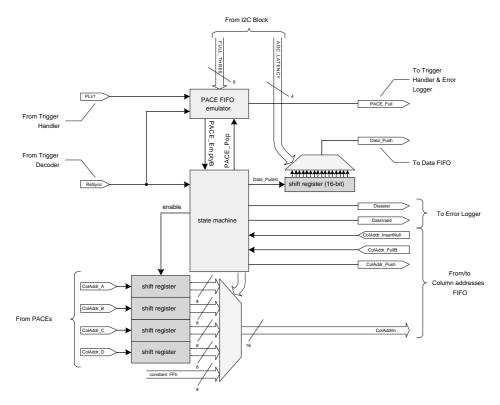

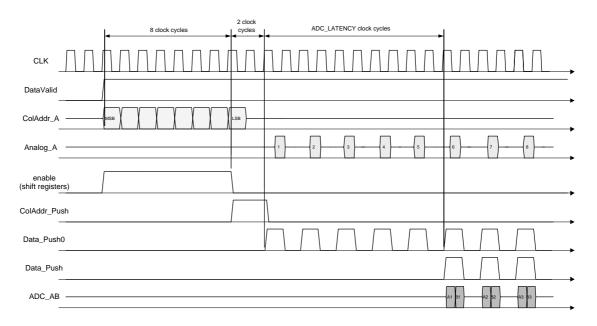

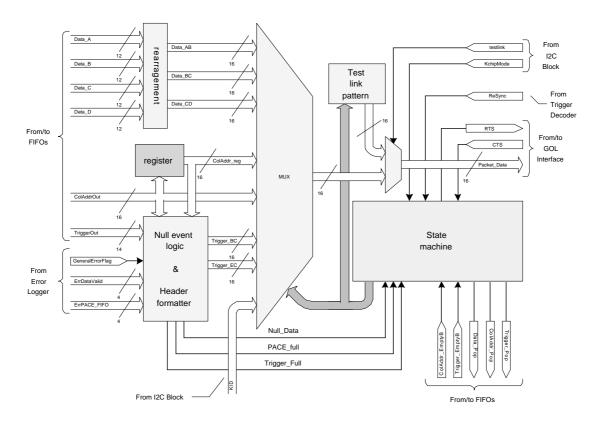

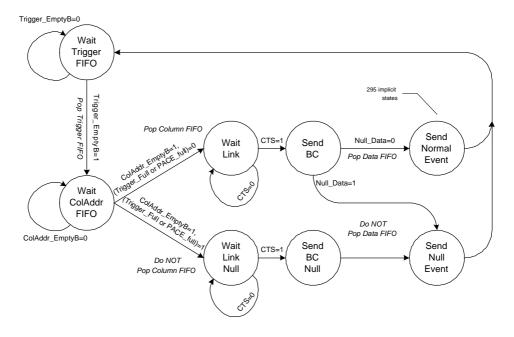

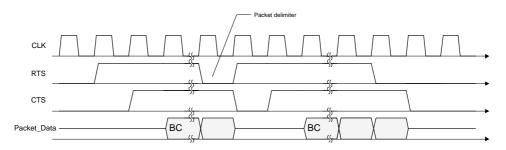

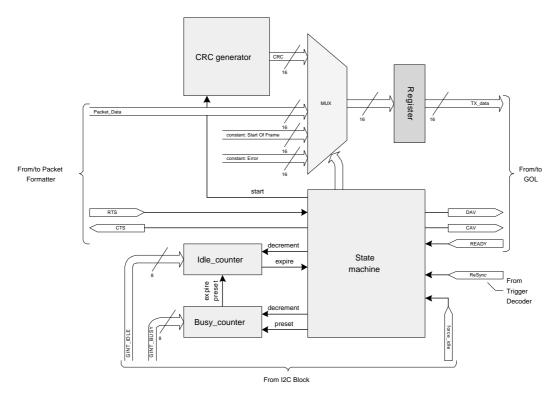

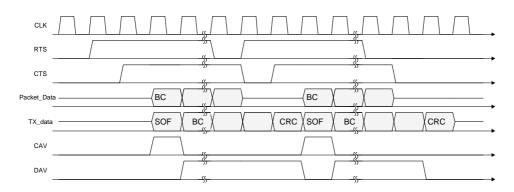

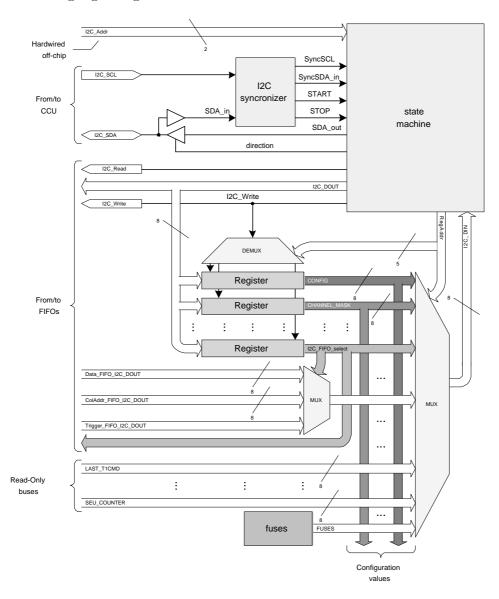

The front-end readout system [18] is composed by a few units, cascaded one to the other, which, following the data path from the source to the outgoing optical fiber, are (see Figure 3.1):

- The silicon strips detector;

- The PACE chipset, composed by a charge-sensitive amplifier and a pipeline analog memory;

- The analog-to-digital converter (ADC);

- The Kchip;

- The Gigabit Optical Link (GOL) chip, which is a high-speed data serializer and laser driver;

- The light emitting diode laser;

A detector, together with a PACE chipset and a Detector Control Unit (DCU), form a micromodule (see the Introduction). Up to 10 micromodules are then connected to one motherboard made out of an ADC stage, a number of Kchips, one GOL and one laser diode per Kchip, plus some control logic. In practice every Kchip can read the data coming from up to four detectors.

The 800 Mbit/s optical fiber goes then into what is called the *counting* room, where event building and Level-1 trigger evaluation take place. Two pairs of optical fibers are also connected to a motherboard for slow control signaling and clock distribution. All the communication between the motherboard and the counting room are implemented with optical fibers, while with wires among the motherboards.

#### 3.1.1 The control logic

The control logic comprises the Communication and Control Unit module (CCU), the Phase Locked Loop (PLL) and other smaller components like the Digital Optical Hybrid (DOH).

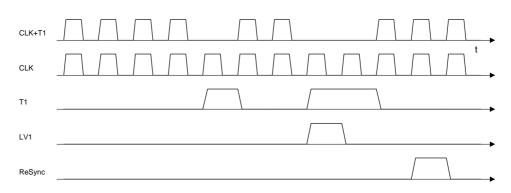

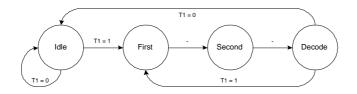

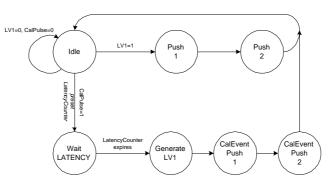

The PLL device takes care of receiving and extracting the 40.08 MHz LHC clock signal (CLK), which comes from the counting room through an optical fiber token ring, and distributing it to the rest of the motherboard. It also performs clock jitter reduction and programmable deskewing with steps of 1.04 ns. Along with the clock, the Level-1 trigger is transmitted, coded in missing pulses, and the PLL provides its extraction. Figure 3.2 shows the Level-1 trigger T1 decoding. In addition, the trigger channel carries other coded information. All these signals are referred as *fast timing control signals* and will be clarified later.

The DOH is responsible of the electrical to optical (and viceversa) translation. Fast switching electrical signals are often implemented in Low Voltage Differential Signaling (LVDS) standard<sup>1</sup>, a current-steering mechanism which provides low power and very low noise necessary for the FE analog parts.

A primary and a secondary token ring are both available for slow control bidirectional communication. A DOH is mounted on each one of the two master motherboards, each one serving one token ring. The token ring involves up to 12 motherboards. Having two rings provides redundancy for fault tolerance: the networks are doubled and cabled in such a way that, if any motherboard fails, there will still be a path to reach the other ones.

The two DOHs in particular take care of generating the asynchronous reset signals (RESET1b and RESET2b): when no light is observed in the control data fiber a reset is issued. The two low-active signals are the OR-ed inside the CCU module to obtain a single RESETb.

The 40 Mbit/s fiber channel token rings are connected to the CCU, that provides slave control of the connection. In this way, the various circuits in the front-end can be accessed through this component, by a set of 16 lines

36

The PLL

token rings

The DOH  $\mathfrak{G}$  the

The CCU

<sup>&</sup>lt;sup>1</sup>ANSI/TIA/EIA-644(LVDS)

Figure 3.1: Simplified master motherboard schematic showing the preshower FE system architecture.

Figure 3.2: Level-1 trigger decoding from the clock signal and example of fast timing control signals derived.

of  $I^2C$  interface, which is a standard serial communication protocol created by Philips. The FE system is then capable to be programmed and verified from the outside.

The DCU

The DCU (not shown in the schematic) is dedicated to the measurement of environmental parameters of the system (temperatures, voltages, leakage currents and so on).

#### 3.1.2 Fast timing control signals

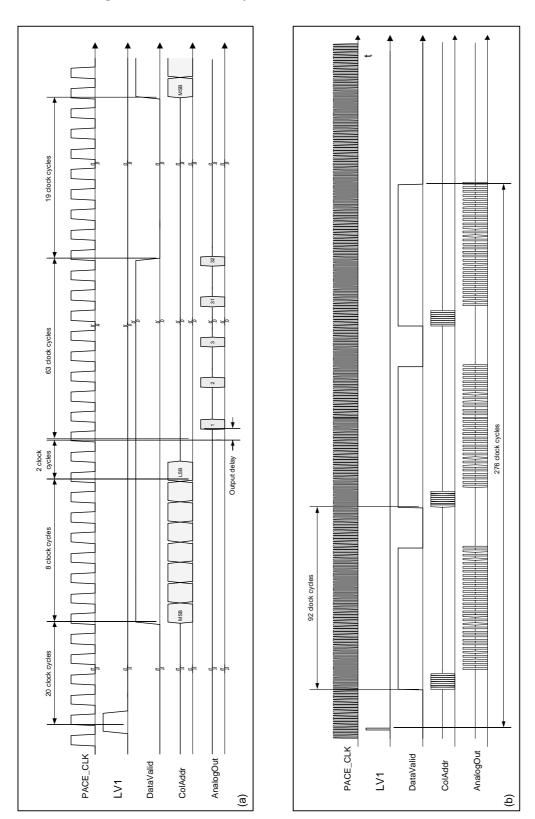

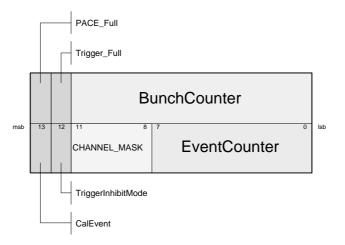

Inside the Level-1 trigger (T1) four possible commands are coded. These commands are represented, in the T1 stream, by a triplet of bits beginning with 1. Table 3.1 shows the four possible commands. Back-to-back commands are allowed in this scheme.

| T1 Pattern | Command  | Description                   |

|------------|----------|-------------------------------|

| 100        | LV1      | Readout request               |

| 111        | CalPulse | Calibration request           |

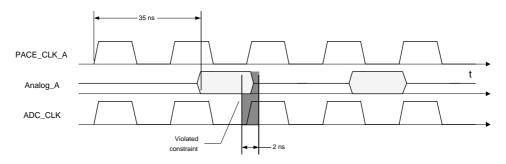

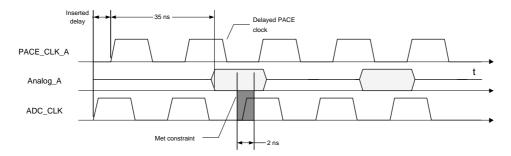

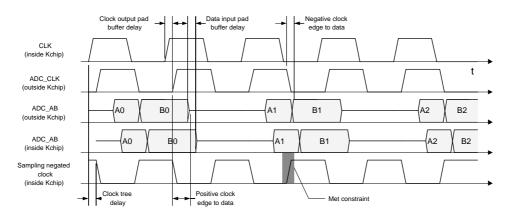

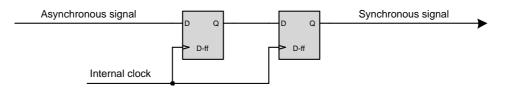

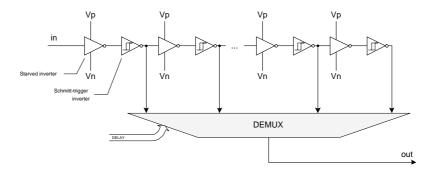

| 110        | ReSync   | Resynchronization request     |