INDET-135 SCIPP 96/12 March 1996

# Beam Test of the Binary Silicon System in H8 in September 1995

J. DeWitt, D. E. Dorfan, T. Dubbs, A. A. Grillo, S. Kashigin, W. Kroeger,

T. Pulliam, J. Rahn, W. A. Rowe, H. F.-W. Sadrozinski , A. Seiden,

E. Spencer, A. Webster, R. Wichmann, M. Wilder, D. Williams SCIPP, Univ. of California, Santa Cruz, CA, USA

> J. Dane, A. Lankford, S. Pier, B. Schmid Univ. of California, Irvine, CA, USA

R. Bonino, C. Couyoumtzelis, P. Demierre Univ. of Geneva, Geneva, Switzerland

> Y. Iwata, T. Ohsugi Hiroshima Univ., Hiroshima, Japan

H. Iwasaki, T. Kondo, S. Terada, Y. Unno *KEK, Tsukuba, Japan*

> W. Dabrowski, M. Idzik IPNT, Krakow, Poland

J. Godlewski INP, Krakow, Poland

R. Takashima Kyoto Univ. of Education, Kyoto, Japan

A. Ciocio, T. Collins, J. Emes, M.G.D. Gilchriese, C. Haber , I. Kipnis, M. Shapiro, J. Siegrist, H. Spieler

Lawrence Berkeley National Laboratory, Berkeley, CA, USA

> N. Tamura Okayama Univ. , Okayama, Japan

A. Grewal, R. Nickerson, R. Wastie Oxford Univ. , Oxford, UK

Y. Gao, S. Gonzalez, A M. Walsh, Z. Feng Univ. of Wisconsin,, Madison, WI, USA

## ABSTRACT

We report results from a beam test of the binary silicon strip system for ATLAS. The data were collected during the H8 beam test at CERN in August/September 1995. The binary modules tested had been assembled from silicon micro strip detectors of different layout and from front-end electronics chips of different architecture. The efficiency, noise occupancy and position resolution were determined as a function of the threshold setting for various bias voltages and angles of incidence. In particular, the high spatial resolution of the track location in-between detector strips.

### INTRODUCTION

We are proposing to simplify the readout of silicon detectors in the Semiconductor Tracking Detector (SCT) [1] of ATLAS [2] by using a binary readout [3], which records only the addresses of strips with pulse height exceeding a fixed threshold value. Thus the pulse height will not be available directly during data taking. We have shown that the distribution of pulse heights can be recovered by varying the threshold and measuring the counting rate, which is the integral of the pulse height spectrum. Likewise, the noise can be determined from threshold scans without beams. It is important to note that the primary parameters of interest for a tracking device are not the signal and noise, but the single channel efficiency the position resolution, and the noise occupancy.

In the following, we report results from the 1995 ATLAS beam test in the H8 beam line in the CERN North Area. Previous beam tests at KEK [4,5] have shown low noise occupancy at the nominal threshold of 1fC and good efficiency even at higher thresholds. In H8, the use of the beam telescope with a resolution of a few microns allowed the investigation of the efficiency at a fine scale as a function of the inter strip location.

#### BEAM SET-UP

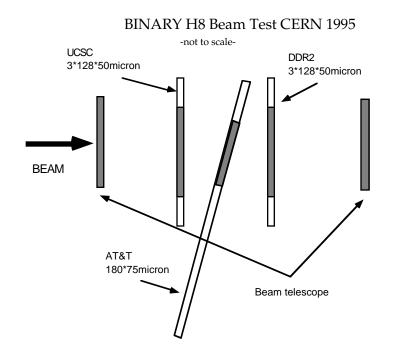

During the 1995 ATLAS beam test in the CERN H8 beam line [6], several silicon micro strip modules with binary readout were tested. Fig. 1 shows the schematic of the set-up during the September run: the x-y beam telescopes bracketed the binary modules, and allowed the location of tracks within the modules to 2-3micron in the horizontal and vertical directions. Two of the binary modules, called UCSC and DDR2, were held fixed, while the central one, called AT&T, was mounted on a rotary stage and could be rotated about an axis parallel to the strips. The distance between the x-y hodoscope planes was about 80cm, and between the binary modules of the order 5cm, respectively.

Fig. 1 Set-up of the binary H8 beam test in September 1995. The shading areas indicate the active regions.

Table 1 lists the detector modules used in the September beam test. All modules are so-called "r- $\phi$ " modules, where the detector strips are directly bonded to the FEE. In addition, the hybrid, which carries the FEE and the data and control signals, is mounted across the detector strips in the approximate center of the 12cm silicon detector module.

The modules combined SSC-style and newly developed LHC-style detectors with different front-end electronics (FEE). Two bipolar amplifier-comparator chips with peaking time of close to 20ns were used. The LBIC [8] was developed for AC-coupled SSC detectors, while the CAFE [9] chip is designed for operation with finite input current for use with ATLAS DC-coupled detectors. Unfortunately the production run with AT&T yielded too few chips to instrument the full complement of modules. Two CMOS digital pipelines were used, the CDP128 [10] a clock-driven binary pipeline and the DDR2 [11] a data-driven binary pipeline with data compression and a data transmission protocol similar to the ATLAS protocol. Neither of the binary pipelines is edge sensing as required in the baseline design. Thus they sample the output width of the comparator chips, which is 2.5 clock cycles of 25ns for the DDR2 and AT&T3 modules and 0.6 clock cycles for the UCSC module. In order to assess the occupancies properly, they will be scaled in the following by the number of time slices the binary pipeline is "live".

The silicon detectors tested were AC-coupled double-sided detectors with 50µ pitch developed in Japan for the SSC [12] and DC-coupled ATLAS-type 75µ pitch detectors fabricated at LBNL [13]. Both Kapton flex-circuit and ceramic hybrids were successfully used, although the yield of Kapton circuits turned out to be extremely low.

| Tested Module | Hybrid  | Detector |       | Pitch | Length   | # of | Amp Chi | p Pipe Line |        |

|---------------|---------|----------|-------|-------|----------|------|---------|-------------|--------|

|               |         | [side    | ə,typ | e,AC] | [micron] | [cm] | strips  |             |        |

| UCSC          | Kapton  | n        | n     | AC    | 50       | 6,12 | 384     | LBIC        | CDP128 |

| DDR2          | Kapton  | р        | n     | AC    | 50       | 6    | 384     | LBIC        | DDR2   |

| AT&T3         | Ceramic | n        | р     | DC    | 75       | 12   | 180     | CAFE        | CDP128 |

The read-out was newly developed for this test and is based on Digital Signal Processors (DSP's) utilizing a 40MHz clock. They were designed to allow a data rate of several kHz, but the data acquisition rate was limited by the readout speed of the telescope to about 100 counts per spill.

In addition to rotation scans, two parameters were varied to map out the performance of the detectors: the detector bias voltage and the threshold of the on-chip comparators. The results from the threshold scans are used to determine the pulse height. The data at different rotation angles help to understand the effects of a finite track crossing angle.

## OCCUPANCY

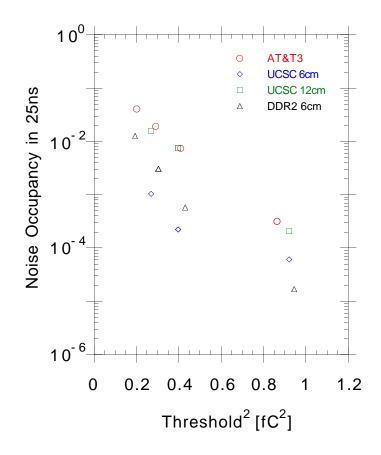

Both the on-beam occupancy and the off-line noise occupancy were measured to verify that the modules were working as designed. The noise occupancy was measured as a function of the threshold voltage to determine the noise sigma's. This was done before and after the run using the full DAQ. Channels which were obviously noisy were removed from the data. 'The occupancy per channel as a function of threshold squared is shown in Fig. 2. The data have been corrected for the number of effective time slices of the 40MHz clock the comparator output level is sensed by the pipe-line, as explained above.

Fig. 2 Noise occupancy of the modules as a function of the threshold

The occupancies are approximate gaussian functions of the threshold voltage [14,15]. The slope is a measure of the noise sigma. We observe the expected dependence of the noise on the strip length (12cm vs 6cm). Table 2 shows the noise occupancies extrapolated to a threshold setting of 1fC.

| Table 2: Noise Occupant | cy at 1fC Threshold for one 40MHz Time Slice |

|-------------------------|----------------------------------------------|

|-------------------------|----------------------------------------------|

| Module     | Noise sigma [ e <sup>-</sup> ] | Occupancy @ 1fC |

|------------|--------------------------------|-----------------|

| AT&T3      | 1640                           | 0.8*10-4        |

| UCSC, 12cm | 1706                           | $1.5*10^{-4}$   |

It should be pointed out that the CAFE amplifier chips were operate on their lowest power setting which results in relatively higher noise levels. Even then the extrapolated noise occupancy at 1fC threshold is of the below 10<sup>-4</sup>.

The on-beam occupancy was determined with the help of a tracking program simultaneously with the efficiency and will be discussed below.

# DATA ANALYSIS

# a) Event selection

Events were filtered from the DST into a 'mini-DST' by requiring one and only one track reconstructed in each event. For the analysis of a particular module, the projected telescope track was required to be in the fiducial region, defined as:

- \* the track impact point was not allowed to fall on a dead strip;

- the track impact point was required to be at least 15 strips away from edge in the x-coordinate (the axis perpendicular to the strips);

- \* the track impact point was required to be approx. 1 mm away from the edge in the y-coordinate, i.e. along the strips.

In addition to the above requirements, only events with a telescope track  $\chi^2$  value of less than 30 were kept.

# b) Clustering

Before the clustering was done, the module readout order was fixed so that strip numbers are sequential. This fix basically consists of the swapping of even and odd strip numbers. Then clusters were constructed in the following way:

- \* a cluster seed was started up to +- 2 strips away from the track impact point;

- \* searches on the left and the right side of the impact point were done independently for hit strips;

- \* the search stopped when no more hit strips are found;

- \* all contiguous hits were then clustered.

The cluster position was then taken to be the average strip position for the strips in the cluster. In order to reduce biases in the clustering introduced by noisy or dead channels, events were further rejected if:

- \* a found cluster contained a hit on a strip flagged as 'noisy';

- \* the closest dead strip was less than 2 strips away from the expected hit strip.

Clusters and events that passed all the above requirements were then labeled 'good' clusters and 'good' events and were used in the efficiency and resolution measurements.

### c) TDC Cuts

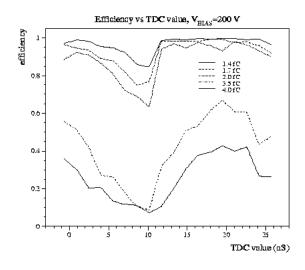

The trigger from scintillation counters was synchronized with the 40MHz readout clock and initiated the read-out of the pipelined data. The phase of the trigger and thus the arrival of the particles in the silicon detectors relative to the clock was determined by a TDC with 200ps resolution. At LHC, the data will arrive with a fixed phase relative to the clock; in H8, the arrival was spread over 25ns and the efficiency as a function of the TDC value had to be determined. We expect variations of the efficiency with the clock phase for the LBIC chip, which was designed for p-side detectors and has a very narrow pulse width for n-side detectors (UCSC module). Due to time walk in the comparator, the TDC distribution depends on the threshold, as shown in Fig. 3 for the UCSC module.

Fig. 3 Efficiency of the UCSC module as a function of the time difference between the trigger and the clock edge. The efficiencies for 1fC and 1.2 fC thresholds are constant and unity.

The data is independent of the TDC value for TDC(UCSC) > 15ns. Likewise for the DDR2 module, the time cut TDC(DDR2) <10.5ns was applied. For the AT&T3 modules which uses an amplifier-comparator chip with a more advanced design, no TDC cut was necessary. Missing or corrupted TDC information was an indication of DAQ problems and caused data runs to be excluded from analysis.

In the following we discuss a few selected results from the data analysis of the different modules.

#### RESULTS

#### a) Efficiency as a Function of Inter strip Position -DDR2-

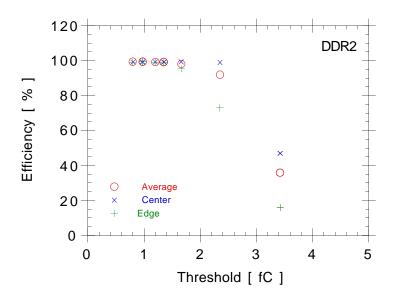

The efficiency for the p-side detector read out with the DDR2 chip is shown in Fig. 4. The efficiency is above 99% even at a threshold 40% higher than the nominal 1fC. It is 50% at close to 3.5fC, the median of the binary Landau distribution.

Fig. 4 Efficiency for the DDR2 module as a function of the threshold.

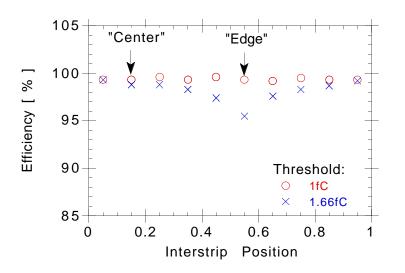

Further insight into the detector performance is gained from the dependence of the efficiency on the inter-strip position of the track. Fig. 5 shows the efficiency as a function of the extrapolated track position between two strips, in fractions of the pitch. The efficiency is shown for two thresholds, 1fC and 1.66fC.

As expected, the efficiency starts to degrade in between the strips first, where the charge sharing decreases the effective pulse height detected in a single strip. In the middle between strips, the charge sharing causes higher hit multiplicities. In order to isolate the inter strip effects, we quote, in addition to the efficiencies averaged over all positions, two values for specific inter strip position, "edge", and "center" (see Fig. 5). "Edge" refers to the efficiency calculated in a 5micron wide bin at the edge of a strip, while "center" refers to the efficiency in a 5micron wide bin at the center of the strip. The values for edge and center are shown in Fig. 4 together with the average efficiency.

Fig. 5 Efficiency as a function of inter strip position for 1.0 and 1.66fC threshold.

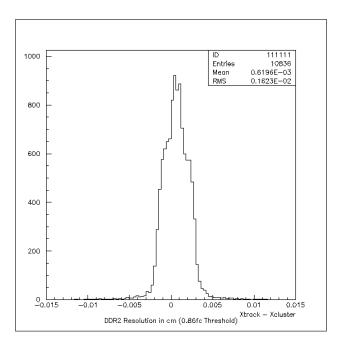

Fig. 6 shows the tracking residuals at 1fC threshold. The distribution is composed of two contributions, one from single hit tracks with a resolution of close to pitch/ $\sqrt{12}$ = 14microns and one from multi-hit clusters, with a resolution of about half that.

Fig. 6 Residuals between a hit in DDR2 and the projected track position.

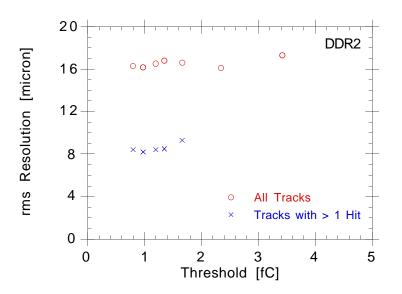

Fig. 7 shows the rms resolution for all tracks and for multiple hit tracks only. The fitted resolutions are about 20% lower than the rms values shown.

Fig. 7 Rms resolution of all tracks and multi-hit tracks.

An improvement in the resolution due to charge sharing is evident, but the usefulness of charge sharing in the binary system is limited to the edge of the strips, where the tracking program places the double-hit tracks. This is reflected in the relative population in the two peaks.

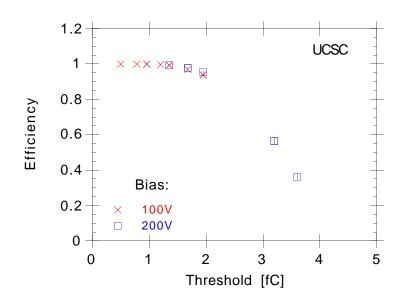

#### b) Bias Voltage Dependence of the Efficiency and Position Resolution -UCSC-

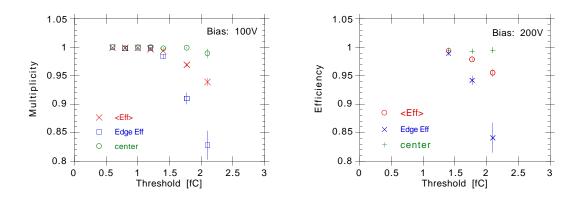

Because n-in-n detectors deplete from the backside, the collection of charge might be less efficient at lower bias voltages than at higher ones. The UCSC module depletes at about 70V. We have operated the module at 100V and 200V bias, and Fig. 8 shows the efficiency as a function of the threshold voltage at both bias voltages. The efficiency is close to unity close to the nominal threshold of 1fC and the median is at 3.5fC, as found in previous beam tests [4,5].

Fig. 8 Efficiency of the UCSC module at bias voltages of 100V and 200V.

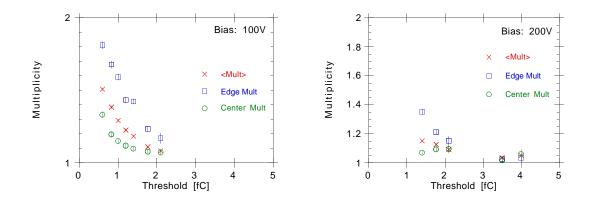

Fig. 9 shows the efficiency and Fig. 10 the hit multiplicity in clusters as a function of the threshold for 100V and 200V bias. The data is subdivided into the average, "edge" and "center" values as described above, with the difference that the width of the "edge" and "center" regions are now 20microns wide. The data of Figs. 8, 9, 10 appear to suggest no difference due to bias in the region of thresholds where the data overlap.

Fig. 9 Efficiency close to nominal threshold for the UCSC module for a) bias voltage = 100V, b) bias voltage = 200V.

Fig. 10 Hit multiplicity as a function of threshold: a) bias =100V, b) bias = 200V.

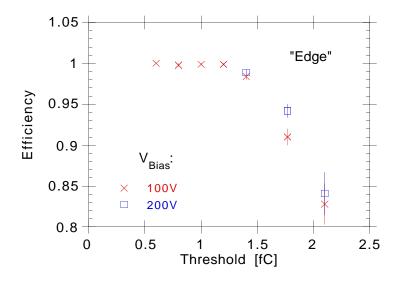

In order to investigate the effect of the bias voltage on charge sharing, we compare in Fig. 11 the efficiencies for the two bias voltages at the edge of the strips, where we would expect to be most sensitive to a more efficient charge collection at higher bias. We find that the data is virtually identical close to the nominal threshold of 1fC, and only at 1.7fC, can we observe an increase in efficiency for the larger bias voltage.

Fig. 11 Efficiency at the edge of the strip vs. threshold for two different bias voltages of the UCSC module.

### c) Efficiency Dependence on Rotation Angle - AT&T3-

The data of the AT&T3 module were taken at constant voltage but varying rotation angle. The n-on-p detector has a depletion voltage of about 140V, and was operated at close to 80V due to the large bias current, which was reaching the power supply compliance of 2mA. With the junction on the n-side, this mode of operation corresponds to an inverted n-on-n detector operated at partial depletion, which was shown to be an option for the ATLAS SCT in case of unexpectedly high radiation levels [16]. The only caveat is that in the module used, the n-implants were somewhat wider and the p-isolation narrower than in the ATLAS direct read-out design. We are planning to test inverted n-on-n detectors with optimized layout in the next beam test.

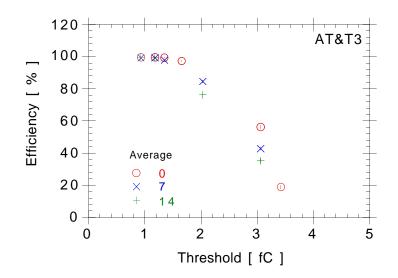

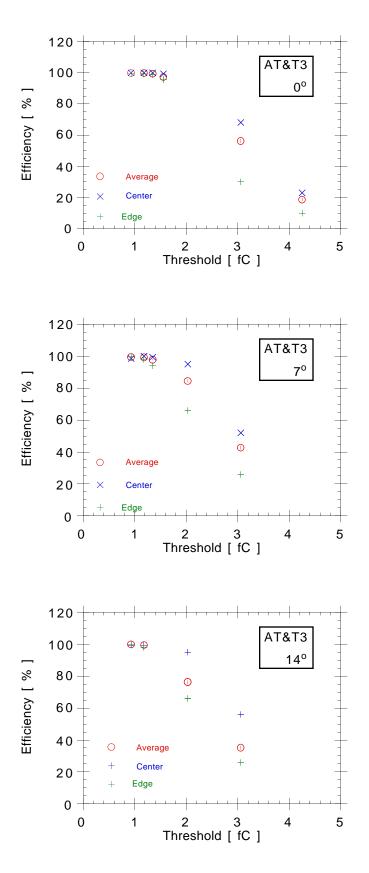

Fig. 12 shows the efficiency for the three rotation angles 0<sup>o</sup>, 7<sup>o</sup> and 14<sup>o</sup>. Due to increased sharing, the pulse height, i.e. the median of the efficiency curve, decreases going to larger angle.

Fig. 12 Efficiency for rotation angles 0° 7°, 14°

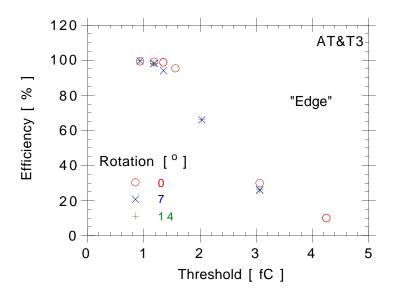

The efficiencies as a function of the threshold for the average, and the "edge" and "center" regions, (here with 7.5micron width) are shown in Fig. 13.a-c. for the three rotation angles 0°, 7°, 14° respectively. The efficiency is close to unity for thresholds below 1.2fC for all angles. Again, we show the worst case, the efficiency at the edge of the strips, in Fig. 14 for the three angles. Although the median appears now at about 2.5fC, there is good efficiency at 1fC.

Fig. 13 Efficiency for rotation angles a)  $0^{\circ}$ , b)  $7^{\circ}$ , c)14<sup>o</sup>.

In Fig. 14 we compare the efficiencies for the three angles in the "edge" region, i.e. in the middle in-between the strips. The data for 7 and 14 degrees are identical for the four common points and we observe efficiencies of 98% for 1.2fC and 94% for 1.4fC (for the 7degree data only). It will be interesting to compare this data with the efficiency of a fully depleted detector.

Fig 14 Efficiency for the "edge" region of the three rotation angles.

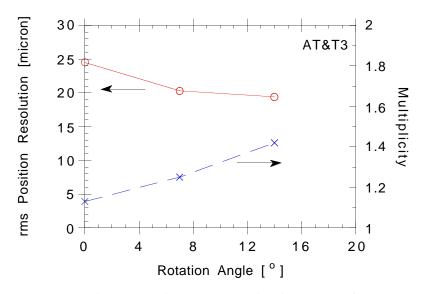

In Fig. 15 we show the average resolution and hit multiplicity as a function of the rotation angle for all events at a threshold of 1fC.

Fig. 15 Position resolution and average multiplicity as a function of angle.

The improvement in resolution with the increased rotation angle is correlated with increased hit multiplicity and thus increased charge sharing between neighboring strips.

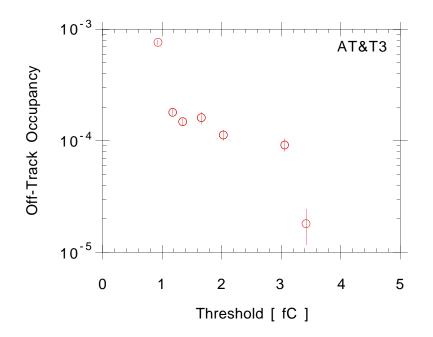

The off-track occupancy in one 25nsec time slice during beam-on time is shown in Fig. 16. It was determined from all hits in the events which were distant by more than 10 strips from the track. Note that at a threshold of .93fC, this result resembles closely the occupancy due to random noise of Fig. 2, while at larger threshold, a long tail extending to large thresholds is observed, similar to results of previous beam tests [4,5] One possible source is additional tracks not recognized by the beam telescope, which would suggest that the noise occupancy is much lower than the measured value.

Fig. 16 Occupancy of hits not associated with a track during beam time.

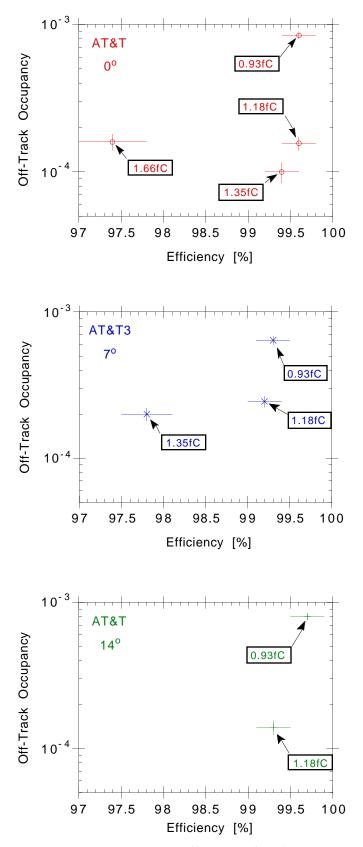

A comprehensive description of the module performance is given in Fig. 17, which displays the noise occupancy vs the efficiency for the AT&T3 module, for the three rotation angles. Each point corresponds to a fixed threshold setting, indicated in the figure. In all cases, the efficiency is above 99% for a threshold setting of 1.18fC, where the occupancy is of the order 5\*10<sup>-4</sup>.

Fig. 17 Noise Occupancy vs Efficiency for the AT&T3 module

From the results of the previous section, we can draw conclusions for the operation of radiation damaged detectors in ATLAS. In the beam test, we used 12cm detectors with 75 $\mu$  pitch, n-implants on p-bulk, which were biased below depletion. The FEE was operated on a non-optimized power setting. The angle of incidence was varied from 0 to 14°.

For all angles, the noise occupancy is acceptable at 0.9fC (below  $10^{-3}$ ), and to specs above 1.0fC threshold ( $10^{-4}$ ). At the same time, the efficiency is acceptable at 1.4fC (> 98%), to specs below 1.2fC (> 99%). This corresponds to a "head room" of the binary system of between 20% and 50%, depending on the criteria, within which the threshold setting can vary without compromising the physics performance of the detector.

This head room should be reserved for unexpected effects, like higher than expected radiation levels, or lowered performance of the silicon detectors, and not account for controllable spread in the performance of the FEE. This calls for a tight specification of the threshold matching (gain & noise) for the bipolar chips. Our previous experience [17] with the testing of the TEKZ chip for the LPS in ZEUS, produced in the SHPi process with Tektronix (now MAXIM) warrants the expectation that indeed the matching will be excellent in a custom bipolar amplifier-comparator chip. Two lots of 6 wafers each produced about a year apart were tested thoroughly and the matching of the gain investigated. The matching of the threshold at 1fC across 6 wafers (660 chips\* 64channels) was 4%, corresponding to 25% of the noise rms of the bonded detectors. The data from the two different lots were indistinguishable. This uniformity of performance allows the 55k LPS channels to be operated with one threshold of 0.78fC. For ATLAS, where we will operate about two orders of magnitude more channels, we most likely need to group chips with similar gain to keep the acceptable yield high.

## CONCLUSION

We have performed a beam test with several binary modules during the 1995 ATLAS beam test in H8. Previous results showing an extended efficiency plateau beyond the nominal threshold of 1fC have been confirmed. With the help of a precision telescope, the efficiency, hit multiplicity and resolution was mapped out as a function of the track position between strips. We found good efficiency for inclined tracks up to 14degrees in a 75micron pitch n-side detector. The efficiency of n-on-n detectors depends only marginally on the bias voltage once the detector is depleted.

## ACKNOWLEDGMENTS

We thank our colleagues in H8, especially Steinar Stapnes, Gareth Moorhead, and David Munday for their help and cooperation. William Murray's extensive help in the data analysis is gratefully acknowledged. This work was supported by the UK Research Council, the US Dept. of Energy, and the US-Japan Scientific cooperation program.

# REFERENCES

[1]ATLAS SCT, CERN/LHCC/94-38.

- [2] ATLAS Technical Proposal, CERN/LHCC/94-43.

- [3] A. Ciocio *et al*, A Binary Readout System for Silicon Strip Detectors at the LHC, Presentation at the LHC Electronics Workshop, Lisbon, Portugal, Sept 12, 1995.

- [4] J. DeWitt *et al*, Signal-to-Noise in Silicon Micro strip Detectors with Binary Readout, IEEE Trans. N.S. Symp. **42**, 445 (1995).

- [5] Y. Unno *et al*, Characterization of DSSD with fast binary readout electronics using pion beams, 1995 IEEE N.S. Symposium, San Francisco, CA

- [6] P. Allport: ATLAS Beam Test Results, 2nd International Symposium on Development and Application of Semiconductor Tracking Detectors, Hiroshima, Japan, Oct 10-13, 1995.

- [7] H. Sadrozinski, et al., Monitoring the Performance of Silicon Detectors with Binary Readout in the ATLAS Beam Test, 2nd International Symposium on Development and Application of Semiconductor Tracking Detectors, Hiroshima, Japan, Oct 10-13, 1995, SCIPP 95/

- [8] E. Spencer *et al.*, A Fast Shaping Low-Power Amplifier-Comparator Integrated Circuit for Silicon Strip Detectors, IEEE Trans N.S. **42**, 796(1995)1

- [9] I. Kipnis, CAFE, A Complementary Bipolar Analog Front-end Integrated Circuit for the ATLAS SCT, unpublished.

- [10] J. DeWitt, A Pipeline and Bus Interface Chip for Silicon Strip Detector Readout,

- IEEE N.S. Symp., San Francisco, CA, Nov. 1993, SCIPP 93/37.

- [11] K. Shankar *et al*, Digital Read-out Chip for Silicon Strip Detectors at SDC, IEEE Trans. N.S. Symp. 42, 792 (1995).

- [12] T. Ohsugi *et al*, Double-sided Microstrip Sensors for the Barrel of the SDC Silicon Tracker, Nucl. Instrum. Methods A342 (1994) 16.

- [13] S. Holland, Fabrication of Silicon Strip Detectors using a Step and Repeat Lithographic System, LBL 31595, (1991).

- [14] T. Dubbs *et al*, Noise Determination in Silicon Microstrip Detectors 1995 IEEE N.S. Symposium, San Francisco, CA, SCIPP 95/19.

- [15] T. Pulliam, Noise Studies in Silicon Micro strip Detectors, UC Santa Cruz Senior Thesis 1995, SCIPP 95/28.

- [16] T. Dubbs *et al.*, Operation of Non-uniformly Irradiated Double-sided Silicon Detectors, 2nd International Symposium on Development and Application of Semiconductor Tracking Detectors, Hiroshima, Japan, Oct 10-13, 1995, SCIPP 95/46.

- [17] E. Barberis *et all*, Design, Testing and Performance of the Frontend Electronics for the LPS Silicon Microstrip Detectors, Nucl. Instrum. Methods A364 (1995) 507.