#### **EUROPEAN ORGANISATION FOR NUCLEAR RESEARCH**

CERN LIBRARIES, GENEVA

LEB Stat

LEB Status Report/RD9 6 January 1997

CERN/LHCC 97-1

### **RD9 FINAL STATUS REPORT**

# A Demonstrator Analog Signal Processing Circuit in a Radiation Hard SOI-CMOS Technology

Spokesmen Erik Heijne and Pierre Jarron

F. Anghinolfi, P. Aspell, M. Campbell, F. Faccio, J. Kaplon, E.H.M. Heijne, P. Jarron, F. Lemeilleur W. Snoeys

CERN, 1211Geneva 23, Switzerland

P. Borgeaud, E. Delagnes, M. Dentan, F. Lugiez, M. Rouger CEA-DSM-DAPNIA Saclay, 91191 Gif-sur-Yvette, France

G. Borel, J. Redolfi, J.M Brice Thomson TCS, F-38521 Grenoble, France

W. Dabrowski

CERN and Institute of Nuclear Physics, Cracow

#### 1 Introduction

The RD9 DRDC project started in 1991 at a time when it was not known whether any commercial radiation hard process would fullfil the design requirements of the complex ASIC chips needed for the LHC experiments with hardening levels of more than 10 Mrad. The primary goals of RD9 were the understanding of the hardening techniques for electronics chips in SOI-CMOS processes and the development of analog demonstrators in the radiation hard 1.2µm SOI-CMOS process HSOI3HD from THOMSON TCS (F). The fact that it was the only available European radiation hardened process at the level of 10Mrad at the time, was the main reason for its selection. In addition, properties of SOI-CMOS processes were considered promising in terms of speed and robustness against Single Event Latch up (SEL) and Single Event Upset (SEU).

The RD9 project was focused on characterisation of samples provided by THOMSON TCS, development of simulation models for analog design, and the design and characterisation of analog demonstrators, such as amplifier, analog memory and ADC. All these goals have been fully reached and have been reported in previous RD9 status reports and at the LERB workshop [1]. The main obstacles we have identified were a lack of uniformity and stability of the HSOI3HD process, due to a too small volume of

production in the TCS wafer fab, and the large series body contact resistance which significantly affects performance of analogue functions. In particular, the MOS transistor in HSOI3HD exhibits a higher noise due to the excess thermal noise of the body contact [2].

We have also learned that the promise of high speed and high density for digital circuits implemented in SOI processes are unfortunately cancelled by the hardening layout design rules used in HSOI3HD. Source and drain regions have a smaller capacitance than in a bulk process, but the gate capacitance is higher, in particular for analogue switches with separate body contacts. This results in inferior speed and device density figures than a bulk CMOS process with comparable gate length. A CRIAD ADC designed in HSOI3HD was 40% larger than the same design done with the 1.5µm "soft" bulk CMOS process from MIETEC N.V.(B).

In view of the limitations of the HSOI3HD process, RD9 started to collaborate with RD29 in 1994 in order to compare the performance of DMILL and HSOI3HD. This work has resulted in the development in 1995 of 2 demonstrators (SCTA and SCTB in the DMILL process) by the RD9 team in collaboration with CEA Saclay, and Cracow. Successful results have been obtained from these chips [3,4].

In 1995, they were rumours that THOMSON would phase out all rad hard SOI processes. This was confirmed at the beginning of 1996: a letter was sent to inform CERN that all their rad hard processes were definitively stopped. At the end of 1996, the decision of the French government to privatise THOMSON CSF resulted in the closure of the Grenoble TCS site and the wafer fab.

#### 2. The 1995-1996 Milestones

The milestones recommended by the 24th meeting of the DRDC in September 1994 were the following:

1. Finish irradiation tests with the 1993 demonstrator circuits and prove validity of the simulation model.

The 1993 demonstrator circuits, an ICON amplifier and a transimpedance amplifier, have been irradiated up to 10Mrad. Analogue characteristics and noise have been measured before and after irradiation. These results have been presented in the LERB workhop (Lisbon) in 1995, and at the NSREC conference in 1995 and published [1,7]. The validity of the simulation model has been checked for a track-and-hold circuit, and results have also been presented at the LERB workshop [1]. After 10 Mrad, amplifier circuits are fully functional, and noise increases by 40%.

2. Evaluate the performance of the 1994 demonstrator circuits.

This second task has been carried out in 1995. The CRIAD ADC demonstrator has been fabricated, tested and irradiated up 20 Mrad. Experimental results are reported in section 3.3.

### 3. Evaluate prototype devices in HSOI4-HD (0.8 µm) technology

At the end of 1994, we have submitted to THOMSON-TCS a demonstrator in HSOI4-HD. In 1995, TCS decided to phase out HSOI4-HD. Therefore this project was very rapidly stopped. Subsequently, it was decided to collaborate with RD29 on an advanced demonstrator project in using the DMILL process, which is also a 0.8 µm CMOS and bipolar rad hard process. Experimental results of this project are briefly reported in section 4 and have been published [3,4]

### 3. Report on 1995 and 1996 HSOI3HD studies

The radiation hardness of digital circuits in the HSOI3HD process reaches the expected level of 10 to 20Mrad. The change in static parameters of transistors after 25 Mrad is acceptable and within the parameter spread of the HSOI3HD process. Nevertheless, we have found several problems which limit the use of the HSOI3HD process, in particular for analogue and mixed signal functions.

Despite the high density typical for SOI-CMOS processes which should offer high speed and low power characteristics, we have found that HSOI3HD does not exhibit better performance than bulk CMOS processes with the same feature size. The conservative layout rules applied for radiation hardness together with the additional body contact, significantly decrease the density of circuits. For instance, the gate capacitance is increased by a factor 2. Therefore, the power consumption of a CRIAD-ADC demonstrator chip was found to be significantly higher than the corresponding version fabricated in a commercial bulk 1.5µm CMOS process.

Another severe limiting factor to the use of HSOI3HD for analog functions comes from the body contact effect. This is a common problem of medium thickness film (150nm) and thin film (80nm) SOI processes. The body effect is caused by a dynamic, and in some case also by a static inefficiency of the body contact. The most severe effects we have studied are an unstable and unpredictable charge injection from analog switches in mixed signal circuits, and an additional noise component in amplifier circuits.

Although the lot-to-lot reproducibility of the radiation hardness was in general acceptable, we have nevertheless noticed sometimes large differences in the radiation response of transistors coming from different fabrication lots. We explained this by the very low volume production in TCS wafer fab, and by the variation of characteristics of SIMOX wafers.

#### 3.1. Device characterisation

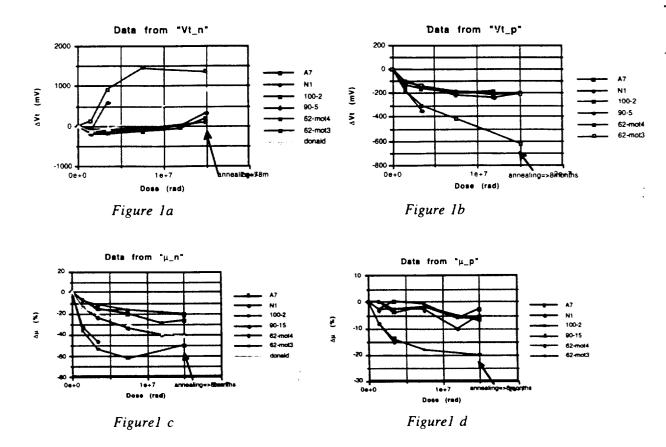

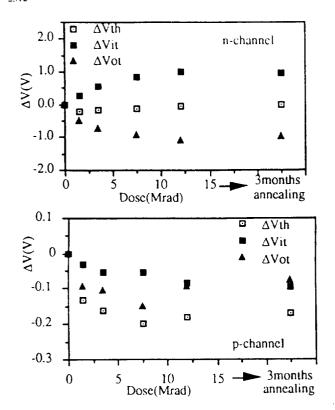

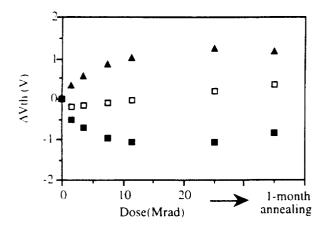

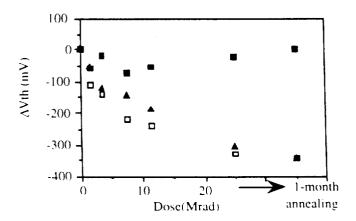

The measurement of ionization effects on NMOS and PMOS devices in the HSOI3HD process when irradiated by a Co-60 source has been performed for devices implemented on different types of SIMOX SOI substrate. V<sub>T</sub> shift, weak inversion slope, back channel threshold, mobility, annealing effect and leakage current for several fabrication lots have been extracted. As an exemple, Fig.1a-d shows variations of Vt shift and mobility of p-

channel and n-channel devices as a function of the total dose for 6 different lots fabricated between 1991 and 1995. Lots 100 and 90 have a totally different radiation response.

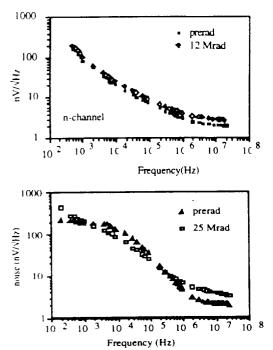

#### 3.2. Noise characterisation

MOS transistors usually exhibit 2 noise components: 1/f noise caused by random trapping of carriers in traps located at the interface or within gate oxide, and white noise caused by thermal motion of carriers in the channel. Complete results on 1/f noise and white noise of the HSOI3HD up to 25 Mrad are reported in references [5,6]. In addition, transistors in HSOI3HD have a third noise source. A detailed study including the design and integration of dedicated test structures has led to the conclusion that this additional component originates from the body resistance. This resistance is high and bias dependent. The result of this study has been presented at the 1996 SOI conference [2].

#### 3.3. HADC11 demonstrator

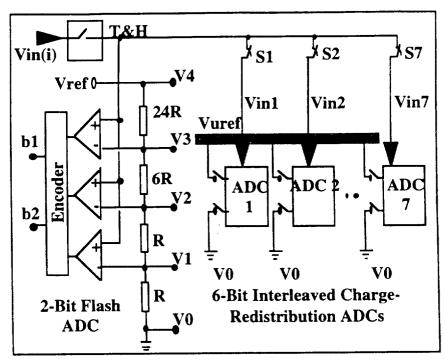

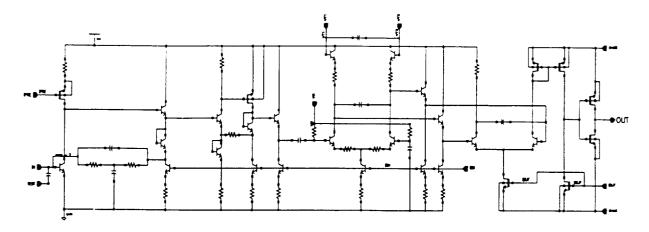

The CRIAD ADC, the block diagram of which is shown in fig.2, was originally designed in a commercial soft bulk CMOS, but has now been redesigned in HSOI3HD.

#### Pre-irradiation results

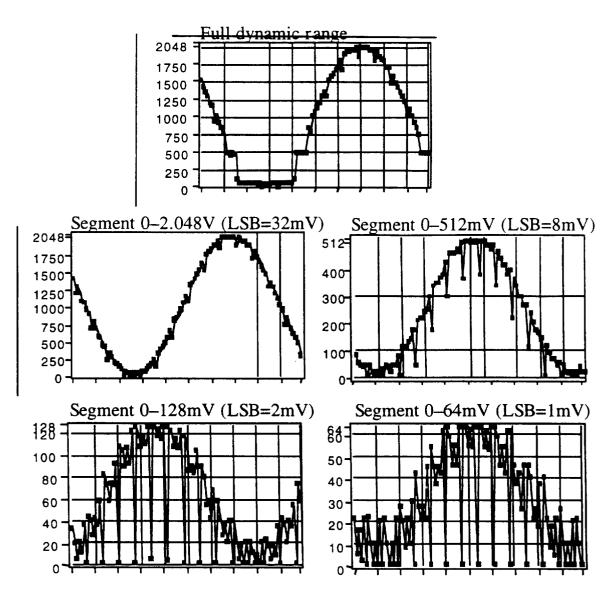

The functionality of the HSOI3HD version was satisfactory, although the timing sensitivity of the track-and-hold was higher than expected. As a consequence, the best

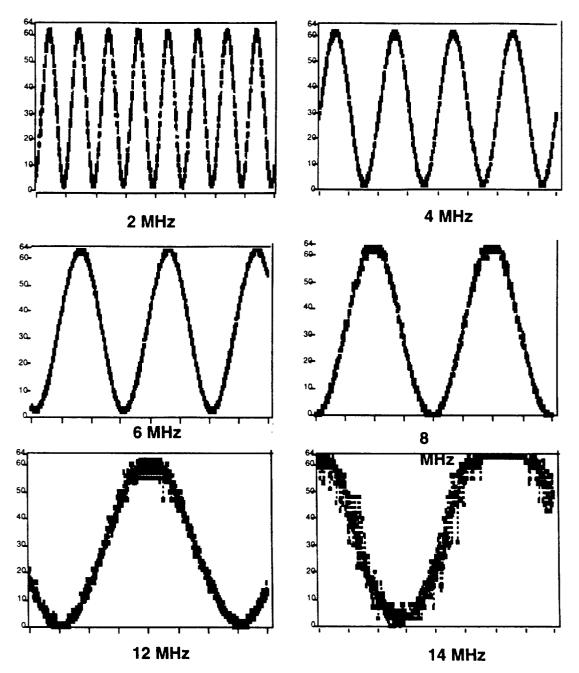

results were obtained with a synchronisation of the clock between track-and-hold and comparators different from the simulation. In those conditions, the maximum sampling rate was 16 Mhz, but above 8 Mhz the LSB precision of 1 mV is not kept. This is shown in Fig.3 which depicts the digitization of a 20Khz sinus wave of 64 mV amplitude at different ADC sampling frequencies. Simulations predicted a maximum data conversion speed of 20 Mhz. The yield evaluated on few samples, 20, was 70% for a circuit area of 15 mm<sup>2</sup>.

Figure 2. CRIAD ADC Block Diagram

Figure 3. Digitization of a 64 mV 20Khz sine wave at different sampling frequencies

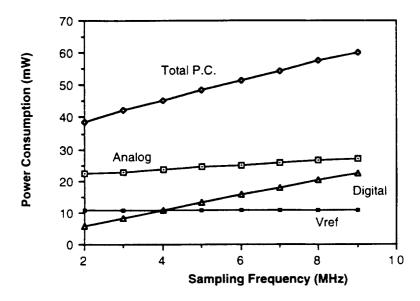

The total power consumption of the chip has been separately measured for the analog and digital blocks, and the resistor network of the 2bit flash ADC, and the result is given in Fig.4. The resistor network is made up of 32 equal elements for a total of  $480\Omega$ . The power supplies voltages were different for analog and digital circuits, being  $\pm 3V$  for the analog and  $\pm 2.5V$  for the digital. For 8Mhz conversion rate, the power consumption of the HSOI3HD ADC-CRIAD version is about 40% higher that the version in a "soft" commercial bulk CMOS. The increase of power is mainly due to the additional parasitic gate capacitance in HSOI3HD.

Figure 4. Power consumption of CRIAD ADC in HSOI3HD

The linearity measurement indicates a precision of 1mV as expected for the first range of 64mV, for conversion frequencies less than 8Mhz. The differential non-linearity is 0.2 LSB in each conversion range, and the integral non-linearity is 0.37 LSB in the first range and 0.15 LSB in the 3 others. All these results were similarly measured on circuits coming from the same production but using 2 different SIMOX wafers: simple and double implanted. This was done to study the impact of the buried oxide implant technique on the performance of VLSI circuits. No significant difference was observed between circuits fabricated with these 2 different substrates.

### Results after irradiation, 10Mrad - 20Mrad

After irradiation, several problems in the ADC operation appeared. The range conversion (2 MSB bits) performed by the flash ADC stage does not work, as shown in Fig.5a for the full dynamic range. The failure is probably due to a very high input voltage offset of the comparators of the 2-bit flash ADC. By forcing the conversion in the largest range, as shown in Fig 5.b-e, it is possible to study the performance of the 7 interleaved ADC stages. Even in this case, the offset of the comparator is so high that the resolution becomes very poor. Other parasitic effects occured, such as the presence of a pattern in the digitized output code which indicates a non-uniformity of the offset through the 7 interleaved ADC stages. Large charge injection in analog switches in the comparator is assumed to be the origin of the failure. This also causes the failure of the offset correction circuit embedded in comparator stages.

After irradiation to a total dose of 10Mrad, the total power consumption increased only by about 20%.

Figure 5. CRIAD ADC performance after irradiation

#### 4. Report on last year's DMILL development

The technical issues of HSOI3HD related to body effects, and the rumours of the possible stopping of rad hard processes at THOMSON TCS lead us to dedicate a significant effort in the evaluation of the DMILL process. RD9 in collaboration with RD29, CEA Saclay DAPNIA and the Faculty of Physics and Nuclear Techniques of Cracow/PL has pursued in 1995 and 1996 the development of BiCMOS front-end electronics demonstrators in the 0.8µm BiCMOS DMILL radiation hardened process.

Two prototype chips, SCTA and SCTB, respectively for the analogue and binary readout of silicon strip detectors in the ATLAS Semiconductor Tracker (SCT) have been designed and manufactured in 32 channel versions using the DMILL process.

The SCTA chip [4] comprises three basic blocks: front-end amplifier, analogue pipeline and output multiplexer. The front-end circuit is a fast transresistance amplifier followed by an integrator, providing fast shaping with a peaking time of 25 ns, and an output buffer. The front end output values are sampled at 40 MHz rate and stored in a 112-cell deep analogue pipeline. The delay between the write pointer and trigger pointer is tunable between 2  $\mu$ s and 2.5  $\mu$ s. The chip has been tested successfully and subsequently irradiated up to 10 Mrad. Full functionality of all blocks of the chip has been achieved at a clock frequency of 40 MHz both before and after irradiation. Noise figures of ENC = 720 e<sup>-</sup> + 33 e<sup>-</sup>/pF before irradiation and 840 e<sup>-</sup> + 33 e<sup>-</sup>/pF after irradiation have been obtained.

The SCTB chip [3], comprises three basic blocks: front-end amplifier, discriminator and a binary pipeline. The preamplifier and shaper implemented in this architecture use the same concept as used for the front-end in the analogue architecture. The shaper is followed by a discriminator providing only 1 bit yes/no information which is stored in a binary pipeline based on a dynamic FIFO digital circuit in order to achieve low power and high density. The chip has been irradiated by a Co-60 source up to 10Mrad under nominal static bias. After irradiation, the SCTB chip is fully functional and performance is maintained. The power consumption increased from  $200\mu W$  to  $360\mu W/channel$  for a clocking frequency of 40Mhz.

#### 5 Conclusion

After these 4 years of RD9 study, we have learned that HSOI3HD is a good process for digital circuits, but has severe limitations for analog and mixed-signal circuits. After irradiation, analog performance of amplifiers was poor and complex circuits did not work anymore (ADC). We have understood this issue 2 years ago, and we therefore turned our efforts towards the DMILL process. This has resulted in demonstrator circuits, SCTA and SCTB, those results have convinced HEP community that rad hard circuits can be built that meet the requirements of LHC experiments. These two circuits are now seriously considered by ATLAS for the readout of the silicon tracker.

#### References

- [1] P.Aspell et al., Study of a radiation hard SOI-CMOS technology for mixed analog-digital IC design for applications in LHC, First Workshop on Electronics for LHC Experiments. Proceedings of the LERB meeting, Lisboa Sept. 1995, CERN/LHCC/95-p.56

- [2] F. Faccio et al., An additional contribution in the noise spectrum of SOI MOSFETs, presented at the 1996 SOI conference, Fort Meyers Fl, USA (Oct. 1996).

- [3] F. Anghinolfi et al., Development of front-end electronics for LHC experiments, Ballaton, Hungary (Sept. 1996), CERN/LHCC/96-39.

- [4] F. Anghinolfi, et al., SCTA A Rad-Hard BiCMOS Analogue Readout ASIC for the ATLAS Semiconductor Tracker, presented at IEEE Nucl. Sc. Symp, Anaheim (Nov.1996).

- [5] F. Faccio et al., Noise Characterization of Transistors in a 1.2 μm CMOS-SOI Technology up to a Total-Dose of 12 Mrad (Si), presented at IEEE NSREC Symposium 1994.

- [6] F. Faccio et al., Analog Performance of SOI MOSFETs up to 25 Mrad (Si), Proc. RADECS' 95 Conference, F (Sept. 1995).

- [7] P. Aspell et al., A fast, low power CMOS amplifier on SOI for sensor applications in a radiation environment of up to 20 Mrad(Si), IEEE Trans. NS vol 42, p.636.

#### **Appendices**

Papers published in 1994, 1995 and 1996.

# Study of a radiation hard SOI-CMOS technology for mixed analog-digital IC design for applications in LHC

P. Aspell, F. Faccio, E.H.M. Heijne, P. Jarron and A. Rivetti CERN, CH-1211 Geneva 23, Switzerland

ABSTRACT. The HSOI-3HD CMOS on SOI technology has been studied in order to assess its suitability for use as a radiation hard VLSI process in LHC detector frontend electronics. In particular the study has concentrated on the analog characteristics of transistors and the design and measurement of a number of demonstrator circuits. The transistor measurements have shown threshold shifts of 250mV and -350mV for n and p channel respectively. The noise study has shown that in addition to the white noise and 1/f noise sources, a third generation recombination (G-R) noise source is apparent. This G-R component appears as a hump in the noise spectra and can be moved in frequency by varying the body-source (Vbs) potential of the device. A IVbsI of 1.3V is sufficient to move this component out of the frequency range of interest for LHC and hence make it negligible. Two amplifiers, namely a grounded gate amplifier and a low noise transimpedance amplifier, and also a track and hold circuit have been designed and fully measured. The results show full operation after doses up to 20Mrad(Si) with little degredation with respect to gain and speed. There is however a significant deterioration in the noise behaviour.

### 1. INTRODUCTION

Complex ICs for signal processing in experiments at the LHC will sit in a high radiation environment. Radiation hardness for total dose up to a level of 10 to 30 Mrad and for single event phenomena is required. Silicon on Insulator (SOI) technologies are immune from Single Event Latchup (SEL) and have a higher threshold than bulk technologies for Single Event Upset (SEU), therefore they are good candidates for applications in the LHC environment.

The only commercially radiation hard process on SOI available in Europe is the HSOI3-HD, a 1.2  $\mu$ m polycide gate CMOS technology manufactured by Thomson TCS (St. Egrève, France) on a SIMOX substrate. It is optimised for high total dose for digital circuits. We have investigated the analog performance of this process and its potential for LHC applications.

# 2.ANALOG CHARACTERIZATION OF THE TRANSISTORS

A series of test transistors of different size and geometry and coming from several processing batches has been measured. The full characterization involved extraction of the static parameters (threshold voltage, mobility, transconductance, leakage current) and study of the noise. Irradiation has been performed at several total dose levels, up to a maximum of 25 Mrad (Si). A constant bias with a current density of  $0.2~\mu\text{A}/\mu\text{m}$  has been kept during both irradiation and room temperature annealing.

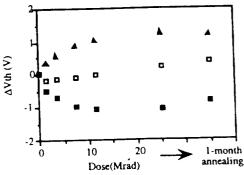

The threshold voltage shift as a function of total dose is depicted in figs. 1 and 2 for n- and p-channel transistors. Relative contributions of interface states and oxide trapped charge are shown. The prerad threshold voltage for p-channel transistors is about -1.3 V, whilst it is 900 mV for the n-channel. This values were extracted with the back interface in accumulation. Room temperature annealing under bias does not have a major importance in the threshold evolution. The threshold voltage shift after 25 Mrad is of the order of 250 mV for n-channel and -360 mV for p-channel transistors. For the p-channel this can impose to use a power supply of at least 3.5V.

Threshold voltage shift is reasonably predictible at any total dose and therefore circuit performance after irradiation

Figure 1: Threshold voltage shift for n-channel transistors. Empty squares represent the overall shift, which is due to the contributions of trapped oxide charge (black squares) and interface states (black triangles).

Figure 2: Threshold voltage shift for p-channel transistors. Empty squares represent the overall shift, which is due to the contributions of trapped oxide charge (black squares) and interface states (black triangles).

can be estimated in the design phase.

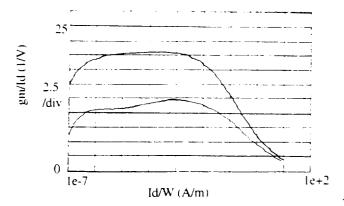

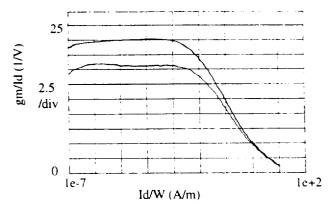

Transconductance in saturation decreases respectively of about 44% and 18% for n- and p-channel transistors. In

every case the drain leakage current stays below a few tens of pA.

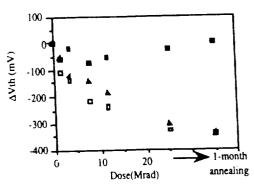

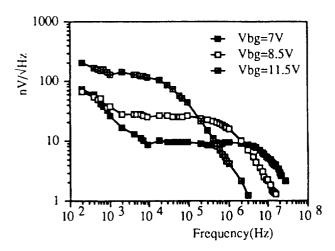

The spectral power density of the equivalent input noise voltage of NMOS and PMOS transistors has been measured before and after 60Co irradiation. Measurements were performed in strong inversion and in saturation, with a constant current density of 0.5 µA/µm. The noise spectrum is composed of three different sources: white noise, 1/f or flicker noise and generation–recombination (G-R) noise. This G-R noise is visible as a hump in the noise spectra only under particular bias conditions, and can be moved widely in frequency by acting on the body or backgate bias.

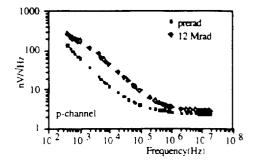

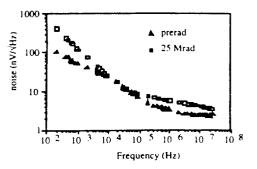

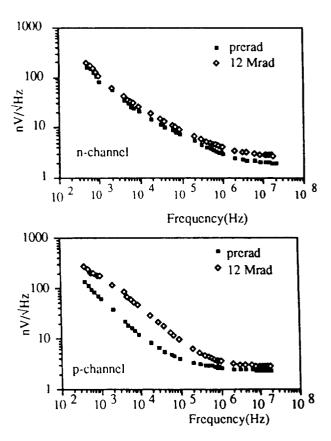

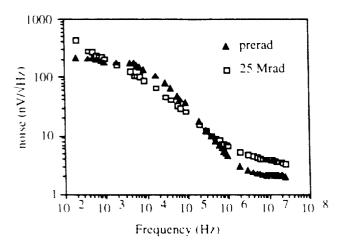

Figure 3: Noise spectra of n-channel transistors from lots 1 (upper picture) and 2 before and after 12 and 25Mrad and annealing. In the spectra shown for lot 1, the applied body bias could move the G-R hump under the 1/f noise. This was not the case for lot 2, due to a different backgate threshold voltage.

The p-channel transistors, which are buried channel devices, have lower 1/f noise. The parameter  $K_f$  characterizes the 1/f noise and increases from  $1.37 \cdot 10^{-9}$  to  $6.9 \cdot 10^{-9}$  fC<sup>2</sup>/ $\mu$ m<sup>2</sup> for PMOS transistors after a 25 Mrad irradiation. Therefore, in the measurement conditions for W/L=1000/1.4, the corner noise frequency Fc (defined for equal 1/f and white noise contributions) stays below 200 Khz even after irradiation.

Figs. 3 and 4 show the noise spectra before and after 12 and 25Mrad for transistors coming from 2 different fabrication lots. The G-R noise contribution is still visible in some of the depicted spectra. Owing to the particular layout of the test structures (common terminals for the n-channel and p-channel transistors), we could not apply a sufficiently high body bias to move this contribution further in the low

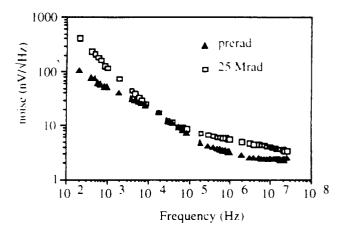

Figure 4: Noise spectra of p-channel transistors from lots 1 (upper picture) and 2 before and after 12 and 25Mrad. Even after 12 Mrad, the noise in the 10-20 MHz region increased significantly more for lot 2.

frequency region in all cases. The backgate threshold voltage determined whether the applied bias was sufficient to make the G-R hump disappear under the dominant 1/f noise. Transistors from lot 2 had higher noise after irradiation. For the n-channel white noise, this was determined by a sharper decrease in transconductance. For p-

Figure 5: Noise spectra of p-channel transistors from lot 3. Noise at 10 Mhz is 1.65 nV/VHz before irradiation and 1.76 nV/VHz after 12Mrad

channel transistors from the same lot it was difficult to clearly identify the white noise after irradiation, but the noise increase in the 10-20 MHz region was much higher than for lot 1.

Noise results of figs. 5 and 6 were obtained from transistors of W/L=2000/1.4 coming from a third fabrication lot. These test transistors were differently layed out to allow more freedom in the bias and to study eventual parasitic effects from the edges. The measurements were performed

with  $I_d$ =1mA to keep the same current density in the channel as for lots 1 and 2. Voltage spectral density (Sv) in the white noise region and 1/f corner noise frequency (Fc) of these 3 different lots are summarised in table 1 before and after irradiation and annealing.

We have observed a variation of the radiation hardness

Figure 6: Noise spectra of n-channel transistors from lot 3. Noise at 10 Mhz is 1.51 nV/VHz before irradiation and 2.1 nV/VHz after 12Mrad.

between transistors coming from different fabrication lots. In particular, lot 2 shows higher noise and lower transconductance after irradiation.

Table 1. Voltage spectral density in the white noise region and 1/f corner noise frequency values for transistors coming from the three different production lots. These results refer to transistors with W/L=1000/1.4 biased at Id=500 $\mu$ A for lot 1 and 2 and W/L=2000/1.4 biased at Id=1mA for lot 3. Sv is in  $\eta V/\sqrt{Hz}$  and Fc in KHz

| LOT     | S v<br>prerad | Sv<br>12Mrad | S v<br>25Mrad | Fc<br>prerad | Fc<br>12Mrad | Fc<br>25Mard |

|---------|---------------|--------------|---------------|--------------|--------------|--------------|

| lot l n | 1.98          | 2.73         |               | 1000         | 800          |              |

| lot 1 p | 2.16          | 2.5          |               | 132          | 179          |              |

| lot 2 n | 2.16          | 3.10         | 3.19          | 1260         | 1760         | 1520         |

| lot 2 p | 2.75          | 3.14         | 3.29          | 69           | 143          | 202          |

| lot 3 n | 1.51          | 2.1          |               | 995          | 2840         |              |

| lot 3 p | 1.65          | 1.76         |               | 71           | 89           |              |

### 3. GROUNDED GATE CURRENT AMPLIFIER

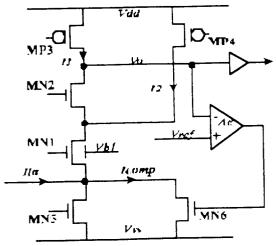

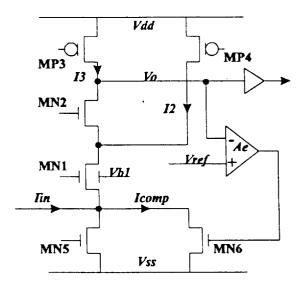

The design of the grounded gate amplifier is shown in Fig.7. It consists of the grounded gate input MOSFET MN1, the cascode stage MN2 and the current sources MP3, MP4 and MN5. The output node Vo acts as an integrating node of capacitance Co. The slow speed error amplifier (Ae) ensures a stable DC potential of the output node and defines a discharge time constant of Co through the controlled current source MN6.

The technique also provides self adjustment for the effect of the sensor dark current which becomes significant as the total dose accumulates. Detector leakage currents of up to 20mA can be compensated for, enabling a DC connection to the sensor. This, in turn reduces the processing cost of the detector.

Figure 7 Grounded gate amplifier as implemented in HSOI3HD

The chip consists of 12 channels each with vertical pitch of 100mm and length 800mm. Including the pads the total surface area is 7.9mm2.

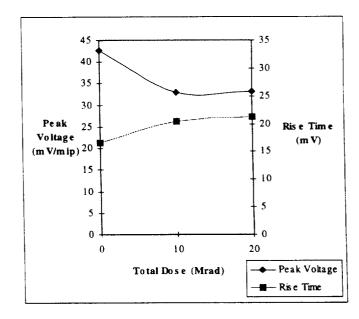

A total of 10 chips were irradiated, five at 10 Mrad and five at 20 Mrad using a 60Co source. The exposure was over a 76 hour period giving dose rates of 133 Krad/hour and 266 Krad/hour.

The noise slope before and after irradiation has been measured. The prerad, result is 78e' /pF (rms) which corresponds to approximately 2nV /Hz<sup>1/2</sup>. After 10 Mrad there is an increase in the parallel noise of approximately 23% whilst the series noise increases by nearly 60%. The degradation thereafter is small and only apparent in the parallel noise, increasing by a further 9%. The majority of the radiation effects is apparent within the first 10 Mrad with only a small change thereafter. Satisfactory operation at higher levels of total dose would therefore seem probable but further study would be needed to confirm this.

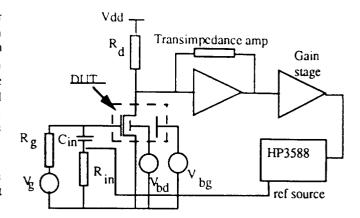

# 4. LOW NOISE TRANSIMPEDANCE PREAMPLIFIER

A transimpedance amplifier using a fast active feedback loop presented elswere [5] in a commercial 0.7μm bulk CMOS technology¹ has been designed and fabricated in HSOI3HD. This amplifier has been sized for a detector capacitance of 10 to 20pF.

Fig. 8 shows the circuit diagram. T1 and T2 forms the amplifier stage with the load MPL. Transistor MPf The input device the p-channel T1 has an aspect ratio W/L=2000/1.4. The sizing of all transistors is very similar to the MIETEC design, except minor modifications due to different parasitic capacitances and body connection of the SOI technology. After 10 Mrad, pulse shape does not change indicating no further radiation damage between 3 to 10 Mrad. The noise result is different, the noise increase continue from 3 to 10 Mrad. These preliminary experimental results are obtained without annealing and must be confirmed after few weeks of annealing time.

MIETEC NV, Oudenaarde Belgium.

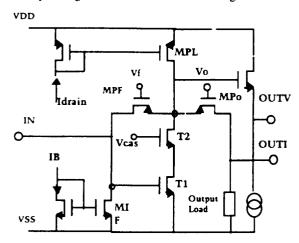

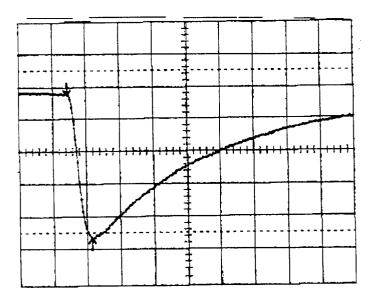

Fig.9 shows the output pulse waveform of the SOI active feedback transimpedance amplifier prerad, after 3 Mrad and 10 Mrad for a feedback current of 40nA and an input capacitor Cin=10pF. After 3 Mrad the gain decrease is 15%, but the peaking time of 80ns does not change.

Figure 8 Circuit diagram of the active feedback transimpedance implemented in HSOI3HD process.

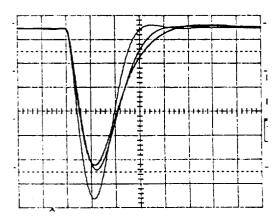

Fig 10 shows the noise characteristic ENC=f(Cin) of the active feedback preamplifier fabricated in  $0.7\mu m$  CMOS bulk process and in HSOI3HD. The fit to the has been obtained by applying a least mean square on the expression,

Figure 9 Output pulse waveform of the active feedback transimpedance for prerad (larger pulse height), 3Mrad and 10 Mrad. Input charge is 4fC,time axis is 100ns/div and y-axis is 10mV/div.

$$ENC = \left[ \frac{\left(3.0310^4 e_n^2 C_{in}^2\right)}{\tau_{ro} + \kappa C_{in}} + 2.7610^4 i_n^2 \left(\tau_{ro} + \kappa C_{in}\right) \right]^{1/2}$$

(2)

where ENC is the equivalent noise charge in electrons rms,  $e_n$  is the equivalent series noise voltage in  $nV/\sqrt{Hz}$ ,  $i_n$  is the equivalent parallel noise current in  $pA/\sqrt{Hz}$ . Cin the input capacitance in pF,  $\tau_{r0}$  is the rise time 10%-90% in ns for Cin=0,  $\kappa$  the rise time dependence with the input capacitance in ns/pF. This technique of calculation takes

into account the peaking time variation for the different input capacitors Cin.

Noise measurement indicates a larger noise for the SOI process. It must be noted that the input transistor is an n-

Figure 10 Noise measurement ENC=f(Cdet) of the active feedback transimpedance amplifier for a peaking time of 45ns and a bias current of 500μA in the HSOI3HD process(top graph) and in CMOS bulk submicron process(bottom graph). Bottom curves are prerad, top curves are after 3Mrad for HSOI3HD and 100Krad for 0.7μm CMOSprocess.

channel. A p-channel version will be submitted for fabrication end of 1995 and will exhibit a better noise figure before and after irradiation. The noise parameters extracted from the fit calculation are shown in table 2.

Table 2 Evolution of the preamplifier noise with radiation in HSOI3HD and MIETEC CMOS  $0.7\mu m$  processes.  $e_n$  [nV/NHz] and  $i_n$  [pA/NHz] are respectively the equivalent series noise voltage and parallel noise current referred to the input and extracted with eq (2).

| CMOS processes      | $e_n$ | $i_a$ | $\tau_{ro}$ | K    |

|---------------------|-------|-------|-------------|------|

| Bulk 0.7µm prerad   | 1.93  | 0.37  | 30          | 0.4  |

| Bulk 0.7µm 100 Krad | 2.31  | 0.33  | 40          | 0.45 |

| HSOI3HD pre-rad     | 2.64  | 0.67  | 48          | 0.7  |

| HSOI3HD 3 Mrad      | 4.5   | 1.01  | 60          | 0.7  |

After 3 Mrad the series noise voltage increase is 70 % which is close to what has been observed with a single n-channel device. In addition, there is an increase of the parallel noise of 50% which is not presently explained.

This effect is not observed on the bulk submicron CMOS process for which series and parallel noise are stable after 100Krad. These experimental results indicate also that the soft submicron CMOS process tested exhibits a better noise figure than HSOI3HD technology.

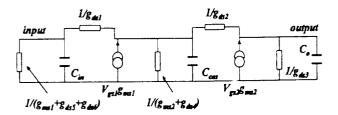

#### 5.FAST TRACK-AND-HOLD

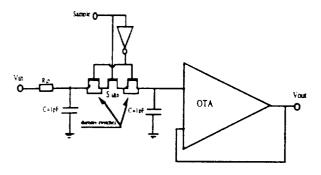

This circuit was designed to be used in the 11-bit CRIAD Analog-to-Digital converter. Its objective was a good tradeoff speed-to-accuracy. The circuit diagram is shown in fig.11. It comprises a Track-and-Hold switch  $(S_{tach})$  and a p-channel differential OTA with Miller compensation. The capacitance at each node of  $S_{tach}$  is equal, thus the charge injection is assumed to be symmetrical at both ends of the switch. This injection is reduced by two dummy switches half the size of  $S_{tach}$  integrated symmetrically.

Figure 11: circuit diagram of the fast track-amd-hold implemented in the HSOI3HD technology.

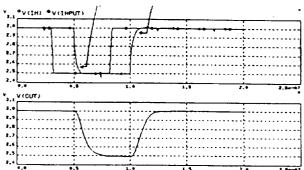

Figure 13: Results from the ELDO simulation of the T&H circuit. The upper picture shows the signal at the input and at the T&H node, whilst the lower one shows the output of the circuit charged with a 10 pF load.

The circuit has been fabricated and tested, and showed a rise time of 17.5 ns and a gain of 0.94, with a power consumption of 12.5 mW. The measurements were in good agreement with the simulation performed with the specially developed SOI model implemented in ELDO. Simulation results are shown in Fig.13.

The high power consumption was caused by an excessively high threshold voltage of the p-channel transistors for the processing lot in which the circuit was implemented. We had therefore to increase Vdd to keep all the transistors in saturation during operation. Another

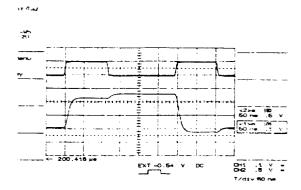

Figure 14: Output waveform of the track and hold stage measured after 12Mrad. They show the clock and the output of the T&H when an input signal of 800 mV is applied. An important parasitic charge injection from the clock is visible, this effect is strongly enhanced by irradiation.

consequence of this problem was a relatively high charge injection at the T&H node, especially after irradiation.

The shape of the response of the track-and-hold after 12Mrad is shown in Fig.14. We have measured a rise time of 19.7ns and a gain of 0.9, the circuit being still fully functional.

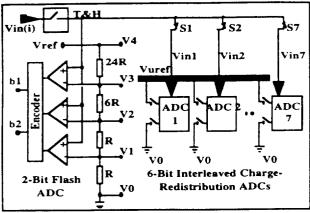

#### 6. 11-BIT LOW POWER ADC

This circuit was the translation in HSOI3-HD of an already existing circuit. fabricated in a bulk 1.5  $\mu$ m radiation soft technology. The specification requiring low power, speed higher than 5 MHz and a resolution higher on low-level signals (11-bits), the architecture of Fig.15 has been chosen. It performs a two-step analog-to-digital conversion using a 2-bit flash nonlinear converter for segmentation and 7 6-bit charge-redistribution ADCs.

It performs a two-step analog-to-digital conversion using a 2-bit flash nonlinear quantizer for segmentation and 7 6-bit charge-redistribution ADCs.

The circuit is currently in fabrication, and results should be available by the end of 1995. The speed performance, according to the simulation, should approach 20 MHz. Compared with the bulk realization, minor modification were required on the comparator to achieve better radiation hardness. Lateral body ties needed to be added to every analog device for noise and stability reasons.

In HSOI3-HD, the parasitic gate capacitance is significantly higher, requiring an oversizing of the driving logic gates. Therefore, a full re-sizing of the whole logic circuitry was necessary to keep the aimed speed performance. Power consumption is thus also increased, as well as silicon surface. An opposite trend towards lower area is given by the smaller metal lines and by the possibility to place n-and p-channel transistors very close to each other.

The total area of the ADC chip in HSOI3-HD is 15 mm<sup>2</sup>, whilst it was 10 mm<sup>2</sup> for the 1.5  $\mu$ m bulk technology as shown in Fig.15.

Figure: ADC architecture principle. The 2-bit flash part performs a segmentation of the reference voltage, whilst the 7 interleaved charge-redistribution ADCs need 7 clock cycles to perform the 6-bit conversion.

Figure 15 photograph of the CRIAD 11-bit ADC chip in 1.5µm CMOS soft process (upper picture) and in HSOI3HD (lower picture). The active chip area is respectively 6 and 8 mm<sup>2</sup>

necessary to keep the aimed speed performance. Power consumption is thus also increased, as well as silicon surface. An opposite trend towards lower area is given by the smaller metal lines and by the possibility to place n-and p-channel transistors very close to each other.

The total area of the ADC chip in HSOI3-HD is 15 mm<sup>2</sup>, whilst it was 10 mm<sup>2</sup> for the 1.5  $\mu$ m bulk technology as shown in Fig.15.

#### 7. CONCLUSION

The study of the analog characteristics of the HSOI3HD technology has been carried out on both test transistors and circuits. Transistors threshold voltage shift, studied up to 25Mrad, is acceptable (maximum=-350mV for p-channel) and predictable. The noise and transconductance degradation is much lower for p-channel transistors, which should be preferred as input devices in low noise circuits. The presence of a G-R component in the noise spectra can be made negligible by an adequate body bias. This introduces nevertheless a further complication in circuit design, and studies to understand its origin and to eliminate it are under way. We have designed test circuits to evaluate the mixed mode capability of the technology, namely two amplifiers. a track-and-hold and an 11-bit low power ADC. The noise of the two amplifiers does not meet the LHC requirements, : but better results are expected after a redesign which will approach the technology limits. All irradiated circuits still perform with full functionality after as much as 20Mrad, an increase of the noise of about 60% being the only real concern. A comparison with bulk radiation soft CMOS processes shows that the use of this technology has its major drawback in integration density and power consumption.

#### REFERENCES

- [1] J.L.Leray et al., "From substrate to VLSI: investigation of hardened SIMOX without epitaxy, for dose, dose rate and SEU phenomena", IEEE Trans.Nucl.Science NS-35(1988)1355

- [2] F. Faccio, M.Bianchi, M. Fornasari, E.H.M. Heijne, P. Jarron and G. Rossi, Noise characterisation of transistors in a 1.2μm CMOS-SOI technology up to a total dose of 12 Mrad (Si). IEEE Trans. On Nucl. Sci., Vol. 41, No.6, pp. 2310-2316, December 1994.

- [3] L.D.Yau and C.T.Sah, "Theory and experiments of low-frequency generation-recombination noise in MOS transistors", IEEE Trans.El.Devices 16(1969)170

- [4] Y.P.Tsividis, Operation and modeling of the MOS transistor, New York, McGrow-Hill, 1988

- [5] P.Jarron, F. Anghinolfi and W. Dabrowski, A novel current mode feedback technique for low noise transimpedance amplifier transimpedance amplifier using a Presented at the 7th Europeen Symposium on semiconductor Detectors, Schoss Elmau, May 1995. To be published in NIM A.

- [6] V.Valencic et al, "A low-power piecewise linear analog to digital converter for use in particle tracking", IEEE Trans.Nucl.Science NS-42, No4(1995)772

### AN ADDITIONAL CONTRIBUTION IN THE NOISE SPECTRUM OF SOI MOSFETs

F. Faccio, P. Aspell, P. Jarron and E.H. Heijne CERN, CH-1211 Geneva 23, Switzerland

#### Introduction

In view of possible analog applications, we have studied the noise characteristics of a medium-thickness SOI technology in the 200 Hz - 25 MHz bandwidth. We have found an additional noise contribution in the form of a hump in the noise spectrum, which can be moved widely in frequency and amplitude by changing the transistor bias. In this paper we present our hypothesis concerning its origin, and some measurements that support our interpretation.

#### Experimental details

The technology we have tested is a medium-thickness SOI. The silicon film can be completely depleted or not depending on the bias applied to the backgate and body electrodes [1]. The thickness of the gate oxide, silicon film and buried oxide is respectively 23 nm, 150 nm and 380 nm. The support for the technology is a SIMOX substrate. The silicon film is contacted to avoid floating body effects [2], and this is done via a lateral contact placed symmetrically on every edge of the transistor. This, moreover, prevents the formation of parasitic lateral conduction paths between source and drain even after exposure to ionising radiation. The width of all the measured transistors was 2000 µm, obtained by connecting 200 elements with W=10 µm in parallel. The noise measurements were performed, where not specified, in saturation and in strong inversion.

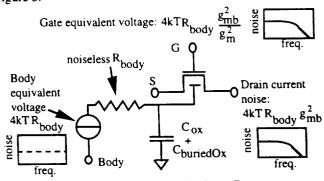

#### Model for the additional noise contribution

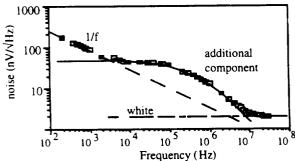

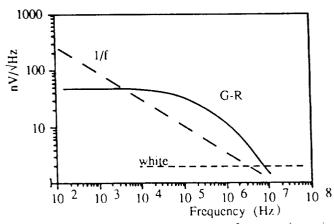

The noise spectrum of the measured transistors, referred to the gate, is qualitatively as shown in figure 1 for both n- and p-channel devices.

Figure 1: qualitative noise spectrum referred to the gate.

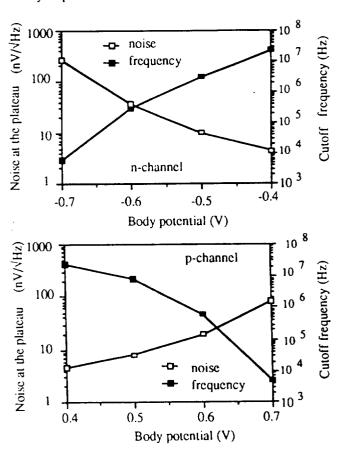

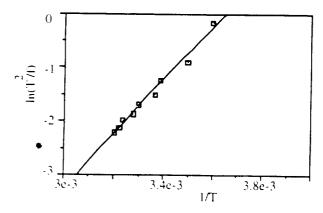

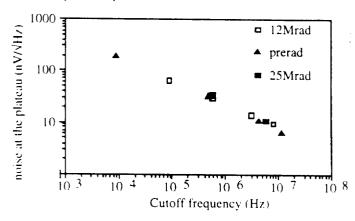

The standard 1/f and white noise components are still visible, though the superposition of an additional source increases considerably the overall noise. This component can be described with a set of two parameters: the noise level at the plateau and the cutoff frequency, which is the frequency where the noise is 3 db under the value at the plateau. A change in the potential applied to the backgate or body electrodes moves the cutoff frequency and modifies the amplitude dramatically. This occurs in a bias range where the depletion condition of the silicon film and hence its resistance are strongly sensitive to the bias.

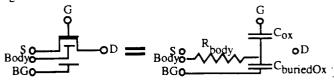

The potential of the silicon film which constitutes the body is imposed by an external bias. The resistance seen from the

power supply to the film is significant, and we assume that it increases with the depletion of the film itself. We call this resistance  $R_{body}$ . If we then introduce the capacitance of the gate and backgate oxides, we obtain the model shown in figure 2.

Figure 2: equivalent model

This resistance gives a thermal voltage noise spectral density

$$S_{\text{Vbody}}^2 = 4kTR_{\text{body}}$$

(1)

which is transmitted as a current noise to the drain through the body transconductance. When we measure the noise of the device, we convert the current noise at the drain into voltage noise by using a transimpedance amplifier, and we then refer all to the gate of the transistor. As a result of this, the voltage noise of R<sub>body</sub> gives the following contribution to the total equivalent voltage noise to the gate:

$$S_{Vgate}^2 = 4kTR_{body} (g_{mb}/g_m)^2$$

(2)

This is independent of the frequency. The resistance together with the capacitances  $C_{OX}$  and  $C_{buriedOX}$  make a low pass RC filter with a cutoff frequency

$$f_{c}=1/2\pi RC \tag{3}$$

The resulting filter cuts the white noise at the cutoff frequency, therefore in the noise spectra referred to the gate it is seen as a hump. The schematic of the process is depicted in figure 3.

Figure 3: transmission of the white noise due to Rbody.

#### Experimental observations

Our model is supported by the following experimental results: i) there is a correlation between the magnitudes of Rbody and the hump;

- ii) when R<sub>body</sub> is equal in different bias conditions, also the equivalent voltage noise referred to the body is equal;

- iii) the correlation is valid also when the transistor works in the ohmic regime;

- iv) the RC filter is effective for all signal injected through the body terminal.

We now detail these observations for the case of the n-channel transistor; they are similar for the p-channel.

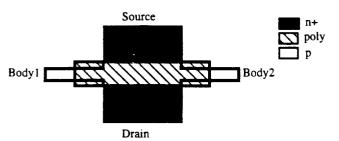

i) In order to get a very rough estimate of  $R_{body}$ , we have designed a special transistor with the two edges of the body film extracted on two separate contacts, as shown in figure 4. The resistance  $R_{meas}$  measured between the two body contacts (Body 1 and Body2) should be related to the actual  $R_{body}$ .

Figure 4: layout of the transistor designed to estimate Rbody.

$R_{meas}$  varies between about  $1.5k\Omega$  and more than  $1M\Omega$  when the body and backgate bias are changed to deplete the film. This happens in the voltage range over which the noise hump moves widely in amplitude and frequency. This correlation between  $R_{meas}$  and the additional noise is then confirmed from the measurement on transistors with the same width but with different gatelength. Both the noise at the plateau and  $R_{meas}$  increase for the shortest transistors.

- ii) We have chosen two different bias conditions, one with the body grounded (and  $V_{BG}=9V$ ) and the other with the backgate grounded (and  $V_{body}=-0.7V$ ), for which  $R_{meas}$  is the same. The value at the plateau referred to the gate is different, but referring it to the body using (2), we get  $S_{Vgate}^2\approx7.2nV/\sqrt{Hz}$  in both cases. Similar results are obtained for other bias values.

- iii) When the same body and backgate bias is applied in the saturation and ohmic working regimes, the value of R<sub>meas</sub> is the same, whilst the ratio between the transconductances is different. The gate-referred noise at the plateau is therefore different in the two regimes, as shown in table I. The body-referred noise is instead equal within 20%, which is reasonable when considering the error on the measurements and its propagation in the calculations.

Table I: noise at the plateau referred to the gate and body. The body bias was 0V in both cases, and  $R_{meas}$  was equal in saturation and ohmic region for each bias condition.

|              |            | Gate-referred noise at plateau (nV/√Hz) | Body-referred noise at plateau (nV/√Hz) |

|--------------|------------|-----------------------------------------|-----------------------------------------|

| $V_{BG}=13V$ | saturation | 45                                      | 69                                      |

|              | ohmic      | 14.7                                    | 67.1                                    |

| $V_{BG}=12V$ | saturation | 17.5                                    | 25.5                                    |

|              | ohmic      | 6.6                                     | 30.2                                    |

Using the body-referred noise value in (1), we extract  $R_{body}$ . For the two bias values of table I, we get respectively about  $50k\Omega$  ( $V_{BG}=13V$ ) and  $290k\Omega$  ( $V_{BG}=12V$ ). In both cases, this

value is a factor 5 less than  $R_{meas}$ . We insert the extracted resistance values in (3), where  $f_C$  is estimated from the cutoff frequency of the hump in the noise measurement, and we extract the capacitance of the RC circuit to get C=7pF. For the transistor under test,  $C_{ox}=13.5pF$  and  $C_{buriedOx}=1.6pF$ . Considering that for the small signal model of a transistor the capacitance seen from the body is equal to a fraction of the total gate capacitance, the extracted C fits well our RC model.

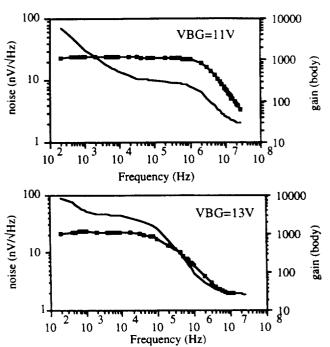

iv) The final evidence that supports our model comes from the gain analysis of the transistor for a signal injected through the body. The hump in the two bias conditions chosen has a different  $f_C$ , as shown in figure 5. As expected from the model, the low pass filter is effective for every signal injected through the body terminal.

Figure 5: noise referred to the gate (solid line) and gain for a signal injected through the body (line with black squares) for two bias conditions.  $V_{body}=0V$ .

Finally, we can use the gain in figure 5 to refer the noise of the same figure to the body terminal. The resulting spectra show no hump, but a white noise whose value is in agreement with the one foreseen by the model.

#### **Conclusion**

We have identified an additional noise source in the spectrum of SOI medium-thickness transistors. Its origin is the resistance of the silicon film which constitutes the body of the transistor, coupled to the gate capacitance to form an RC equivalent low pass filter.

#### References

- [1] J.P.Colinge, Silicon-on-insulator technology: materials to VLSI, Kluwer academic publishers, 1991, p. 109

- [2] T.Ouisse et al., "Investigation of floating body effects in siliconon-insulator metal-oxide-semiconductor field-effect transistors", J. Appl. Physics, Vol. 70, No. 7, pp. 3912-3919, october 1991.

# DEVELOPMENT OF FRONT-END ELECTRONICS FOR SILICON STRIP DETECTORS USING THE DMILL BICMOS RAD-HARD PROCESS.

F. Anghinolfi<sup>a</sup>, W. Dabrowski<sup>a,b</sup>, E. Delagne<sup>c</sup>, P. Jarron<sup>a</sup>, J. Kaplon<sup>a</sup>, F. Lugier<sup>c</sup>, R. Szczygiel<sup>a</sup>

<sup>a</sup> CERN, Geneva <sup>b</sup> Faculty of Physics and Nuclear Techniques, Cracow, <sup>c</sup> CEA, Saclay <sup>d</sup> Institute of Nuclear Physics, Cracow

#### **ABSTRACT**

An overview of development of front-end electronics for silicon strip detectors using the DMILL  $0.8 \mu m$ BiCMOS radiation hard process is presented. The DMILL technology offers an excellent radiation hardness performance for a wide variety of devices: MOSFETs, BJTs, JFETs and high value resistors. Our development follows the two basic readout architecture, analog and binary, considered for the ATLAS Semiconductor Tracker at the LHC. Two 32-channel demonstrator chips: SCT32A for the analog architecture and SCT32B for the binary one have been designed and manufactured successfully. Following the 32-channel demonstrator chips the 128-channel versions of both architectures have been designed. The results obtained for the 32-channel demonstrator chips as well as the designs of the 128-channel versions is presented. The performance of the front-end circuit based on a fast transimpedance BiCMOS preamplifier which has been implemented in both architectures is discussed. Along with the results on fabricated chips the radiation effects in DMILL bipolar transistors is presented.

#### 1. INTRODUCTION

The DMILL technology offers an excellent radiation hardness performance for a wide variety of devices: MOS transistors, fast bipolar transistors, junction field effect transistors and high value resistors with low stray capacitance [1]. It is therefore suitable for mixed signal chip architectures and offers a unique possibility to integrate fast low noise analog circuits and digital functions in a single chip. Our development follows the two basic readout architectures, binary and analog, considered as the baseline and the fall-forward solution respectively for the ATLAS Semiconductor Tracker. As a first step, two 32-channel demonstrator chips: SCT32A for the analog architecture and SCT32B for the binary one have been developed. Based on the results obtained for these demonstrator chips we have designed 128-

channel versions of both readout architectures following the system specification for the SCT readout.

The development of the readout chips was carried on in parallel with the development and radiation hardness study of the DMILL technology. A fast transimpedance front-end amplifier based on a bipolar transistor is employed in both readout architectures. This solution offers a very good noise vs power figure of merit for relatively large detector capacitances, in the range of 15 - 20 pF, as foreseen for the ATLAS tracker. Therefore the noise performance and radiation hardness of bipolar transistors available in the DMILL technology have been studied in detail in order to understand whether these transistors are suitable for our applications and to verify their stability.

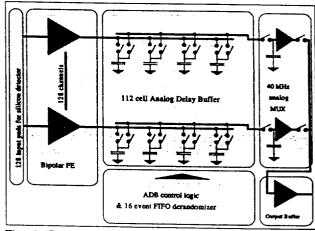

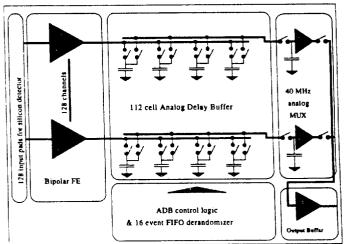

#### 2. ANALOG READOUT ARCHITECTURE

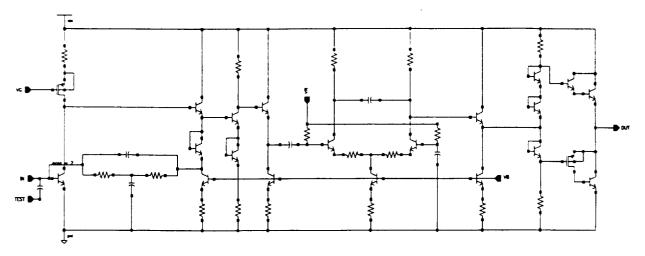

The basic blocks of the analog readout architecture as implemented in the SCT32A and SCT128A chips are shown in fig. 1. The chip comprises four basic blocks: front-end amplifiers, analog pipeline, control logic including the derandomizing FIFO and output multiplexer. The front-end circuit is a fast

Fig. 1. Block diagram of the complete analog readout chip SCT128A.

Fig.2. Schematic diagram of front-end circuit implemented in the SCT128A chip

transimpedance amplifier followed by an integrator, providing a fast semi-gaussian shaping with a peaking time of 25 ns, and an output buffer. The peak values are sampled at 40 MHz rate and stored in a 112-cell deep analog pipeline. The mean amplitude corresponding to 1 MIP input signal is about 70 mV and it is sufficiently high so that the noise figure obtained for the front-end amplifier will not be degraded by the second stage contribution. A storage capacitor of 310 fF for a single cell has been chosen. The concept of the pipeline and of the control logic is similar to the APC3 chip [2].

Once the trigger signal arrives, the analog values from a 128-channel memory column chosen by the read pointer are read out via the output multiplexer. The delay between the write pointer and trigger pointer is tuneable between 2 µs and 2.5 µs. In the first 32-channel version a moderate speed multiplexer working up to 10 MHz has been implemented to test the performance of the front-end circuit and the analog pipeline. For the 128-channel version a 40 MHz multiplexer has been designed which allows to multiplex 256 channels (2 chips) onto one optical link for the level 2 trigger rate of 100 kHz as foreseen for the ATLAS experiment.

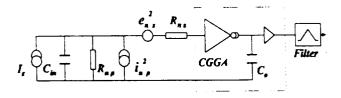

#### 1.1. FRONT-END CIRCUIT

The front-end circuit is based on a transimpedance amplifier with a bipolar input transistor since for large detector capacitances and short shaping time constants bipolar devices offer a superior noise vs power figure of merit [3]. The schematic diagram of the preamplifier-shaper circuit is shown in fig. 2. The input stage designed as a BiCMOS transimpedance amplifier is followed by a single gain stage and an integrator providing the proper peaking time. The output stage is designed as a class AB amplifier and provides sufficient driving capability to drive the analog pipeline at relatively low quiescent current of 100 µA. The total power dissipation of the front-end circuit, including the

output buffer is below 1.5 mW/channel for a collector current of 200  $\mu A$  in the input transistor.

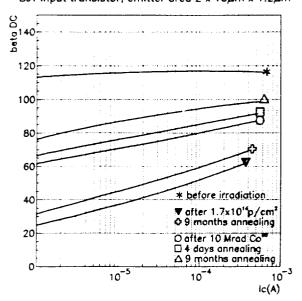

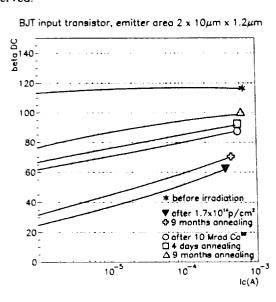

There are two critical issues concerning bipolar transistors which determine their low-noise and radiation hardness performance, i.e. the base spread resistance and the degradation of current gain factor  $\beta$  caused by radiation damage. Radiation tests performed on individual bipolar transistors manufactured in the DMILL technology have shown a similar behavior of  $\beta$  as observed for other bipolar technologies [4], i.e. the  $\beta$  is more degraded when the current density is low. The size of the input transistor has to be optimized taking into account the series voltage noise contribution from base spread resistance and the parallel current noise due to the base current. The later will increase after irradiation since we need to keep a constant value of the collector current in order to keep the voltage noise low.

Transistors of different emitter area from 1.2 x 1.2  $\mu m^2$  up to 2 x 1.2 x 10  $\mu m^2$  have been tested. For all types of transistors the base spread resistance has been evaluated from the noise measurements. Based on the radiation test results of individual transistors we have chosen a geometry for the input device which provides a relatively low value (of the order of 100  $\Omega$ ) of the base spread resistance and a reasonable high current density.

The degradation of the current gain factor  $\beta$  for the transistor geometry as used in the input stage after different radiation tests is shown in fig. 3. One set of devices was irradiated with photons in a Co-60 source up to a total dose of 10 Mrad and the other one in a high energy proton beam up to a total fluence of 1.7 x 10<sup>14</sup> p/cm<sup>2</sup>. In both cases the devices were kept under bias during and after irradiation at the room temperature. For the nominal collector current of 200  $\mu$ A as foreseen for the input transistor the  $\beta$  is still above 60 after irradiation to the maximum doses expected for the ATLAS Semiconductor Tracker. This value of  $\beta$  is sufficiently high so that the parallel shot noise of the base current will not be a limiting factor after these extreme radiation

BJT input transistor, emitter area  $2 \times 10 \mu m \times 1.2 \mu m$

Fig. 3. Degradation of the current gain factor  $\beta$  for the transistor geometry used for the input device.

doses. At room temperature a long term annealing is clearly visible for both sets of devices.

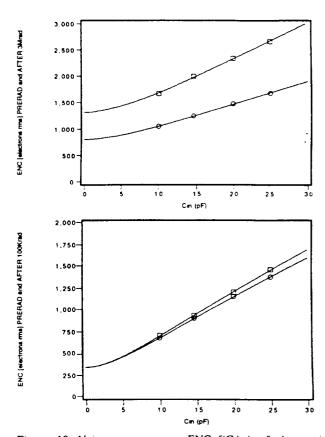

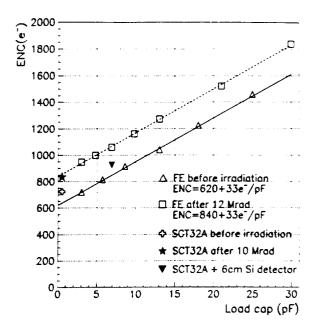

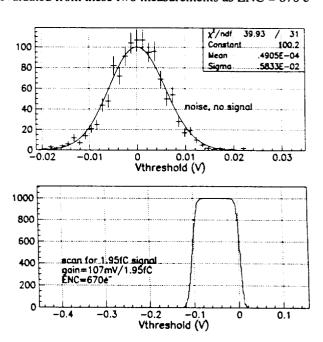

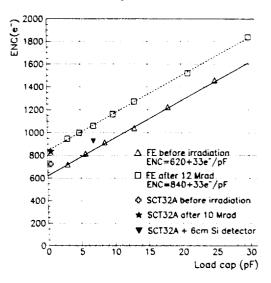

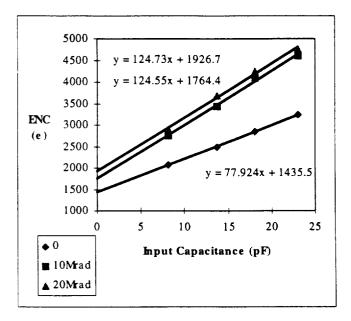

#### 2.1. NOISE MEASUREMENTS

The noise measurements have been performed for the front-end circuit standing alone as well as for the full chip operating at a nominal clock frequency of 40 MHz. For the front-end amplifiers not connected to the pipeline the noise figures of ENC = 620 e + 33 e/pF has been obtained before irradiation and ENC = 840 e + 33 e/pF after 12 Mrad of gamma irradiation for a collector current of 220  $\mu A$  in the input transistor. Performing the noise measurements while reading the signal and noise via the complete readout chain, including the pipeline clocked at 40 MHz and the multiplexer, a noise figure of 720 e' was obtained for zero input capacitance. The noise (without signal) was measured reading randomly the cells of the pipeline so the measured value includes fluctuations introduced by cell-to-cell variation of the pipeline. Comparing the results of these two measurements, without the pipeline and with the pipeline, we obtain the cell-to-cell amplitude variation of 1 mV rms, to be compared with the 70 mV signal amplitude for 1 MIP input signal.

The obtained results indicate that additional sources of fluctuations, i.e. the pick-up of digital noise and the non-uniformity of pipeline storage cells, add only a marginal contribution to the noise figure of the front-end amplifier. For the detector capacitances of the order of 15 pF, as foreseen for the ATLAS Semiconductor Tracker, we do not expect any significant contribution from these additional noise sources.

Fig. 4. Summary of noise measurement performed for the BICMOS front-end only or with the full chip running.

The results of various noise measurements are shown in fig. 4. The noise figure obtained for the chip connected to a 6 cm long strip detector is consistent with other measurements performed for discrete capacitors connected to the input.

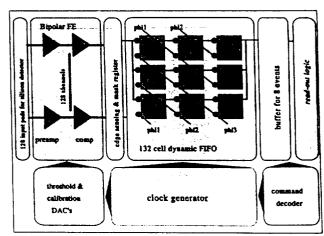

#### 3. BINARY READOUT ARCHITECTURE

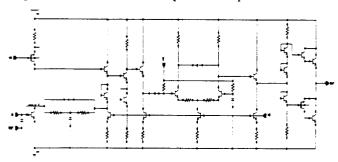

The block diagram of binary readout architecture realized in SCT32B and SCT128B chips is shown in fig. 5. The preamplifier and shaper implemented in this architecture use the same concept as used for the frontend in the analog architecture. The shaper is followed by a discriminator providing only 1-bit yes/no information which is stored into a 128-cell deep FIFO module.

Fig. 5. Block diagram of the complete binary readout chip SCT128B

Fig. 6. Schematic diagram of the binary front-end circuit implemented in the SCT128B chip.

The SCT128B chip has been designed following the specification for the binary readout architecture. Originally the binary readout architecture has been proposed for the ATLAS semiconductor tracker by former SDC collaboration as a two separate chip solution, bipolar front-end and CMOS digital pipeline. The DMILL process allows us to implement both, the front-end and the binary pipeline in a single chip. The SCT128B chip, in addition to the basic functional blocks mentioned above, comprises in addition a calibration circuitry for internal generation of calibration pulses, one DAC for control of the amplitude of calibration pulses, another DAC for control of the discriminator threshold, and a 8-bit deep derandomizing readout buffer. The back-end control and readout logic is compatible with the HAC chip architecture [5].

#### 4.1. BINARY FRONT-END CIRCUIT

The front-end circuit for binary readout architecture includes, in addition to the preamplifier and shaper, a discriminator. The schematic diagram of the front-end circuit implemented in the SCT128B chip is shown in fig. 6. The preamplifier is the same transimpedance BiCMOS configuration as used in the analog architecture. A key issue for the binary architecture is the channel-to-channel matching of gain, noise, and dc levels at the shaper output since a common threshold is applied for all 128 channels. The required uniformity is obtained by: (i) an ac coupling between the amplifier and the discriminator so that the dc offsets originated in the front-end circuit, which is a single ended structure due to noise requirements, are cut off, (ii) high enough gain in the preamplifier-shaper circuit, of the order of 100 mV/fC, so that the input offsets in the discriminator are negligible compared to the signal amplitude, (iii) applying a differential scheme for setting the discriminator threshold so that common mode effects are canceled.

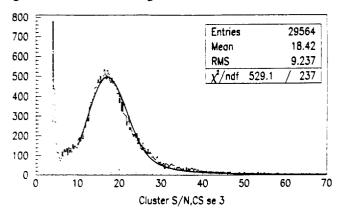

The noise and gain measurements for a typical channel are shown in fig. 7. The upper plot shows the noise occupancy as a function of threshold applied to the discriminator. Since the threshold is applied differentially, the discriminator is sensitive either to positive or to negative pulses depending on the setting. By scanning the effective differential threshold around zero a full gaussian distribution of noise is obtained as shown in fig.7. From another threshold scan for a given signal applied to the input (lower plot) the signal amplitude at the input of discriminator and so the gain of the front-end circuit is measured. The noise figure can be evaluated from these two measurements as ENC = 670 e

Fig. 7. Noise and gain measurement for a single channel of the SCT32B chip. The number of noise counts when no signal is applied and the number of signal counts is plotted as a function of the discriminator threshold voltage.

for the zero input capacitance. This value agrees well with the number obtained for the analog chip SCT32A in which a similar front-end circuit has been implemented. Also for the binary architecture we do not observe any significant noise increase when the chip is fully operating at 40 MHz clock frequency.

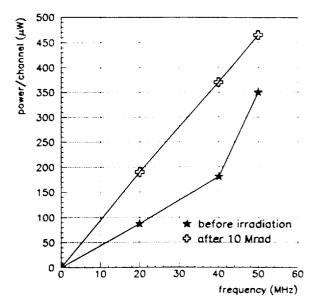

#### 4.2. BINARY PIPELINE

The binary pipeline is realized as a multiplexed FIFO circuit. The principle of operation of this circuit is shown schematically in fig. 8. An array of  $n \times n$  dynamic memory cells is controlled by n non-overlapping clock signals. In each clock cycle only n cells out of  $n \times n$  are switched while the effective delay provided by such a block is equal  $n \times (n-1)$  clock cycles. The applied architecture results in two very valuable features: low power consumption and a very compact layout. The pipeline block of 128 channels, each 132-bit deep, occupies only the area of 9 mm². The expected power consumption for this block is of the order of 140  $\mu$ W/channel at clock frequency of 40 MHz and does not depend on the data rate.

Fig. 8. Circuit principle of the binary pipeline based on a multiplexed FIFO circuit.

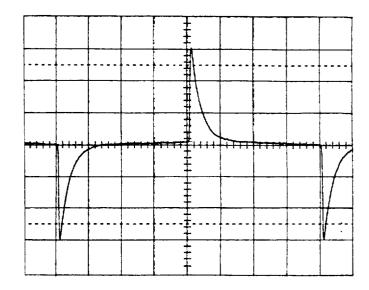

The chip has been irradiated in Co-60 source up to 10 Mrad under nominal static bias. The main goal of this test was to check the radiation hardness of the digital pipeline structure. The chip has been tested successfully at different clock frequencies up to 50 MHz before and after irradiation. After irradiation an increase of the power consumption is observed as expected (fig. 9). The measured power shown in fig. 9 is higher compared to the expected 140  $\mu$ W/channel but it includes a contribution from the ECL-to-CMOS converters for the clock and control signals implemented in the SCT32B. In the final design the clock and signal receivers will be designed according to the LVDS standard resulting in a lower power consumption.

Fig. 9. Power consumption per channel of the 132-bit deep pipeline as a function of clock frequency before and after irradiation in Co-60 source up to 10 Mrad. The measured values include the power consumption of the ECL-to-CMOS clock and control signal receivers.

#### 4. CONCLUSIONS

The results obtained for the prototype chips SCT32A and SCT32B prove that the DMILL technology offers the performance and appropriate radiation hardness required for the readout electronics for the ATLAS Semiconductor Tracker. The completed designs of the full size 128-channel chips, SCT128A and SCT128B, show that the DMILL technology is suitable for either readout architecture.

#### REFERENCES

- M. Dentan et al., First Workshop on Electronics for LHC Experiments, CERN/LHCC/95-56, 1 October 1995, p.41.

- K. Borer et al., IEEE Trans. Nucl. Sci. NS-41/4 (1994) 1091.

- P. Jarron et al., First Workshop on Electronics for LHC Experiments, CERN/LHCC/95-56, 1 October 1995, p.130.

- 4. P. Barberis et al., Nucl. Phys. B32 (1993) 540.

- J. DeWitt, IEEE Nuclear Science Symposium, Conference Record, Vol.2, p. 749, San Francisco 1993.

# SCTA - A Rad-Hard BiCMOS Analogue Readout ASIC for the ATLAS Semiconductor Tracker

F. Anghinolfi<sup>1</sup>, W. Dabrowski<sup>1,3</sup>, E. Delagnes<sup>2</sup> J. Kaplon<sup>1</sup>, U. Koetz<sup>1,4</sup>, P. Jarron<sup>1</sup>, F. Lugiez<sup>2</sup>, C. Posch<sup>1</sup>, S. Roe<sup>1</sup> and P. Weilhammer<sup>1</sup>

<sup>1</sup>CERN, 1211 Geneva 23 Switzerland <sup>2</sup>CEA DAPNIA, Saclay, France

<sup>3</sup> Faculty of Physics and Nuclear Techniques, al. Mickiewicza 30, 30-059 Cracow, Poland <sup>4</sup>DESY, D-22603 Hamburg, Germany

#### Abstract

Two prototype chips for the analogue readout of silicon strip detectors in the ATLAS Semiconductor Tracker (SCT) have been designed and manufactured, in 32 channel and 128 channel versions, using the radiation hard BiCMOS DMILL process. The SCTA chip comprises three basic blocks: frontend amplifier, analogue pipeline and output multiplexer. The front-end circuit is a fast transresistance amplifier followed by an integrator, providing fast shaping with a peaking time of 25 ns, and an output buffer. The front end output values are sampled at 40 MHz rate and stored in a 112-cell deep analogue pipeline. The delay between the write pointer and trigger pointer is tunable between 2 µs and 2.5 µs. The chip has been tested successfully and subsequently irradiated up to 10 Mrad. Full functionality of all blocks of the chip has been achieved at a clock frequency of 40 MHz both before and after irradiation. Noise figures of ENC = 720 e + 33 e/pF before irradiation and 840 e + 33 e/pF after irradiation have been obtained.

#### I. INTRODUCTION

The readout of silicon tracker systems for the LHC experiments requires high density multichannel mixed signal ASICs combining several analogue processing functions with high speed digital circuits. The analogue readout of tracker systems with several millions of channels requires the use of low power design techniques such as the analogue memory CMOS circuit which locally store analogue signals during the level 1 trigger latency [1], [2], [3], [4], [5], [6]. The analogue memory technique performs simultaneous read and write operations enabling detector readout without dead time. We present here an approach based on the same architecture principle as developed before, but the analogue front end has been designed with bipolar devices available in the DMILL technology [7]. The DMILL technology offers an excellent radiation hardness performance [8], [9] for a wide variety of devices: MOS transistors, fast bipolar npn transistors, junction field effect transistors and high value resistors with low stray capacitance. It is therefore suitable for mixed signal chip architectures and offers a unique possibility to integrate fast low noise analogue circuits and digital functions on a single chip.

In the DMILL technology we have at our disposal all three types of transistors, JFET, MOSFET and BJT, which can be used as input devices. The *npn* bipolar transistor offers

the highest  $g_m/I_c$  ratio and the lowest input capacitance. For this reason, the *npn* bipolar transistor is intrinsically the best input device for a low noise preamplifier when the series noise contribution dominates. This is a particularly relevant issue for silicon strip trackers at the LHC with a typical strip capacitance of 20 pF and signals with a peaking time of 25 ns in the front-end signal processor.

For comparison of the noise performance between frontend systems with the bipolar and the MOS transistor we assume triangular shaping offering an effective noise suppression for both series and parallel noise sources. For a readout system using a bipolar input device biased with collector current I<sub>c</sub> the equivalent noise charge (ENC) is given as

ENC =

$$\sqrt{\frac{4kT(r_{bb} + \frac{kT}{2qI_c})(C_a + C_d)^2}{T_p} + \frac{2qI_cT_p}{3\beta}}$$

(1)

where  $r_{bb}$  is the base spread resistance and  $\beta$  is the current gain factor of the input transistor,  $C_a$  is the amplifier input capacitance, typically below 0.5 pF,  $C_d$  is the detector capacitance and  $T_p$  is the peaking time of the filter. The parallel noise contribution from the feedback resistor is ignored here since for an optimized preamplifier this contribution is negligible.

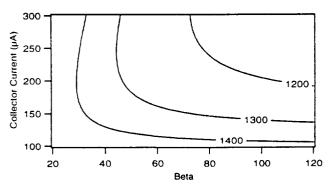

For a given peaking time, detector capacitance and current gain factor one can find an optimum value of the collector current which gives the minimum noise. Degradation of the  $\beta$  factor due to radiation damage of the bipolar transistors should be taken into account as this will result in some degradation of noise and a different optimum value of the collector current. The contour plot of constant ENC as a function of the collector current and  $\beta$  factor is shown in fig. 1.

The plot shown in fig. 1. indicates that a noise below 1200 e rms can be obtained for a detector capacitance of 20 pF and a relatively low collector current, about 200  $\mu$ A. A degradation of  $\beta$ , even down to 50 as expected for DMILL transistors irradiated up to  $2\times10^{14}$  p/cm², causes only a minor increase in noise (up to 1300 e rms). Accepting this increased noise one can then use the transistor with a lower collector current, about 150  $\mu$ A. The low value of the optimum collector current matches the low power requirements of the Atlas Semiconductor Tracker readout very well.

Figure 1: Constant noise contours for a bipolar input transistor and ideal triangular shaping of 25 ns peaking time. Base spread resistance of 50  $\Omega$  and detector capacitance of 20 pF is assumed.

For a MOS input device and triangular shaping the equivalent noise charge is given as

$$ENC = \sqrt{\frac{4kT\frac{2\Gamma}{3g_m}(C_a + C_d)^2}{T_p}}$$

(2)

where  $g_m$  is the transconductance,  $\Gamma$  is the excess noise factor and C, is the input capacitance of the input MOS transistor. Compared with a bipolar transistor the amplifier input capacitance is not negligible since a large Width/Length ratio (W/L) for the input transistor is required to give a high transconductance. Given a minimum length allowed by the technology and short channel effect a large W/L can be obtained by increasing the width and so the total gate area. For a comparison of the noise vs power figure of merit, it is important to notice that transconductance is proportional to collector current in a bipolar transistor while for a MOS transistor it is proportional only to the square root of the drain current. Thus for a given detector capacitance and shaping time there are two parameters, the width of the input transistor and the drain current which should be optimized in a system using MOS input transistors.

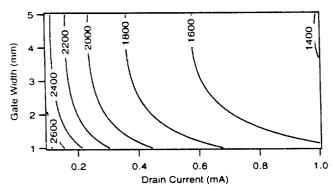

The constant ENC contour plot for typical parameters of a PMOS transistor in a submicron technology is shown in fig.2.

Figure 2: Constant noise contours for a PMOS input transistor, ideal triangular shaping of 25 ns peaking time and a detector capacitance of 20 pF. Minimum gate length of 1.5  $\mu$ m, gate capacitance of 1.5 fF/ $\mu$ m<sup>2</sup> and  $\Gamma$  factor of 1.5 has been assumed.

The contour plot shows that an ENC of 1800 e rms is achieved for a drain current of 400  $\mu$ A and a gate width ranging from 2000  $\mu$ m to 4000  $\mu$ m. This result indicates that with a bias current twice as high in the MOS device, the minimum achievable noise is still 60% more than for a bipolar device. The lower series noise factor, 1/2 for a bipolar device compare to 1 for a p-channel MOS, and the lower input capacitance, 0.5 pF for a bipolar device and 5 pF for a large p-channel MOS input device explain this significant difference in noise performance.

In addition, radiation damage increases the series noise factor of the MOS transistor whereas bipolar series noise is unchanged. The additional parallel noise caused by the beta drop of an NPN device in the DMILL process, typically  $100 \text{ to } 60 \text{ after } 2 \times 10^{14} \text{protons/cm}^2$ , is not significant when compared to the detector shot noise after irradiation.

The measurements of ENC versus C<sub>d</sub> for a bipolar transistor as shown later in sect. IV indicate that the contributions from parallel and series noise add almost linearly. This indicates that the two noise sources in a bipolar transistor are significantly correlated for high frequencies. For a relatively large detector capacitance, about 20 pF, this effect does not play a major role since the total noise is dominated by the series noise.

#### II. CHIP ARCHITECTURE

Fig. 3 shows the block diagram of the SCTA chip architecture which has been designed in two versions, 32 channels and 128 channels. The chip comprises four basic blocks: front-end amplifier, analogue pipeline, control logic including a derandomizing FIFO, and an output multiplexer. The front-end circuit is a fast transresistance amplifier followed by an integrator, providing a semi-gaussian shaping with a peaking time of 25 ns, and an output buffer. The peak values are sampled at 40 MHz rate and stored in the 112-cell deep analogue pipeline. The mean amplitude obtained for a 1 MIP input signal is about 100 mV. It is sufficiently high that analogue signal processing after the front end does not contribute significantly to the overall noise figure.

Figure 3: Block diagram of the SCTA - a full analogue readout chip.

#### A. BiCMOS preamplifier Shaper

The front-end circuit is based on a transresistance amplifier with a bipolar input transistor for the reasons presented in sec. I. The schematic diagram of the preamplifier-shaper circuit is shown in fig. 4. The input stage designed as a BiCMOS transimpedance amplifier is followed

Figure 4: Schematic diagram of the front-end circuit implemented in the SCT128A chip.

by a single gain stage and an integrator providing the proper peaking time. The output stage is designed as a class AB amplifier and provides sufficient capability to drive the analogue pipeline at a relatively low quiescent current of  $100~\mu A$ , so no extra write amplifier is needed in front of the analogue pipeline.

The transresistance preamplifier is built around a single ended NPN feedback pair circuit configuration which offers a low noise characteristic associated with a sufficient gain-bandwidth product. A phase margin of about 70° is achieved by a compensation network associated with the feedback resistor. The load of the input device is built with a p-channel MOS degenerated current source which offers a low output conductance and parasitic capacitance.

#### B. Analogue memory

The SCT128A memory samples the analogue signal voltage from the front end every 25 ns into a storage capacitor of 310 fF. The system performs a very simple and reliable voltage sampling. The readout need only retrieve the sample belonging to the peak of the pulse to recover the full time and amplitude information. Once the trigger signal arrives, the analogue values from the pointed physical address of the 128-channel memory column are read out via the output multiplexer. The delay between the write pointer and trigger pointer is tunable between 2  $\mu$ s and 2.5  $\mu$ s in the present version of the circuit.

#### C. Control logic of the analogue memory

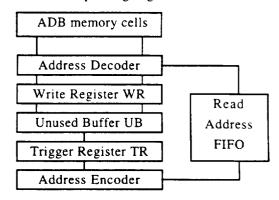

Refering to fig. 5. the pipeline control of the memory allocation is done by two registers clocked at 40 Mhz, the Write column Register WR and the Trigger column Register TR, and one buffer, the Unused column Buffer UB. Register pointers have a delay between them such that the TR pointer passes memory cells later than the WR pointer by a delay equal to the trigger latency. The WR pointer controls writing of data into unused columns. The TR pointer sets a flag in the

UB buffer at the request of an external trigger signal. The UB buffer thus holds flags to memory columns belonging to successive triggers. Because the readout time is generally longer than the loop pointer time, WR and TR pointers skip over columns where flags are set in the UB buffer. Each time a trigger generates a flag in the UB buffer, the Address Encoder generates the 7-bit binary address of the column. The encoded words are stored in the Read Address FIFO. Once a read signal is received, the first available address in the FIFO is decoded through the Address Decoder, enabling the readout of the column. The decoding of this address is used to free the corresponding flag in the UB buffer.

Figure 5: Block diagram of the memory control logic.

#### D. Analogue Multiplexer

The multiplexer chip contains 128 channels with sampleand-hold circuits and the output buffer. Each channel consists of an input switch, a storage capacitor and a sample-and-hold buffer designed as a source follower based on an NMOS transistor biased with 50 µA. In the readout phase this current is increased in the readout channel up to 600 µA which is sufficient to drive the parasitic capacitance of the internal bus line of the multiplexer. To provide a driving capability for 40 MHz operation of the chip placed on the final hybrid when the load capacitance is in the range of 60 pF, an additional output stage was necessary. A PMOS source follower biased with 5 mA current has been employed as an output buffer. The multiplexing function is implemented as a simple array of 128 NMOS switches controlled by a shift register. The 32channel SCTA version has a moderate speed multiplexer working up to 10 MHz.

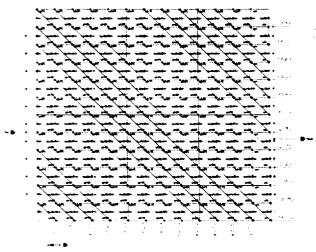

#### III. CHIP LAYOUT

The two versions, 32 channels and 128 channels, have essentially the same floor planning. Fig. 6 shows a photo of the 128 channel version, SCT128A. The front-end channels and the analogue pipeline are laid out with a pitch of 50  $\mu$ m. The BiCMOS circuitry implemented in the front-end results in a very compact layout so that the front-end channel is only 800  $\mu$ m long. The input bonding pads are laid out with 50  $\mu$ m pitch. The die size is  $9.3\times6.9$ mm².

Figure 6: Photo of the SCT128A chip implemented in the DMILL BiCMOS process

#### IV. EXPERIMENTAL RESULTS AND PERFORMANCES

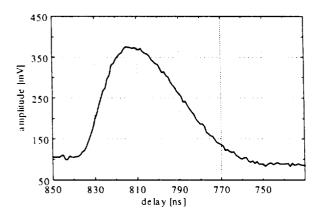

#### A. Output Signal