SCP CERN DRDC 91-10 CERN LIBRARIES, GENEVA

SC00000113

EUROPEAN ORGANIZATION FOR NUCLEAR RESEARCH

CERN/DRDC 91-10 DRDC/P26 7 March 1991

**R&D** Proposal

## DEVELOPMENT OF HIGH RESOLUTION Si STRIP DETECTORS FOR EXPERIMENTS AT HIGH LUMINOSITY AT THE LHC

H. Borner, P. Jalocha, W. Lange, H.G. Moser, E. Nygård, J. Straver, P. Weilhammer<sup>\$</sup>, K. Yoshioka *CERN, Geneva, Switzerland*

A. Czermak, W. Dabrowski, S. Gadomski, K. Pakonski, M. Turala Institute of Nuclear Physics, Cracow, Poland

R. Brenner<sup>\*</sup>, I. Hietanen, J. Lindgren, R. Orava, C. Rönnquist, T. Tuuva University of Helsinki, Helsinki, Finland

> G. Hall, M. Raymond, S. Roe, R. Wheadon Imperial College, London, U.K.

> > T. Buran University of Oslo, Oslo, Norway

B. Avset, L. Evensen, A. Kjensmo, H. Von Der Lippe S.I., Oslo, Norway

M. Tyndel Rutherford-Appleton Laboratory, Chilton, Didcot, U.K.

> J.D. Berst, W. Dulinski, M. Schaeffer LEPSI, Strasbourg, France\*\*

> > P. Giubellino, L. Ramello INFN, Turin, Italy\*\*\*

R. Harr Yale University, New Haven, USA

\$ Spokesman

\* At CERN from 1.5.91

\*\* Pending approval of IN2P3 and ULP-Strasbourg

\*\* Pending approval of INFN

## Abstract

Recent studies indicate that good tracking near the interaction region in LHC experiments will be crucial to fully exploit the physics potential of this machine up to the highest luminosities. It is believed that Si strip detectors are among the best candidates to survive in the experimental environment imposed by the high energy, high luminosity and the severe radiation levels expected.

It is therefore proposed to perform a systematic study of the feasibility of using Si strip detectors and suitably designed front-end electronics for tracking in LHC experiments.

Issues discussed here are possible physics applications, requirements and design characteristics for Si strip detectors and front-end electronics and cooling. An R&D programme for the coming two years is described.

Everything should be made as simple as possible, but no simpler.

Albert Einstein, 1879 · 1955

ü

# **Table of Contents**

| 1. INTRO  | DDUCTION                                                                                                                                            | 1              |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1.1       | Tracking at LHC                                                                                                                                     | 1              |

| 1.2       | Scope of Proposal                                                                                                                                   | 2              |

| 2. POSSI  | BLE APPLICATIONS                                                                                                                                    | 4              |

| 2.1       | Tracker and Vertex Detector for Luminosities of $10^{34}cm^{-2}sec^{-1}$ 2.1.1       Proposed Design         2.1.2       Performance Considerations | 4              |

| 2.2       | Tracking for Heavy Ion Experiments at LHC and SPS2.2.1Physics with Heavy Ions at LHC2.2.2Fixed Target Experiments with Pb Beams at SPS              | 8              |

| 2.3       | A Dedicated Beauty Experiment at the LHC                                                                                                            | 11             |

| 3. SI STR | IP DETECTORS                                                                                                                                        | 12             |

| 3.1       | Performance Specifications                                                                                                                          |                |

| 3.2       | Choice of Technology                                                                                                                                |                |

| 3.3       | Specific R&D Projects                                                                                                                               | 16             |

| 4. FRON   | T-END ELECTRONICS                                                                                                                                   | 19             |

| 4.1       | Constraints                                                                                                                                         | 19             |

| 4.2       | Aims of the Readout Electronics                                                                                                                     | 19             |

| 4.3       | Proposed Methods to be Used                                                                                                                         | 20             |

| 4.4       | Suggested Implementation                                                                                                                            | 20             |

| 4.5       | Choice of Technology                                                                                                                                | 22             |

| 4.6       | Specifications                                                                                                                                      | 22             |

| 4.7       | Discussion on the Choices of Methods                                                                                                                | 23             |

| 4.8       | Specific R&D Projects                                                                                                                               | 24             |

| 5. PREC   | ISION MOUNTING, MECHANICS AND COOLING                                                                                                               | 26             |

| 5.1       | Cooling<br>5.1.1 Specific R&D Projects                                                                                                              | 26<br>27       |

| 5.2       | Microbump Bonding<br>5.2.1 Solder-Bump Bonding<br>5.2.2 Resin Technology<br>5.2.3 Conducting Glue Drops                                             | 27<br>27<br>28 |

| 6. MANI   | POWER, INFRASTRUCTURE AND FUNDING                                                                                                                   | 30             |

|           |                                                                                                                                                     |                |

| 7. REQU   | ESTS TO CERN                                                                                                                                        | 32             |

| APPENDIX A. | DESIGN REQUIREMENTS FOR SILICON DETECTOR<br>AND READOUT CHIPS FOR THE LHC BEAUTY | ۷S |

|-------------|----------------------------------------------------------------------------------|----|

|             | EXPERIMENT                                                                       | 33 |

| APPENDIX B. | FRONT-END ELECTRONICS:                                                           |    |

|             | REQUIREMENTS AND PERFORMANCE                                                     |    |

|             | SPECIFICATIONS                                                                   | 35 |

|             | PROPOSED CHIP AND SYSTEM SOLUTION                                                | 42 |

| APPENDIX C. | REQUIREMENTS FOR A COOLING SYSTEM AND                                            |    |

|             | AVAILABLE TECHNOLOGIES                                                           | 48 |

## 1. INTRODUCTION

## 1.1 Tracking at LHC

The construction of high-luminosity, high-energy hadron colliders within the next decade is by now recognized to be the top priority in high energy physics. It is realistic to assume that a machine like the LHC can perform at luminosities of above  $10^{33}cm^{-2}sec^{-1}$  and may reach extreme luminosities of above  $10^{34}cm^{-2}sec^{-1}$  in order to shed light on new phenomena in physics. Possible physics scenarios attainable with such accelerators have been widely discussed [1.1, 1.2]. In the boson sector, the discovery of the standard model neutral Higgs or of charged Higgs doublets would be of prime importance. In the fermion world, the top quark awaits discovery, which may happen before at the Tevatron collider (present limits on the top mass from CDF, UA1, UA2 and LEP seem to push it out of the range of 200GeV LEP). In this case, however, a detailed study of the properties of the t quark [1.3] will be a realistic physics goal for an LHC. Other scenarios predict the appearance of supersymmetric particles, technicolour particles, composite W and Z bosons, ... at LHC energies.

1

Whereas it seems feasible how to build high luminosity machines, there is much more uncertainty at present how to build detectors which are capable of measuring the outcome of interactions at these extreme energies and luminosities. This proposal addresses the question if Si strip detectors are suitable for tracking in an LHC environment. It is assumed that tracking is necessary - at least in some detectors - up to the highest possible luminosities in order to fully exploit the physics potential of the LHC. Many arguments in favour of the necessity of good tracking have been made recently [1.3,1.4,1.5,1.6]. These will not be repeated here. However, in order to explain the scope of this proposal, a few physics cases are mentioned here, which have been considered for guidance to develop ideas for a R&D programme on Si strip detectors to be used for tracking at LHC.

Tracking will be essential for processes with interesting fermions, which have relatively high cross-section, but are nevertheless buried in very high backgrounds. E.g., it is argued that for top quark masses up to 300 or 400GeV LHC is a top factory able to produce up to 10<sup>6</sup>  $(m_t = 350GeV)$  or  $10^7$   $(m_t = 200GeV)$  events per year at  $\mathscr{L} = 10^{33}cm^{-2}sec^{-1}$ . In studying these t particles, b meson tagging with a very precise vertex detector will be important to enhance signals above background. B particles are copiously produced at LHC. High statistics clean event samples can be obtained using a very high performance vertex detector tagging these events by the B decay vertex. Enough statistics may be available even after a very rigorous selection using vertex criteria to allow a study of possible CP violation effects in the Bsector. This requires a reasonable statistics sample of fully reconstructed decays in a defined CP eigenstate. For processes with interesting bosons, e.g. the standard neutral Higgs decaying into 4 leptons via  $Z^0Z^0$  or  $H \rightarrow \gamma\gamma$  decay, highest luminosities will be needed to have a few detectable events. For this case, it is extremely difficult to predict if global tracking can still be done ( $\mathscr{L} \geq 10^{34}cm^{-2}sec^{-1}$ ), but it nevertheless seems essential to have some tracking information to allow association of tracks which are identified in calorimeters or filters as leptons or associate leptons or  $\gamma$ 's with the correct primary vertex. A further point under consideration is that at very high luminosities multiple interactions in one bunch crossing need tracking information near the vertex to separate the primary vertex of the interesting events from several other minimum bias event vertices.

A non-exhaustive list of topics where high precision tracking near the vertex will be required is listed here :

- Primary vertex identification.

- Impact parameter measurement at the primary vertex with high precision for leptons and hadrons from heavy flavour decays.

- Full reconstruction of secondary vertices from inclusive and exclusive decays of heavy flavours.

- Separation of several primary vertices within one bunch crossing.

- Momentum measurement of charged particles.

- Lepton identification in conjunction with a calorimeters and  $\mu$  filters.

- $\gamma$  conversion rejection together with e calorimetry.

- Association of identified leptons with proper primary vertex.

- Identification of topologies, e.g. very high  $p_T$  jets, charged particle multiplicity, . .

- Measurement of jet thrust axis.

- Use of track information in second level trigger.

- . . . .

## 1.2 Scope of Proposal

Si detectors are considered to be good candidates of tracking detectors which can operate in an LHC environment. The speed of charge collection in Si, typically about 30nsec for  $300\mu m$  thick detectors, the radiation hardness and the possibility to have fine granularity almost at will predestines Si strip detectors (and clearly also Si pixel detectors) to fulfil the requirements for their use at high luminosity and very high track densities expected for LHC experimentation. Existing experience with the Si vertex detectors of ALEPH and DELPHI experiments at LEP is very encouraging concerning their capability of high precision tracking. It is however clear that none of the existing devices could be used straightforwardly in an LHC environment. For both detectors and front-end electronics, the requirements, in particular radiation hardness and speed, are so much more demanding at LHC that an intensive R&D programme is necessary to prove that these devices can indeed be used in LHC experiments. Similarly, one has to extrapolate from existing trackers by at least a factor of 10 to 20 in size, so that totally new systems aspects, e.g. mechanical stability, radiation hardness of support materials, alignment, quality control, etc. have to be considered.

The purpose of this proposal is to show areas where R&D work has to be done on specific components of a Si tracking device and propose specific projects to solve open questions. It is not intended to propose at this time to build a prototype of a Si tracker for an LHC experiment, but to study the performance of all the necessary components under conditions as expected around the beam pipe of an LHC interaction region.

Included in this study are applications for experiments both with protons and with heavy ions, including SPS heavy ion experiments. In order to evaluate the requirements on the detector components, a model of a possible Si tracker for each application is defined to serve as a test ground and to understand which system aspects have to be worked on. It is intended to arrive at the end of an about 2 year long R&D programme, which is the subject of this proposal, at a precise specification of a Si tracker for the different applications. It is expected that the construction of a full prototype system will be proposed as an outcome of this work.

#### References

- [1.1] Proc. of ECFA Study Week on Instrumentation Technology for High Luminosity Hadron Colliders, Vol. 2, CERN 89-10 ECFA 89-124, Nov. 1989.

- [1.2] Large Hadron Collider Workshop, Aachen, Oct. 1990, CERN 90-10, ECFA 90-133, Vol. I, Dec. 90 and Vol. II.

- [1.3] F. Badeschi et al., Top Quark Physics with B-Tagging at LHC. ECFA Aachen, Vol. III, p.268.

- [1.4] G. Tonelli et al., Silicon Tracking at High Luminosity. ECFA Aachen, Vol. III, p.285.

- [1.5] D. Saxon, Track and Vertex Detection. ECFA Aachen, Vol. I, p.339.

- J. Hylen et al., Silicon Tracker Conceptual Design Report. SCIPP 90/24, JHV-HEP-90-0831, CALTEC 68-1673, Sept. 90.

## 2. POSSIBLE APPLICATIONS

## 2.1 Tracker and Vertex Detector for Luminosities of 10<sup>34</sup>cm<sup>-2</sup>sec<sup>-1</sup>

### 2.1.1 Design Concept

Physics requirements ask for a first coordinate determination with the highest possible accuracy as close as possible to the interaction point. This requirement has however to be confronted with the limited radiation hardness of detectors and front-end electronics and technical limits to the finest achievable granularity of strips which determine the quality of two-track separation. The approach in this study aims at full functioning of the detector at the highest luminosities (of and above  $10^{34}cm^{-2}sec^{-1}$ ) but also takes into consideration that a large amount of very important physics (in the fermion sector) can already be done at a luminosity of  $10^{33}cm^{-2}sec^{-1}$ . Since, to present knowledge Si strip detectors can survive about 3 years of continuous opera-tion at  $\mathcal{L} = 10^{34}cm^{-2}sec^{-1}$  with still reasonable performance (see Chapters 3 and 4 of this pro-posal), it is assumed that a first layer of detectors can be placed approximately at r = 10cm. It may have to be foreseen that the one or two innermost layers of a realistic detector are con-structed in a modular way, so that they can be exchanged every 2 or 3 years, or whenever their performance has degraded below a certain required level.

An optimal design for a tracker/vertex detector will only be possible after considerably more knowledge has been gained concerning the performance of the different detector components in an LHC environment. To develop ideas for relevant R&D studies one needs however to have a concept of a detector. A central detector, covering a range of  $\eta$  from -1.8 to +1.8 (range of polar angle from 20 to 160 degrees) is proposed. The covered range is approximately the same as proposed for the Silicon Tracker Preshower, which is regarded for this exercise as a complementary detector. Two ideas are described here, which can be further studied, modified and evaluated.

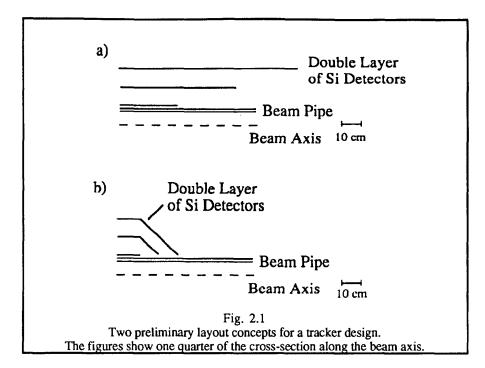

The first of the proposed designs is in Fig. 2.1a. The detector consists of 3 double layers. These layers are built of double-sided microstrip detectors with strip pitch of  $50\mu m$  on both sides. The radii of these layers are 10, 20 and 30cm. The total area of silicon is  $10.6m^2$ ; the total number of readout channels is 8.5 million.

Another design is drawn in Fig. 2.1b. There are also three double layers built of the same detectors as mentioned before. In the central part, where layers have cylindrical shape radii are also 10, 20 and 30*cm*. The range of polar angle covered is also the same. Tracks with  $\theta$  lower then 30 degrees cross only one layer however. For 30 <  $\theta$  <45 two layers, and for  $\theta$  > 45 all three layers are crossed. This design will also probably make system aspects (mechanics, cooling, powering and readout) more difficult. But the total area of silicon is only  $3.5m^2$  and the total number of readout channels is 2.8 million, both three times less than for the first design. Another important advantage is that the tracks do not cross detector planes at angles lower than 45 degrees. In the first design it is only 20 degrees near the cylinders ends.

For small angles the signal is divided between many strips on one of the sides and much harder to detect because of that.

It is expected that the future design of the tracker will be a modified version of one of the two presented here. The design decisions depend on further studies on :

- physics performance simulation using SLUG (Simulation for LHC Using Geant), in cooperation with groups working on other proposed detectors

- double-sided detectors and readout electronics

- system aspects: cooling, mechanical stability and precision, powering and readout connections

- radiation hardness of the detectors and electronics.

It should be emphasized that some of the most complex problems will be posed by the requirements on the cooling.

#### 2.1.2 Performance Considerations

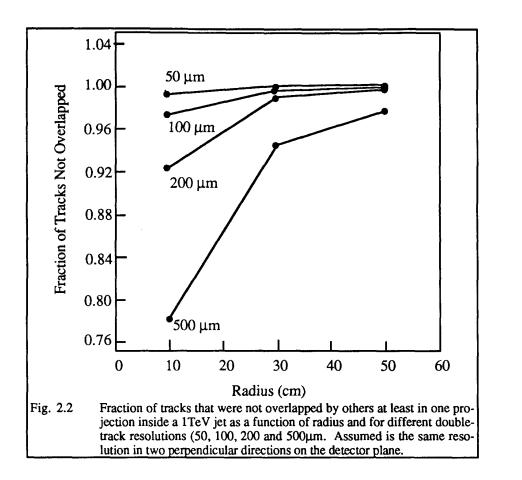

First studies concerning double-track resolution have already been performed with the use of the PYTHIA event generator. The highest demands for this resolution are inside high energy jets, typical for interesting high transverse momentum events. Figure 2.2 shows the average fraction of tracks that are not overlapped by others as a function of radius and for different double-track resolutions (50, 100, 200 and 500 $\mu$ m) inside a 1*TeV* jet. Assumed is a double-sided strip detector, that has the same resolution in two dimensions and of the order of at least 200 $\mu$ m is necessary to resolve tracks in the conditions expected.

Extensive simulation studies including tracker combined with other detectors have to be performed to test the physical performance of the considered designs. Some results can be obtained before that however.

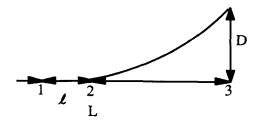

Stand-alone momentum resolution of a Si tracker is given by the formula:

$$\frac{dp}{P} = \frac{P}{0.3 B} \sqrt{\frac{720}{N+5}} \frac{e}{L}$$

- p: momentum (or  $P_t$  in principle) in GeV

- B: Magnetic field in Tesla (I assume a 2T field)

- N: Number of points (equidistant). According to the PDB the formula is ok for N > 10, but I checked that it is still good for N=3

- e: resolution of the tracker (I assume  $e = 15 \ \mu m$ )

- $\boldsymbol{\ell}$ : projected length of the track (= lever arm of the device)

If we assume 3 double layers at 10, 20, 30*cm* we get: N = 3,  $e = 10\mu m$  (each double layer provides one point with  $e/\sqrt{2}$  precision) and  $\ell = 20cm$ :

$$dp/p = 0.41\% \times p$$

(33% at 80 GeV)

This is not very exciting and there is need of an external measurement.

Assumed is a third measured point at L = 1m, with a resolution of  $200\mu m$ . The momentum measurement is simple : a straight line is extrapolated from the tracker at 1, 2 to 3 and the distance D to the track impact is measured. We ignore problems of pattern recognition at that point. Then :

$$\frac{dp}{P} = \frac{6.7 p}{B} \sqrt{S^2 + 2\left(\frac{L}{L}\right)^2 e^2} \frac{1}{L^2}$$

with s : resolution at 3. (This formula is approximate, it requires L/L >> 1 (5 is ok), and in principle only 2 points measured in the tracker (3 improves a bit). With L = 20cm, L = 1m,  $e = 15\mu m$  and  $s = 200\mu m$ , B = 2T one achieves:

$$dp/p = 0.07\% \times p$$

, (33% at 500 GeV),

which is sufficiently good.

Under these assumptions, the resolution is dominated by the intrinsic resolution of the external tracker (s) and its lever arm (L). It is an interesting exercise to find the minimal requirements for the tracker, before it starts to have the main contribution to the resolution:

$$s > \sqrt{2} \frac{L}{L} e$$

as  $e = 15 \mu m$  is more or less granted, (let's have some safety margin!) we find that L/L > 10, or the device should be longer than 10cm

It could be concluded that a 3 (double) layer tracker at 10-30cm, together with a measurement at large radius (with moderate resolution) provides a momentum resolution which is sufficient for most LHC physics. In stand-alone mode the resolution is very moderate, but might still be of help for pattern recognition and track extrapolation to outer devices.

With r: inner radius and  $\mathcal{L}$ : lever arm, the impact parameter resolution is

$$d(i) = e \sqrt{1 + 2\frac{r}{\ell} + 2\left(\frac{r}{\ell}\right)^2}$$

With r = 10cm,  $\ell = 20cm$ , e = 15:

$d(i) = 23\mu m (16 \text{ with double layers})$   $r = 20cm, \ \ell = 10cm, \ e = 15:$  $d(i) = 54\mu m$

The average impact parameter of a B-track is about  $240\mu m$ : A simple example: assuming *i* is exponentially distributed for b events and we make a cut a  $3\sigma$  resolution to reject non-B background one would be 75% efficient with  $d(i) = 23\mu m$ , with  $54\mu m$  the efficiency would drop to 50%

Concerning impact parameter resolution it is necessary to go as close to the interaction point as possible. 10cm seems to be sufficient, 20cm is probably too far away.

## 2.2 Tracking for Heavy Ion Experiments at SPS and LHC

An area of physics for which the proposed R&D programme would be of the highest interest are the Heavy-Ion experiments foreseen at CERN in the years 1994-1995 at the SPS (fixed target) and in the first years of operation at the LHC, used in collider mode with nuclear beams up to Pb.

The aspects of relevance are different in the two cases, and will be treated separately in the following, although the researchers concerned are the same and the physics programme are ideally one the continuation of the other. It should be apparent that these timescales make some of the developments on the critical path for the experiments, and would thus have a high priority for the physicists involved.

#### 2.2.1 Physics with Heavy Ions at LHC

The injection of heavy ions in LHC is currently foreseen since the beginning of its operation [2.1]. The centre-of-mass energy per nucleon would be lower than in the protonproton mode, still giving a 1262TeV total c.m. energy for Pb-Pb collisions. The design luminosity would be  $2 \cdot 10^{27} cm^{-2} s^{-1}$ , several orders of magnitude below the maximum luminosity in the p-p mode.

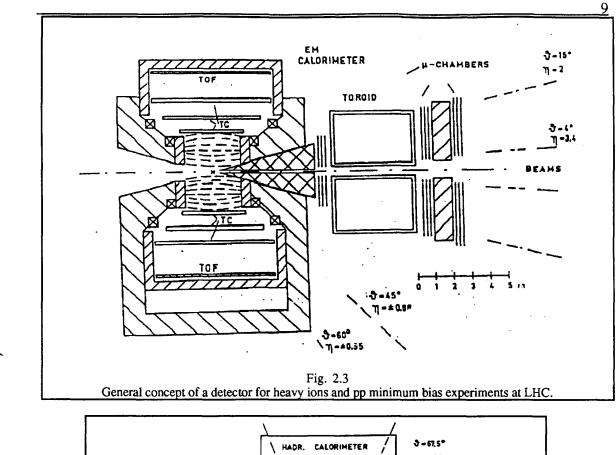

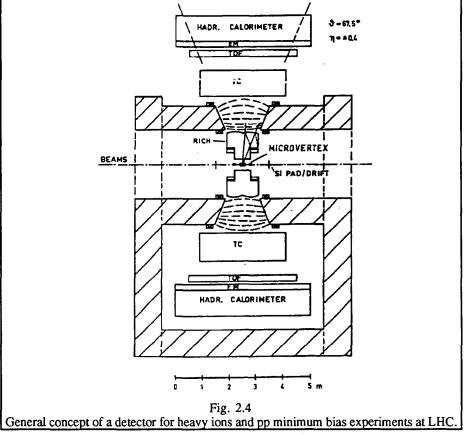

A proto-collaboration for an experiment addressing both heavy ion physics and p-p minimum bias physics was set up in December 1990, at which point several working groups on specific items were formed, namely : 1) Global event characteristics and event generators; 2) Hadron spectra; 3) Dileptons and direct photons; 4) Hard processes (jets); 5) pp minimum bias. So far no detailed detector specification has been given, and only general concepts have been presented (see Figs. 2.3 and 2.4).

The expected charged particle densities are considerably higher than in p-p collisions : for central *Pb-Pb* collisions, event generators like VENUS [2.2] indicate dN (charged)/dy of the order of 2000 and dN (charged)/d (Omega) around  $300sr^{-1}$ .

The detector components where high resolution silicon detectors would be highly desirable are :

- a) Microvertex for hyperon decay detection and determination of Cerenkov rings' centres;

- b) Multiplicity detector to tag central collisions.

Both applications demand rather high granularity, due to the high multiplicity : for example, a microvertex layer at R = 5cm with a track density of 13 tracks/ $cm^2$  would require  $200 \times 200 \mu m^2$  elements to ensure 0.5% cell occupancy. On the other hand, at larger distances, double-sided strip detectors represent the most attractive option.

For this application, rate and radiation hardness requirements are substantially less demanding than for LHC p-p at full luminosity, while most of the system aspects would be the same.

#### 2.2.2 Fixed Target Experiments with Pb Beams at SPS

The operation of SPS with heavy ion beams is foreseen to start in 1994 (the concept of the accelerating facility is described in the report CERN 90-01). Proposals for experiments are currently in preparation : among them, four groups are considering using high resolution silicon detectors (NA35, NA38, WA80, WA85).

Due to the high luminosity (up to  $4 \cdot 10^8$  ions / 15 seconds, and with targets of up to 20% of an interaction length) and to the Lorentz boost, experimental conditions are actually more challenging than at LHC/ions and even LHC/pp.

In particular, at R = 5cm, track densities at forward angles would be up to  $30/mm^2$  for central interactions, and integrated fluxes for a 50 days run (at  $10^8$  ions/burst on a 20% target) would be up to  $7.5 \cdot 10^{13}$  neutrons/ $cm^2$  and  $4 \cdot 10^{15}$  charged particles/ $cm^2$ .

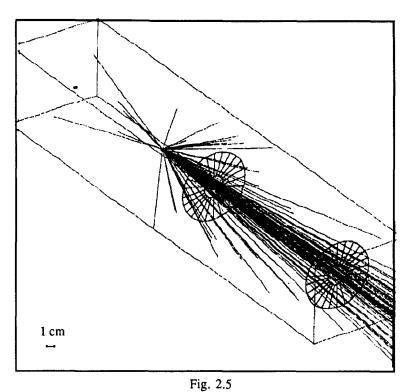

A specific application which is being studied with extensive Monte Carlo simulations is the measurement of charged multiplicity in NA38 (a high-rate dimuon experiment) in the laboratory pseudorapidity range 1.6 to 4.0.

A distance of a few cm from the interaction point is required to limit the number of background muons coming from pion and kaon decays. Good resolution on N(charged) for central events (about 1400 tracks in the quoted angular range) requires a granularity of the order of  $10^4$  elements.

A schematic view of a possible detector arrangement is shown in Fig. 2.5, with two identical detectors subdivided into 24 sectors each; every sector would be further segmented into a few hundred strips. Overlaid is an event as expected from heavy ion interactions. Detailed specifications are expected in a few months from now.

Schematic view of a possible arrangement of a silicon detector for a fixed target experiment.

## 2.3 A Dedicated Beauty Experiment at the LHC

During last autumn, a test to use a high resolution Si tracker with forward geometry has been successfully performed in the UA1 interaction region of the SppS collider (P238 test). This vertex detector consisting of 48 Si strip detectors was running at a distance of  $\pm 3mm$  from the interacting beams at high luminosities with negligible background and good track efficiency.

This result encourages the planning of a dedicated beauty experiment for the LHC using a Si forward tracker and dedicated trigger processors. This development will be the subject of a separate proposal for R&D to the DRDC. The specifications for Si detectors and associated front-end electronics for such an experiment will be similar to those required by the applications mentioned in Chapters 2.2 and 2.2. Some of the specific design requirements for silicon detectors and front-end electronics for this application are described in Appendix A. It is intended to do some R&D work specific for this application within the framework of this study.

#### References

- [2.1] G. Brianti, LHC Workshop, Aachen, CERN 90-10, Vol. 1, p. 40-53.

- [2.2] P. Cerello, P. Giubellino, K. Werner, LHC Workshop, Aachen, CERN 90-10, Vol. 2.

## 3. Si STRIP DETECTORS

#### **Requirements for LHC**

We make the assumption that double sided silicon microstrips are the most likely detectors to be used on a wide scale for tracking close to the beam at LHC as a consequence of probable availability and expertise in their use. Naturally, this does not exclude more complex detectors like pixels to be employed when available where they offer advantages. Neither does it exclude the use of simpler detectors such as single sided microstrips, although complex events in a low mass detector will require maximum information from minimum material.

#### 3.1 **Performance specifications**

It is important to note that detailed specifications can only be arrived at in combination with simulation studies which identify the physics requirements. Conversely, realistic simulations can only be carried out with a knowledge of the practical possibilities for the detectors. There will be important limitations imposed by occupancy in terms of size of element and allowable space point ambiguities from multiple hits. The requirements on momentum resolution are not well known and will influence the layout of the strips. Radiation damage effects are easier to estimate, as far as signal to noise performance is required, but there are many unknowns to be evaluated. Power consumption and cooling, as well as mechanical support will be ingredients in the final specification.

With these qualifications in mind we propose some outline specifications as a guide to future design, Table 3.1, which can be refined as further information becomes available. They are based on what we believe to be achievable in the near future using present technology.

No assumption has yet been made about the relative orientation of the strips since this can be chosen as required once the technology is fully demonstrated. We expect to commence with orthogonal strips but orientations of less than 90° may be advantageous to reduce spatial ambiguities if the required spatial resolution in both coordinates can be achieved.

The three main requirements emphasised by Table 3.1 are segmentation, speed and radiation damage. We comment briefly on each of these.

| Table 3.1 | Possible starting specifications for LHC microstrip detectors - |

|-----------|-----------------------------------------------------------------|

|           | based on double-sided, a.c coupled technology                   |

| Parameter                | Value                      | Comment                                                  |

|--------------------------|----------------------------|----------------------------------------------------------|

| Wafer thickness          | ~300µm                     | on 4inch wafer                                           |

| Strip dimensions         | $60mm \times \sim 10\mu m$ | fit 4inch wafer & minimise strip capaci-<br>tance        |

| Strip pitch              | 50µm                       |                                                          |

| Number of strips         | 9 x 128                    |                                                          |

| Strip leakage current    | <10µA                      | after several years                                      |

| Total leakage current    | 30mA                       | guard currents should not be excessive after irradiation |

| Bias resistor            | $100k\Omega$               |                                                          |

| p-side strip capacitance | <5pF                       | if possible, adjust strip widths                         |

| n-side strip capacitance | <5pF                       | to achieve                                               |

| Decoupling capacitance   | 100 <i>pF</i>              |                                                          |

| Depletion voltage        | <50V                       | during operation                                         |

| Operating voltage        | 100V                       |                                                          |

| Breakdown voltage        | >150V                      |                                                          |

| Interstrip resistance    | >100kΩ                     |                                                          |

#### Segmentation

This parameter depends on the position resolution, signal sharing between strips and radiation damage induced leakage currents. Strips must be read individually, for reasons of speed and immunity to radiation damage, and it will be challenging to bond at higher density than  $50\mu m$ .

#### Speed

A good signal to noise ratio cannot be achieved unless the charge collection time is short compared to the amplifier time constant. It has already been emphasised [3.1] that detectors must be well over-depleted to ensure sufficiently rapid charge collection but, to make matters worse, charge collection times are expected to change during the lifetime of the detector as a consequence of bulk radiation damage [3.2]. This particularly affects the hole component of the signal which is expected to be slowed significantly. Recent measurements indicate that charge collection can be maintained at least up to neutron fluences of ~10<sup>14</sup>  $n.cm^{-2}$  if detectors are operated at 100V [3.3].

#### Radiation damage

In the central cavity the charged particle dose will depend (as  $1/r^2$ ) on radial distance from the beam while the neutron fluence will be practically isotropic. Annual neutron fluences

of  $\sim 10^{13} cm^{-2}$  will be typical while a charged particle dose of  $\sim 2 \cdot 10^4$  Gray at 10cm radius may be expected [3.5].

From data on bulk damage to silicon by neutrons and charged particles estimates can be made of the increase in leakage current, probably with sufficient accuracy [3.2], since there are strong dependences (factors of  $\sim$ 3) on design of the overall system, in particular the calorimeter composition and location. There are also possibilities to reduce the flux of neutrons by inserting moderator materials.

To demonstrate the conditions under which a tracking detector must operate estimates are made of expected changes in bulk leakage currents at LHC and consequences for a "minimal" detector (Table 3.1). Damage constants based on available data have been used -  $6.9 \cdot 10^{-17}$  A.cm<sup>-1</sup> for neutrons and  $2.9 \cdot 10^{-17}$  A.cm<sup>-1</sup> for charged particles. (For details of the assumptions see [3.2,3.5]). Annealing effects, which are not yet fully understood, may result in a reduction in leakage currents in actual operation (by factor ~ 2).

| Table 3.2Annual rate of leakage current increasefor $\mathscr{L} = 10^{-34} cm^{-2} s^{-1}$ and $10^{7} sec/year$ operation |        |       |                        |                         |                     |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|--------|-------|------------------------|-------------------------|---------------------|--|--|--|--|--|

| Layer                                                                                                                       | R (cm) | L(cm) | ΔΙ(μAcm <sup>-2)</sup> | ∆I <sub>layer</sub> (A) | ∆P(kW)<br>(at 100V) |  |  |  |  |  |

| 1                                                                                                                           | 10     | 50    | 131                    | 0.4                     | 0.04                |  |  |  |  |  |

| 2                                                                                                                           | 30     | 130   | 33                     | 0.8                     | 0.08                |  |  |  |  |  |

| 3                                                                                                                           | 50     | 200   | 25                     | 1.6                     | 0.16                |  |  |  |  |  |

Г

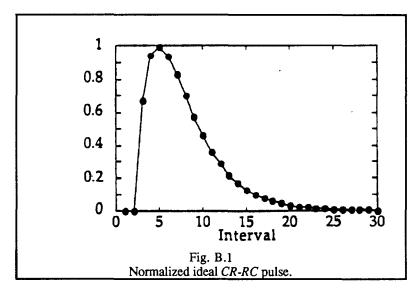

Electronic noise depends on detector segmentation; examples are calculated assuming microstrips  $50\mu$ m × 6cm in each layer. After five years of operation the strip currents and shot noise, assuming CR-RC shaping, are given in Table 3.3.

| Table 3.3Microstrip leakage currents and shot noise<br>contribution after 5 years operation |                          |                                       |                                        |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------|--------------------------|---------------------------------------|----------------------------------------|--|--|--|--|--|--|--|

| Layer                                                                                       | ΔI <sub>strip</sub> (μΑ) | ENC <sub>shot</sub> (e)<br>15ns CR-RC | ENC <sub>shot</sub> (e)<br>45 ns CR-RC |  |  |  |  |  |  |  |

| 1                                                                                           | 20                       | 1890                                  | 3270                                   |  |  |  |  |  |  |  |

| 2                                                                                           | 5.0                      | 950                                   | 1650                                   |  |  |  |  |  |  |  |

| 3                                                                                           | 3.8                      | 825                                   | 1430                                   |  |  |  |  |  |  |  |

Although present indications are [3.3] that the detectors would function adequately after several years the shot noise will become high enough that cooling of the detector below ambient temperature may well be advisable. In addition to current increases in the strips themselves it may be necessary to pay special attention to guard currents at the periphery of the detectors to ensure that power consumption does not become unacceptably high.

The consequences of radiation damage are not confined to leakage current increase [3.2] and most of these effects are only beginning to be studied significantly. Many of the questions can only be answered by designing and fabricating new detectors and evaluating them for hardness. It is unlikely that any detectors presently in use will be adequate without further development.

## 3.2 Choice of technology

Double sided microstrips must be a.c coupled to the electronics. In principle this need only be the case for one surface if the second surface strips are read out through low input resistance, d.c. coupled preamplifiers but experience to date suggests that interstrip currents will necessitate capacitors on both surfaces.

The capacitors should be integrated on the detector for reasons of space, which is not difficult. There are two biasing techniques in use - punch-through and accumulation layer resistors (*Aleph* [3.6,3.7]) and polysilicon resistors (*Delphi* [3.8]). There are two isolation techniques - field stops (*Aleph*) and field plates (*Delphi*). None of the alternatives can yet be excluded on the basis of experimental results, although accumulation layer resistors on the n-side are hard to manufacture with great uniformity [3.9]. The polysilicon resistors are now known to be very hard with respect to neutron irradiation [3.4] so appear to be particularly promising.

#### Detector thickness

We expect signal to noise to be a challenge. Therefore, despite the wish to minimise material, we assume that  $\sim 300 \mu m$  is required which can be achieved with 4 inch wafers. Most probable signals of  $\sim 25,000$  electrons are expected. For several reasons this is not likely to be the typical signal observed on a single microstrip. Landau fluctuations tend to give rise to average pulses larger than the most probable value. Particles will not usually be incident on the silicon normally, again increasing the total pulse size.

Charge sharing between strips will be common on at least one surface, which will reduce the typical signal on a strip. The combination of magnetic field and electric field in the silicon will give rise to non-normal drift paths for electrons and holes. The effect is most serious for the electrons where angles of up to ~18° for a 2T field  $(tan(\mu_H H)~0.3)$  may be expected. This can significantly distort the position measurement in a digital readout system [3.10] and reduce the signal on each strip. If the strips are orthogonal on the two surfaces, the effect could be minimised by ensuring that the p-type strips, collecting holes, are placed parallel to the magnetic field - which is easy to arrange in the barrel of a solenoidal detector.

#### Microstrip capacitance and decoupling capacitors

Noise, speed and power consumption are vital determinants of a silicon tracking detector system. They depend explicitly on the detector capacitance at the amplifier input [3.11] and it is advantageous to reduce the microstrip capacitance if possible. It is well known that this is determined mainly by interstrip capacitance, and thus can be reduced to some extent, but there is concern that on the ohmic side of the detector this is higher than on the junction side. Some calculations [3.12] have suggested that this can be reduced significantly. If true, this will be an important specification to be achieved.

The values of decoupling capacitors are chosen to ensure the maximum signal transfer into the amplifier; some, usually small, loss is inevitable. The conditions usually applying to a charge-sensitive amplifier are that  $C_d \ll C_c \ll C_a$  referring to, respectively, detector, coupling and effective amplifier input capacitances. This seems to be quite easy to attain in most circumstances, eg a 5cm x 10µm strip using 0.2µm oxide gives  $C_c=90$ pF. For a current sensitive amplifier, much the same condition holds except that now  $C_d \ll C_c \ll 1/\omega R_a$  with  $R_a$  the input resistance. Since typical values of  $R_a$  are likely to be ~100 $\Omega$ , and must be kept small to minimise the pulse rise time, this condition should still be satisfied.

#### **Bias resistors and interstrip resistances**

Given the expected increase in leakage current, there is no purpose in making bias resistors of the values currently in use. From a noise point of view, a  $100k\Omega$  resistor in parallel with the amplifier input is equivalent to a leakage current of  $0.5\mu$ A and would be adequate at LHC. If every strip is read out relatively low interstrip resistances can also be tolerated; the requirement is that they should be large compared to the amplifier input impedance which is likely to be ~ $100\Omega$ .

#### 3.3 Specific R&D projects

Some systematic studies of radiation hardness of detectors (for example using neutrons) are already under way and some double sided detectors exist, or are in an advanced stage of production, which will be available for irradiation. We see a need to supplement the information which is now, or shortly will be, available by further systematic radiation studies using several different particle types and specifically designed components, as well as detectors themselves, to understand fully the tolerance of detectors to the LHC environment.

We propose therefore to design test structures (which will include detectors of several sizes) which will be fabricated and tested under irradiation. The test devices will include

microstrips, diodes, resistors, capacitors and gated diodes which will allow the evaluation of key elements of full size detectors but they will be fabricated on only one side of the silicon wafer, allowing the independent testing of the two surfaces. Particular properties which require examination are the behaviour of different types of bias resistors, maintenance of interstrip isolation, charge collection speed and annealing behaviour, as well as technology specific features possibly unique to individual manufacturers.

The irradiations will be carried out at RAL (using neutrons), Strasbourg (low energy electrons), CERN (particle beams) and elsewhere, as available. These will provide complementary information on both bulk and surface components of the damage. We hope to identify not only weak points in the designs, but also to shed some further light on the basic origins of the radiation damage so that further hardening can be achieved.

Since bulk damage is of such importance to the leakage currents and thus the noise behaviour of the system there is interest in demonstrating more clearly whether or not any improvement in bulk tolerance can be expected. In addition, serious attention must be paid to the n-side of the detectors, about which little is yet known regarding their post-irradiation behaviour, and interstrip capacitance, which has an important influence on power consumption of the front end amplifier.

The production of test structures and much of their evaluation should take place in the first year of the programme with continuation expected at a lower level in the second year. Our main interest in the second year, having identified the elements of a successful radiation tolerant design, will be to fabricate detectors of close to full size using a limited number of directly comparable designs in the technologies available to us.

We have identified three main manufacturers - SI (Norway), IHP (Germany) and VTT (Finland) - with whom we have developed working relationships in the last few years and who have expressed interest in participating in this programme. We expect to continue to work closely with them on the detector design and fabrication technology to achieve our goals. However there is no intention to exclude from consideration detectors produced by other manufacturers who may be willing to collaborate with us.

#### References

- [3.1] S. Gadomski et al., *Calculations of Pulse Shape in Silicon Detectors*. Aachen LHC workshop, CERN 90-10 Vol. 3 (1990) 241.

- [3.2] G. Hall, Radiation Resistance of Semiconductor Detectors and Associated Electronics. Aachen LHC workshop. CERN 90-10 Vol. 3 (1990) 693

- [3.3] M. Edwards, G. Hall, S. Sotthibandhu. Neutron Radiation Damage Studies of Silicon Detectors. London Conference on Position Sensitive Detectors, September 1990. IC/HEP/90/3

- [3.4] G. Hall, S. Sotthibandhu. Imperial College internal note (1991)

- [3.5] G. Stevenson. New dose calculations for LHC detectors. Aachen LHC workshop CERN 90-10 Vol. 3 (1990) 566.

- [3.6] ALEPH detectors (Munich)

- [3.7] ALEPH detectors (Pisa)

- [3.8] DELPHI detectors

- [3.9] L. Bosisio. private communication

- [3.10] W. Sailor. SSC Silicon tracker meeting, Albuquerque, August 1990.

- [3.11] P. Jarron et al. Study of Analogue Front End Electronics for Supercollider Experiments Aachen LHC workshop CERN 90-10 vol. 3 (1990) 84.

- [3.12] H. Sadrozinski. Paper presented at London Position Sensitive Detector Conference, September 1990.

## 4. FRONT-END ELECTRONICS

The requirements for a front-end electronic system which can operate around an LHC interaction region at a luminosity of around  $10^{34} cm^{-2} s^{-1}$  and a possible solution are discussed. This paragraph outlines the general principles. Details are discussed in Appendix B.

#### 4.1 Constraints

In the absence of definitive timing constraints, which will be determined by the detailed functioning of the different subsystems of a big LHC detector, a list of parameters is given below which serve as a guide-line for speed requirements on the front-end electronics. Similar numbers are used in first studies of other detector components [4.1,4.2]:

| ٠ | Interval between each beam crossings           | : 15ns             |

|---|------------------------------------------------|--------------------|

| • | Time delay, first level trigger                | : ≈ 1µs            |

| • | Average time between each first level trigger  | : ≈ 10µs           |

| • | Time delay, second level trigger               | : 20-100 <i>µs</i> |

| • | Average time between each second level trigger | $: \approx 1 ms$   |

Another global constraint to be mentioned is power consumption. Specific numbers on this cannot be given at this stage since the question of cooling and detector layout has not yet been clarified. However, it is clearly of great importance to keep the power consumption at the lowest level possible.

#### 4.2 Aims of the Readout Electronics

The main goals of the front-end readout electronics is to provide:

- Very low noise, including minimal distortion of valid information at any stage of the processing.

- Very precise time-tagging to correlate all the signals of interest to the correct BCO.

- Maximum background-free information.

- Minimum pile-up problems.

- No dead-time.

- Selective (sparsified) readout of analog pulseheight values.

In addition, the system must be robust, reliable and easy to calibrate and to verify for functionality.

#### 4.3 **Proposed Methods to be Used**

We propose to achieve these aims through the following key items:

- Charge sensitive preamplifier.

- Shaper with a peaking-time optimized w.r.t noise, but not constrained to the BCO frequency.

- Time-slicing and preliminary on-chip storage of all useful information.

- Waveform analysis for precise time-tagging of every interesting signal, for handling eventual pile-up effects, and for suppressing background, noise and out-of-time signals.

- Sparsified hierarchical readout scheme.

- Built-in test and verification functions.

#### 4.4 Suggested Implementation

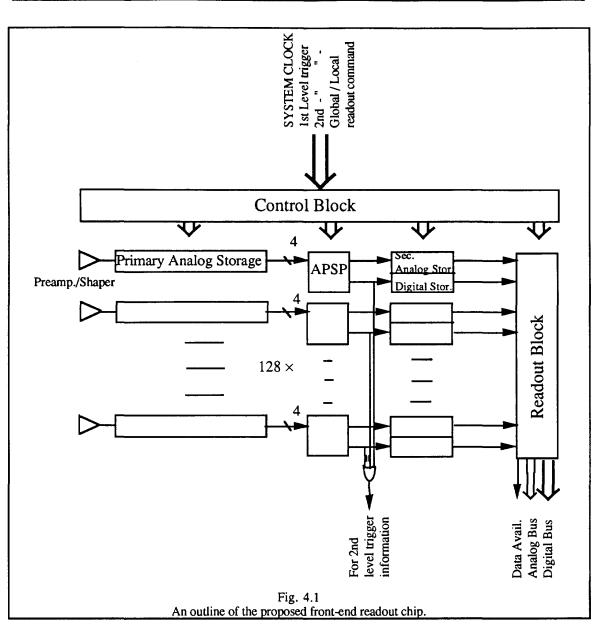

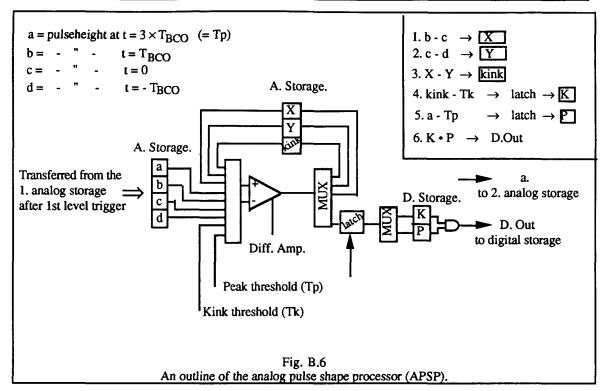

An outline of the proposed front-end readout chip is shown in Fig 4.1. It consists basically of the following main parts:

- 1. Control block.

- 2. Preamplifier with shaper.

- 3. A primary analog storage (pipe-line).

- 4. An Analog Pulse Shape Processor(APSP).

- 5. A secondary analog/digital storage.

- 6. A readout block.

Except for the control and readout block, there will be one each of the other modules for every channel on the chip.

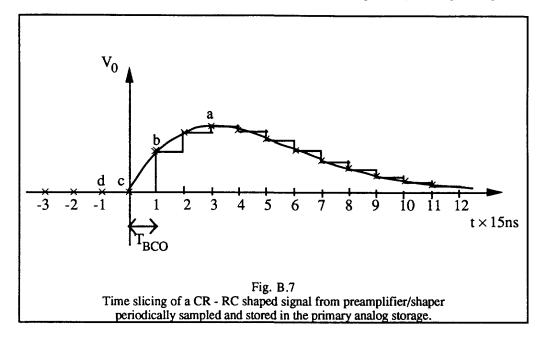

The analog time-continuous output from the preamplifier/shaper is being periodically sampled (for every BCO) which transforms the signal into a still analog but now time-discrete form. All of the sampled values will be stored temporarily in the primary analog storage [4.4,4.5].

On a positive 1st level trigger, relevant information i.e. some predetermined samples corresponding to the BCO for which the trigger was for, will be transferred to the APSP. This unit is the "brain" of the system having the task of analyzing the analog pulse shape and to make a decision on whether or not the signal fulfils predetermined requirements for being defined as a real hit.

The output of the ASPS, which operates on the speed of the average time between each 1st level trigger, is the analog value of the peak of the shaped output in addition to a digital

'yes/no' signal telling if the event in the channel was accepted or not. Both the values are put on the secondary analog and digital storage respectively. In addition, the 'yes/no' answers from all the channels in the chip, will be OR'ed together and made available on a separate output pin for eventual use in the 2nd level trigger decision.

Upon a positive 2nd level decision (or possibly earlier) the corresponding data will upon request of a global readout command be transferred to the readout block which will take care of performing a hierarchical sparsified readout.

The control block will take care of correct timing including the flow of data in and out of the different modules. In addition it has the important task of buffering information in the storages in the case of consecutive triggers on both levels.

## 4.5 Choice of Technology

In order to build prototypes of the different subcircuits as the first approach, and later on a prototype of the final front-end chip, a traditional CMOS bulk process will be used. This is convenient for prototype circuits and has the advantage of being cheap in addition to provide easy access and frequent Multi Project Chip runs.

However for the final circuits, it is necessary to choose a technology which is radiation resistant enough to survive the radiation environment at the LHC. For the moment a CMOS/SOI process [6] seems very promising and will probably be commercially available from several foundries in the near future. Yet, from what we know, processes of this type have not been evaluated sufficiently for analog purposes. However, it is likely that a redesign from the CMOS/bulk system into such a process should not cause any particular problems.

#### 4.6 Specifications

Below are listed specifications of the front-end readout electronic which will be aimed for :

| ٠ | No. of channels per front-end chip : | 128              |

|---|--------------------------------------|------------------|

| ٠ | Power consumption per channel :      | < 3mW            |

| ٠ | Type of amplifier :                  | Charge sensitive |

| ٠ | Type of shaper (filtering) :         | CR-RC            |

| ٠ | Shaper peaking-time :                | 45 <i>ns</i>     |

| ٠ | Total gain preamplifier/shaper :     | 20-30mV / MIP    |

| ٠ | Detector capacitance $(C_d)$ :       | ~ 10 <i>pF</i>   |

|   |                                      |                  |

• Noise for  $C_d = 10pF$  (excl. noise from leakage current) :  $\approx 700 \ r.m.s. \ e^{-1}$

| • Type of information provided :        | Analog pulseheight and digital address                    |

|-----------------------------------------|-----------------------------------------------------------|

| • Readout procedure :                   | Sparsified, parallel and hierarchical                     |

| • Discrimination method :               | Threshold on timing, shape and peak value                 |

| • Readout after 1st level trigger :     | OR'ed digital information (possibilities of full readout) |

| • Readout after 2nd level trigger :     | Full readout (if not already done)                        |

| • Operating speed zero level :          | 15 <i>ns</i>                                              |

| • Available processing time 1st level : | ~ 10µs                                                    |

| • Available processing time 2nd level : | ~ 1 <i>ms</i>                                             |

| • Sampling method :                     | Voltage                                                   |

| • Average pitch :                       | 50µm                                                      |

| • Process :                             | Radiation resistant CMOS                                  |

#### 4.7 Discussion on the Choices of Methods

A front-end electronic readout system has been proposed which is believed to be a good solution for the application described in this proposal. Below are listed arguments for some of the methods/solutions which have been chosen and which are of a fundamental character:

**Charge sensitive preamplifier** : It has very good noise performance [4.3] and a wide range of experience is available for this type in these applications.

Analog system : In general, information about the waveform is advantageous to provide:

- **on-chip**, a precise time-tagging and pile-up handling, in addition to excellent rejection of background, noise and out-of-time signals

- off-chip, off-line, possibilities of centre of gravity calculations, Landaucorrelations and determination of number of charged particles by pulseheight measurements (in particular in the case of  $\gamma$ -conversions).

- **Time-slicing** : It gives the freedom to choose peaking-times of the amplifier with respect to optimal noise performance without being constrained to the time between each BCO. This implies of course that a precise time-tagging is performed at some stage.

- **Time-tagging**: Of course this has to be performed if a peaking-time longer than the time between each bunch crossing is used. However, it should be noticed that even for systems where the peaking-time is constrained to the BCO frequency, situations are likely to occur where out-of-time signals will be erroneously interpreted as real signals

which were in reality the tail of a signal from the previous bunch crossing. This is an additional good reason for addressing the problem from the very beginning.

**Peaking-time**: 45*ns* is proposed because it makes a good amplifier design easy to achieve for reasonable values of power consumption. It also provides excellent noise performance even for quite high values of leakage current. It is also short enough for the time-tagging to be precise.

## 4.8 Specific R&D Projects

Listed below are the proposed specific R&D projects for the coming two years.

- Evaluation of the performance of the preamplifier/shaper which is already under design.

- Adaption of the already existing analog storage element to this particular application. This includes also working on the interface with the control block.

- Design of the control block.

- Exploration of the properties of waveform analysis (APSP). This includes simulation studies and in particular analysis of experimental data from a real test set-up.

- Design of the APSP.

- Design of the readout block.

- Definition of the digital I/O i.e. signal type and levels. Designing I/O units that corresponds to the definition.

- Definition of a global test and verification procedure for the system including work on how to implement it on each level.

- Assembly of a test system using many submodules, later assembly of a part of the system using complete modules.

- A close interaction with the on-going efforts by other groups, in particular for the evaluation of the CMOS/SOI radiation hard processes.

## **References**

- [4.1] N.Ellis et al., A Digital Solution to First Level Triggering Using Calorimetry at the LHC. CERN 90-10/ECFA 90-133 vol.3, December 1990.

- [4.2] G.Goggi et al., Digital Front-end Electronics for Calorimetry at LHC. CERN 90-10/ECFA 90-133 vol.3, December 1990.

- [4.3] E.Nygård et al., CMOS Low Noise Amplifier for Microstrip Readout. Design and Result. CERN-PPE/90-142, October 1990.

- [4.4] P.Jarron et al., *Study of Analog Front-End Electronics for Supercollider Experiments*. CERN 90-10/ECFA 90-133 vol.3, December 1990.

- [4.5] F.Anghinolfi et al., Monolithic CMOS Front-End Electronics with Analog Pipelining. CERN/ECP 90-13.

- [4.6] J.L.Leray et al., CMOS/SOI Hardening at 100 Mrad. IEEE Transactions on Nuclear Science, vol.37 no.6, December 1990.

## 5. PRECISION MOUNTING, MECHANICS AND COOLING.

#### Mechanical Structure and Cooling of an LHC Silicon Tracking Detector

One of the most crucial issues which will face the designers of any silicon microstrip tracker for application at the LHC will be the maintenance of the mechanical stability of the detector. Since the goal will be to achieve spatial measurements of a few microns precision, the position of elements of the detector must be maintained to a similar level. This is an especially difficult problem because of the need for a low mass structure and the high heat output, mainly from the local electronics but also from the detectors themselves, which will necessitate cooling on a much larger scale than in previous experiments.

The power dissipation in the electronics is expected to be a few mW per channel and the total heat load is estimated to be several kW. Temperature uniformity of the system is an important consideration, to maintain the structure to  $\sim 5\mu$ m tolerances, and it may be necessary to maintain the temperature significantly below ambient, to give a margin of safety in noise as a result of leakage current increase.

Some attention has been given to similar problems in the context of a tracking detector for SSC [5.1]. It will be important to consider whethere there are alternatives to the solutions developed there since they involve novel and, for cooling, hazardous materials.

#### 5.1 Cooling

It is obvious that a high precision structure must be carefully cooled to keep it stable to the precision required. This means that, ideally, the temperature should be uniform throughout the tracker and, secondly, that it should be maintained close to a chosen operating point. What is more difficult, without a thorough engineering study, is to say what the tolerances should be. There is a disadvantage in allowing the temperature to rise since leakage currents increase rapidly. Any system will also need to be carefully controlled during shutdowns so that temperature changes occur sufficiently slowly not to distort the structure.

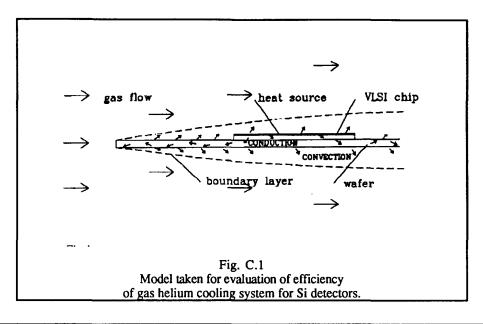

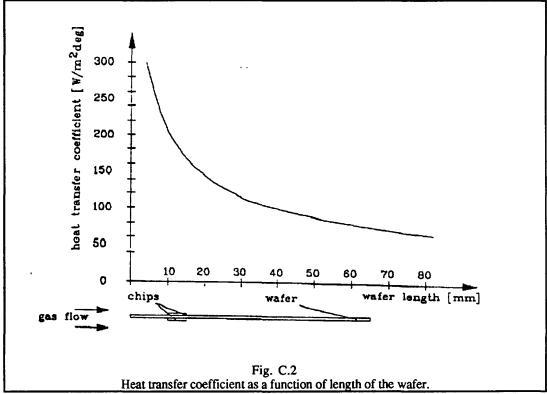

The large heat load rules out many solutions because of insufficient cooling power but it is possible that helium cooling, which is simple in concept, may be viable[Appendix ..]. Detailed engineering studies are required to demonstrate that the cooling can be uniform enough to avoid excessive thermal gradients and, thus, physical distortions.

The proposed SSC solution [5.1] is evaporative liquid cooling whereby a phase change in a working fluid removes thermal energy by its latent heat of vaporisation. An advantage of this approach is that the process can be controlled quite precisely because there is a well defined relationship at equilibrium between temperature and fluid pressure. However although many refrigerant fluids have been considered, all of them - fluorocarbons, amines, hydrocarbons - present serious safety hazards. They require a complex distribution system and, for safety, double enclosure in a nitrogen environment.

The problems of mechanical construction and, particularly, cooling a detector are so great that consideration must be given to them at an early stage. We require dedicated mechanical engineering support with access to computer design tools to evaluate a serious design of a support structure.

## 5.1.1. Specific R&D Projects

In the context of an investigation of a helium gas cooling system the tasks and time scale planned are:

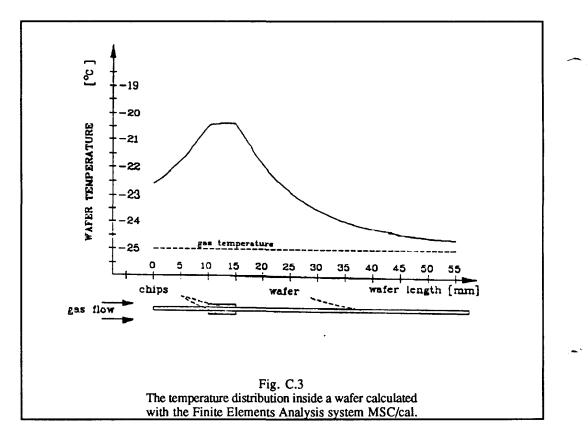

- estimation of the mechanical stresses and possible deformation of wafers caused by thermal and gas flow loads (Finite Element Analysis) summer of 1991,

- study of a way of supporting of the wafers against vibration forced by the gas stream

end of 1991,

- experimental confirmation of the results obtained from the thermal and mechanical analysis spring of 1992,

- consideration of possible detector arrangements inside the tracker and computer modeling of the gas flow through the tracker to improve the uniformity of the gas velocity distribution - summer of 1992,

- construction of a maquette of a quarter of the tracker and measure the gas velocity in all places of interest using the thermo-anemometry technique end of 1992.

## 5.2 Microbump Bonding

The number of bond wires needed for a LHC silicon detector can exceed a few million. It is questionable if the wire bonding techniques used to date offer sufficiently high yield and reliability for future application on such a large scale. One possible alternative is to consider the use of bump bonding which could allow the placement of electronic chips directly on the silicon and the construction of convenient modules for assembly and, relatively easy, replacement. There are several possible approaches to the problem:

#### 5.2.1 Solder-Bump Bonding

Imperial College and Rutherford Appleton Laboratory have, in a general context, been evaluating the use of flip-chip bump bonding of microelectronics to silicon detectors. In collaboration with GEC-Plessey Ltd, a first iteration has been completed and further iterations are being planned.

The technique employed [5.2,5.3] is the use of lead-tin solder bumps, where a precise volume of solder is confined between wettable metal pads of known area on each side of the bond, these pads being surrounded by regions into which the solder will not flow. When the

temperature is raised to the melting point of the solder (~180°C), surface tension forces tend to bring the structures into alignment. Thus accurate alignment of large number of connections can be made using standard techniques of metal deposition and photolithography.

Precision at the few micron level can be achieved with bond densities of 10,000 in a small area [5.3]. Our efforts, so far, have concentrated on the bumping of RAL MX chips (128 elements at 50µm pitch) to existing silicon detectors. New detectors have been fabricated to take this a stage further by mounting several MX chips on a detector and to examine small arrays of pixels. The results appear to be very promising. Examination of the bonds at several stages of the process has shown highly regular, precisely positioned and shaped metal areas as required. In January this year the first complete units were received from GEC-Plessey and tests are under way to evaluate them. Further devices, of new design, will be bonded later this year.

### 5.2.2 Resin Technology

Microbump bonding is done by using bump crowns on bond pads and simply gluing another chip onto the detector with corresponding pad layout and bumps aligned back to back. A special insulating resin is needed. The bumps are pressed against each other by the shrinkage stress force of the resin when the resin is set using UV-light.

An automatic bonder of this type has already been used to make an A4 size LED array module [5.4]. To use the microbump technique, the chips have to be aligned with respect to each other, which has to be done anyway, then a chip with corresponding pad layout is pressed on and aligned. This method would speed up the production of detector modules. The joint would be as solid as the detector, and no special caution is needed compared to the bond wires which can not stand mechanical stress. The joint can be opened using a solvent and jointed again up to 30 times [5.4].

The possibility to exploit this technology is under study in Finland.

#### 5.2.3 Conducting Glue Drops

As mentioned above, industrial techniques exist for bump-bonding, but the manufacturers are few (Plessey, Thomson/LETI, IBM, Philips), and iteration costs range from 50 to 250 KSF. Also delivery delays can be quite important. The Centre de Physique des Particules de Marseille (CPPM) has started some R&D work on developing a laboratory-scale bumpbonding method, for quick hybridization of chips with reasonable size (100 connections).

A gluing device has been designed, using micropositioning tables, and drops of conductive glue are deposited onto the silicon chip, by stamping. The drops are spherically shaped, and diameters of  $40-50\mu m$  are obtained on a regular basis, when producing arrays of few hundreds of connections. Various glues have been tried, in particular b-stageable epoxies, which have two phase-transition temperatures, one that corresponds to drying, the other to polymerisation. A lot of work is devoted to finding, in cooperation with manufacturers, the right glue that would have the correct properties of viscosity, conductivity, stamping ability, room temperature operation,...

In parallel, we have designed a positioning tool to align the two chips, and press them together for bonding. We hope to develop an optical system, based on split-prisms, that would help to align the chips while viewing them from in-between.

### References

- [5.1] W. Miller et al., Superconducting Super Collider Silicon Tracking Subsystem Research and Development Interim Report. Los Alamos National Laboratory. August 1990.

- [5.2] D.J. Pedder. Hybrid Circuits 15 (1988) 4.

- [5.3] M.J. Wale & C. Edge. IEEE Trans. Comp. Hybrids & Manuf. Tech. 13 (1990) 780.

- [5.4] K. Hatada et al., LED Array Modules by New Technology Microbump Bonding Method, IEEE Transactions On Components, Hybrids, and Manufacturing Technology, Vol. 13, No. 3, September 1990.

## 6. MANPOWER, INFRASTRUCTURE AND FUNDING

At this time, ten institutes and two industrial-oriented institutes (IHP Frankfurt and S.I. Oslo) are participating in this study. The manpower allocated to this effort will evolve with time. A number of people signing this proposal have, in addition to the contribution foreseen for this study, responsibilities in on-going projects. There are discussions with further European institutes with expertise in this field, who may decide to join this effort at a later date. In particular, the CPPM (Marseille, France) which is already participating in the R&D proposal for pixel detectors, is planning to join efforts on microbump bonding, irradiations and tests of detectors and electronics chips.

The Santa Cruz Institute for Particle Physics (SCIPP) at the University of California at Santa Cruz will participate in this R&D effort through existing collaborations with participating institutions, which are part of this proposal. These are on-going efforts :

- a) Development of radiation-hard silicon strips detectors with Imperial College and University of Turin, geared towards production at S.I.

- b) Cooling, alignment and mechanical structures with Cracow University.

- c) Data acquisition with Cracow University and Rutherford-Appleton Laboratory.

- d) Front-end development with Rutherford-Appleton Laboratory, University of Turin and Cracow University. The emphasis here is on fast shaping and a purely digital readout.

Moreover, the superior noise performance and radiation hardness of bipolar technologies are exploited. There exists familiarity with radiation-hard technologies in the U.S.

The fact that this R&D effort at SCIPP is parallel to their HERA/SSC R&D will provide a potential for exploring a variety of technical solutions. Participating SCIPP personnel will be: Hartmut Sadrozinski, Nicolo Cartiglia, Katherine O'Shaughnessy, Daniel Pitzl, Ned Spencer, David Dorfan and Joel DeWitt.

A first preliminary division of tasks, best suited to available or to be created infrastructures in the different laboratories is summarized in Table 1.

Table 2 summarizes a budget request for the first two years of activity. Projects concerning detectors assume that developments will be made in parallel with several different firms. This is essential since it is expected that different technologies have to be investigated to find an optimal solution. The figures indicated in Table 2 are mostly the processing costs of devices in specialized foundries. Point 1 under electronics includes one prototype run each year to develop bipolar front-ends for the Pb-Pb SPS experiment, which will be undertaken by the Turin group. Some special equipment will have to be bought and circuit design and fabrication of PCBs and ceramic hybrids is foreseen. Points 6 and 7 under the heading of electronics cover special equipment not available in participating laboratories. A small amount of travel money is included for allowing people who have limited support from their home institutes to come to meetings and visit firms and pay subsistence for short-term stays at CERN.

| Table 1 |

|---------|

|---------|

| ACTIVITY INSTITUTE =                | 1 | 2     | 3          | 4 | 5   | 6        | 7        | 8 | 9        | 10  | 11 | 12      | 13 |

|-------------------------------------|---|-------|------------|---|-----|----------|----------|---|----------|-----|----|---------|----|

| SIMULATIONS                         |   | † – T | <u> </u>   | T | İ   |          | Î        |   | <u> </u> | h   |    |         |    |

| (i) Physics performance of tracker  |   | X     | t          |   | X   |          | X        |   |          | ļ   |    |         |    |

| (ii) Mechanical structures          |   | X     |            |   | Ľ.  |          | X        |   |          |     |    | <b></b> |    |

| (iii) Electronics using CAE tools   | X | l .   |            |   | 1   | <b> </b> | <u> </u> |   |          |     |    |         |    |

| (iv) Detectors                      | X | X     |            |   |     |          | [        |   |          | 1   |    |         |    |

| DETECTORS / TEST STRUCTURES         |   |       | T          |   | T T |          |          |   | Τ        | l l |    |         |    |

| (i) Design                          | 1 |       | X          | X | X   |          |          | X | X        | X   |    |         |    |

| (ii) Evaluation (C-V,I-V)           | X | X     | X          | X | X   |          | X        | X | X        | X   | X  | X       |    |

| (iii) Assembly / bonding            | X |       |            |   |     |          |          |   | X        |     | -  |         |    |

| (iv) Detectors + chip test          | X | X     |            | X | X   | X        |          |   | X        | X   | X  | X       |    |

| (v) Test beam                       | X | X     |            | X | X   | X        | X        |   | X        | X   | X  | X       |    |

| (vi) Bump bond development          |   |       |            | X | X   | X        |          |   | X        |     |    |         |    |

| (vii) Mechanical precision mounting | X |       |            |   |     |          | [        |   | X        | X   |    |         |    |

| (viii) Processing                   |   |       | X          |   |     |          |          | X |          |     |    |         |    |

| FRONT-END ELECTRONICS               |   | Ī     |            |   |     |          |          |   | Γ        |     |    |         |    |

| (i) Design                          | X |       |            |   |     | X        |          | X | X        | 1   |    |         |    |

| (ii) Prototype device testing       | X | X     |            | X |     | X        | 1        |   | X        |     |    |         |    |

| (iii) Chip testing                  | X |       |            | X |     | X        |          |   | X        |     |    |         |    |

| (iv) Systems tests                  | X |       |            | X |     |          |          |   |          | [   |    |         |    |

| (v) Hybrids, special technologies   | X |       |            |   |     |          |          |   |          |     |    |         |    |

| (vi) PCB, auxiliary electronics     |   | X     |            | X |     |          | X        |   | X        |     |    |         |    |

| (vii) Pure digital design           |   | X     |            |   |     |          |          |   | X        |     | X  |         | X  |

| IRRADIATIONS (e, y, n, p)           | X |       |            |   | X   | X        |          |   | X        | X   |    |         | X  |

| MECHANICS                           |   |       |            |   |     | I        |          |   |          |     |    |         |    |

| (i) Cooling                         |   | X     |            |   | X   |          |          |   |          |     |    |         | X  |

| (ii) Prototypes                     |   | X     |            |   |     |          | X        |   | X        |     |    |         | X  |

| ALIGNMENT                           | X | X     |            |   |     |          |          |   |          |     |    |         | X  |

| DAQ                                 |   | X     |            |   |     |          |          |   |          |     |    |         | X  |

| BEAM TESTS                          |   |       |            | I |     |          |          |   | J        | Ĭ   |    |         |    |

| (i) Running                         | X | X     | <b>—</b> — | X | X   | X        | X        |   | X        | X   | X  | X       |    |

| (ii) Analysis                       |   | X     |            | X | X   |          | İ        |   | X        | X   | -  |         |    |

- CERN

- CERN Inst. of Nucl. Physics, Cracow IHP, Frankfurt/Oder University of Helsinki Imperial College London CPPM, Marseille University of Oslo

- 2 3 4 5 6 7

- SI, Oslo Rutherford-Appleton Laboratory LEPSI, Strasbourg INFN, Torino Yale University SCIPP, Santa Cruz

- 9 10

- 13

#### Table 2

| Estimated Budget for Development of Si Strip detectors,                           |  |  |  |  |

|-----------------------------------------------------------------------------------|--|--|--|--|