# The electronics of the INDRA $4\pi$ detection array

J.Pouthas<sup>1\*</sup>), A.Bertaut<sup>1</sup>). B.Borderie-<sup>1</sup>. P.Bourgault<sup>1</sup>. B.Cahan<sup>3</sup>), G.Carles<sup>3</sup>), D.Charlet<sup>2</sup>), D.Cussol<sup>4</sup>), R.Dayras<sup>3</sup>), M.Engrand<sup>2</sup>). O.Jouniaux<sup>5</sup>). P.Le Botlan<sup>4</sup>), A.Leconte<sup>4</sup>). P.Lelong<sup>2</sup>), L.Martina<sup>1</sup>), P.Mosrin<sup>4</sup>). L.Olivier<sup>1</sup>. J.P.Passerieux<sup>3</sup>; B.Piquet<sup>1</sup>), E.Plagnol<sup>1\*</sup>). E.Plaige<sup>5</sup>), B.Raine<sup>1</sup>), A.Richard<sup>2</sup>). F.Saint-Laurent<sup>1</sup>), C.Spitaels<sup>1</sup>). J.Tillier<sup>4</sup>), M.Tripon<sup>1</sup>). P.Vallerand<sup>1</sup>), P.Volkov<sup>2</sup>) and G.Wittwer<sup>1</sup>).

<sup>1)</sup> GANIL, IN2P3-CNRS et DSM-CEA, BP 5027, 14021 Caen Cedex, France.

<sup>2)</sup> Institut de Physique Nucléaire, IN2P3-CNRS, 91406 Orsay Cedex, France.

<sup>3)</sup> CEA, DAPNIA, CE Saclay, 91191 Gif sur Yvette, France.

<sup>4)</sup> Laboratoire de Physique Corpusculaire, IN2P3-CNRS et Université de Caen, ISMRA, 14050 Caen Cedex, France.

<sup>5)</sup> Laboratoire de l'Accélérateur Linéaire, IN2P3-CNRS, 91405 Orsay Cedex, France.

<sup>\*)</sup> Present address: Institut de Physique Nucléaire. 91406 Orsay Cedex. France.

# The electronics of the INDRA $4\pi$ detection array

J.Pouthas<sup>1\*</sup>), A.Bertaut<sup>1</sup>), B.Borderie<sup>2</sup>), P.Bourgault<sup>1</sup>), B.Cahan<sup>3</sup>), G.Carles<sup>3</sup>), D.Charlet<sup>2</sup>), D.Cussol<sup>4</sup>), R.Dayras<sup>3</sup>), M.Engrand<sup>2</sup>), O.Jouniaux<sup>5</sup>), P.Le Botlan<sup>4</sup>), A.Leconte<sup>4</sup>), P.Lelong<sup>2</sup>), L.Martina<sup>1</sup>), P.Mosrin<sup>4</sup>), L.Olivier<sup>1</sup>), J.P.Passerieux<sup>3</sup>), B.Piquet<sup>1</sup>), E.Plagnol<sup>1\*</sup>), E.Plaige<sup>5</sup>), B.Raine<sup>1</sup>), A.Richard<sup>2</sup>), F.Saint-Laurent<sup>1</sup>), C.Spitaels<sup>1</sup>), J.Tillier<sup>4</sup>), M.Tripon<sup>1</sup>), P.Vallerand<sup>1</sup>), P.Volkoy<sup>2</sup>) and G.Wittwer<sup>1</sup>).

#### **Abstract**

INDRA is a  $4\pi$  detection array designed for the studies of "hot nuclei" at the heavy ion accelerator GANIL. The INDRA multidetector is composed of 96 ionization chambers, 196 silicon detectors, 324 CsI(Tl) scintillators and 12 NE102/NE115 phoswich detectors. This article describes the associated electronics. The signal treatment is performed through specifically designed modules, most of which are in the new VXIbus standard. This standard allows us to considerably reduce the number of modules by regrouping many functions in the same module. For example, all the functions related to 24 CsI(Tl) scintillators are stacked in one D-size module. VXIbus also provides the opportunity to locate all the electronics close to the detector, in the beam cave, with full remote control (VXI-VME buses) including visualization of analogic and logic signals on oscilloscopes. The large dynamic range (4000 to 1) required for the silicon detectors is reached by means of a new method: a low noise amplifier providing a unipolar signal which is charge integrated and converted on two dynamic ranges. The trigger system relies on a new working mode called "asynchronous mode" and performs event selections based on multiplicity functions which are built up from subgroups of detectors. The performances of the data acquisition and the graphical software packages which were developed to set up and control the electronic parameters are also presented.

Submitted to Nuclear Instruments and Methods

<sup>1)</sup> GANIL, IN2P3-CNRS et DSM-CEA, BP 5027, 14021 Caen Cedex, France.

<sup>2)</sup> Institut de Physique Nucléaire, IN2P3-CNRS, 91406 Orsay Cedex, France.

<sup>3)</sup> CEA, DAPNIA, CE Saclay, 91191 Gif sur Yvette, France.

<sup>4)</sup> Laboratoire de Physique Corpusculaire, IN2P3-CNRS et Université de Caen, ISMRA, 14050 Caen Cedex, France.

<sup>5)</sup> Laboratoire de l'Accélérateur Linéaire, IN2P3-CNRS, 91405 Orsay Cedex, France.

<sup>\*)</sup> Present address: Institut de Physique Nucléaire, 91406 Orsay Cedex, France.

#### 1. Introduction

The formation and decay of hot nuclear systems formed in heavy ion collisions at intermediate energies is one of the major research axis at GANIL (Grand Accélérateur National d'Ions Lourds, Caen, France). The ultimate goal is to form highly excited nuclei at the "limit of stability". In the last few years, theoretical approaches predicted new decay modes for these nuclei, especially the possibility of a "sudden multifragmentation" of the nucleus, accompanied or not, by a phase transition. The de-excitation of very hot nuclear systems is characterized by the emission of a large number of "light charged particles" (hydrogen and helium nuclei) and, to a lesser extent, heavier fragments. Experimental studies require an event by event detection of all particles and fragments, with precise measurements of their number, their size (charge, mass), their spatial distribution and their energy. To satisfy these requirements, the community of physicists interested in the multifragmentation process at the GANIL Facility decided in 1989 to undertake the construction of INDRA which is able to detect, in charge, complete or quasicomplete events. In 1993 and 1994, two sets of experiments which lasted two months each were successfully run with INDRA. Argon, nickel, krypton, xenon, gadolinium, tantalum and uranium beams bombarding various targets were used.

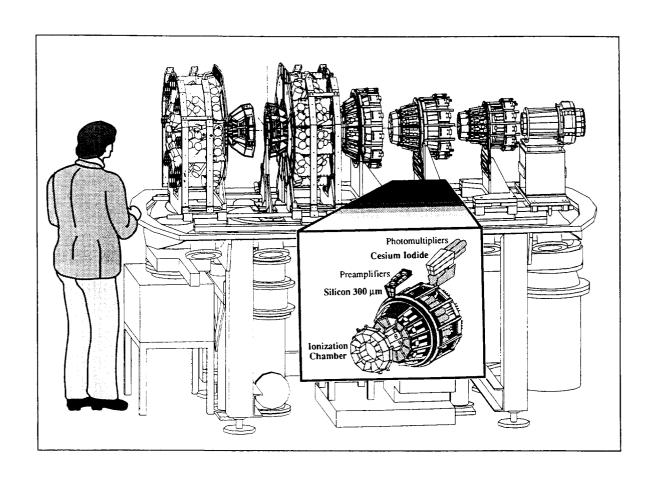

A split view of INDRA is shown in Fig. 1. The multidetector array which operates in vacuum, covers about 90% of the space around the target. It can be schematically described as an ensemble of 336 detection cells arranged according to 17 rings centered on the beam axis. In order to compensate the forward peaked angular distributions of emitted particles, the solid angle subtended by each cell increases by a factor of 100 from ring 1 (forward angles) to ring 17 (backward angles). Due to high counting rates expected at very forward angles, the first ring  $(2^{\circ}<\theta<3^{\circ})$  is made of 12 fast NE102/NE115 phoswich detectors, enabling charge identification up to Z=30 for fragments having an energy greater than 20 A.MeV. For rings 2 to 9  $(3^{\circ}<\theta<45^{\circ})$ , the charge identification (up to Z = 50) is achieved through the usual  $\Delta$ E/E method, by measuring the energy deposited in three detection layers of increasing thickness: a low pressure gas-ionization chamber, a 300 µm thick silicon detector and a CsI(Tl) scintillator thick enough (14 to 10 cm depending on the ring) to stop all particles. In the last 8 rings (45°<θ<176°), the energy range of the fragments is much smaller and only two stages of detection are used: gas ionization chambers and CsI(Tl) crystals of a thickness from 8 to 5 cm. The ionization chamber layer with almost  $4\pi$  solid angle coverage and high geometrical efficiency is certainly the most original feature of the detector, since it gives charge identification from very low energy thresholds (≈ 1 A.MeV). Identification of H and He isotopes is obtained by using pulse shape discrimination techniques on the CsI(Tl) detector signals. INDRA is therefore composed of 12 phoswich detectors, 96 ionization chambers, 180 silicon detectors and 324 CsI(Tl) scintillators. For energy calibration purposes, rings 10 to 17 ( $45^{\circ} < \theta < 176^{\circ}$ ),

which do not incorporate silicon detectors were each equiped with a two-element telescope (80  $\mu$ m and 2 mm thick silicon detectors). The INDRA  $4\pi$  array, the detectors and the performances obtained are presented in Ref. [1]. The present paper presents the electronics which was not described in this reference.

The INDRA detectors have the intrinsic capacity of satisfying the required specifications concerning nucleus identifications and energy resolutions. However, the energy measurements must be performed on a large dynamic range as, for example, from 1 MeV to 4 GeV for silicon detectors with an energy resolution of a few hundred of keV. Such a performance could not be obtained by using conventional methods and commercially available electronic modules. Furthermore, the complexity of the electronics associated with the large number of channels raises some difficulties related to its tuning, control and overall management. Consequently, a number of complementary requirements were placed on the design of the INDRA electronics and data acquisition: i) a very low noise level and a large dynamic range, ii) a close proximity to the detector, iii) a minimum number of connectors, iv) a full software control of settings, v) a compatibility with the VME based GANIL acquisition [2] and vi) an easy visualization of the relevant signals. To meet these requirements the electronics had to be adapted to the specifications of the detectors and so, most of the electronic modules were designed and constructed by the collaborating laboratories. Among the particular features which contribute to the final performance, the following should be pointed out. An important effort was invested in the design of the reaction chamber, the detectors, the front end electronics and connections, with special care being paid to the ground reference in order to avoid crosstalk and ground loop effects. Requirements i)-ii) imply that the front end electronics (preamplifiers and photomultiplier bases) are located inside the reaction chamber, as close as possible to the detectors. These devices and their associated cable connections which must be fed through the vacuum chamber are presented in section 2. In order to entirely fulfill the requirements i) and ii), it was also decided that all the electronics should be placed in the beam cave. In conjunction with items iv) and v), this had important consequences concerning the choice of a new standard: the VXIbus. The VXIbus [3] has been developed for high quality electronic applications and compatibility with the VME computer bus. It allowed us to considerably reduce the number of modules and connections (item iii) by grouping many functions in the same module. This choice also has the additional advantage of allowing the development of an easy to use and remotely controlled visualization of the signals (item vi) without cable disconnections. The INDRA electronic architecture which is largely based on the VME and VXI buses is discussed in section 3.

In relation to signal processing and encoding, INDRA is composed of two kinds of detectors: i) Scintillators (phoswich and cesium iodide) which need a double signal integration in a "fast gate" and a "slow gate"; ii) Ionization chamber and silicon detectors for which energy measurements have to be done on a large dynamic range (more than 1000 to 1). This last

performance is obtained by means of a new method which is discussed in section 4. The associated electronic modules are presented in the same section. The signals coming from the CsI(Tl) scintillators are fed to 24 input VXIbus modules containing all the necessary processing functions. This module is presented in section 5. A similar VXIbus module with 16 inputs is used for the phoswich detectors. The new method of triggering called "asynchronous mode" is briefly described in section 3 and their associated electronic modules are presented in section 6. The time measurements (10 ns resolution) necessary to estimate the importance of random coincidences are performed in 96 input VXIbus modules which are briefly described in the same section. Section 7 presents the data acquisition system and its performances as well as the graphical software packages developed for the control of the electronic modules.

# 2. Electronics inside the vacuum chamber

The 336 photomultiplier bases associated with the scintillators (324 CsI(Tl) and 12 NE102/NE115 detectors) and the 292 charge preamplifiers coupled to the ionization chambers (96 channels), the 300 µm thick silicon detectors (180 channels) and the calibration telescopes (16 channels) must work under vacuum. This section presents these devices and discusses the problems of power consumption. In order to satisfy the requirements of very low crosstalk and noise levels in signal transmissions, a standardized system of connections has been developed. This system, also used for the analog transmission of signals between the electronic modules, is described at the end of this section.

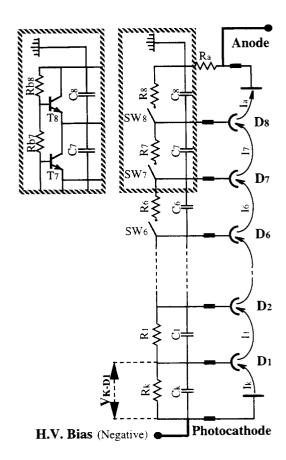

#### 2.1 Low consumption and fast recovery photomultiplier bases

The decay time of CsI (Tl) crystals consists of two components of  $\approx 0.5~\mu s$  and  $\approx 7~\mu s$ . This means that, for a given signal amplitude, the total charge is much higher than that usually given by other scintillators. Therefore, the associated photomultiplier has to deliver high charge output per signal and this demand is equally required of the photomultiplier base. It became rapidly clear that the standard RC chain was inadequate [4]. We turned therefore to a transistorized photomultiplier base. Fig. 2 shows the principle of such a base for a 8 dynode (D<sub>1</sub> to D<sub>8</sub>) photomultiplier. The charge supplies to the dynodes are the capacitors  $C_k$  to  $C_8$ . As these capacitors are discharged by dynodes, one has to replenish them as quickly as possible in order to maintain the stability of the interdynode voltages. It is the bias current,  $I_b$ , which replenishes the capacitors  $C_k$  to  $C_8$ . Since the maximum signal is given at the output stage (the anode), the capacitor  $C_8$  must deliver the maximum charge  $Q_8 = Q_a$  and has to be replenished with the whole current,  $I_b$ . This is accomplished by opening the switch  $SW_8$  so that the total bias current  $I_b$  rushes into the  $C_8$  capacitor, to make up for the lost charge  $Q_8$ . As soon as the  $C_8$  capacitor is

recharged, the switch  $SW_8$  closes again, so that  $I_b.R_8$  equals the voltage  $V_{C8}$ . One practical solution of the  $SW_8$  switch could be obtained by a transistor as shown in the inset of Fig.2. The switches  $(SW_8, SW_7...)$  of Fig. 2 are only used where the discharge of the interdynode capacitors is significant. Practically, one only controls 3 to 5 stages by switches. The rest of the chain is of the RC-type. Such a transistorized photomultiplier base works well if it is adapted to the charge of the anode signal and the counting rate.

The bias current is calculated by:

$$I_b \ge 2.7 \lambda Q_a \tag{1}$$

and the capacitor C<sub>8</sub> is given by:

$$C_8 \ge 10^2 \, Q_{a \, \text{max}} / \, V_8$$

(2)

where  $\lambda$  is the average counting rate,  $Q_a$  the average anode charge,  $Q_{a \; max}$  the maximum anode charge and  $V_8$  the DC voltage of dynode  $D_8$ .

The subsequent capacitor  $C_7$  is calculated by  $C_7 \ge C_8$  /  $g_8$ , where  $g_8$  is the current gain of the dynode  $D_8$ . Similarly,  $C_6 \ge C_7$  /  $g_7$ . If we want an average anode signal of 2.5 V pulse height (which corresponds to a charge  $Q_a = 55$  nC) with an average counting rate of  $\lambda \le 500$  counts/sec, the expression (1) gives us  $I_b \ge 75$   $\mu A$ . As the transistors  $Q_8$  and  $Q_7$  need a minimum quiescent current of approximately 10  $\mu A$ , the bias current will be  $I_b = 85$   $\mu A$ .

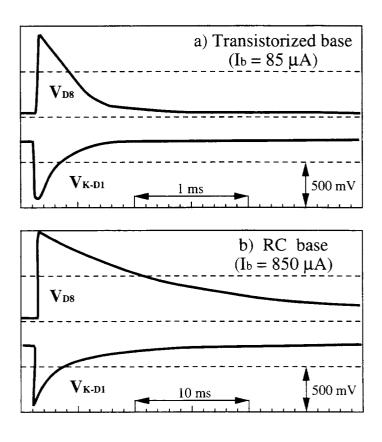

Fig. 3-a shows the waveforms of the dynode D8 voltage ( $V_{D8}$ ) and the cathode K-dynode  $D_1$  voltage ( $V_{K-D1}$ ) for a transistorized photomultiplier base with  $I_b = 85~\mu A$  and for an anode signal of 2.5 V. The photomultiplier type is the Philips XP2961. One can note that the voltage  $V_{D8}$  across  $C_8$  drops to less than 1V and that the capacitor is replenished within 700  $\mu s$ . The  $V_{K-D1}$  voltage also drops to less than 1V and recovers within the same time as  $V_{D8}$ . The curves were obtained by a computer simulation (VALID-AWB), but the measurements performed on a real photomultiplier base gave the same results. The excellent simulation precision is due essentially to the correct photomultiplier modelling. For comparison purposes, one can find in Fig. 3-b, the waveforms in the case of a resistor-only (or RC) photomultiplier base. Note that the bias current is  $I_b = 850~\mu A$ , a value which is ten times greater than that for the transistorized base. For this RC-base, the voltage  $V_{D8}$  recovers exponentially with a constant of around 15 ms and reaches 90% of its original value in a time greater than 40 ms.

The transistorized photomultiplier base developed for the INDRA detector dissipates 10 times less power and recovers 30 times faster than its resistor-only (or RC) counterpart. The low power consumption of these bases allows one to work under vacuum without cooling. The maximum counting rate fixed at 500 counts/sec is sufficient for the CsI(Tl) detectors of rings 4 to 17. However, in rings 2 and 3 the base current is  $I_b = 150~\mu A$  in order to accept counting rates up to 1000 counts/sec. A similar transistorized base has been developed for the 12 phoswich (NE102/NE115) detectors. Due to the relatively fast decay constant of the scintillators (2.4 ns for the NE102 and 240 ns for the NE115), the maximum counting rate has been

increased to 5000 counts/sec with a base current of 200  $\mu$ A. A cooling of the photomultiplier bases is still not necessary.

#### 2.2. The charge preamplifiers

The charge preamplifiers are associated with two types of detectors for which the required characteristics are different. Due to the low energy deposit and low current conversion in the ionization chamber, the preamplifier must have a very high sensitivity together with a low noise. Conversely, the main feature of the silicon detector preamplifier is its high dynamic range capability which leads to a low sensitivity and thus to a channel noise figure dominated by the following amplifier (see below, section 4). Therefore, two types of preamplifiers were developed. In order to fulfill the characteristics requirements and to get low overall dimensions, both preamplifiers are constructed with SMT (Surface Mounted Technology) components.

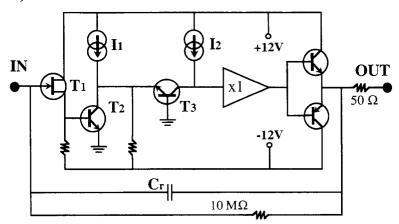

Fig. 4-a shows the circuit diagram of the ionization chamber preamplifier. The input stage is a conventional cascode circuit composed of a field-effect transistor T<sub>1</sub> of transconductance g<sub>m</sub> followed by a fast current amplifier  $A_i$  of gain  $G_i$ . This stage  $(T_1, A_i)$  is equivalent to a transistor of  $g = g_m \times G_i$ transconductance. Thus, the open-loop voltage gain is increased by the factor G<sub>i</sub> and reaches 30 000 in the filter band-pass (100 kHz). The dynamical capacitance is around 6 nF, a value which is greater than the few pF detector capacitance. The preamplifier output stage delivers negative or positive signals with a maximum amplitude for a linear response of 5 V on 100  $\Omega$ , i.e. 2.5 V on the 50  $\Omega$ impedance of the amplifier input. The very high sensitivity is obtained by a low feedback capacitor C<sub>r</sub> of around 0.22 pF. This sensitivity which is equivalent to 200 mV/MeV for silicon detectors leads to pulse amplitudes of 20 mV/MeV for ionization chambers filled with C<sub>3</sub>F<sub>8</sub> gas. The capacitor C<sub>r</sub> of 0.22 pF is not available as a component and moreover the interference circuit capacitors must be included in this value. In fact, the capacitor C<sub>r</sub> is made of two copper lines which are separated by a short distance on the printed circuit board. The value of C<sub>r</sub> is adjusted by increasing the distance between the two copper lines. The value is fixed by a bench test measurement where the preamplifier sensitivity is compared to a reference one. This method allowed us to adjust the 96 preamplifier sensitivities to within 1%. The main characteristics of these charge preamplifiers are given in Table 1. They have been controlled for the 96 devices on the test bench constructed for the gain tuning.

Fig. 4-b shows the circuit diagram of the silicon detector preamplifier. The most important feature is the high dynamic range needed and thus one must consider, instead of the noise, the open-loop voltage gain and the rise time characteristics. The input stage is a field-effect transistor  $T_1$  working as an impedance corrector. The high open-loop voltage gain is obtained by a cascode circuit composed of the bipolar transistors  $T_2$  and  $T_3$ . This gain is controlled through the variation of the dynamical input impedance of  $T_2$  with the value of the current generator  $I_1$ . The open-loop voltage gain, measured in the filter band-pass (100 kHz), is around 100 000. The preamplifier output stage works for the two signal polarities. Nevertheless, a fast signal rise time of 25 ns is only obtained on

the negative excursion for the full dynamic range with a 200 pF detector capacitance. In fact, the preamplifiers were optimized for negative output signals and the capacitances of the INDRA 300  $\mu m$  thick silicon detectors which vary from 140 pF to 400 pF. The preamplifier output stage delivers negative output signals of up to -10 V on 100  $\Omega$ , i.e. -5 V on the 50  $\Omega$  impedance of the amplifier input. The 180 devices were checked on a test bench. The sensitivity variations do not exceed  $\pm$  1% as expected with the choice of the  $C_r$  component (COG in the EIA specification : value within  $\pm$  1%, temperature coefficient of 0  $\pm$  30 ppm / °C). The main characteristics of these charge preamplifiers are summarized in Table 4. The 16 silicon detectors which compose the 8 calibration telescopes are equipped with similar charge preamplifiers which provide positive output signals with maximum amplitudes of + 5 V on 100  $\Omega$ .

As discussed in Ref [1], the preamplifiers are located as close as possible to the detectors and are mounted in groups of 4 to 6 devices on multilayer printed circuit boards. The large dynamic range needed in the energy measurements led us to develop charge preamplifiers which can deliver high amplitude signals. Even if particular care was taken in the preamplifier designs, the power consumption is too high for working under vacuum conditions [1]. A water based cooling system had to be implemented in order to remove the excess heat. After 10 hours of water circulating at 10 °C, the temperature stabilizes at 20°C on the mechanical supports of the printed circuits boards.

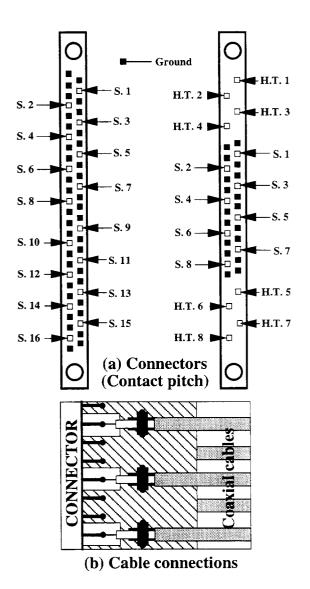

## 2.3. Analog signal transmission. Cables and connectors

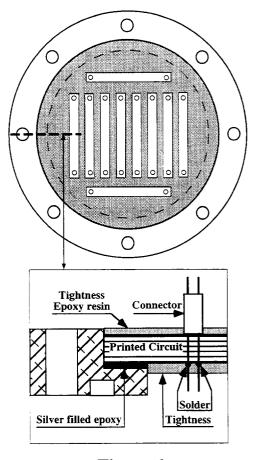

The photomultiplier bases and the preamplifiers are located in the vacuum chamber. These devices must be connected to the electronic modules with a relatively large number of cables: 888 for signal transmissions and 405 for high voltage power supplies. Moreover, due to the large dynamic range in energy measurements, the noise pickup and the cross-talk between channels must be held at very low levels. In order to meet these requirements and to reduce the costs, a specifically designed system of coaxial cable connections has been developed. This technique makes use of standard and low cost 2.54 mm contact pitch connectors, as shown in Fig. 5. Two types of connections have been standardized and implemented on the vacuum chamber flanges. The signals and the moderate high voltage bias (< 600 V) associated with the ionization chambers and the silicon detectors are grouped by 16 channels (S.1 to S.16) on a 53-contact connector (Fig. 5-a, left-hand side). The ground shielding between the channels is ensured by the remaining 37 contacts and the implementation of the coaxial cables as shown in Fig. 5-b. The braids of the coaxial cables are soldered on both sides of a three-layer printed circuit board. The central layer of this circuit is also grounded. The interconnections of analog signals between the electronic modules also rely on the same technique. The coaxial cables are grouped by 8 on a 29-contact connector with a distribution of the 8 signals and ground interconnections corresponding to half (S.1 to S.8) of the 53-contact connector of Fig.5-a. Despite a non-coaxial transmission through the connectors, the short distance involved together with the relatively slow rise time of the signals (> 25 ns) does not introduce significant signal perturbations. The most important feature is the high performance of this design technique in regard to electro magnetic compatibility (EMC). In particular, a very low cross-talk is obtained and a signal of 5 V in amplitude and 25 ns rise time induces on an adjacent channel an interference signal of less than 1 mV in amplitude. For the scintillator detectors, the high voltage biases of the photomultipliers are set between 1000 V and 1600 V. Another connector was designed for the connections through the vacuum chamber flanges (Fig. 5-a, right-hand side). In order to obtain a safe distance between the high voltage contacts, the grounded contacts surrounding them were removed. We checked that this type of connection gives satisfactory working conditions for high voltages up to 3000 V. For the signal connections we kept the same design with grounded contacts around S1 to S8. Such a technique allows us to connect, on one small-sized device, a set of 8 scintillator detectors. The implementation of the connectors on the vacuum chamber flange is shown in Fig. 6. Ten connectors are soldered onto a printed circuit of 160 mm diameter and 6 mm thickness. All ground contacts are connected to a plane which constitutes a ground reference connected to the flange, and so to the reaction chamber, by a silver-filled epoxy glue (EPO-TEK H20E from Epoxy Technology). The reaction chamber which is electrically insulated from the beam pipe and the floor can then be considered as the main ground reference of the setup. The air-tighness is obtained by the contact soldering on the printed circuit and reinforced by the deposit of an insulated epoxy resin (EPO-TEK H77) on both sides of the printed circuit. In order to respect the two connector designs, two types of printed circuit are used. On the flange associated with the scintillator detectors, one can connect 80 detectors, i.e. 80 signal and 80 high voltage lines. For the other detectors, the number of available coaxial connections is 160.

#### 3. Electronics architecture

The design of electronics with commercially available NIM or CAMAC modules would have led to a large number of them with a numerous connections and several front pannel adjustements of parameters. Moreover, the high dynamic range energy measurements are very difficult to perform following the classical signal processing method provided by these modules. Facing these problems and in order to reduce the costs and increase the quality and the reliability of the system (see section 1), we decided to design and build electronic modules using mainly a new standard, the VXIbus (VME Extension for Instrumentation). Developed by a consortium of test equipement manufacturers, VXIbus [3] is an architecture for modular instruments based on the VME computer bus [5] which was already used for data acquisition at GANIL [2]. This being the main reason for our choice, we can mention other advantages: a good shielding of the modules, a satisfactory Power Distribution Bus (±24V, ±12V, - 5.2V, +5V, -2V), multiple possibilities of connections by different backplane buses (ECL or TTL lines, clock signals). A VXIbus system consists of a central timing module (Slot 0) and up to

12 additional instrument modules in four different sizes with the same width (1.2 in.). We choose the bigger one (D size: 14.4 in. x 13.4 in.) which provides all VXIbus facilities and gives the maximum room for implementation of analog components on daughter boards and so allowing a considerable reduction in the number of modules.

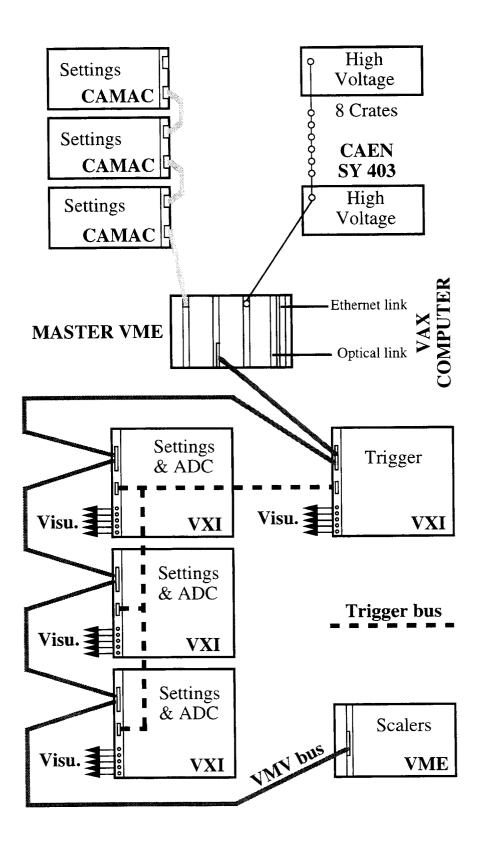

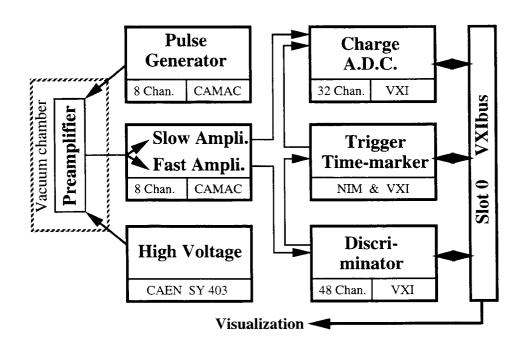

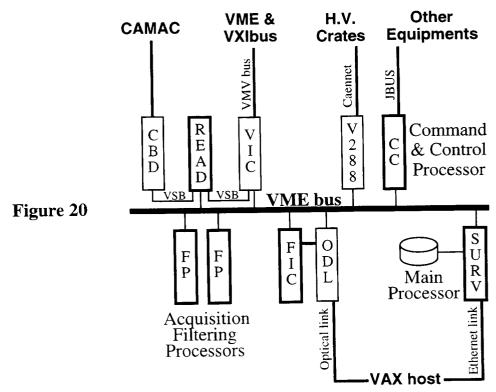

Fig. 7 shows the architecture of the electronics which is, as indicated in section 1, located in the beam cave with no access during the beam periods. The data acquisition system is the standard GANIL one running on VME based CPU and an optical fiber link transmission to a central VAX computer [2]. Using VXIbus does not mean that the totality of the electronic modules must be constructed in this standard. The link between the VME and the CAMAC crates is still available and we used CAMAC modules to implement functions which do not need fast data readout. The high voltage power supply system is composed of 8 CAEN Model SY403 crates [6]. Each crate contains up to 64 independent channels arranged in boards of 16 channels and the system is controlled via the serial link "caenet" from the VME. The scalers are VME modules (16 channels CAEN modules, [6]) and are housed in one VME crate which is linked to the central VME master crate by the VMV bus provided by the CES company [7]. The same solution has been adopted to incorporate the VXIbus. The Slot 0 modules are the STR8032 ones, designed at the Daresbury laboratory [8] and commercially available from the Struck company [9]. The board for this module allows one to accommodate any commercial VME processor and we used the VIC8250 from CES which contains the access through the VMV bus. As a consequence, for data acquisition and parameter software control, the VXIbus system works like the VME one. These Slot 0 modules also provide access to some of the VXIbus backplane lines through front pannel connectors and buffered circuits. This facility allowed us to distribute the trigger signals to the modules by a "trigger bus" simply connected from the trigger VXIbus crate to the Slot 0 modules of the other crates. It also permitted the introduction of standardized remote visualizations of signals. On the VXIbus crate backplane, five lines are assigned to these functions: 2 lines for analog signals, 2 lines for logic ones and 1 line for coincidence adjustments ("gate control"). Under software control, the signals inside the modules can be multiplexed and accessed through 5 coaxial connectors (Lemo 00) on the VXIbus Slot0 front panel and displayed on oscilloscopes. Thus, the connections to the INDRA electronics are reduced to VME-Computer links (Ethernet and data optical fibers) and to a set of 20 coaxial cables (5 per VXIbus crate) for remote visualization of signals.

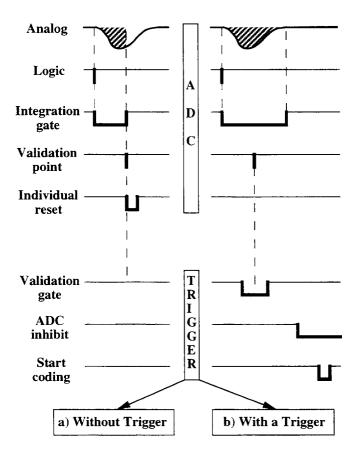

A new method for the ADCs timing has been introduced. Fig. 8 shows schematically its logic, called "asynchronous mode". The integration gate opens when the corresponding discriminator fires and without any logic condition coming from the trigger. At the end of a delay of around 1 µs, a "validation point" is generated. Each encoding channel cycles on its own (start -> integration gate and validation point -> reset) as long as the event configurations are rejected by the trigger (fig. 8a). Once a configuration is accepted, the trigger issues a "validation gate" to all the encoding modules enabling to proceed and to convert only those

channels which have their "validation point" in coincidence with the trigger gate (Fig. 8b). A "start coding" signal generated by the trigger starts the digital conversion. During this operation, and until a reset is emitted at the end of data acquisition, all the channels are disabled by a general "ADC inhibit" signal. The fact that the validation is delayed by 1 µs gives time to prform complex triggering functions and to wait for slow detectors. However, the most important advantage stands in the individual channel working which avoids the use of cumbersome long delay lines which deteriorate the linear signals.

Table 2 summarizes the INDRA standardized buses, their functions and their implementation in the VXIbus system: external access through the Slot 0 module and distribution on the VXIbus backplane. The "trigger bus" which achieves the connections between the trigger crate and the other ones, is composed of 9 logical lines: two "validation gates" (same function with different timing settings), "start coding", "ADC inhibit", "general reset", "discriminator inhibit" (used to stop all discriminators), "ADC test" (used to fire the test pulse signals directly inside the encoding modules) and two lines used for data acquisition purposes ("ADC coding line" and "ADC reading line"). The parameter settings are provided by VME and digital to analog conversion inside the modules. Results of this conversion can be controlled in the Slot 0 (ADC conversion and VME reading) in sending the analog value on the "voltage measurement" line. In the VXIbus standard, 2 clock signals of 10 MHz and 100 MHz frequencies are generated in the Slot 0 module and distributed in the crate. Both of them have been used in the trigger module and the 10 MHz line for logic sequencing in the other modules. Among the advantages of VXIbus, we can also underline the autoconfiguration of modules. The individual module identification line, MODID, allows one to test for the presence of a module, and to identify each module's location by a slot number. The system automatically identifies each device, its type, model manufacturer, and all the requirements of memory loading. As a consequence, all modules can be directly accessed for initialization or data readout without any modification of the acquisition files, even if a module location has changed.

# 4. Large dynamic range energy measurements (ionization chambers and silicon detectors)

#### 4.1. Limitations of classical electronics

In association with an ionization chamber or a silicon detector, a charge preamplifier normally preserves the intrinsic high resolution energy capability of these detectors. The energy measurements are usually achieved by a "spectroscopy amplifier" and a peak sensing ADC. However, the dynamic range that can be covered by a standard electronics is generally limited to 100 to 1. The main reason for this limitation comes from the stretcher of the ADC which cannot

satisfactorily work on low level signals with rise times of a few µs. In order to obtain a higher dynamic range, a second amplifier with a different gain is generally introduced. For example, one amplifier and its associated ADC covers the energy range from 1 MeV to 100 MeV whereas the second chain is adjusted for the 10 MeV to 1 GeV range. This method is not free of difficulties, particularly with regard to the very long recovery times of the high gain amplifier for energies largely exceeding its range. The electronics generally used with a ionization chamber or a silicon detector has been developed for very high resolution and low dynamic range energy measurements. In these spectroscopy amplifiers, one of the most important features is the optimization of the signal to noise ratio. This leads to complex shaping networks such as the approximate semi-Gaussian shaping performed with a network consisting of a CR differentiation followed by four RC integration stages. The large number of channels (292) needed to equip INDRA and the limitations and relative complexity of classical electronics led us to study new methods of energy measurement on a large dynamic range .

# 4.2. A new method: a low gain amplifier and a double charge encoding

In order to overcome the dynamic range limitation due to the pulse height encoding, one could introduce an acceptance time window centered on the peak of the amplifier pulse. Satisfactory working conditions of the ADC stretcher could be obtained if care has been taken to ensure the timing accuracy of the gate signal. To avoid precision timing considerations, which are basically non necessary in INDRA, we turned to another method based on charge sensitive ADCs. Let us assume that the amplifier output is purely unipolar and that a logic pulse (a gate) with a width larger than the linear signal could be generated (these hypotheses will be discussed below). A charge integration of the amplifier pulse is performed during the gate and thus a voltage proportional to the surface of the linear pulse is obtained. Concerning the dynamic range, there is no limitation due to the noise of the linear pulse. For instance, with a 12-bit A/D converter, one could expect energy measurements from a few channels (≈10) to the maximum (4095) with an intrinsic resolution of 1 or 2 channels. Unfortunately, these characteristics do not satisfy the requirements of the energy measurement resolution for the silicon detectors. If we assume that the maximum energy is 4 GeV, a 12 bit ADC has a 1 MeV per channel resolution which is ten times the resolution required for low energy measurements. In fact, for the silicon detectors, an equivalent dynamic range of a 16-bit ADC is needed. Different techniques could be use to construct these ADCs. We experimentally explored three of them on prototype circuits [10]. The large number of channels imply that several charge integrators must be associated with a common converter through a linear multiplexer. We found that the settling time and the resolution of the available multiplexer circuits were not compatible with 16-bit ADCs. Another technique, largely used in the LEP OPAL detector, is described in Refs [11] and [12]. The outputs of 32 charge integrators are multiplexed and simultaneously fed into two chains of conversion: a conventional 12-bit ADC and a x8 amplifier followed by another 12-bit ADC. On our prototype we extended the 15-bit dynamic range to a 16-bit one with a x16 amplifier gain. As in the first method, the charge integration must be performed with a high resolution since the noise will also be amplified by a factor 16. In particular, the reference voltage of the integrator must be very stable. On our prototype, we found a resolution of 5 channels (fwhm) for the 16-bit range, a value compatible with the typical pedestal distribution (for a 15-bit range) presented in Ref. [12]. Better results have been obtained with a third method: a dual range conversion based on two charge integrations per channel. Each integrator is associated with a multiplexer followed by a 12-bit ADC. A x16 factor between the two ranges called "high gain" and "low gain" is simply obtained in varying the integrator capacitances by a factor 16. The main advantage over the previous technique is the lower quality required for the charge-integrating front end on the high gain range which is limited to an equivalent 12-bit dynamic range. Intrinsic resolutions of one channel have been obtain for the low gain (32 nC full scale range) as well as for the high gain (2 nC full scale range). For silicon detectors, this technique leads to energy measurements which are performed by two simultaneous 12-bit encoding: a few MeV to 4 GeV with 1 MeV per channel ("low gain") and a few hundred of keV to 250 MeV with 62 keV per channel ("high gain").

We have now to consider the hypotheses introduced, in particular about the possibility to obtain unipolar shaped pulses compatible with the resolution required. A 100 keV resolution seems to be so large that the choice of the shaping amplifier becomes trivial. Unfortunately, in the numerous works on the optimization of the signal to noise ratio, high dynamic range measurements are not considered. The discussions are generally limited to a careful evaluation of the detector and preamplifier noises and the effect of different pulse shaping on these noises [13, 14]. In a spectroscopy chain, the intrinsic noise of the filtering amplifier need not to be considered since the noise is dominated by that of the preamplifier. Conversely, in a high dynamic range chain, the preamplifier and amplifier must be set at such low gains that the energy resolution is dominated by the amplifier noise as shown in Ref. 15. The INDRA preamplifier provides 1 mV pulses on 50  $\Omega$  for 1 MeV deposited in the silicon detector. The intrinsic resolution is 14 keV at FWHM and corresponds to a noise of 6 µV (rms) at the amplifier input which has to be compared to the intrinsic amplifier noise. For the spectroscopy amplifier Enertec 7129, the manufacturer gives the equivalent input noise voltage :  $3 \mu V$  (rms) for a high gain and  $80 \mu V$  (rms) with the minimum gain limited to 3. With this amplifier, the resolution is 190 keV (fwhm) for the amplifier gain set to 3. Lower gains, necessary to process the 4 V pulse which corresponds to an energy deposit of 4 GeV in the detector, can only be obtained by the introduction of an attenuator between the preamplifier and the amplifier. At an equivalent gain of 1, the resolution will be 670 keV! Thus, the intrinsic noise of the amplifier must be reduced. A solution was found by a simplification of the filter-amplifier design with which very low noise integrated circuits can be used [16]. The negative amplifier pulse is

obtained through a bipolar shaper (1.5  $\mu$ s CR-RLC) followed by a clamp circuit. This simple design presents other advantages. A pole zero cancellation of the preamplifier decay time (220  $\mu$ s time constant) is not necessary since a rejection of  $\approx 10^4$  is provided by the bipolar shaping. Due to the zero crossing timing properties, the total pulse width ( $\approx 3.1~\mu$ s) is practically independent of the amplitude and the integration in the ADC can be performed on the totality of the pulse. This is important as the jitter in the time references (a few tens of ns) does not allow an integration limited to a well defined part of the analog pulse.

Another important feature in energy measurements of heavy ions with silicon detectors is that of the ballistic deficit due to detector collection times which can reach 1 µs [1,15]. In classical chains based on pulse-height ADCs, the ballistic deficit (BD) is the loss of the amplifier signal amplitude due to the interplay between the preamplifier rise time which follows the detector collection times and the amplifier time constants. The relative ballistic deficit (RBD<sub>amp</sub>) is the ratio of the amplitude loss for a finite collection time to the amplitude obtained for an instantaneous collection time. A relative ballistic deficit RBD<sub>cha</sub> can be similary defined for charge encoding as the ratio of the results obtained for finite collection times and an instantaneous one. The calculated RBD<sub>amp</sub> and RBD<sub>cha</sub> obtained by a simulation of the INDRA amplifier with the PSpice program [16] are presented in Table 3. The preamplifier pulse shape observed with silicon detectors [1] can be approximated by an exponential variation with respect to time:  $1 - \exp(-t/\theta)$ . A linear rise time is also considered for a comparaison to the RBD<sub>amp</sub> obtained with the standard CR-(RC)<sup>4</sup> shaping, a differentiator followed by four integration stages. These calculations show clearly that the ballistic deficit with the INDRA amplifier is more than five times smaller for charge encoding when compared to pulse height encoding. The low  $RBD_{cha}$  can be qualitatively understood as following : when the preamplifier rise time increases, the slight widening of the amplifier pulse width, due to the bipolar CR-RLC filtering, compensates the pulse height decrease. The calculations of the RBD<sub>amp</sub> for the CR-(RC)<sup>4</sup> amplifier were performed with the analytical formula of Loo, Goulding and Gao [17] which relies on the Baldinger and Franzen approach [18]. The relative ballistic deficit is expressed by  $RBD_{amp} = (1/24.N).(T/\tau)^2$  where N is the filter order, T the total input rise time considered as linear and  $\tau$  the filter time constant. We considered the fourth order filter (N=4) and two time constants,  $\tau = 1 \mu s$  and  $\tau = 0.25 \mu s$ . The first one is the standard value used in spectroscopy amplifier, while the second one corresponds to the same 1 µs peaking time of the INDRA amplifier. For the low value of  $\tau$ , we also performed a simulation as the analytical formula overestimates the RBD<sub>amp</sub> for the large rise times. The data show that a short time constant which could increase the dynamic range in the associated peak sensing ADC, is not compatible with the relatively large collection times of the silicon detectors. The most important result lies in the comparaison of the RBD<sub>cha</sub> obtained with the INDRA chain to the RBD<sub>amp</sub> of the standard CR-(RC)<sup>4</sup> amplifier set with  $\tau = 1 \mu s$ . Similar ballistic deficits are obtained, but the shape of the amplifier output pulses are very different. The CR-(RC)<sup>4</sup> amplifier provides pulses of 4  $\mu$ s peaking time and an overall pulse width which exceeds 15  $\mu$ s. The INDRA amplifier delivers pulses which have quasi constant and short widths : 3.1  $\mu$ s to 3.7  $\mu$ s for instantaneous and 1.2  $\mu$ s rise times respectively. This last feature is very important for charge encoding.

## 4.3. Consequences on the detector time references

In order to allow quite a large jitter in detector time references, a 330 ns delay line has been placed in the output circuit of the amplifier. Therefore, the most important timing feature is to fire a discriminator on a large dynamic range. If we consider a classical timing system composed of a fast amplifier and a constant fraction discriminator, the dynamic range is usually limited to few hundreds to one. The limitation comes from the discriminator for which the maximum input voltage, generally limited to 5 V, has to be compared to the minimum effective threshold. This depends upon factors such as the input signal rise time, the fraction and the delay line of the discriminator. In order to increase the dynamic range, a specific timing amplifier has been developed. The main features are : a fixed voltage gain of 8, a CR-RC filtering of 50 ns integration and 300 ns differentiation times and a limit of 5 V for the maximum output voltage [16]. If we consider the previous example of a silicon detector preamplifier which gives a signal of 1 mV/MeV at the amplifier input, the 5 V saturation corresponds to an energy of 625 MeV and, for higher energies, a signal with a flat top at 5 V is delivered. This saturation mode allows the discriminator to fire up to the maximum energy of 4 GeV while also preserving a low energy threshold. In fact, the situation is a little bit more complex if we consider the large rise time variations due to the detector. Experimental results with the 300  $\mu m$ thick silicon detectors have shown that a 100 % efficiency timing reference within 25 ns can be obtained above a threshold of a few MeV. In order to decrease this threshold one can consider the telescopic arrangement of the detectors. On forward angles (3°<0<45°), the 300 µm thick silicon detectors are followed by CsI(Tl) scintillators and a low energy loss in the first ones generally corresponds to a high energy loss in the second ones. By starting the charge integration gate of the ADC on a logical OR built on the two time references of the corresponding silicon and CsI(Tl) detectors, one obtains a very low threshold for the particles which cross the silicon detector. As protons can lose less than 1 MeV and as the electronics are set to collect up to 4 GeV, a dynamic range of more than 4000 to 1 is achieved. This method is also applied to the ionization chamber electronics for which the OR circuit is built on the time references provided by the ionization chamber discriminator and the four discriminators corresponding to the four pads of the associated silicon detector. At backwards angles (45°<θ<176°), where there is no silicon detector, the OR circuit makes use of the CsI(Tl) discriminators instead of those of the silicon detectors. As shown in Ref. [1], the energy threshold thus obtained is low enough to detect He nucleus with the ionization chambers. This corresponds to energy measurements as low as a 100 keV with a chain set up to a maximum energy of 200 MeV.

#### 4.4. Description of the electronic modules

Fig. 9 presents a general view of the electronics associated with the 96 ionization chambers and the 196 silicon detectors. The preamplifier signal is sent to slow and fast amplifiers which are housed in the same 8 input CAMAC module. The energy measurement is achieved by double charge encoding in ADCs implemented in a 32 input VXIbus module. The fast output of the amplifier is fed to a constant fraction discriminator (48 input VXIbus module) which delivers a time reference signal to the "Trigger and Time-marker" system. As explained previously, the individual opening of the charge integrators in the ADC modules is a logical combination (performed in the trigger system) of different detector time references. For the total number of 292 channels, we need 37 amplifier modules, 7 discriminator modules and 10 ADC modules. The VXIbus spare channels and another amplifier module are used in the electronic chains of the PIN diodes which control the stability of the laser system associated with the scintillators [1]. In order to control the stability of the electronics, 8 output CAMAC pulse generators were also developed. There is one generator output for each ionization chamber, calibration telescope and PIN diodes, i.e. 120 generator channels in total. Each 300 µm silicon wafer shares the same generator signal, thus leading to 48 generator channels. Therefore, the total number of CAMAC generator modules is 21. The electronics is very concentrated; only 3 CAMAC crates and one and a half VXIbus crates are necessary to house it. For the high voltage bias of the detectors, we use two SY403 crates of CAEN [6] equipped with the following boards : five negative 600~V boards for the 48 silicon wafers of  $300~\mu m$  thickness and the 5ionization chamber arrays, one positive 60 V board for the 8 silicon detectors of 80 µm thickness and one positive 600 V board for the 8 Si(Li) detectors. Fig. 9 shows, for one detector channel, the connections which are implemented on the module front pannels. All the other connections are made through the Slot 0 modules and the backplanes of the VXIbus crates.

Let us now present the four electronic modules which constitute the ionization chamber and silicon detector chain.

#### 4.4.1. The octal CAMAC pulse generator

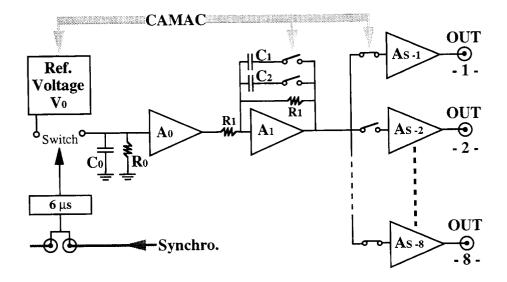

Fig. 10 shows a block diagram of the programmable pulse generator packaged in a #1 CAMAC module. The NIM input "Synchro." signal which triggers the generator is shaped to a width of 6  $\mu$ s and limited to a maximum frequency of 100 Hz. The DC reference voltage is set to a value  $V_0$  between - 5 V and + 5 V by a 16-bit DAC. When a synchronisation signal

occurs,  $V_0$  is switched during 6  $\mu$ s on the capacitance  $C_0$  = 820 pF and so a pulse of amplitude V<sub>0</sub> is generated. The rise time given by the switch-on resistance of the commutator coupled to  $C_0$  is around 50 ns. The decay time constant is  $\approx 1$  ms corresponding to the discharge of  $C_0$  in the resistor  $R_0 = 1.2 \text{ M}\Omega$ . When the analog switch goes off, a slight signal (< 10 mV) appears. The 6 µs duration was chosen as it is larger than the charge integration gate (4 µs) of the ADC and smaller than the dead time of the discriminator fixed at 8 µs. Under CAMAC control, the rise time can be increased to 200 ns or 800 ns by the selection of the capacitances C<sub>1</sub> or C<sub>2</sub> of the integrator A<sub>1</sub>. The pulse is distributed to the 8 outputs through amplifiers of gain 2 and buffered circuits. Eight relays allow a CAMAC software inhibit of each channel. The pulse amplitude is the same to within 1% on the 8 low impedance outputs and can be adjusted from - 10 V to + 10 V by steps of 0.3 mV. The integral non-linearity is better than 10 mV on 10 V. In the fabrication, particular care has been taken in the implementation of the capacitance and relay components. The fast, high linearity and high input FET impedance integrated circuits AD843 from Analog Devices are used for the DC reference voltage output and the amplifiers A<sub>0</sub> and A<sub>1</sub>. They are also used for the amplifier A<sub>S</sub>, in conjunction with the LH0043C buffered circuit.

#### 4.4.2. The octal CAMAC amplifier

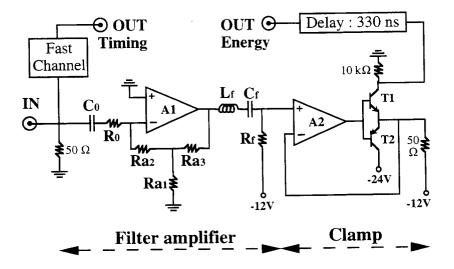

This #1 CAMAC module contains 8 channels of "fast" amplification for timing and 8 channels of "slow" amplification for energy measurements with charge ADCs. A detailed description with noise calculations is presented in Ref. [16] and we give here an overview of the main characteristics. Fig. 11 shows a block diagram of the energy channel filter-amplifier. The shaping network configuration, CR-RLC with time constants of 1.5 µs, is obtained through a passive input high pass filter ( $C_0 = 1.5 \text{ nF}$  and  $R_0 = 1 \text{k}\Omega$ ) followed by an  $R_f L_f C_f$ band pass filter ( $R_f = 287 \Omega$ ,  $L_f = 220 \mu H$ ,  $C_f = 10 nF$ ) which gives a bipolar pulse. This filtering configuration has the main advantage of requiring only one operational amplifier A<sub>1</sub> for which a very low voltage noise integrated circuit, such as the AD844 from Analog Devices, can be chosen. For a unitary gain, the filter attenuation is 0.45 and that corresponds to a maximum amplitude of ≈2.25 V for an input amplitude of 5 V. Under CAMAC control, the true voltage gain can take 8 different values from 0.45 to 4.7 by multiplicative steps of 1.4. This function is obtained by the commutation of relays associated with the resistors R<sub>a1</sub>, R<sub>a2</sub> and R<sub>a3</sub>. The amplifier A2 and the transistors T1 and T2 constitute a clamp circuit which limits the output pulse to the negative part and gives a current output signal. A 330 ns delay line is added at the output in order to encompass the totality of the linear pulse within the charge integration gate. The maximum output current is 60 mA and must not exceed 40 mA for a linear response. With the pulse shape provided by the amplifier (1.5 µs rise time and 3.1 µs total width), this corresponds to a maximum charge for a linear response of ≈80 nC. The silicon detector preamplifier provides pulses of 1mV/MeV amplitude on the 50  $\Omega$  amplifier input impedance. Under these conditions, the amplifier's intrinsic resolution is 70 keV (fwhm) at the 0.45 minimum gain with a 4  $\mu$ s charge encoding gate [16]. During the experiments and depending on the detectors, a resolution of 100 keV to 200 keV was obtained. The degradation of the resolution can be attributed to background noise of a very low level which cannot be seen on an oscilloscope as a 100 keV variation corresponds to a voltage step of less than 20  $\mu$ V during the 4  $\mu$ s opening of the ADC gate.

The main characteristics of the fast amplifier channel have been underlined in section 4.3 and are detailed in Ref. [16]. One of the difficulties in the electronic design came from the saturation mode chosen to ensure a timing with a high dynamic range. The solution was found in a fast biased line restorer which gives restitution times not exceeding 20 µs after saturation. Moreover, the polarity of the output signal is always negative whatever the polarity of the input signal is, and so multiple firing of the discriminator is avoided.

#### 4.4.3. The 48-channel VXIbus discriminator

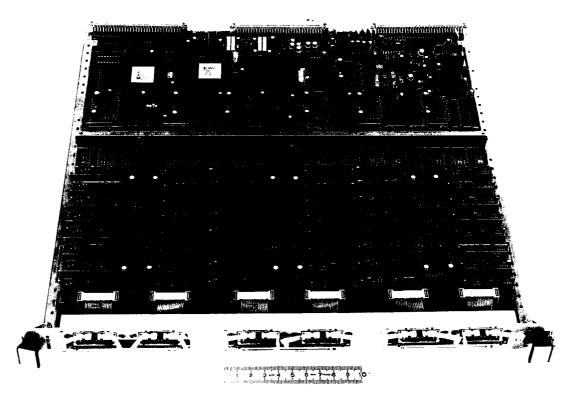

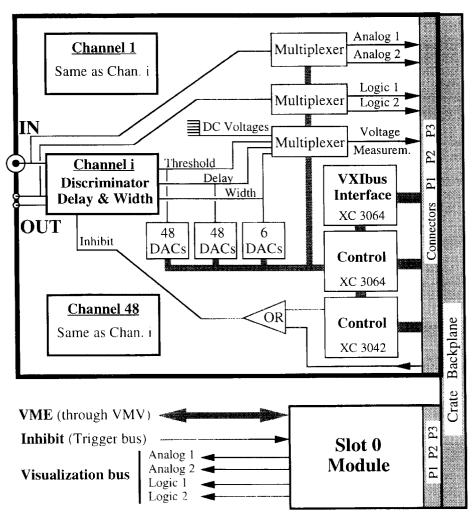

A photograph of this module is shown in Fig. 12. It represents a typical example of the VXIbus modules produced for the INDRA project. On the printed circuit motherboard two parts can be distinguished. On the forward part, the analog circuitry for each channel is implemented on a daughter board which is vertically plugged in the motherboard and can be easily changed. These daughter boards are multilayer PCB with SMT (Surface Mounted Technology) components on both sides. A high density analog circuit implementation is thus achieved with a very good separation between channels. A very low cross-talk can be preserved if attention is paid in the manufacture of the PC motherboard. As for example, in this 48-channel discriminator module, a 12 layer design of the PCB allows one to work with 40 ns rise time signals at 2mV thresholds without firing on a 5 V amplitude signal sent on an adjacent channel. The second part of the module, close to the three VXIbus connectors, is dedicated to the logic functions. In order to achieve a high density and versatility in the realisation of these functions, we used CMOS field-programmable gate arrays provided by the Xilinx Company [19] such as the XC 3042 and XC 3064 Logical Cell Arrays (LCA). The LCA structure consists of a perimeter of programmable Input Output Blocks (IOB), a core of configurable Logic Blocks (CLB) and their interconnection resources. Table 4 summarizes the main features of two LCA circuits. The CLB and IOB functions and their interconnections are controlled by a configuration program which is loaded automatically, on the power-up, from a serial PROM. In all the INDRA modules, the VXIbus interface is made by an XC 3064 which runs the same functions. A variable number of other LCAs (one XC3042 and one XC3064 in the discriminator module) are dedicated to the command of specific functions.

Fig. 13 shows a block diagram of the VXIbus discriminator module. Each of the 48 daughter boards contains a complete constant fraction discriminator (CFD) circuit and a delay and gate generator. The CFD shaping delay is 55 ns and an auto walk adjustement cancels the DC offsets and low frequency noise. An internal 8 µs dead time avoids multiple firing within the amplifier restitution times. The delay and the width of the output logic pulse are determined by two voltage comparators working on a linear ramp fired by the CFD. The following characteristics are remote controlled:

- thresholds, individually, from 0 to 255 mV in 1 mV steps

- output delays (non including the shaping times), individually, from 15 to 270 ns in 1 ns steps

- output widths, in groups of 8 channels, from 10 to 265 ns in 1 ns steps

- channel enabling and disabling, individually

On each channel, the analog input can be sent on any one of the 2 analog visualization lines through remote controlled analog multiplexers. Logic multiplexers ensure the same function for the logic output which can be sent on the 2 logic visualisation lines. This allows to check and compare the signals on an oscilloscope without dismounting the connector cables as discussed in section 3. All the analog values generated by the DACs, as well as the power voltages inside the module, can be controlled by the VME through the "voltage measurement" line and the associated ADC in the Slot 0 module.

#### 4.4.4. The 32-channel VXIbus charge ADC

Fig 14 presents a block diagram of this 32-channel module which is described in detail in Ref. [10]. As discussed in section 4.2, the analog to digital conversion is achieved by a double encoding: two charge integrators with gains in the ratio 1:16 and two multiplexed 12 bits convertors. The "low gain" data are obtained on the full dynamic range and the "high gain" ones are provided for low energies only (corresponding to 1/16 of the full dynamic range). The two charge integrators for each channel are implemented on one SMT daughter board. The pulse from the amplifier is split into two equal currents which are integrated over capacities of 8700 pF and 540 pF. These values correspond respectively to dynamic ranges of ≈32 nC for the low gain and ≈2 nC for the high gain. Due to the 0.5 pC resolution needed on the high gain, particular care has been taken in the design of the ground and DC references. For example, the voltage drift of the input virtual ground is held below a value equivalent to 0.1pC/°C by a low frequency closed loop circuit [10]. Each dual integrator is associated with a logic gate SMT daughter board which includes the individual firing and validation of channels required by the "asynchronous mode" of the INDRA working logic. On this logic daughter board, the individual gate (Ti), validation point (VPi) and reset (Ri) signals are generated. They can be adjusted by software commands through VXIbus and DACs. The standard settings used are 4 µs for T<sub>i</sub> and 1 µs for VP<sub>i</sub>. When an event is accepted by the trigger, only the channels having their VP<sub>i</sub> in the trigger "validation gate" are processed in the two parallel chains of AD conversion. Each chain comprises four parallel connected 8 input analog multiplexers (MX818 from Datel) and one analog to digital converter of a 12 bit resolution and a 350ns conversion time (ADC530 from Datel). The multiplexers have a 800 ns settling time down to 10-4. The ADC has an intrinsic 80% differential non linearity and is used in conjunction with a sliding scale circuit which reduces the differential linearity error to 1%. In order to avoid perturbations during the analog to digital conversion, the two conversions are made sequentially in the ADCs. This leads to a total conversion time of 2 µs for the two ranges of one input channel validated by the trigger through the "validation gate" and "start coding" signals. The data are stored in a R.A.M. memory working in the same way as a F.I.F.O: the 12-bit data and their corresponding 14-bit labels are read following the D32 mode of the VME until there is nothing more to be read in the module. The module logic is mainly constructed of LCA circuits which can be grouped into two functions: the VME interface (one XC3064 and one XC3042) and the control and sequence block (four XC3042s) which assumes the logic functions specifically related to this module. However, in order to avoid important time dispersions, the interface with the VXIbus timing signals, such as the "trigger bus", uses ECL technology. Some functions which are important in controlling the operation of the module are not presented in Fig 14. The pedestal of the channels can be adjusted by sending a DC current to the integrators. A local test mode makes use of a current generator which is fired when the "ADC test" signal is generated by the trigger. The following characteristics of the module are remote controlled:

- channel enabling and disabling, individually

- gate widths, from 1 µs to 11 µs, defined on 12 bits

- delays of the validation point, from 0.3 μs to 1.7 μs, defined on 12 bits

- pedestals, negative or positive, defined on 12 bits

- amplitudes of the test generators, defined on 12 bits

The main logical signals of each channel (integration gate, validation point, coding cycle...) can be sent on the two logic lines of the visualization bus. On the "gate control" line of this bus, one can see the validation point added to the validation gate sent by the trigger. As this corresponds to what occurs inside the module for each channel, this allows a precise adjustment of the coincidence functions. In fact, controls during the experiments show that the same value of the validation point delay can be used for the same family of detectors. This is due to the good reproductibility of the electronics and to the attention paid in the design of the timing circuits.

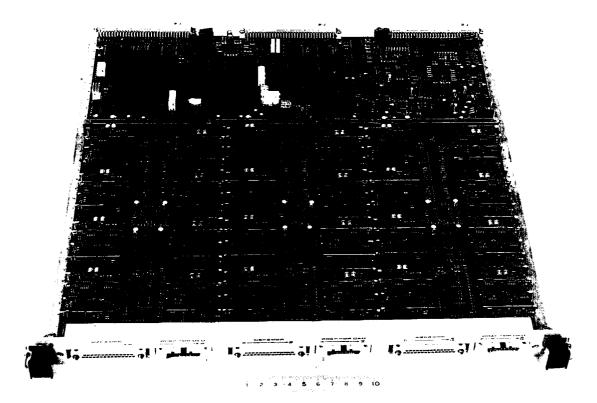

### 5. Compact modules for scintillator signal processing

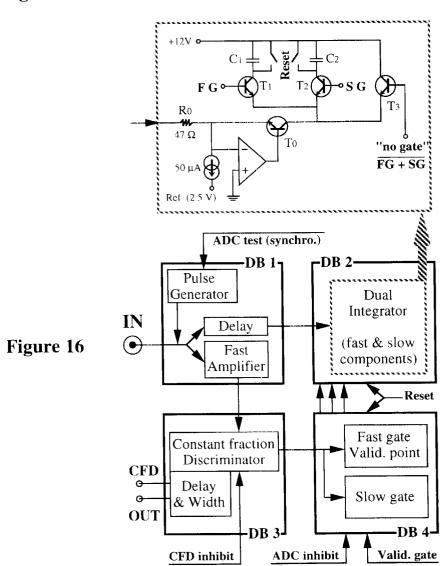

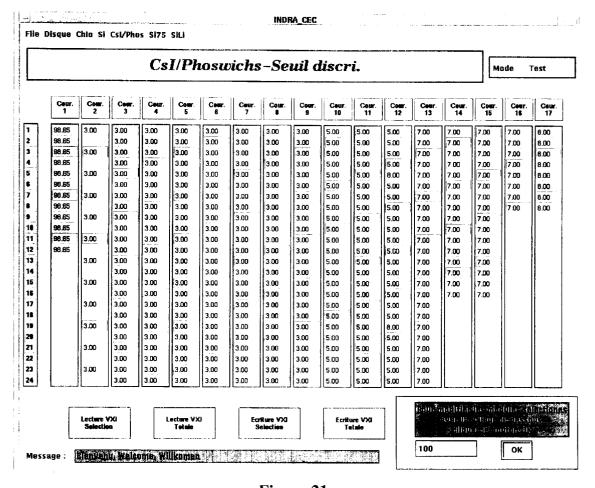

The 324 CsI(Tl) detectors constitute the outer layer of the INDRA detector and no fast or individual logic information from the other detectors has to be considered. It was therefore decided that a VXIbus module containing a maximum number of channels with all the electronic functions should be designed [20]. The connections are thus reduced to one analog input and one logic output per channel. The other connections are general ones (VME bus, trigger bus, visualization bus, etc) and come through the VXIbus backplane. Fig. 15 shows a photograph of the "CsI module" in which the complete electronics for 24 channels has been implemented. As for the other VXIbus modules, the logic functions are assumed by LCA circuits located close to the bus connectors. The analog circuitry for each channel is implemented on 4 daughter boards, each having a surface of 40 x 18 mm<sup>2</sup>. Such a high density is obtained mainly through the use of SMT components on both sides of the daughter boards. Fig. 16 presents for one channel, a block diagram of this circuitry. The CsI(Tl) signal processing needs the generation of a fast time reference which is sent to the trigger and two integrations, one in a fast gate (400 ns) and the other in a delayed slow gate (1.5 µs width and 1.6 µs delay). The photomultiplier signal arrives in the first daughter board (DB 1) where it is split into two channels. On one channel the signal is delayed by 55 ns and sent to the DB 2 daughter board which contains the two integrators. On the other channel, the signal is amplified by a factor of 3 and sent to the discriminator (DB 3 daughter board). The last daughter board (DB 4) contains the gate and delay generators which are fired by the discriminator and provide the fast and slow gates as well as the validation point of the channel triggering logic. The DB 1 daughter board also incorporates a test pulse generator which delivers particle-like signals to the input of the circuit. The inset in Fig. 16 shows a block diagram of the dual integrator. Due to the specifics of the fast and slow gates, which do not overlap, it was possible to simplify the electronic design. The common base input configuration (transistor T<sub>0</sub> and resistor R<sub>0</sub>) ensures a well defined input impedance which is necessary for matching with the 50  $\Omega$  impedance of the DB 1 delay line. Depending on the logic signals (FG fast gate, SG slow gate or "no gate"), the input current signal flows into only one of the transistors T<sub>1</sub>, T<sub>2</sub> or T<sub>3</sub>. Thereafter, the current is integrated in the C<sub>1</sub> capacitor during the fast gate and in the  $C_2$  capacitor during the slow gate, while it flows into the  $T_3$  transistor when the two gates are inactive. A pedestal current of 50 µA is added to the signal in the input circuit in order to obtain a good linearity for low amplitude signals. The analog to digital conversions of the 24 channels are performed by two multiplexed ADCs implemented on the motherboard, one for the fast signal component and the other for the slow one. As for the other detectors, the CsI module follows the asynchronous mode of triggering and only the channels having their validation point in coincidence with the validation gate are converted. In order to save place on the motherboard, small-size audio converters (Crystal CS5101) without sliding scale corrections are used. Only 12 bits of these 16-bit converters are kept and a satisfactory differential nonlinearity of 3% is thus obtained. The coding time takes about 10  $\mu$ s. The main electronic characteristics of this module are given in Ref. [20]. The following parameters are remote controlled:

- channel enabling and disabling, individually

- discriminator thresholds, individually, from 0 to 128 mV in 0.5 mV steps

- discriminator output delays (non including the shaping times), in groups of 8 channels, from 15 to 270 ns in 1 ns steps

- discriminator output widths, common, from 10 to 265 ns in 1 ns steps

- fast gate widths, common, from 50 ns to 1.1 μs, defined on 8 bits

- slow gates: the start and the stop of the gate signals are adjustable from 100 ns to

- 3.8  $\mu$ s, values are common to all channels and defined on 8 bits (the fast gate and the slow gate must not overlap)

- delays of the validation point, common, from 15 ns to 1.1 µs, defined on 8 bits

- test generator : channel enabling and disabling, individually

- amplitudes of the test generators, defined on 12 bits

As the module contains all the functions, it is important to be able to visualize the internal analog and logic signals. This is assumed by multiplexers which, under software control, send the signals to the crate backplane and then, through the Slot 0 module, to one of the five lines of the INDRA visualization bus. The signals which can be visualized are: the analog inputs, the fast integrator analog outputs, the discriminator outputs, the fast gates, the slow gates and the validation points added to the validation gate.

The CsI module was adapted to the characteristics of the CsI(Tl) and cannot be used for the NE102/NE115 phoswich detectors. The main reason is due to faster rise and decay times of the NE102 plastic scintillator, so that the integrations must be performed in a different way. In this case a short gate (30 ns) is required, during which the fast plastic light is measured, and a larger gate (800 ns) for the integration of the entire signal. The modifications needed led us to design a specific 16-channel module which is presented in Ref. [21]. In what concerns the parameter setup and the signal visualizations, this module works like the CsI module and the operating software system is quite similar for the two modules.

# 6. The trigger and time references for detectors

The trigger system selects the events, delivers the logic signals to the ADC modules and assumes the conversation with the data acquisition system. The large number of detectors rule out the possibility of event selections in which all the discriminators would be considered individually. The requirements of physics and the axial symmetry of INDRA led us to consider event selections based on ring dependent multiplicity levels. The ionization chamber logic signals are not actually used and thus INDRA can be considered as an arrangement of 336 detection cells within 17 rings [1]. Each

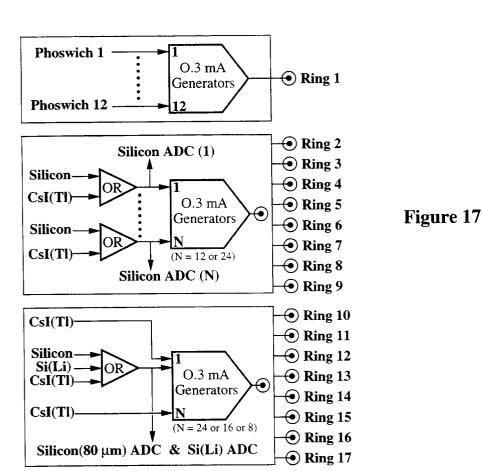

detection cell delivers a 0.3 mA signal per hit which are added to form 17 multiplicity current signals as shown in Fig. 17. For ring 1, it is simply a 12 input circuit receiving the discriminator signals associated with the 12 phoswich detectors. Due to the arrangement of detectors in telescopes, the situation is more complex for the other rings. In the forward rings (2 to 9), the introduction of OR circuits allows the creation of only one individual multiplicity current when the particle hits one or two detectors of the same Silicon-CsI(Tl) telescope. In the backward rings (10 to 17), only the CsI(Tl) detectors are considered, except for the cells (one per ring) which comprise the calibration telescopes for which OR circuits are also needed. In each ring, three identical multiplicity currents are available on three LEMO 00 connectors. These multiplicity and OR functions do not need software access and they are implemented in NIM modules which belong to a system called the "grouper". Not only does the grouper system reduces the number of signals to consider in the event selection, but it also assumes other logic functions. As shown in Fig. 17, the OR circuits deliver signals which fire the ADC gate of the silicon detectors (see section 4.3). Similarly OR functions ensure the firing of the ADC gates of the ionization chambers. For each ionization chamber cell, a logic OR is built between the ionization chamber discriminator and the discriminators of the detectors placed just behind, these are silicon detectors for rings 2 to 9 and CsI(Tl) for rings 10 to 17. The grouper also aids in reducing the number of channels which are controlled by the scalers. For example, one scaler is used for the four channels coming from the same silicon wafer. Therefore, only 16 VME scaler modules of 16 channels each are needed, whilst an individual control of each detector discriminator would have led to more than 40 scaler modules. The grouper is actually composed of 30 NIM modules of four different kinds. The functions performed can be varied or other functions added simply by changing the connections between the modules. For instance, multiplicity currents could be generated from the ionization chamber discriminators and used to select events for which a high energy deposit is required in the first layer of gaseous detectors.

In order to have the option of easily changing the trigger configuration, the event selection itself is performed in a VXIbus module called the "selector". Fig. 18 presents a simplified block diagram of the triggering inputs which can be selected under software commands. Two modes can be distinguished: the "physics mode" in which the system is triggered by one of the A to H inputs and the "test mode" which ensures the generation of the synchronization signals for the laser system associated with the scintillator detectors [1], the CAMAC pulse generators and the test generators of the ADC modules. During an experiment, the three synchronization signals which are denoted L.T. for the laser, C.T. for the CAMAC generators and A.T. for the ADC generators, are regularly generated by the selector following the time sharing of the beams delivered by GANIL, i.e., in a typical arrangement, during 10% of the time cycle when the beam is directed to another experimental area. Under software command, one can choose different test configurations which are automatically and successively selected at each beam cycle. Four test configurations are available: L.T. alone, C.T. alone, A.T. alone and L.T. and C.T. simultaneously. The frequencies (Fr) of the C.T. and A.T. signals can be selected from 40 Hz to ≈0.005 Hz on 14 values: Fr (in Hz) = 160 / 2<sup>n</sup> with n = 2 to

15. In order to obtain the best stability on the laser system, its working frequency must be fixed at 10 Hz [1] and instead of a frequency, one can select the L.T. signal every few cycles, more precisely L.T. is generated during only 1 per N cycles with N = 1 to 15. Thus, the "test mode" allows to check the stability of the electronics during the experiments with a selected number of events and without beam on the target.

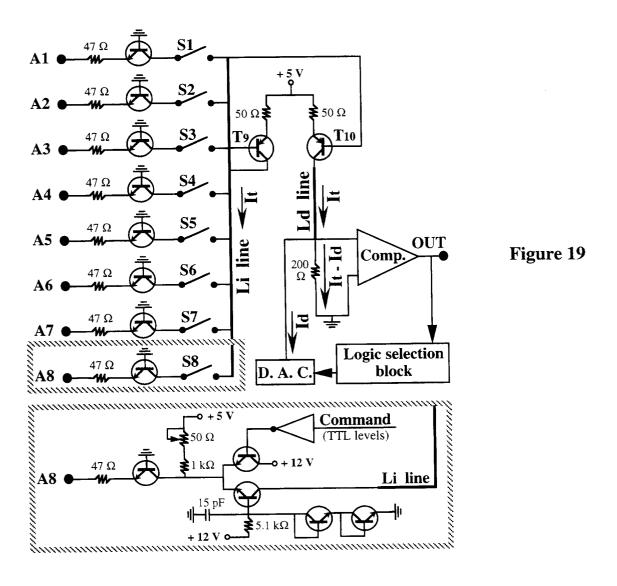

The triggering in the "physics mode" relies on the inputs A to H. The first three (A to C) run the same functions and perform a multiplicity selection of the events. Fig. 19 presents a block diagram of one of these inputs. In order to obtain fast responses, the multiplicity logic works in the current mode. The current signals of 0.3 mA per hit generated by the grouper NIM modules arrive on 8 inputs A1 to A8. The common base configuration of these inputs ensures a fast response together with a well-defined input impedance of 50  $\Omega$ . After crossing the analog switches S1 to S8, which allow to open or close the corresponding channels, the input currents are added on the common line Li. The current mirror, composed of transistors  $T_9$  and  $T_{10}$ , transfers this total pulse current (It) to the line Ld where it is added to a current Id generated by a DAC. The current Id determines the multiplicity threshold. When "It" is greater than "Id", the discriminator fires and a logical signal is created. Therefore, whatever the chosen multiplicity is, the discriminator always works at the same low level threshold. However, it is important to carefully adjust the current Id. This is carried out by the logic selection block in the following way. When a configuration and a multiplicity value are selected, the selector module generates a "discriminator inhibit" signal which disables all the detector discriminators. Then, through a counter progression and a comparison with the comparator circuit response, the logic block searches for the true zero level. The corresponding numerical value is added to the selected multiplicity value to create, via the DAC, the current Id. This method ensures that the multiplicity levels do not depend of the residual current which could vary with the number of NIM grouper modules considered. The standard INDRA triggering configuration makes use of the A selector input. The 17 individual multiplicity currents generated in the grouper modules are added to form 8 independent signals corresponding to rings 1 alone, 2 and 3, 4 and 5, 6 and 7, 8 and 9, 10 and 11, 12 and 13 and finally 14 to 17. The addition is simply performed by connecting on the same coaxial cable the corresponding grouper module outputs. We have checked that despite the relatively high number of primary logic channels, this multiplicity selection is very clean regardless of the detector hit. The two selector inputs, B and C, which are not actually used, will allow the incorporation of future triggering configurations such as, for example, multiplicity selections based on the ionization chamber discriminators. The D and E inputs are devoted to calibrations at backward angles. On the inputs  $D_1$  to  $D_8$ , it is possible to select the 8 calibration telescopes placed in the rings 10 to 17, whilst on the inputs E<sub>1</sub> to E<sub>8</sub>, all the detectors except the ionization chambers of the corresponding ring can be selected. The last three inputs can receive NIM logic signals and are thus open to future developments in which other detectors could be added to the INDRA ones. The logic signals  $(L_A \text{ to } L_H)$  corresponding to the eight inputs (A to H) are then individually allowed, or not, to trigger the system. A coincidence function can also be performed between these 8 inputs but for simplicity it has not been shown in Fig. 18. The first signal to arrive fires a coincidence gate of duration T during which the 8 input signals, delayed by a value T/2, are memorized. A set of configurations can be pre-selected amongst the 255 possibilities given by the 8 memorized signals. All the settings of the selector module are under software control. The triggering configurations are selected by switches and level multiplicity adjustments. The timing (delays, gate and signal widths) is performed through numerical counters working on the VXIbus 100 MHz clock. Therefore, all the time settings rely on binary registers and can be adjusted in steps of 10 ns.

The trigger must also ensure the conversation with the data acquisition system and the VXIbus encoding modules. These functions are implemented in a specific VXIbus module called the "correlator". The splitting into two modules preserves future evolutions of the data acquisition system in which only the correlator module would be changed.