## UNIVERSITÀ DEGLI STUDI DI PADOVA FACOLTÀ DI INGEGNERIA DELL'INFORMAZIONE Master Degree in Electronic Engineering

## Degradation and Dose-Rate Dependence in Decananometer MOSFETs Exposed to Ultra-High Levels of Total Ionizing Dose

Relatore: Prof. S. Gerardin Correlatore: Ing. G. Borghello PhD (CERN) Candidato: S. Costanzo Matr. 1152935

Anno Accademico 18/19Padova - 09/09/2019

### Degradation and Dose-Rate Dependence in Decananometer MOSFETs Exposed to Ultra-High Levels of Total Ionizing Dose

#### Sebastiano Costanzo

#### Abstract

The main experiment performed in this thesis is called "Low Dose-Rate Sensitivity", an analysis conducted on 65-nm technology node, intended to be implemented in most of the circuitry for CERN HL-LHC (High Luminosity - Large Hadron Collider) upgrade. The dose-rate (DR) is the dose absorbed per unit of time. If the DR is integrated over the irradiation time, then the Total Ionizing Dose (TID) deposited is obtained. The electronic components mostly affected by ionizing radiation, belonging to CMS and ATLAS detectors, are expected to reach TIDs up to  $1 \operatorname{Grad}(SiO_2)$ in 10 years. The relative dose-rate is therefore around  $0.01 \text{ Mrad}(\text{SiO}_2)/\text{h}$ . In the standard radiation assurance procedures, the devices are irradiated with dose-rates in the order of 10 Mrad(SiO<sub>2</sub>)/h, which are are 1000 times higher than the real faced one. BJT are strongly sensitive to the changes in the DR, in what is called Extremely Low Dose Rate Sensitivity (ELDRS). In practice, for the same level of TID, low dose-rate experiments provoke a much more severe degradation than a high DR irradiation. Up to now, MOSFETs are supposed to be insensitive to changes in the dose-rate. We demonstrated with a set of experiments that this dose-rate dependency is found also in the modern transistors. We obtained interesting results regarding the bias and temperature dependencies. In addiction, we used both an experimental and modeling approach, developing a coherent model that takes in account the differences between high and low dose-rates mechanisms. The results obtained will be the starting point for future studies and will be used for scientific publications.

We conducted experiments on the 28 nm technology node, which can represent a good alternative for CERN applications. In fact, as previously mentioned in other recent papers, this technology is particularly strong against ionizing dose. We irradiated up to 1 Grad(SiO<sub>2</sub>) a set of devices, and we encountered output current percentage degradation of nearly 10%. This is an encouraging result since, compared to previous technology nodes like the 130 nm or even the 65 nm, the same parameter was reduced by approximately 70%. As a notable draw-back, this new technology is strongly affected by drastic increases in the leakage current. These rises provoke enhancement in the static power dissipation of the circuits, which is intolerable in most of modern applications.

### Degradazione e Dipendenza dal Dose-Rate in MOSFET Decananometrici Esposti a Livelli Ultra-alti di Dose Totale Ionizzante

#### Sebastiano Costanzo

#### Abstract

L'esperimento principale di questa tesi si chiama "Low Dose-Rate Sensitivity", un'analisi condotta per il nodo tecnologico a 65 nm, destinato ad essere implementato nella maggior parte dei circuiti per l'aggiornamento del CERN HL-LHC (High Luminosity - Large Hadron Collider). Il dose-rate (DR) è la dose assorbita per unità di tempo. Se il DR viene integrato nel tempo di irraggiamento, si ottiene la dose ionizzante totale (TID) depositata. I componenti elettronici maggiormente colpiti da radiazioni ionizzanti, implementati nei rivelatori CMS e ATLAS, dovrebbero raggiungere livelli di TID fino a  $1 \text{Grad}(\text{SiO}_2)$  in 10 anni. Il relativo dose-rate è quindi circa  $0.01 \, \text{Mrad}(\text{SiO}_2)/\text{h}$ . Nelle procedure standard di irraggiamento, i dispositivi sono irradiati con dose-rates nell'ordine di 10  $Mrad(SiO_2)/h$ , che sono 1000 volte superiori a quello che realmente incontreranno. I BJT sono fortemente sensibili ai cambiamenti nel DR, in quella che viene chiamata Extremely Low Dose Rate Sensitivity (ELDRS). In pratica, a parità di TID, gli esperimenti a basso doserate provocano una degradazione molto più evidente rispetto ad un irraggiamento condotto a alto DR. Finora, i MOSFET vengono ritenuti essere insensibili ai cambiamenti del dose-rate. Abbiamo dimostrato con una serie di esperimenti che questa dipendenza rispetto al dose-rate si trova anche nei moderni transistor. Abbiamo ottenuto risultati interessanti per quanto riguarda le dipendenze da diverse tipologie di bias e temperatura. Inoltre, abbiamo usato sia un approccio sperimentale che modellistico, sviluppando un modello coerente che tiene conto delle differenze tra meccanismi ad alto e basso DR. I risultati ottenuti saranno il punto di partenza per studi futuri e saranno utilizzati per pubblicazioni scientifiche.

Abbiamo condotto esperimenti sul nodo tecnologico a 28 nm, che può rappresentare una buona alternativa per le applicazioni del CERN. Infatti, come già accennato in altre recenti pubblicazioni, questa tecnologia è particolarmente forte contro le dosi ionizzanti. Abbiamo irraggiato fino a 1  $\text{Grad}(\text{SiO}_2)$  una serie di dispositivi, e abbiamo incontrato una degradazione percentuale della corrente erogata di quasi il 10%. Questo è un risultato incoraggiante in quanto, rispetto ai precedenti nodi tecnologici come i 130 nm o addirittura i 65 nm, lo stesso parametro degrada di circa il 70%. Un notevole svantaggio per questa nuova tecnologia è un drastico aumento della corrente di leakage, ovvero la corrente erogata quando il dispositivo è spento. Tali aumenti provocano un incremento della potenza statica dissipata dei circuiti, che è intollerabile nella maggior parte delle applicazioni moderne.

# Contents

| 1        | Intr | oduction                                                | 11        |

|----------|------|---------------------------------------------------------|-----------|

| <b>2</b> | TID  | 0-Induced Degradation                                   | 15        |

|          | 2.1  | Interaction Between Radiation and Matter                | 15        |

|          | 2.2  | Holes Transport And Oxide-Traps Formation               | 16        |

|          |      | 2.2.1 Recombination Models                              | 18        |

|          |      | 2.2.2 Holes Transport in $SiO_2$                        | 18        |

|          |      | 2.2.3 Hole Trapping in $SiO_2$                          | 19        |

|          | 2.3  | $Si/SiO_2$ Interface Traps Depassivation                | 21        |

|          | 2.4  | ELDRS in Bipolar Devices                                | 22        |

|          |      | 2.4.1 Space Charge Models                               | 23        |

|          |      | 2.4.2 Bimolecular Process Models                        | 24        |

|          |      | 2.4.3 Binary Reaction Rate Model                        | 26        |

| 3        | CEI  | RN X-Ray Setup                                          | <b>27</b> |

|          | 3.1  | CERN X-Ray Setup                                        | 27        |

| 4        | TID  | Effect on Modern CMOS Technologies                      | 31        |

|          | 4.1  | STI-Related Effects                                     | 32        |

|          |      | 4.1.1 RINCE Effects                                     | 32        |

|          |      | 4.1.2 Radiation-Induced Drain to Source Leakage Current | 33        |

|          | 4.2  | Spacers-Related Effects                                 | 33        |

| <b>5</b> | Low  | Dose Rate Effect on 65 nm Node MOSFET                   | 37        |

|          | 5.1  | Introduction                                            | 37        |

|          | 5.2  | Experiment Details                                      | 38        |

|          | 5.3  | Results for the n-Channel MOSFETs                       | 39        |

|          |      | 5.3.1 Threshold Voltage                                 | 42        |

|          |      | 5.3.2 Transconductance                                  | 46        |

|          |      | 5.3.3 Sub-Threshold Swing                               | 49        |

|          |      | 5.3.4 Interchangeability of Source and Drain            | 50        |

|          |      | 5.3.5 Impact of Temperature                             | 53        |

|          |      | 5.3.6 Model for LDR effects in nMOS                     | 55        |

|          |      | 5.3.7 A dose-rate Sensitivity Coefficient               | 58        |

|          | 5.4  | Results for the p-Channel MOSFETs                       | 59        |

|          | 5.5  | Conclusions on the dose-rate effect                     | 65        |

| 6            | Nex | t Technology Step for CERN Applications: 28 nm | 67 |

|--------------|-----|------------------------------------------------|----|

|              | 6.1 | Experiment Details                             | 68 |

|              | 6.2 | Results: nMOS                                  | 70 |

|              |     | 6.2.1 Threshold Voltage                        | 70 |

|              |     | 6.2.2 Transconductance                         | 73 |

|              |     | 6.2.3 Drive Current                            | 73 |

|              |     | 6.2.4 Leakage Current                          | 77 |

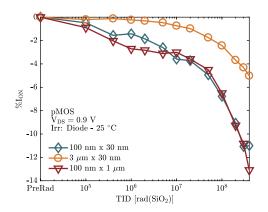

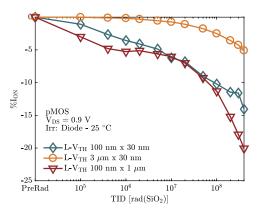

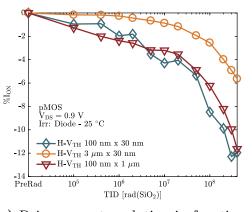

|              | 6.3 | Results: pMOS                                  | 80 |

|              |     | 6.3.1 Threshold Voltage                        | 80 |

|              |     | 6.3.2 Transconductance                         | 80 |

|              |     | 6.3.3 Drive Current                            | 80 |

|              | 6.4 | Final Comments on Manufacturer A 28 nm         | 86 |

|              | 6.5 | Manufacturer A vs Manufacturer B               | 86 |

| 7            | Con | aclusions                                      | 89 |

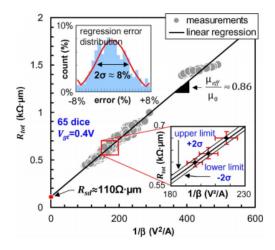

| $\mathbf{A}$ | Sou | rce-to-drain resistance extrapolation          | 97 |

# List of Figures

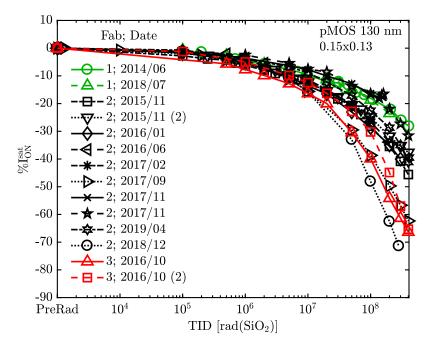

| 1.1          | Ion percentage degradation for pMOS with $W = 150 \text{ nm}$ and $L = 130 \text{ nm}$ produced in different fabs, irradiated up to $400 \text{Mrad}(\text{SiO}_2)$ in diode configuration and with $T = 25 ^{\circ}\text{C}$ .                                                                                                                                                    | 12              |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

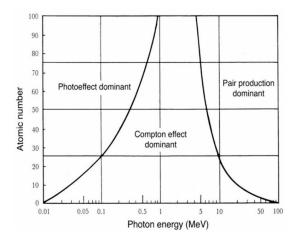

| 2.1          | Importance of three photon interactions as a function of atomic num-<br>ber and photon energy. Solid lines correspond to equal cross sections<br>for paighbouring effects. Taken from [15]                                                                                                                                                                                         | 16              |

| 0.0          | for neighbouring effects. Taken from [15]                                                                                                                                                                                                                                                                                                                                          |                 |

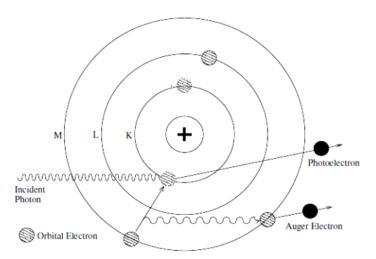

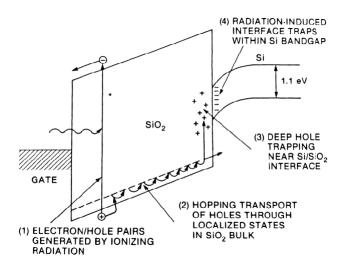

| $2.2 \\ 2.3$ | Description of photoelectric effect in a free atom. Taken from [16]<br>Schematic of ionizing radiation induced effects in MOS structures,                                                                                                                                                                                                                                          | 16              |

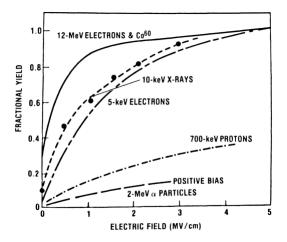

| 2.4          | with positive gate applied to n-channel MOSFET. Taken from [9] Fractional yield as a function of applied electric field for several dif-                                                                                                                                                                                                                                           | 17              |

| 2.5          | ferent kinds of radiation incident particles on $SiO_2$ . Taken from [9]<br>Representative image of a polaron. The conduction of one electron in<br>a ionic crystal repels the negative ions and attracts the positive ones.                                                                                                                                                       | 18              |

|              | Taken from $[27]$                                                                                                                                                                                                                                                                                                                                                                  | 19              |

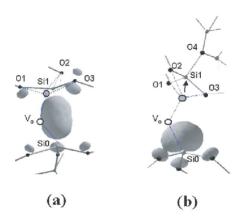

| 2.6          | Schematic of the $E'_{\delta}$ center (a) and $E'_{\gamma}$ center (b), taken from [31].<br>IEEE © 2002                                                                                                                                                                                                                                                                            | 20              |

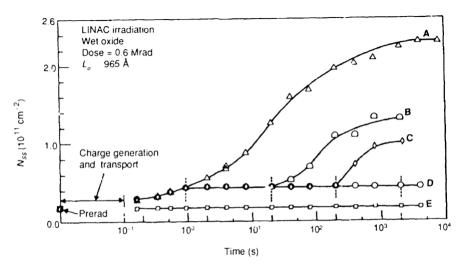

| 2.7          | Field experiments showing importance of positive field during second stage of Winkour model [34]                                                                                                                                                                                                                                                                                   | 22              |

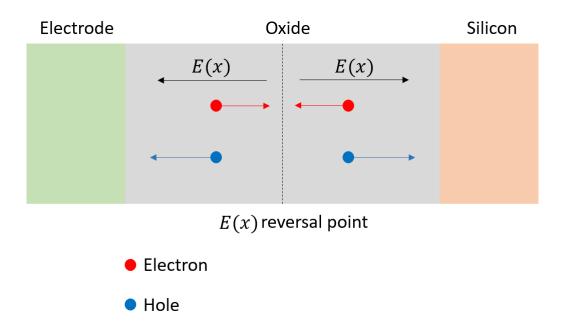

| 2.8          | At high dose-rates holes and protons generated close to the gate side drift toward the gate, rather than toward the $Si/SiO_2$ interface, due to local reverse in the electric field caused by the space charge. After [46] IEEE ( $\hat{C}$ ) 1998                                                                                                                                | 24              |

| 2.9          | A uniform space charge distribution causes local inversion of the elec-<br>tric field in the bulk the oxide. As it is possible to notice, holes gen-<br>erated close to the Si interface drift toward the silicon bulk and can<br>create interface traps. From the other side, holes generated closer to<br>the gate electrode tend to drift toward it and get collected, reducing |                 |

|              | the net charge in the oxide. After [50] IEEE $\bigcirc$ 1998 $\ldots$ .                                                                                                                                                                                                                                                                                                            | 25              |

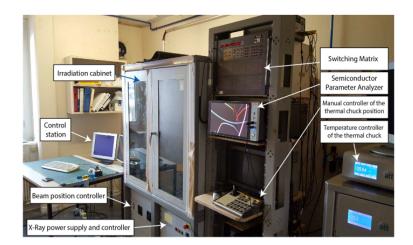

| 3.1          | CERN EP-ESE group X-Ray irradiation facility, with all the related instruments used to perform accurate irradiation experiments                                                                                                                                                                                                                                                    | 27              |

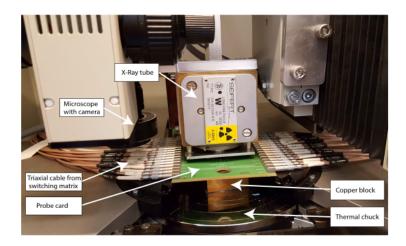

| 3.2          | Inner view of the CERN X-Ray cabinet.                                                                                                                                                                                                                                                                                                                                              | $\frac{21}{28}$ |

| 3.3          | Probe card needles contacting a generic array.                                                                                                                                                                                                                                                                                                                                     | 28              |

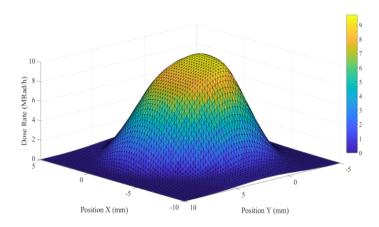

| 3.4          | 3D calibration of the beam used to carry out the experiments                                                                                                                                                                                                                                                                                                                       | 29              |

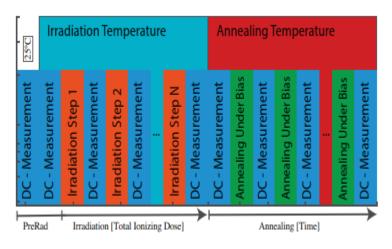

| 3.5          | Typical qualification procedure used during TID experiments. Tran-<br>sistors are irradiated to a specific TID level and the irradiation is<br>stopped to measure the device characteristic. Once the irradiation<br>reaches the wanted TID, the annealing part starts.                                                                                                            | 30              |

|              | reactions the warroad rip, the annealing part boards                                                                                                                                                                                                                                                                                                                               | 50              |

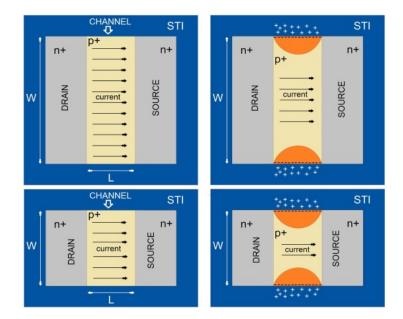

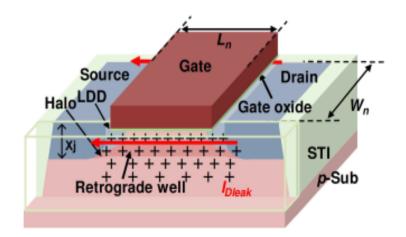

| 4.1  | Graphical representation of the radiation induced narrow channel effect (RINCE). In narrow transistors the electric field generated by the charge trapped in the STI influences a larger percentage of the channel, limiting the current flowing between source and drain. Courtesy of G. Borghello, taken from [67]                                                     | 32              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 4.2  | Parasitic path between source and drain, due to charge trapped in the STI. After [69] IEEE © 2017                                                                                                                                                                                                                                                                        | 33              |

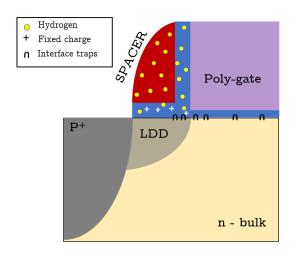

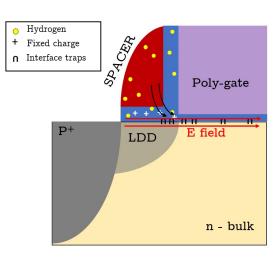

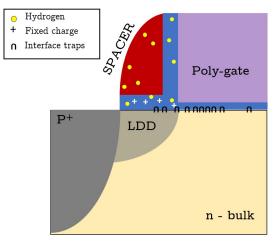

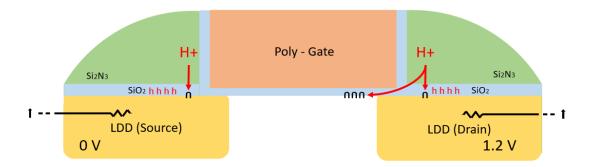

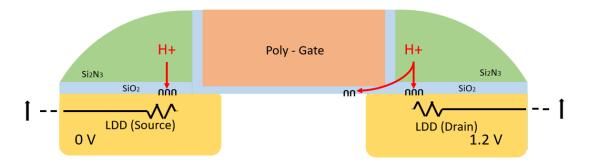

| 4.3  | Multiple stage ionizing process in the spacer oxides. The hydrogen ions are reported in yellow, while the positive fixed charge is represented by a + sign. The interface traps are represented with a $\cap$ .                                                                                                                                                          | 35              |

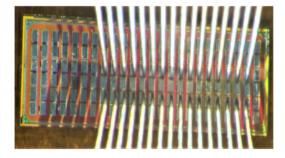

| 5.1  | Test structure used to carry out LDR experiment. The 6 separated gates, 3 for nMOS and 3 for pMOS, allow the possibility to apply different biases to different transistors.                                                                                                                                                                                             | 38              |

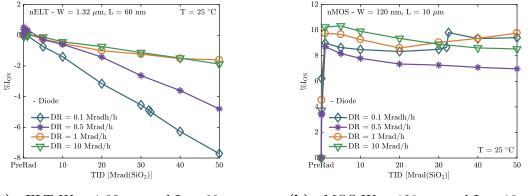

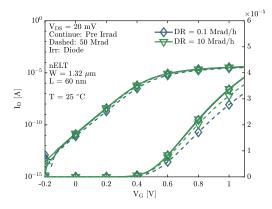

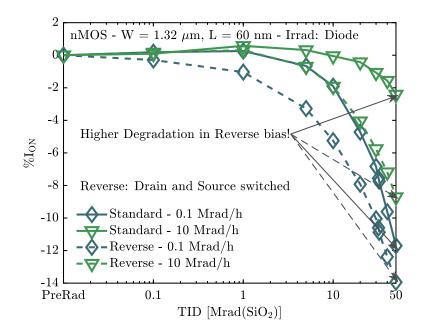

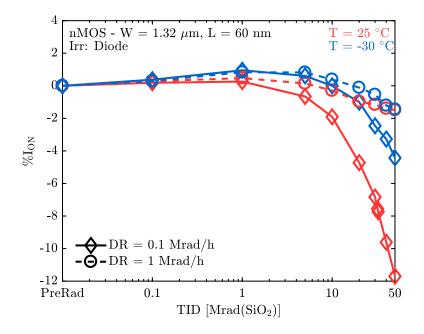

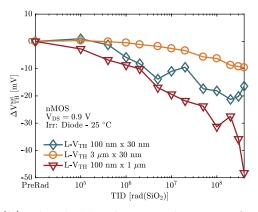

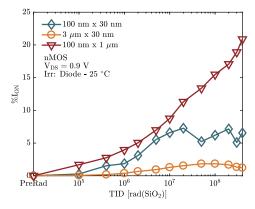

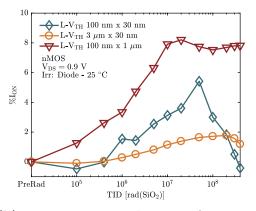

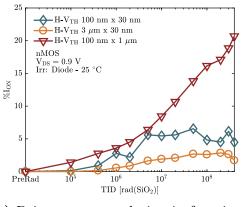

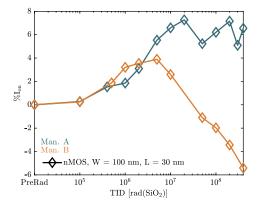

| 5.2  | $I_{ON}$ percentage variations in function of TID for the n-MOS transis-<br>tors, irradiated with different DRs up to $50Mrad(SiO_2)$ . The devices<br>are biased in diode configuration.                                                                                                                                                                                | 40              |

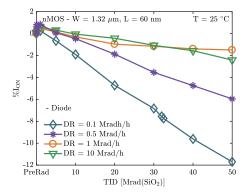

| 5.3  | $I_{ON}$ percentage variations in function of TID for n-MOS transistors irradiated at 10 and 0.1 Mrad(SiO <sub>2</sub> )/h with different bias configurations.                                                                                                                                                                                                           | 40              |

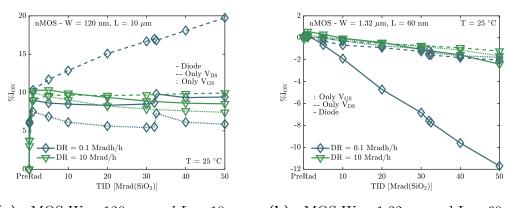

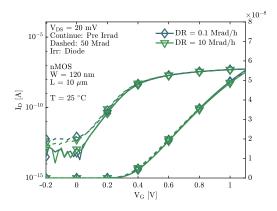

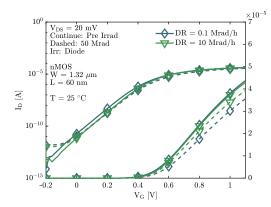

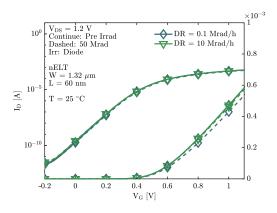

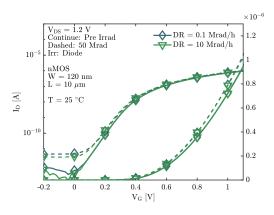

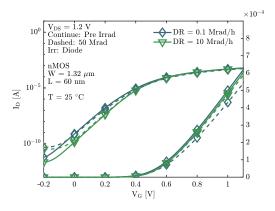

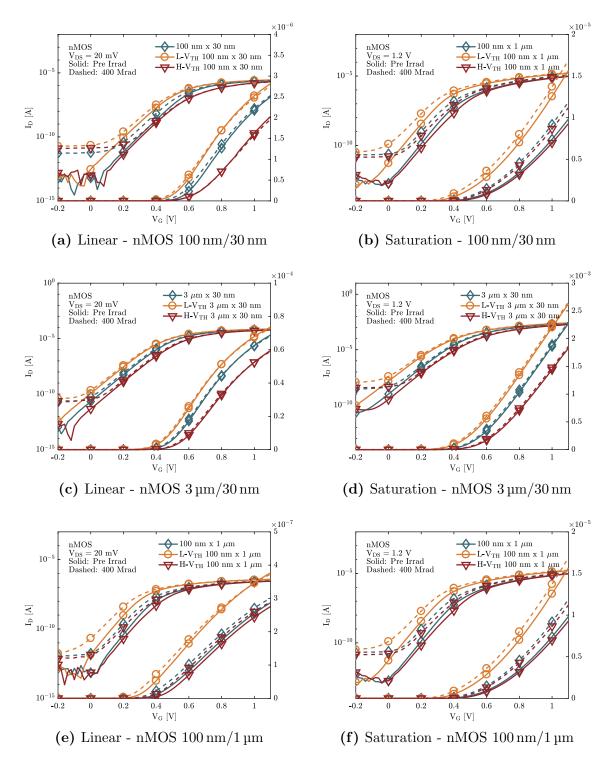

| 5.4  | $I_D$ vs $V_{GS}$ curves in linear (left) and saturation (right) region for all nMOS devices, irradiated with the highest and lowest dose-rates (10 Mrad and 0.1 Mrad(SiO <sub>2</sub> )/h) in diode configuration.                                                                                                                                                      | $l(SiO_2)/h$ 41 |

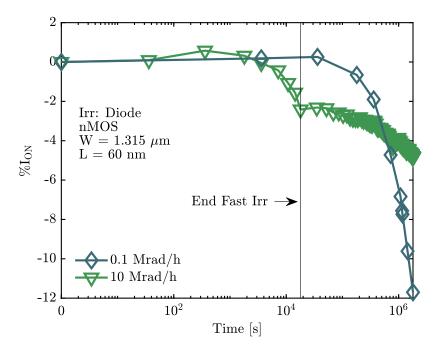

| 5.5  | Drive current degradation for the $W = 1.32 \mu\text{m}$ and $L = 60 \text{nm}$ devices, irradiated with the highest (green) and lowest DRs (blue). The time is reported on the horizontal scale. After the end of 10 Mrad(SiO <sub>2</sub> )/H irradiation, the MOSFET underwent a long room temperature annealing, which allowed us to exclude times dependent effects |                 |

| 5.6  | High temperature annealing for the devices reported in Figure 5.5.<br>The high temperature does not produces any substantial evolution in the I <sub>ON</sub> .                                                                                                                                                                                                          |                 |

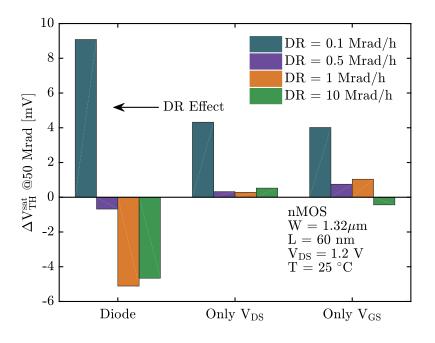

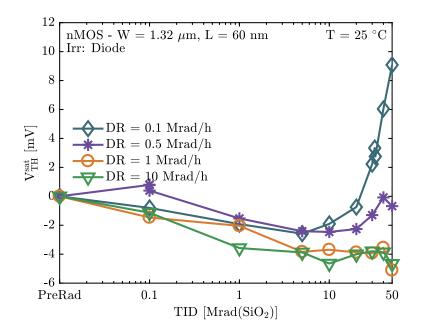

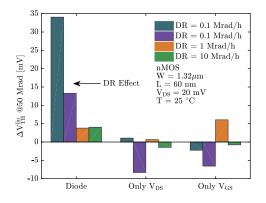

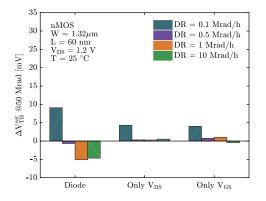

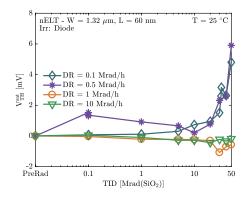

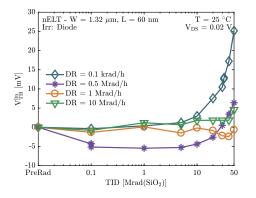

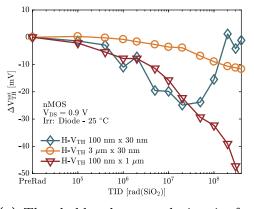

| 5.7  | Threshold voltage variations for the $W = 1.32 \mu\text{m}$ and $L = 60 \text{nm}$<br>n-MOSFET, irradiated up to 50 Mrad(SiO <sub>2</sub> )                                                                                                                                                                                                                              | 43              |

| 5.8  | Threshold Voltage analysis for the $W = 1.32 \mu\text{m}$ and $L = 60 \text{nm}$ n-MOSFET. The Figure contains only the devices irradiated with a diode bias, for the all DRs.                                                                                                                                                                                           | 44              |

| 5.9  | Comparison of the evolution of the threshold voltages for the $W = 1.32 \mu m$ and $L = 60 nm$ structure, both in linear (5.9a) and in pinch-<br>off condition (5.9b).                                                                                                                                                                                                   | 45              |

| 5.10 |                                                                                                                                                                                                                                                                                                                                                                          | 45              |

| 5.11 | Comparison of the evolution of the threshold voltages for the $W = 1.32 \mu m$ and $L = 60 nm$ ELT structure, both in linear (5.11a) and in pinch-off condition (5.11b)                                                                                                                                                                                                  | 46              |

|      | • • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                  |                 |

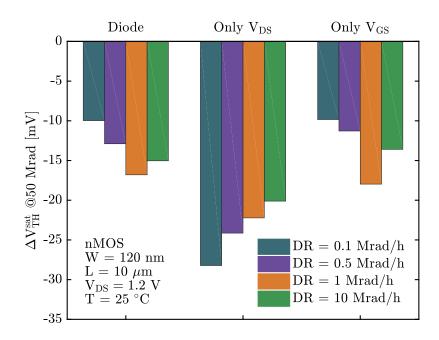

| 5.12  | Threshold Voltage variations for the $W = 120 \text{ nm}$ and $L = 10 \text{ µm}$<br>n-MOSFET, irradiated up to 50 Mrad(SiO <sub>2</sub> ). All the bias and DR |    |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|       | are considered in the Figure                                                                                                                                    | 47 |

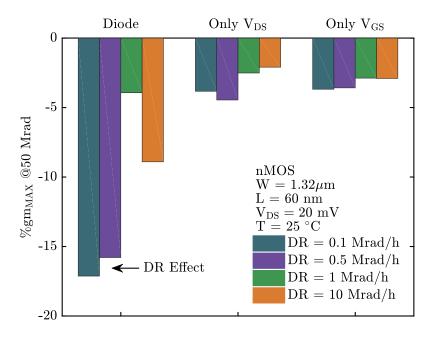

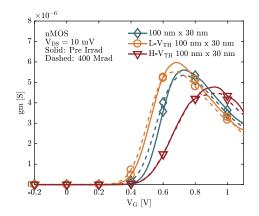

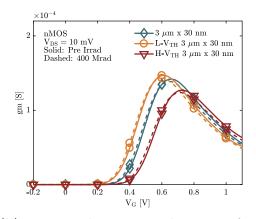

| 5 1 2 | Transconductance variation at 50 Mrad(SiO <sub>2</sub> ) for the $W = 1.32 \mu m$                                                                               | 41 |

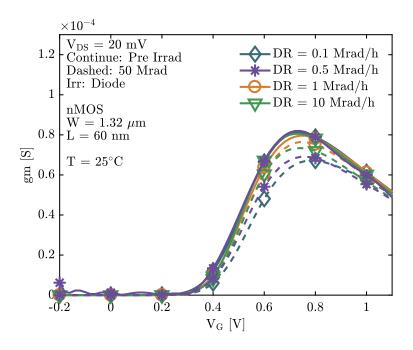

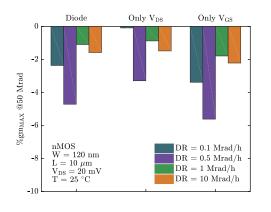

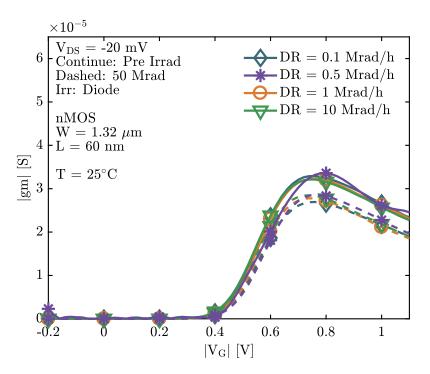

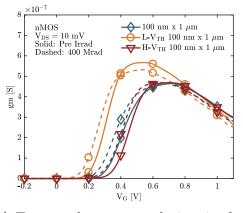

| 0.10  | and $L = 60 \text{ nm nMOS}$ .                                                                                                                                  | 47 |

| 511   |                                                                                                                                                                 | 41 |

| 0.14  | Transconductance comparison pre-post irradiation for the $W = 1.32 \mu m$<br>and $L = 60 nm nMOS$ .                                                             | 10 |

| F 1 F |                                                                                                                                                                 | 48 |

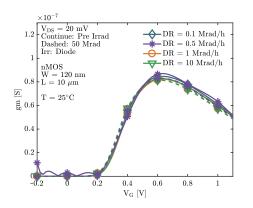

| 5.15  | Complete analysis for the transconductance for the narrow and long                                                                                              | 10 |

|       | device. No DR effect observed                                                                                                                                   | 49 |

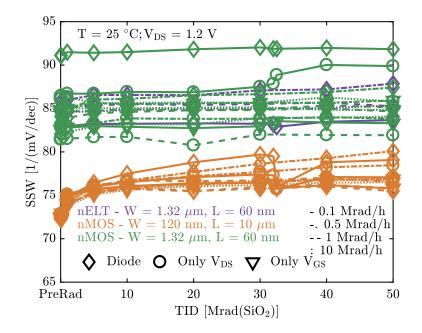

| 5.16  | Sub-threshold swing evolution in function of TID for all the n-channel                                                                                          | -  |

|       | devices analyzed.                                                                                                                                               | 50 |

| 5.17  | Standard (blue) and reverse (green) drive current degradation com-                                                                                              |    |

|       | parison for n-Channel MOSFET with W = $1.32 \mu\text{m}$ and L = $60 \text{nm}$ .                                                                               | 51 |

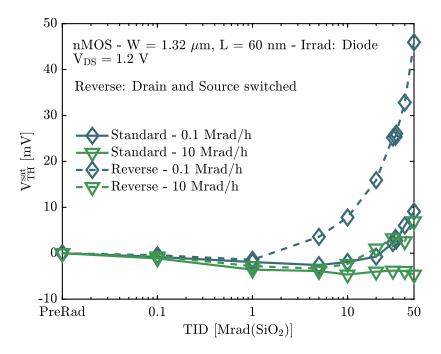

| 5.18  | Threshold voltage evolution during irradiation for the $W = 1.32 \mu m$                                                                                         |    |

|       | and $L = 60 \text{ nm n-MOS}$ device. Presence of the reverse configuration                                                                                     |    |

|       | analysis (dashed lines) for highest DR (green) and lowest one (blue).                                                                                           | 52 |

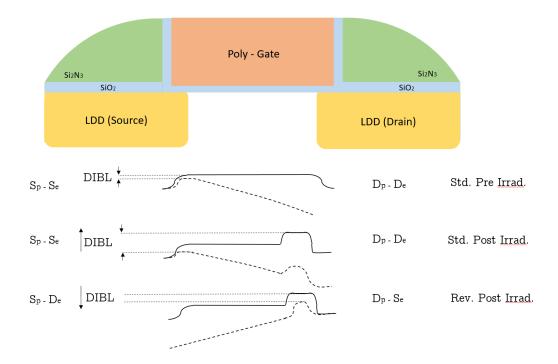

| 5.19  | Representation of a generic MOSFET structure. The drain and source                                                                                              |    |

|       | region and the relative LDD extensions are represented in yellow. The                                                                                           |    |

|       | $SiO_2$ oxide part, used to create the gate and the inner part of spacers                                                                                       |    |

|       | oxide is light-blue colored, while the outer part of the spacer, formed                                                                                         |    |

|       | of $Si_2N_3$ is shown in green. The poly-gate region is represented in                                                                                          |    |

|       | orange                                                                                                                                                          | 54 |

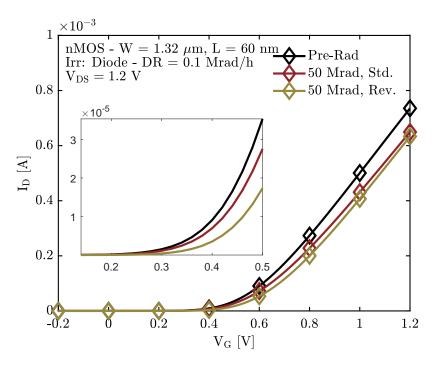

| 5.20  | $I_D$ vs $V_{GS}$ curves for the W = 1.32 µm and L = 60 nm device, plotted                                                                                      |    |

|       | for $V_{DS} = 1.2V$ . The solid black line correspond to the pre-irradiation                                                                                    |    |

|       | case, the red one to the post-irradiation standard configuration and                                                                                            |    |

|       | the yellow one to the post-irradiation reverse configuration. A visible                                                                                         |    |

|       | $V_{TH}^{sat}$ shift is present, while the slope of the curve is almost constant                                                                                | 54 |

| 5.21  | Drive current variation for n-MOS device with $W = 1.32 \mu m$ and                                                                                              |    |

|       | L = 60  nm in function of the TID both for high temperature and low                                                                                             |    |

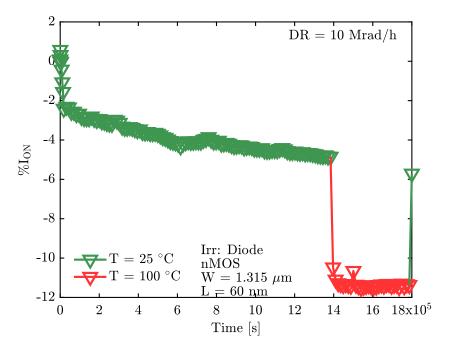

|       | temperature experiments                                                                                                                                         | 55 |

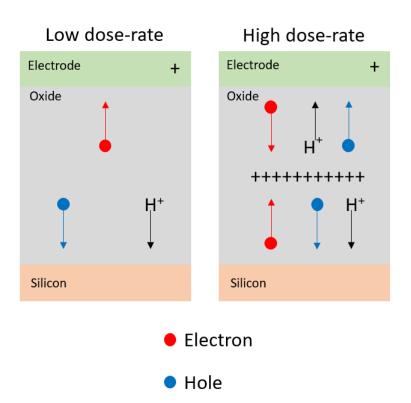

| 5.22  | Proposed model for the High-DR experiments                                                                                                                      | 56 |

| 5.23  | Proposed model for the Low-DR experiments                                                                                                                       | 57 |

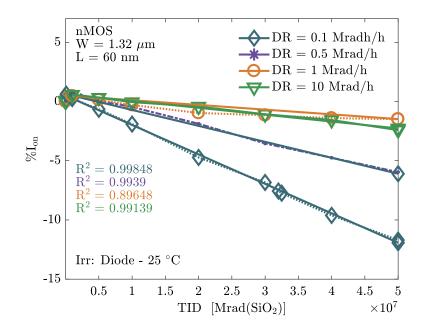

| 5.24  | Fitting of the drive current variation curves                                                                                                                   | 58 |

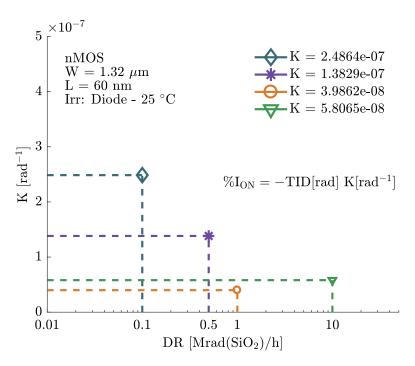

| 5.25  | K coefficient for the different DRs analyzed.                                                                                                                   | 59 |

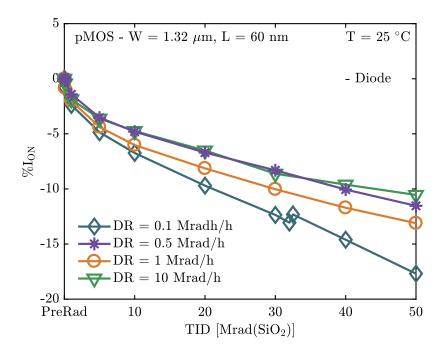

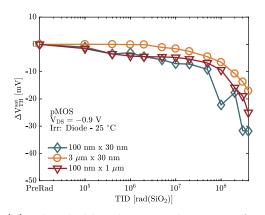

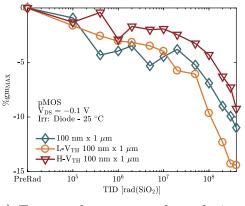

| 5.26  | $I_{ON}$ percentage variations in function of TID for the W = $1.32 \mu m$                                                                                      |    |

|       | and $L = 60 \text{ nm pMOS}$ transistor, irradiated with different DRs up                                                                                       |    |

|       | to 50 $Mrad(SiO_2)$ . The devices are biased in diode configuration.                                                                                            |    |

|       | A lower DR provokes a higher degradation for these type of struc-                                                                                               |    |

|       | ture, as previously encountered also in the W = $1.32\mu\text{m}$ and L =                                                                                       |    |

|       | $60 \operatorname{nmnMOS}(5.2c)  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $                                                      | 60 |

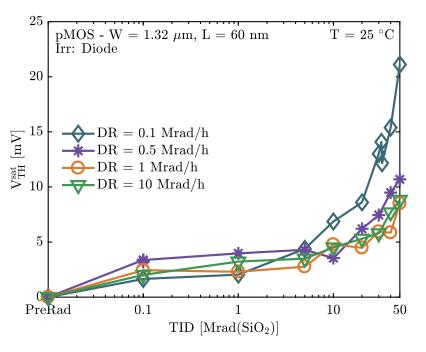

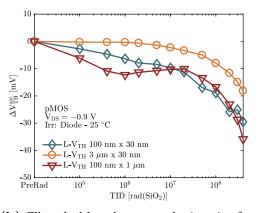

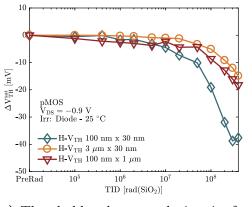

| 5.27  | Threshold voltage variations for the W = $1.32 \mu m$ and L = $60 nm$                                                                                           |    |

|       | p-MOSFET                                                                                                                                                        | 61 |

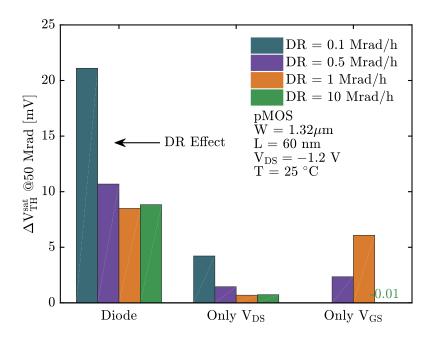

| 5.28  | Threshold voltage shifts after 50 $Mrad(SiO_2)$ for the W = 1.32 µm                                                                                             |    |

|       | and $L = 60 \text{ nm p-MOSFET}$                                                                                                                                | 62 |

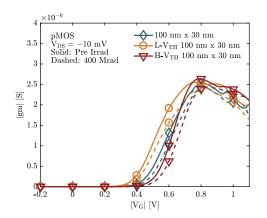

| 5.29  | Pre- and post-irradiation transconductance curves for the $W = 1.32 \mu m$                                                                                      |    |

|       | and $L = 60 \text{ nm p-MOSFET}$                                                                                                                                | 62 |

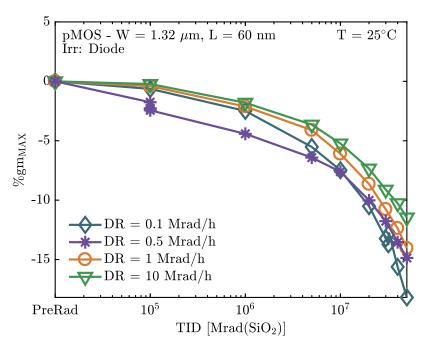

| 5.30  | Evolution of the peak of the transconductance for the $W = 1.32 \mu m$                                                                                          |    |

|       | and $L = 60 \text{ nm p-MOSFET}$                                                                                                                                | 63 |

|       |                                                                                                                                                                 |    |

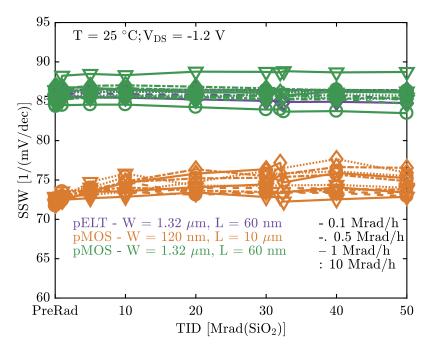

| 5.31 | Evolution of the Sub-Threshold Swing for the $W = 1.32 \mu m$ and $L = 60 nm p$ -MOSFET                                                                                                                                                                                                       | 63       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

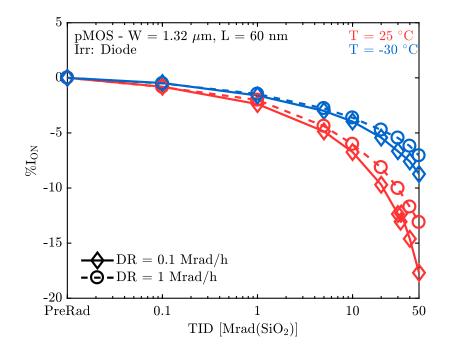

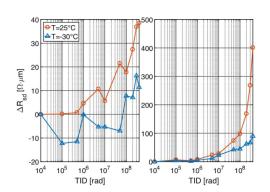

| 5.32 | Temperature effect on the drive current for the $W = 1.32 \mu m$ and $L = 60 nm p$ -MOSFET                                                                                                                                                                                                    | 64       |

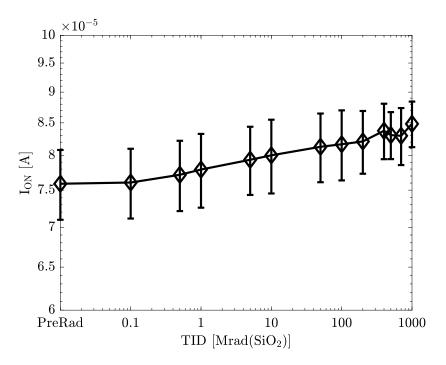

| 6.1  | Ion variations for nMOS with $W = 80$ nm and $L = 30$ nm, irradiated<br>up to 1 Grad. Sigma variation bars are considered                                                                                                                                                                     | 68       |

| 6.2  | $\sigma$ over mean ratio, for the drive current, in function of TID                                                                                                                                                                                                                           | 69       |

| 6.3  | Array of the chip analysed in the 28 nm technology node studies. Note the presence of different $V_{TH}$ flavours                                                                                                                                                                             | 69       |

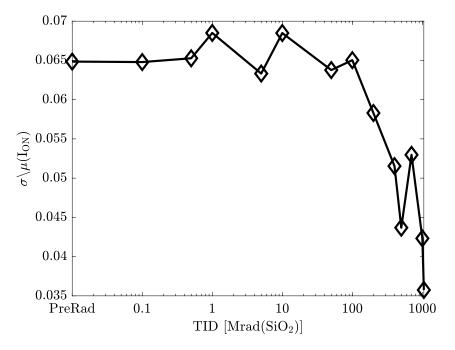

| 6.4  | $I_D$ vs $V_{GS}$ curves for all nMOS devices, irradiated up to 400 Mrad<br>in diode configuration. In the left column the curves for linear zone<br>are presented, while the right contains the curves for the saturation<br>zone. The MOS are divided in group in function of their W and L | 81       |

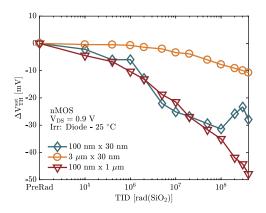

| 6.5  | dimensions                                                                                                                                                                                                                                                                                    | 71<br>72 |

| 6.6  | Comparison between pre- and post-irradiation transconductance curves<br>for the devices analysed. The structure are divided into group in func-<br>tion of their channel length and width.                                                                                                    | 74       |

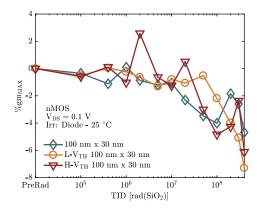

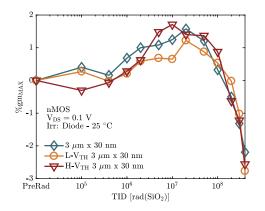

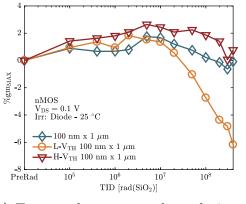

| 6.7  | Evolution of the peak of the transconductance for the analysed de-<br>vices. The structure are divided into group in function of their chan-<br>nel length and width.                                                                                                                         | 75       |

| 6.8  | Drive current evolution in function of TID for the analysed devices.<br>The structure are divided into group in function of their threshold<br>voltage flavour.                                                                                                                               | 76       |

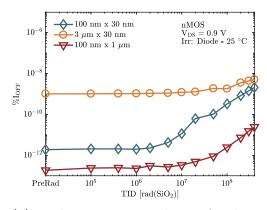

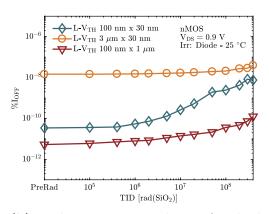

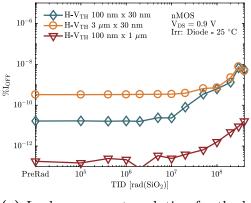

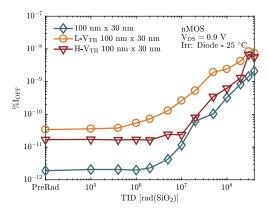

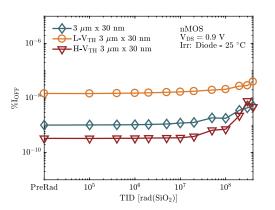

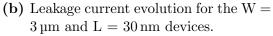

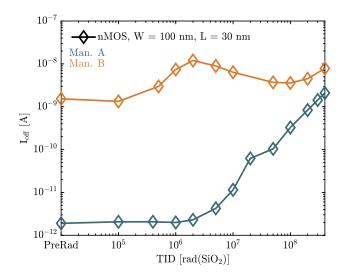

| 6.9  | Leakage current evolution in function of TID for the analysed devices.<br>The structure are divided into group in function of their threshold<br>voltage flavour.                                                                                                                             | 78       |

| 6.10 | Leakage current evolution in function of TID for the analysed devices.<br>The structure are divided into group in function of their W and L                                                                                                                                                   | 79       |

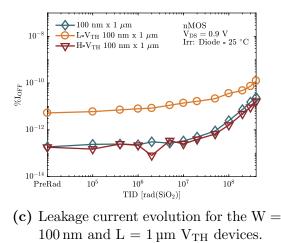

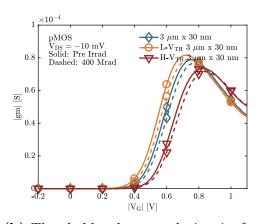

| 6.11 | $I_D$ vs $V_{GS}$ curves for all pMOS devices, irradiated up to 400 Mrad<br>in diode configuration. In the left column the curves for linear zone<br>are presented, while the right contains the curves for the saturation<br>zone. The MOS are divided in group in function of their W and L |          |

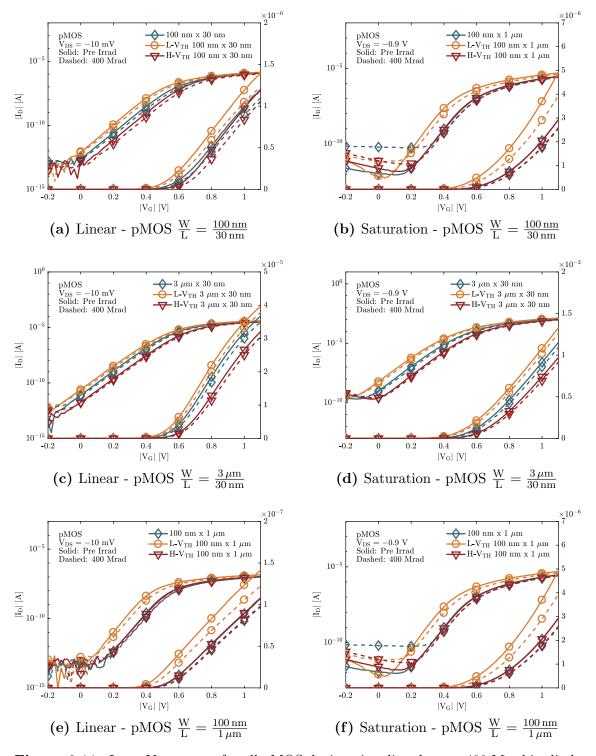

| 6.12 | dimensions                                                                                                                                                                                                                                                                                    | 81       |

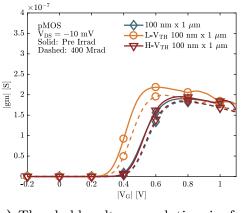

| 6.13 | ysed for the 28 nm technology node                                                                                                                                                                                                                                                            | 82       |

|      | for the devices analysed. The structure are divided into group in func-<br>tion of their threshold voltage flavour                                                                                                                                                                            | 83       |

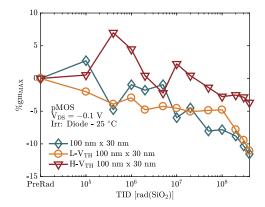

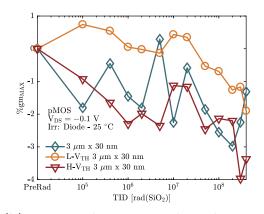

| 6.14 | Evolution of the peak of the transconductance for the analysed de-<br>vices. The structure are divided into group in function of their thresh-<br>old voltage flavour.                                                                                                                        | 84       |

| 6.15 | Drive current evolution in function of TID for the analysed devices.<br>The structure are divided into group in function of their threshold                                                                                                                                                   |          |

|      | voltage flavour.                                                                                                                                                                                                                                                                              | 85       |

| 6.16 | Drive current comparison between two different manufacturers mini-      |    |

|------|-------------------------------------------------------------------------|----|

|      | mum size, standard flavour nMOs (left) and pMOS (right). Devices        |    |

|      | producded by Man. A are represented in blue, while the one created      |    |

|      | by Man. B are shown in orange                                           | 87 |

| 6.17 | Leakage current evolution comparison between minimum size, stan-        |    |

|      | dard flavour nMOSETs produced by Man. A (blue) and Man. B               |    |

|      | (orange)                                                                | 87 |

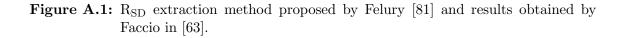

| A.1  | $R_{SD}$ extraction method proposed by Felury [81] and results obtained |    |

|      | by Faccio in [63]                                                       | 98 |

## Chapter 1

## Introduction

The discovery of the radiation is dated back at the end of 17<sup>th</sup> century, thanks to the studies of Wilhelm Röntgen, Marie Curie and Henri Becquerel. Citing the first of the three listed researchers: "It seemed at first a new kind of invisible light. It was clearly something new, something unrecorded..." [1]. At first radiation sources were not considered an health hazard. Also Marie Curie died of problems mainly related to exposure to ionizing sources [2]. One of the classical example that highlighted the dangers of ionizing radiation was the case of the "Radium Girls", workers whose job was painting watch dials with radium. After five of the workers sued the company (United States Radium), and also thanks to the ensuing publicity, the health risks of radiation exposure were brought to the public attention [3]. Radiation compromises also electronics standard operation. Generally, radiation-related degradation in electronics occurs due to the interaction between an impinging particle (proton, photon, heavy ion, electron, pion etc.) and the materials building the device. The type of damages are directly related to the energy of the particle and their relative ionizing proprieties. Radiation damages can be divided into two categories: nonionizing (e.g. displacement damages) or ionizing. This thesis focus only on ionizing radiation effects on MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor). The integrated energy deposited by ionizing particles, called Total Ionizing Dose (TID), causes a cumulative build-up of charge in the oxides present in MOS transistors. The effect of multiple interactions can cause substantial changes in the nominal behaviour of the devices, therefore electronics intended to operate in harsh environments, i.e. with high radiation level, must be developed taking into account the effects of their interaction with particles. A well-known example of radioactive environment is the outer space. Satellites are in fact exposed to solar winds, cosmic rays and they orbits through Van Allen belts [4]. An updated analysis of radiation induced degradation on satellites in space application can be found in [5]. Among all the environments in which radiation is a threat to electronics systems, the Large Hadron Collider (LHC) running at CERN [6] and especially its future upgrade, High-Luminosity LHC (HL-LHC), that will be operative from 2025 [7], is the harshest environment in term of ionizing dose. In detail, CERN main experiments, such as ATLAS (A Toroidal LHC Apparatus), CMS (Compact Muon Solenoid), LHCb (Large Hadron Collider beauty) and ALICE (A Large Ion Collider Experiments) have to withstand the highest radiation level. In perspective, while TID usually reaches fractions of  $Mrad(SiO_2)$  in space applications [8], the electronics designed for the inner layer of the particle detectors for the future HL-LHC experiments will

Figure 1.1: Ion percentage degradation for pMOS with W = 150 nm and L = 130 nm produced in different fabs, irradiated up to 400Mrad(SiO<sub>2</sub>) in diode configuration and with T = 25 °C.

experience up to one thousand  $Mrad(SiO_2)$  [7]. The electronic components currently installed in LHC apparatus are mostly based on 250 nm technology node, while for the future upgrade the technologies will be scaled down to 130 and 65 nm transistors. In addition to the greater computational power allowed by the use of shorter channel devices, technology scaling naturally improves radiation-hardness [9]. As a draw back, the aggressive scaling enhances the device-to-device variability, which is nowadays one of the crucial issues encountered in radiation qualification processes [10]. As reported in [11], in each generation of devices, fewer atoms are employed in the fabrication processes, hence the presence of the absence of a single dopant atom can produce significant changes in the threshold voltage of a MOSFET. This high sensitivity requires extremely precise production processes to obtain robust chips. Radiation assurance analysis is becoming economically heavier at each technology scaling down step [12], since multiple tests are often required in order to obtain enough statistic to margin the variability unavoidably present in the fabrication processes. In addition, TID enhance the mentioned variability, as deeply analysed in [11]. As an example, Figure 1.1 reports the drive current percentage degradation variability in function of TID for nominal identical devices of the 130 nm technology node, produced by the same manufacturer but in three different fabrication plants, namely Fab. 1 (green), 2 (black) and 3 (red). Figure 1.1 is a clear representation of lot-to-lot variability. All the devices were irradiated up to  $400 \text{Mrad}(\text{SiO}_2)$ , at room temperature and in diode configuration. The percentage variations at the end of the exposure are almost unpredictable, with some devices decreasing their output current of -70% and other just of -30%, even if produced in the same fab but in different years. The wide range in which the results fall shows how difficult it is to extrapolate models that can faithfully reproduce the behavior of devices exposed to different TID. Consequently, the objective of the radiation assurance experiments

is the identification of mechanisms which greatly contribute to the degradation of the devices, independently from the inevitably present variability. Our job consists in determine which effects are enhanced or mitigated by particular auxiliary oxide structures, commonly implemented in modern MOSFETs. Our goal is hence to provide qualitative knowledge on the mechanisms that most occur during the ionization of oxides, rather than solid predictions on the final percentage of degradation of the device taken individually and irradiated at any level of TID.

This thesis presents two nuclei: The Dose-Rate (DR) effect on 65 nm technology node and a comparison between two 28 nm structures, produced by two different manufacturers. The analysis of true DR effects is based on extremely time-requiring tests and lasted in total multiple months. The DR effect on this technology has been already briefly reported in [13]. We gained further knowledge on this phenomenon, and we will propose some comments on the causes of the enhanced damage at low dose-rates. We were able to perform multiple tests, in which we covered different combinations of biases, temperatures and, of course, of DRs. In addition, the devices irradiated at the highest DR have been kept under bias for additional time, in order to exclude the possibility that the enhanced degradation at low dose-rates was caused by time-related effects.

We performed studies on the 28 nm technology node exposed to ultra-high level of ionizing dose. While several parameters of this devices are only slightly affected by TID even at ultra-high doses, the leakage current rises of multiple orders of magnitude. This technology can represent anyway a valuable choice for future electronic developments at CERN. We analysed the main parameter variations as a function of TID for two different manufacturer technologies, named Manufacturer A and B.

The thesis outline is here reported.

Chapter 2, *TID-Induced Traps Formation* will briefly discuss the basic mechanisms occurring in MOSFET oxides exposed to irradiation, focusing on charge generation, transport and relative trap centers formation. It is the preliminary chapter that allows to understand the mechanisms presented in Chapter 4, 5 and 6.

Chapter 3, *CERN X-Ray Setup* will describe the experimental setup used to obtain all the results reported in this thesis.

Chapter 4, *TID Effect On Modern CMOS Technologies* briefly summarize the most common degradation phenomena occurring in STI and spacer oxides for modern technologies, exposed to ultra-high levels of radiation. We will mostly focus on Radiation-Induced Narrow Channel Effect (RINCE) and Radiation-Induced Short Channel Effect (RISCE), and on the radiation induced drain to source leakage current path creation.

Chapter 5, Low Dose Rate Effect on 65 nm node MOSFET will contain a detailed analysis on the true DR effect measured in the 65 nm technology node.

Chapter 6, A Prospective To CERN Future: 28 nm will show the robustness of the 28 nm technology node exposed to ultra high level of radiation. We will compare two different manufacturers, proposing comments on the cause of the differences in the parameters evolution in function of TID.

## Chapter 2

## **TID-Induced Degradation**

This chapter summarizes the processes that provoke the formation of trap centers, located either in the bulk of oxides or at the  $Si/SiO_2$  interface. In Section 2.1 is reported a brief introduction on the photoelectric effect, that will allow us to understand under which conditions ionization in the oxides can occur. Section 2.2 covers the typical transport mechanisms of holes through the oxides that culminate with charge built-up in the depth of the oxides (generation of the oxide traps) and in the insulator region closer to the silicon bulk (creation of border traps). Section 2.3 analyzes the complex processes that result in the creation of  $Si/SiO_2$  interface traps. We will compare the main differences between these traps and the one located in oxide bulk.

### 2.1 Interaction Between Radiation and Matter

The interaction of radiation with solid-state devices depends mainly on the mass, charge state and kinetic energy of the impinging particles, and on the atomic mass, atomic number and density of the target [14]. This thesis will refer to the interaction between photons and typical materials that compose the classical MOSFET, silicon (Si) and silicon dioxide  $(SiO_2)$ . There are three type of interactions between photons and targets material, each of them produces energetic free electrons [14]. In the experiments conducted, the photoelectric effect is mainly involved in the interactions, as it possible to see from Figure 2.1, taken from [15]. In fact, the atomic numbers of silicon and oxygen are respectively  $Z_{Si} = 14$  and  $Z_O = 8$ , while the X-Ray source spectrum used in the experiments conducted has a maximum of intensity at the energy of 10 keV. In the photoelectric effect, if the incoming photon has an energy high enough to excite an electron of the target atom from the K-shell, i.e. the closest shell to the nucleus, to an higher energy level, for example the L-shell (which is further from the nucleus, compared to the K-shell), then around 80 % of the collisions happen with K-shell electrons [14]. Photoelectric effect takes place predominantly in the K atomic shell and therefore it is possible to use its cross-section to estimate the total photoelectric cross-section [16]. The emitted electron completely absorbs the photon, and can be called photoelectron, even if its charge and mass are the same as a classical electron. Another electron, coming from the L-shell will fulfill the vacancy left from the photoelectron. Since the electron loses energy, there will be an emission of a low-energy photon (or so called fluorescence photon), with an energetic level equal to the difference of the energy level of the two shell, i.e. L and

Figure 2.1: Importance of three photon interactions as a function of atomic number and photon energy. Solid lines correspond to equal cross sections for neighbouring effects. Taken from [15]

Figure 2.2: Description of photoelectric effect in a free atom. Taken from [16]

K. It is possible that the fluorescence photon emitted ejects another orbital electron, called Auger electron. Figure 2.2 provides a good representation of the photoelectric effect. Therefore, from the interaction of a photon with the insulating layer of the device, there are the generations of an electron-hole (e-h) pair, a low-energy photon and sometimes an Auger electron. The freed photoelectron, passing through the material, deposit a portion of its energy as ionization and the remaining as atomic lattice displacement. For charged particles, such as electrons, most of the loss of energy occurs via ionization, even if a small amount of atomic displacement can happen, while for neutrons is the opposite [14].

### 2.2 Holes Transport And Oxide-Traps Formation

Ionizing radiation effects are a concern for both the silicon bulk and the oxides of a MOSFET structure. When the ionization processes take place within a part of the MOS capable of retaining charges, such as layers of silicon dioxide, the effect of multiple interactions can accumulate over time. Figure 2.3 shows the ionizing

Figure 2.3: Schematic of ionizing radiation induced effects in MOS structures, with positive gate applied to n-channel MOSFET. Taken from [9]

radiation effects in a generic nMOSFET structure, with a positive bias applied to the gate. Multiple stages succeed one another in the process of charge trapping in the oxide layers. In particular:

- 1. Creation of electron-hole pairs by ionizing radiation

- 2. Transport of holes via polaron hopping through localized states in  $SiO_2$  bulk

- 3. Deep hole trapping in the  $SiO_2$  bulk, and near  $Si/SiO_2$  interface

- 4. Interface traps depassivation at the  $Si/SiO_2$  interface

As previously reported in Section 2.1, the photoelectron can, along his trace, ionize other particles, generating e-h pairs. Previous studies proved that the average energy required to create an e-h pair in SiO<sub>2</sub> is approximately  $17 \pm 1$  eV [17, 18]. As soon as the e-h pairs are generated, some of them are instantaneously recombined. The electrons are much more mobile than the holes, and can be considered negligible in the charge trapping processes in MOS oxides. From [19], the mobility of electrons in  $SiO_2$  varies from ~ 20 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, measured at room temperature (T = 300 K), to  $\sim 40 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  measured at low temperature (T < 150 K). For high electric field in the oxides,  $E_{OX} \ge 5 \times 10^5 \text{ V cm}^{-1}$ , the electron drift velocity saturates quite sharply to  $1 \pm 0.1 \times 10^7$  cm s<sup>-1</sup> [20]. Nowadays, since the thickness of the gate oxide is in the order of some nm, the magnitude of electric filed crossing them is high enough to give at the electrons the possibility to reach the saturation drift velocity. This implies a transit time of the electrons in the oxides of the order of some picoseconds. Essentially, for all the temperatures and the electric fields, electrons transport can be considered instantaneous. Regarding holes, their mobility is dependent on both temperature and electric field, and in any case is smaller than the same parameters of the electrons. In fact, their mobility varies from  $10^{-4} \div 10^{-11}$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> [21]. Therefore holes are considered immobile compared to electrons, and for this reason the radiation induced effects are attributed exclusively at their presence.

Figure 2.4: Fractional yield as a function of applied electric field for several different kinds of radiation incident particles on SiO<sub>2</sub>. Taken from [9].

#### 2.2.1 Recombination Models

Two basic models have been developed in order to describe the recombination of e-h pairs from an analytic point of view: the columnar model and the geminate model [9]. They differ between each other for two parameters:  $r_t$ , which is the initial distance of separation between the hole and its corresponding electron, and  $\lambda$ , which is the mean distance of separation between different e-h pairs. The columnar model proposes that the generation of e-h pairs happens in very narrow and dense columns, therefore for this model  $r_t \ll \lambda$ . On the other side, the geminate model proposes that one hole and its electron are further from each other than from another e-h pair couple, imposing  $r_t \gg \lambda$ . In most of the real cases, the actual recombination process is a combination of the two models.

#### 2.2.2 Holes Transport in SiO<sub>2</sub>

The charge generation and recombination processes are completed in few picoseconds after the impact of the radiation source. After this small amount of time, the fraction of holes that escaped recombination process – which is called charge yield - undergoes transport in  $SiO_2$ , optionally promoted by the presence of an electric field. As it is possible to notice from Figure 2.4, for a 10 keV X-Ray source the fractional yield rate approaches the unity for high electric fields, therefore it is clear that holes transport is a big concern for ionizing radiation effects. Over a certain amount of time, holes start to move toward the negative electrode, i.e. the silicon substrate, since, in this example, the gate has a positive bias imposed. The holes are then collected in the silicon substrate or captured in deep trapping sites. A large set of experiments, conducted since 1971, demonstrated the dependence of the hole transport mechanism by time, temperature and electric field [22, 23, 24]. It has become clear that the hole transport in  $SiO_2$  is rather anomalous in nature, since it lasts over decades of time, therefore is an highly time-dispersive process [25]. The holes that did not move through the oxide cause a negative flatband voltage shift, and therefore a negative threshold voltage shift [14]. From the set of experiments conducted in [22] and in [23], it emerged that the recovery time of the flatband voltage can be speeded from high temperatures and high electric fields, reaching a

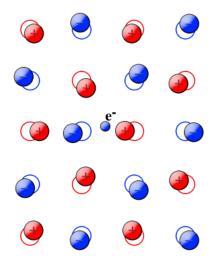

Figure 2.5: Representative image of a polaron. The conduction of one electron in a ionic crystal repels the negative ions and attracts the positive ones. Taken from [27]

reestablishment on the parameter in short time  $(t \ll 1 \text{ s})$ .

Holes transport in silicon dioxide through a complex mechanism, called polaron hopping. A polaron is a quasi-particle, proposed by Lev Landaun in 1933 [26], formed by the coupling of a charge and the defects that surround it, which result in a localized distortion of the lattice. This combination of charge and distorted defects moves with decrease velocity, since the effective mass is higher than the mass of the single charge. In Figure 2.5 is reported a visual representation of a polaron structure, taken from [27]. The time-dispersive movement is non-Gaussian. In a Gaussian transport process, the mean displacement of a carrier package,  $\overline{x}$ , increases linearly with time, while its dispersion,  $\overline{\sigma} = \sqrt{\overline{(x-\overline{x})}^2}$ , increases with the square root of the time. In a time dispersive transport, the time dependence of  $\overline{\sigma}$  is the same as  $\overline{x}$ , therefore their ratio is independent from time. This implies an asymmetric change in the carrier distribution over time [9]. In practice, there will be some fast charges that move rapidly deep in the oxide bulk, while most of the carriers will be left behind, since the dispersion increases faster in a timedispersive process [25]. Many studies, for example [25], showed that hole transport is precisely described from Continuous-Time Random Walk (CTRW) model. This model describe a walker hopping randomly on a periodic lattice, with the steps occurring at random time intervals [28].

#### 2.2.3 Hole Trapping in SiO<sub>2</sub>

Once the radiation-generated holes completed their transport through the SiO<sub>2</sub>, MOS structure presents a negative voltage shift in its electrical characteristics, for example in the threshold voltage (V<sub>TH</sub>), that can persist for years [9]. This longterm effect is attributed to the positive charge trapped in the oxide layer [9]. The term "hole trap" refers to a normally neutral oxide defect that can capture holes and retain them for long time period. Those defects are mostly formed by vacancies in the SiO<sub>2</sub> structure [29]. The silicon atoms are bonded with four oxygen atoms, and, if one of them is missing, two silicon atoms will be weakly bonded together, in a

Figure 2.6: Schematic of the  $E'_{\delta}$  center (a) and  $E'_{\gamma}$  center (b), taken from [31]. IEEE © 2002

structure generally called E' center [30]. The two silicon atoms share two electrons. The holes, moving along the oxide, can easily break this bond, recombining with one of the two electrons shared between the Si-Si structure. If this happens, the two silicon atoms are bonded with just a single electron. From [31], there are two different type of defects in the SiO<sub>2</sub> structure. The first, (which represent around 80 % of the total defects), is called  $E'_{\delta}$  center and is the only stable configuration. In this case, the electron is equally shared between the two Si-Si atoms, making the configuration neutral, with a shallow electron containing energy level (around 1 eV). In the second structure (which represent the other 20% of all the defects), one of the two silicon atom relaxes back past the plane defined by its three oxygen neighbors and bonds with another network of oxygen atoms, forming an asymmetrical positive charge structure, which is called  $E'_{\gamma}$  center and has a much higher electron containing energy level (around 4.5 eV). In Figure 2.6 there is a visual representation of the centers, taken from [31].

The charge trapped in the oxide undergoes through annealing processes, caused for example from tunneling effects in the silicon substrate, e-h recombination or electron injection from silicon [9]. It is clear that, the nearest is the charge trapped in the oxide, the easiest it can be neutralized by electrons coming from the silicon substrate. As an implication, oxide traps collocated far from Si/SiO<sub>2</sub> interface are, statistically, harder to neutralize. In case the trap is located near enough to the silicon substrate, it can react to any change of bias, switching back and forth from a positive charge state to a neutral state. This kind of traps have been formalized and defined as border traps, in [32], where all the oxide traps collocated at 3 nm or less from the Si/SiO<sub>2</sub> interface can be considered part of this category. From analysis conducted in [9], it is possible to express overall charge buildup process in the following incremental form:

$$\Delta n_{\rm th}(x,\Delta D) = F_{\rm h}(x)\sigma_{\rm ht}(E_{\rm ox}(x))[N_{\rm ht}(x) - n_{\rm ht}(x)] - F_{\rm e}(x)\sigma_{\rm r}(E_{\rm ox}(x))n_{\rm ht}(x)$$

(2.1)

Where,  $F_h(x)$  and  $F_e(x)$  are the local fluences per unit of dose for radiation-generated holes and electrons;  $n_{ht}(x)$  is the local density of trapped holes;  $N_{ht}(x)$  is the local density of hole traps;  $\sigma_{ht}(x)$  is the local oxide field-dependent cross-section of the holes traps for capturing holes;  $\sigma_r(x)$  is the local oxide filed-dependent cross-section for recombination of an electron with a trapped hole. The first part of the equation suggests that, starting from initial fluences per unit of dose of generate holes, some of them will be captured – therefore the presence of the field-dependent cross section term. The difference  $N_{ht}(x) - n_{ht}(x)$  are basically the empty traps state, that are effectively participating in the charge build-up process. The second part of the equation is subtracted to the first, since electron have a negative impact (due to recombination process) in the charge build-up. The charge density per unit of area is obtained integrating  $n_{ht}(x)$  over the oxide area, generally called  $d_{ox}(x)$ :

$$\Delta N_{\rm ot} = \frac{1}{d_{\rm ox}} \int_0^{d_{\rm ox}} n_{\rm ht}(\mathbf{x}) \mathbf{x} \, \mathrm{d} \mathbf{x} \tag{2.2}$$

Finally, the flatband voltage shift is:

$$\Delta V_{\rm ot} = -\frac{q}{\epsilon_{\rm ox}} d_{\rm ox} \delta N_{\rm ot}$$

(2.3)

From the previous equation it is possible to notice the linear dependence of the flatband voltage shifts from the oxide thickness. If the oxide thickness decreases, the shift of the flatband voltage follows the same trend. This linear dependence has led to a reduced sensitivity of the gate oxide in modern technologies, e.g. 130 and 65 nm, which has been proved to be capable of withstand ultra-high level of total dose [33]. In these technologies, the gate oxide is few nanometers thick (around 2 nm in the 65 nm technology node) and entirely composed of silicon dioxide. As we will see, the radiation response is dominated by the presence of auxiliary oxides, like the STI (Shallow Trance Isolation) and spacers.

### 2.3 Si/SiO<sub>2</sub> Interface Traps Depassivation

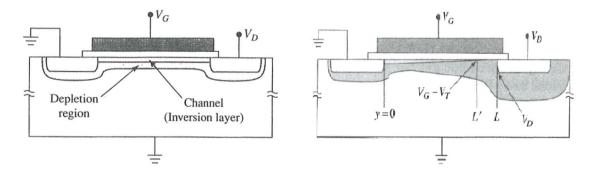

The interface between silicon and silicon dioxide is generally deficient of oxygen. therefore there is a good amount of strained or "dangling" silicon bonds. These dangling bonds act as interface traps with energy within the energy gap of the silicon [9]. More in the detail, Winkour and colleagues developed between 1977 and 1979 a model in which is sustained that the formation of interface traps occurs in a two-stage process [34]. The first stage is associated with the transport of radiationgenerated holes through the oxide. The hopping transport, described in Section 2.2, releases energy (evaluated around 5 eV). This energy breaks relatively weak H bonds with trivalent Si or with strained Si-O bonds formed during fabrication process. A released  $H^+$  ion, in case of positive bias, drift through  $Si/SiO_2$  interface, where it interacts with the dangling bonds and depassivate an interface traps. The activation of interface traps strongly depends on the electric field applied to the devices [35]. In fact, as it is possible to understand from Figure 2.7, extracted from [35], high electric fields enhance the formation and the trapping of charge in the  $Si/SiO_2$  trap centers. In that experiment, multiple samples were tested, each of them having different electric field applied. Sample E had negative electric field of -4 MV cm<sup>-1</sup> applied to the gate, and no increase from the pre-irradiation interface state value was observed. Sample A, had a positive and extremely high field applied, 4 MV cm<sup>-1</sup>, imposed for almost 10000 seconds. As regards samples B, C and D, the electric field was positive and equal to the one imposed on sample A, but after 1 second it was switched to the negative value of -4 MV cm<sup>-1</sup> and the charge trapping an the

Figure 2.7: Field experiments showing importance of positive field during second stage of Winkour model [34]

interface stopped. For sample B the electric field was switched positive again after a total time of 10 seconds, while for sample C it was switched back after 100 seconds. For sample D is kept at -4 MV cm<sup>-1</sup> until the end of the experiment. The results showed the extremely dependence from the electric field applied to the gate of the structure in the interface traps depassivation mechanisms.

As stated in [9], interface traps must be collocated within one or two atomic bond distances (about 0.5 nm) from the silicon lattice, so that electrons and holes can easily tunnel from valence band to conduction band and vice versa. It has been shown that high temperature strongly enhance the transitions rate – the number of transitions per unit of time – between the two energetic bands [36]. At T = 300 Kthe transitions rate for trap centers collocated close to the interface is about 100 transitions per second, while for further traps is 0.01 transitions per second. At T = 100 K, for the first type of traps centers the transitions rate drastically drops to  $10^{-8}$  transitions per second, while the latter one are essentially frozen, with a transition rate of 10<sup>-18</sup> transitions per second. Another extremely important propriety of the interface traps is their ampotheric nature. In fact, the polarity of the net charge residing in them can be positive, neutral or negative, with the respect of their position in the energy gap of the silicon, compared to the Fermi Level  $(E_F)$  and the Mid-Gap Level  $(E_M)$ . The defects in the bottom part of the band diagram are usually donor, which means that are neutral under  $E_F$  and when they are situated above  $E_F$  they free one electron, becoming positive charged. From the other side, defects collocated in the top part of the band diagram are acceptor, which means they are negative when above  $E_F$  and neutral once under it. As implication, if the voltage imposed on the gate is equal to the difference  $E_F - E_M$ , all the interface traps will have a neutral sign [9, 37].

### 2.4 ELDRS in Bipolar Devices

The discovery of the presence of a DR effect in microcircuit transistors can be dated back in 1991 [38] and in bipolar circuits in 1994 [39]. Following these first papers, several articles on Enhanced Low Dose Rate Sensitivity (ELDRS) have been produced, for example [40] and [41]. Most of those concepts have been summarized and further investigated by Pease and co-workers in [42]. The acronym of ELDRS was introduced before a real understating of the mechanisms. Further studies showed that the mechanism was more a reduced degradation for High-DRs, rather than an enhanced degradation for Low-DRs. A more accurate name would be therefore Reduced High Dose Rate Sensitivity (RHDRS). However, the acronym ELDRS remained and it is still used to refer to a DR sensitivity of the radiation response. A true low dose-rate effect is not always easy to distinguish, and may be confused with a time dependent effect. In particular, quoting [42]: "to distinguish real dose rate effects it is necessary to anneal the device irradiated at high dose rate maintaining constant the temperature for a period of time at least as long as the irradiation time at low dose rate". Many models have been proposed in order to explain and understand true dose rate effects in bipolar transistors. These models can be grouped into three main categories:

- Space Charge Models, see e.g. [43, 44, 45, 46]

- Bimolecular Process Models, see e.g. [47, 48]

- Binary Reaction Rate Model, see e.g. [49]

In the following sections a brief explanation of these three models will be proposed. The three models discuss the mechanisms differently and no agreement has yet been reached on which one is actually more consistent with the real processes. In any case, the effect of the dose-rate on the devices is extremely complex and it is difficult for a single model to explain with total correctness what phenomena occur.

### 2.4.1 Space Charge Models

Space charge model has been first developed by Fleetwood et. al., in the 1994 [43] and then further developed in other papers [44, 50]. In the first version, [43], it was reported how high dose-rates produce a space charge accumulation inside the BJT oxides. The accumulation of space charge was attributed to mechanisms that slows hole transport. In fact, the density of  $E_{\delta}$  trap centers in parasitic oxide is usually high and they trap the radiation-generated holes, causing a decrease in the holes mobility. As high dose-rate irradiation proceeds, more and more holes are trapped inside the centers, forming a "wall" of potential that prevents additional holes to get trapped in deep trap centers. The space charge generated at high dose-rates produces a local reversion of the potential, therefore part of the holes are trapped closely to the interface (instead of in the bulk of the oxide) where they are easily annealed, as reported in Figure 2.8. From the other hand, if the radiation is performed with a low dose-rate, the flux of generated holes is not high enough to keep constantly filled the big majority of the  $E'_{\delta}$  trap centers. Therefore the process proceeds without any slowdown and there is not formation of space charge in the oxide. In [44], an improved second version of the model proposed that also the radiation-generated electrons participate to a reduction in the overall damages as the DR increases. In fact, these electrons can recombine with a hole which is part of the space charge and create a stable neutral dipole, reducing the positive overall charge in the oxide, N<sub>ot</sub>. The first two versions of the model took in account the differences that low or high dose-rates cause to the charge trapped in the oxide,

Figure 2.8: At high dose-rates holes and protons generated close to the gate side drift toward the gate, rather than toward the  $Si/SiO_2$  interface, due to local reverse in the electric field caused by the space charge. After [46] IEEE © 1998

but they did not explain the influence of the DR on the depassivation of interface traps ( $N_{it}$ ). This was introduced in 1998, with the last version of the space charge model [50]. The space charge formed at high DRs reduces the effective number of H<sup>+</sup> able to reach the interface and then react with the Si-H bonds, reducing  $N_{it}$ .

In conclusion, space charge model states that high dose-rates generate a space charge in the oxide (supposed in [50] to be uniformly distributed, as reported also in Figure 2.9) that reduce the net positive charge trapped in the oxide,  $N_{ot}$  thanks to trapping of holes close to the interface (hence easily annealed) due to local electric field reversal [43] and thanks to radiation-generated electrons/holes recombination mechanisms [44], that lead to the formation of neutral stable dipoles. In addition, the number of interface traps is reduced since a less hydrogen ions are able to reach the interface [50].

#### 2.4.2 Bimolecular Process Models

Bimolecular process models are based on the interaction between two particles. Some studies suggested the presence of processes involving hydrogen reaction [51], trapped electron – free hole recombination [52], free electron – free hole recombination [51], molecular hydrogen formation [47], or a combination of hydrogen cracking and free electron recombination with trapped or transporting holes [48]. In general, each of these processes leads to a true dose rate effect by producing a sublinear total dose response at high dose rates [42]. In each of the studies proposed, authors carefully calculated the critical dose and dose rate (often respectively called N<sub>c</sub> and g<sub>c</sub>) values which must be exceeded before ELDRS effect is tangible. The most recent ELDRS models attempt to explain the effects of hydrogen on the ELDRS response of N<sub>it</sub> [48]. The reduced effects at High-DR can be related to a competition between defect reactions involving holes. The main reaction observed involves E'<sub> $\delta$ </sub> centers.

Figure 2.9: A uniform space charge distribution causes local inversion of the electric field in the bulk the oxide. As it is possible to notice, holes generated close to the Si interface drift toward the silicon bulk and can create interface traps. From the other side, holes generated closer to the gate electrode tend to drift toward it and get collected, reducing the net charge in the oxide. After [50] IEEE © 1998

Molecular hydrogen (two H atoms sharing their two electrons) is cracked at these sites and in the process, protons are released:

$$\mathbf{E}_{\delta}^{\prime} + \mathbf{H}_2 \to \mathbf{E}^{\prime}\mathbf{H} + \mathbf{H}^+ \tag{2.4}$$

From the previous interaction there is the formation of a trapped neutral hydrogen at the source site, which can in turn react with another hole to release an additional proton:

$$\mathbf{E}' + \mathbf{h} \to \mathbf{E}'_{\delta} \mathbf{H}^+ \to \mathbf{E}' + \mathbf{H}^+ \tag{2.5}$$

Where E' are neutral traps site. The protons migrate to the interface and depassivate the hydrogen, forming interface traps. At high dose rates, the net positive charge of the free holes, trapped holes and protons tends to confine the electron in the oxide [42]. The confined electron tends to recombine with the positively charged species, primarily the holes trapped at cracking sites:

$$\mathbf{E}_{\delta}^{\prime} + \mathbf{e} \to \mathbf{E}^{\prime} \tag{2.6}$$

Consequently, fewer protons will be released by these sites at high dose rates, and less damage will occur.

#### 2.4.3 Binary Reaction Rate Model

One last model that is worth to be discussed is the one developed by Freitag et. al. in [49] in which it is assumed that the built up of  $N_{it}$  is a results of two defects interacting according to binary reaction rate theory. Radiation generated holes reacts with pre-existing quantity of hydrogen, causing an initial buildup of  $N_{it}$ , with a rate that initially increases and the decreases as the quantity of hydrogen is used up. Later, a new "supply" of hydrogen (radiation generated) reaches the interface, increasing the rate of  $N_{it}$  build up. In [49], it is shown that the amount of degradation that occurs when the delayed cargo of hydrogen reaches the interface is much greater if the device is under irradiation. This mean that in low dose rate experiments – more time requiring than High-DR ones – the degradation will be enhanced.

## Chapter 3

## **CERN X-Ray Setup**

In this chapter we will briefly explain the whole measurement system used by the experiments reported in this thesis. It is a complex system that requires continuous maintenance. The implemented software is periodically updated, in order to have a good organization of the data obtained from the experiments.

### 3.1 CERN X-Ray Setup

All the irradiation experiments reported in this thesis are conducted inside the CERN X-Ray Seifer RP149 cabinet, pictured in Figure 3.1. Inside the cabinet, the X-Ray beam is located above a probe card, which is connected to the switching matrix (showed in 3.1) via Lemo cables. The device under test is placed on a copper block and the thermal chuck is moved manually to reach contact with the DUT, while monitoring trough the microscope incorporating a camera, as reported in Figure 3.2. The temperature is controlled by a thermal chuck, whose temperature can vary from -50 °C up to 200 °C. Its position can be controlled with a pad, connected via a serial port interface. The thermal control assure a stable temperature for the whole experiment, which is mandatory in qualification processes, since most of the radiation related processes are thermally activated at different temperatures. The measurements are performed with a semiconductor parameter analyzer, nomi-