**CERN-PPE/92-70** April 10th, 1992

# A NOVEL TECHNIQUE FOR FAST PULSE-SHAPING USING A SLOW AMPLIFIER AT LHC

N.Bingefors<sup>1</sup>, S.Bouvier<sup>2</sup>, S.Gadomski<sup>3</sup>, G.Hall<sup>4</sup>, T.S.Høgh<sup>5</sup>, P.Jalocha<sup>3</sup>, H.vd.Lippe<sup>6</sup>, J.Michel<sup>2</sup>, E.Nygård<sup>6</sup>, M.Raymond<sup>4</sup>, A.Rudge<sup>7</sup>, R.Sachdeva<sup>4</sup>, P.Weilhammer<sup>7</sup> and K.Yoshioka<sup>7</sup>

We describe a new technique for front end signal processing for LHC type applications, where a shaping amplifier with a time constant of several beam crossing intervals is used. The method is based on discrete time filtering of data extracted from an analogue pipeline after a first level trigger. A finite impulse response type filter deconvolutes the sampled voltages of the shaped pulse to retrieve the original impulse signal with high precision. Measurements showing the performance of the technique and its implication for signal to noise are presented.

The method is well matched to CMOS front ends, where low power consumption and low noise is achieved for silicon strip readout by utilising pulse shapes with time constants ~50 nsec. A CMOS circuit emulating the filter has been built. It has been implemented with very low power consumption (< 0.1mW) in a small silicon area to be utilized on every channel in the system.

LEPSI, Strasbourg, France 2)

Uppsala University, Uppsala, Sweden

<sup>3)</sup> Institute of Nuclear Physics, Cracow, Poland

<sup>4)</sup> Blackett Laboratory, Imperial College, London, UK

<sup>5)</sup> Norwegian Institute of Technology, Trondheim, Norway

6) Senter for Industriforskning, Oslo, Norway

<sup>7)</sup> CERN, Geneva, Switzerland

## INTRODUCTION

The detection of events generated in proton-proton collisions at the Large Hadron Collider will require the observation of interactions at intervals of 15nsec. It will be essential to identify the time origin of a signal with the precision of a single beam crossing interval. However it is extremely demanding, in terms of power consumption, to process signals from detectors with low noise using very short amplifier shaping times. In addition, pulse shapes employed in most amplifiers have tails which have durations several times longer than the rise time. These contribute to pile-up so that the presence of a pulse height above a given threshold may not alone constitute evidence of a detected particle.

For the readout of silicon microstrip detectors for tracking applications at LHC, low power and low noise are major considerations. Detector systems will contain several million channels of densely packed readout electronics in quite small volumes and the heat dissipated creates serious problems for the mechanical design. Therefore it is of the utmost importance to design an adequately low noise readout system with minimum power dissipation. A front end system based on a charge sensitive preamplifier and shaper to be implemented using CMOS technology is under study for LHC applications[1]. To achieve low power the shaping amplifier uses a relatively long shaping time of 45nsec. A novel technique is then used for processing the signals to achieve the aim of fast pulse shaping. This is referred to as deconvolution, since the operation performed is equivalent to retrieving the initial signal impulse from the shaped amplifier pulse. An important feature of its use is the fact that it relies on the regular sampling of amplifier output voltages at the beam crossing rate of the LHC machine (67MHz). This introduces the possibility of applying techniques more familiar in digital signal processing applications.

# THE DECONVOLUTION METHOD

In a linear amplifying system with an impulse response, h(t), the output, v(t), from an initial signal, s(t), can be written as a convolution integral:

$$v(t) = \int_{-\infty}^{t} h(t-t').s(t').dt'$$

In a system where the amplifier output voltage is sampled at regular intervals, so that the measurements of v(t), for example, are  $(v_1 \ v_2 \ v_3 \ v_4 \ v_5 ...)$  it is convenient to write the equation in a matrix form as

$$V_i = \sum_j H_{ij} S_j$$

or  $V = H. S$

The original signal impulse can be recovered by performing the inverse operation

$$S = W, V = H^{-1}, H, S$$

and the elements of the weight matrix W can be found by numerical matrix inversion of H. It can be shown [2] that for the CR-RC filter which is commonly used in amplifier systems the equations above reduce to a particularly simple form. If the system response is described by

$$v(t) = e^{1}(t/\tau). e^{-t/\tau}$$

there are only three non-zero weights necessary and

$$s_k = w_1. v_k + w_2.v_{k-1} + w_3.v_{k-2}$$

with values

$$w_1 = e^{x-1}/x$$

$w_2 = -2e^{-1}/x$   $w_3 = e^{-x-1}/x$

where  $x = \Delta t/\tau$  and  $\Delta t$  is the sample interval. This means that a filter performing this operation can be constructed by forming the weighted sum of three consecutive voltage samples in time. The same result can be derived in another way using z-transform theory[3-5].

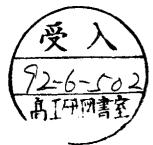

Estimates of noise in such a system can be made in a number of ways [2]. One method is to use the weighting function [6] which can be calculated by answering the question "What output is produced at some observation time  $T_m$  by an impulse which occurs at time t?" For the CR-RC pulse shape and the weighted sum above the weighting function can be written as

$$w(t) = (1+f) e^{-fx}$$

$-1 < f < 0$

= (1-f)  $e^{-fx}$   $0 < f < 1$

= 0 elsewhere,

where  $f = t/\Delta t$  and t = arrival time of impulse with respect to the sample time. Thus f > 0 corresponds to an early impulse and f < 0 to a late impulse. f = 0 corresponds to an impulse coincident in time with the signal delta pulse being measured; as required, w(0) = 1. The function is plotted in Fig. 1.

The noise in the system can be calculated by computing two integrals:

$$\int_{-\infty}^{\infty} [w(t)]^2 dt$$

for the parallel noise, and

$$\int_{-\infty}^{\infty} [w'(t)]^2 dt$$

for the series noise.

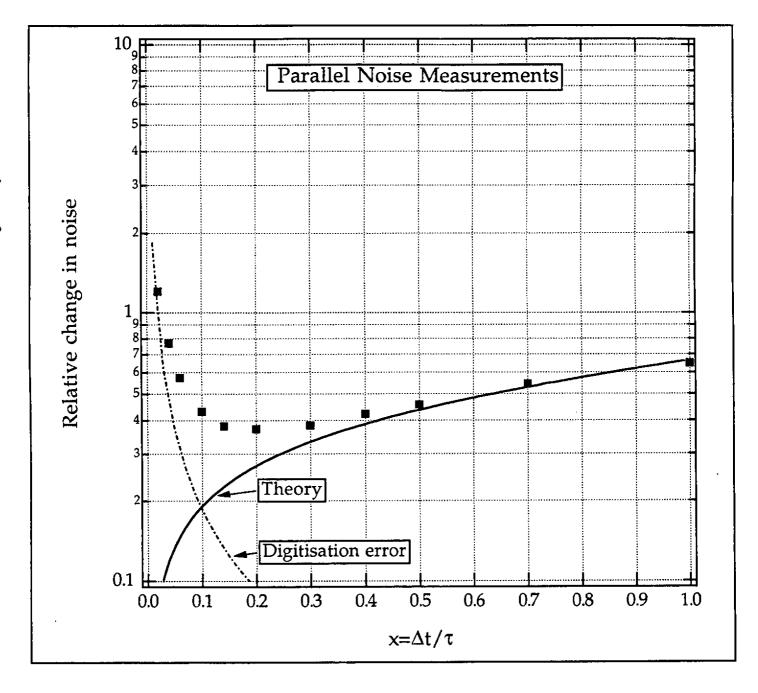

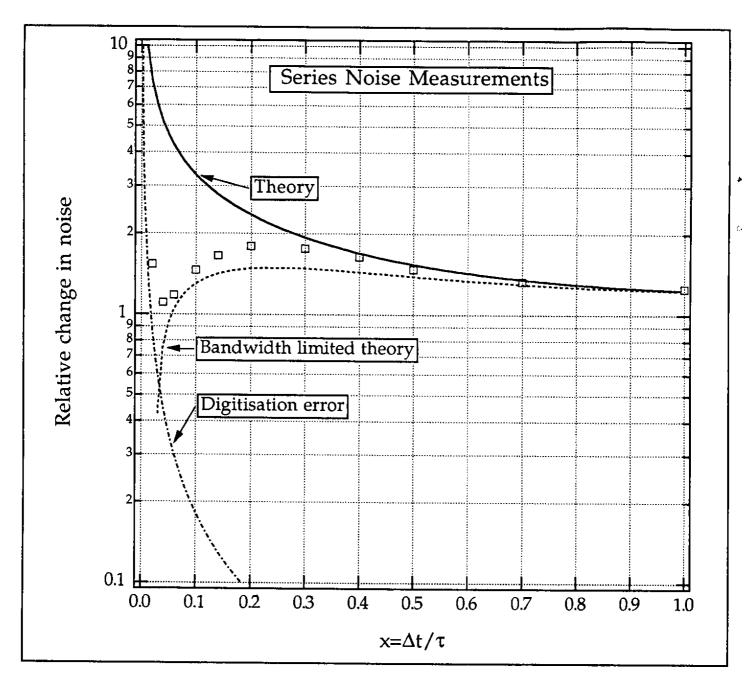

The results are given in [1], normalised to the same integrals for the CR-RC filter. They show that parallel noise is reduced following the filter and series noise is increased, as the operation is effectively equivalent to reshaping the output pulse with a shorter time constant.

## **DEMONSTRATION OF THE DECONVOLUTION METHOD**

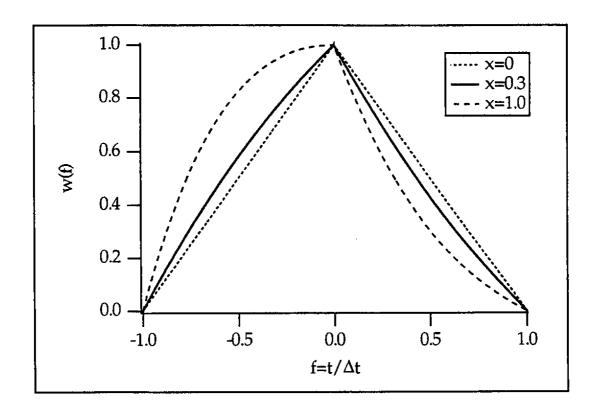

Using an amplifier constructed as a prototype for silicon strip readout at LHC [7] we have verified the principle by digitising output waveforms using a sampling oscilloscope. The amplifier is a CMOS circuit with a charge sensitive preamplifier and shaping filter closely approximating an CR-RC pulse shape with t=45nsec. Fig. 2(a) shows the digitised output produced by a fast test pulse at the amplifier input and Fig. 2(b) shows the consequence of forming a weighted sum of the samples using the weights calculated above for a value x=1/3. This corresponds to the proposed ratio of sampling time ( $\Delta t=15$ nsec) to  $\tau$ .

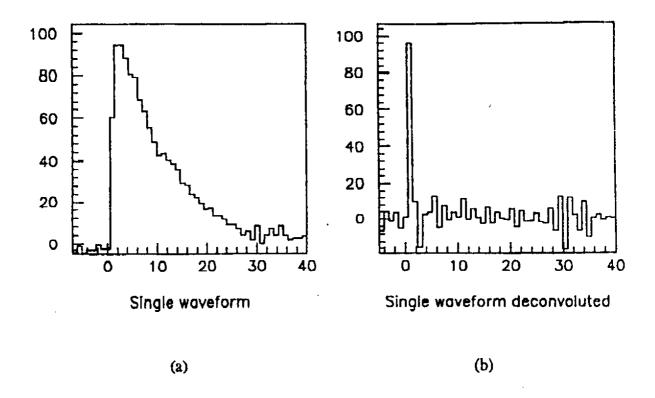

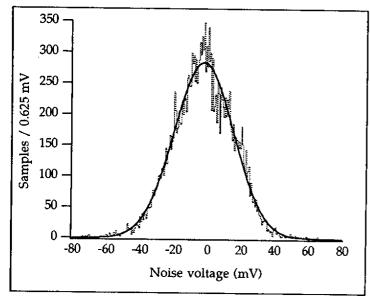

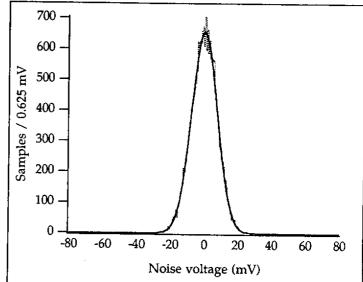

It was considered of great importance to verify the general validity of the noise calculations [2]. To achieve this another charge sensitive amplifier (Ortec 142A) was used with a pulse shaping filter with a time constant of approximately 500nsec. The scheme is shown in Fig. 3. Low value resistors were placed at the system input as a means of generating parallel noise in the system which would dominate over other noise sources. Data were digitised at intervals of 10nsec and transferred to an offline computer for analysis where they were processed by selecting samples at different intervals so that a wide range of x, 0.02 - 1, could be covered. The noise fluctuations were histogrammed and r.m.s values extracted before and after the deconvolution operation (Fig. 4) from a fit to a gaussian line shape. In a similar way data were also acquired using a large capacitor at the amplifier input to ensure that series noise dominated and the noise before and after deconvolution compared. The results are summarised in Fig. 5.

To compare the calculations to measurements it is important to be aware of additional experimental factors which enter [8]. In a digital system quantisation of the measured samples with the resolution of the ADC (8 bits) occurs, which makes an additional contribution to the measured error. For measurements of series noise the bandwidth of the system, which is modified by the large input capacitance, needs to be taken into account since this increases the preamplifier risetime in a well known way [9]. Once these effects are taken into account the data agree well with the calculations.

#### A BRIEF SYSTEM DESCRIPTION

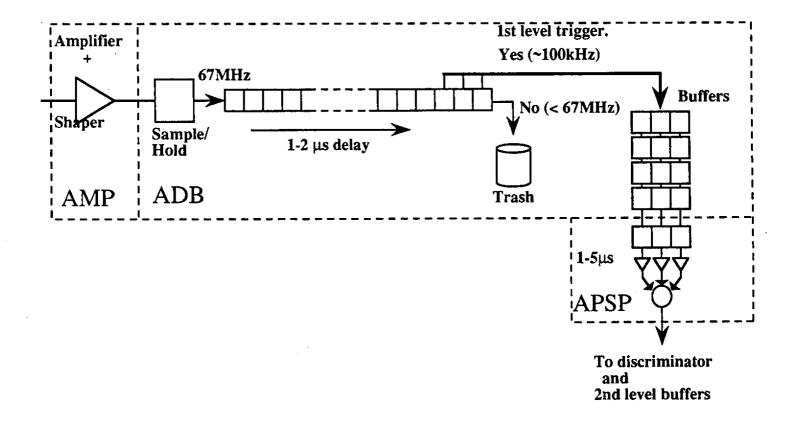

A system has been built which realizes the scheme. It is shown in Fig. 6 and consists presently of three separate chips: the preamplifier with CR-RC shaper (AMP), an Analog Delay and Buffer (ADB) and an FIR (finite impulse response) filter denoted as Analog Pulse Shape Processor (APSP). The ADB is an analog pipeline running at 67MHz and includes the digital logic necessary to control the flow of data to interface with the APSP.

The output of AMP is sampled every 15ns. Each sample is stored exactly for the same time as the 1st level trigger delay. During the period in which no 1st level trigger occurs ("no"), which is more than 99% of the time, samples are discarded and overwritten by new samples. However, when a 1st level trigger does occur ("yes"), three samples are transferred to the APSP, which calculates the convolution sum. The average time between each positive 1st level trigger is expected to be ~10µs. Consequently, if the APSP spends less time than this on each calculation, the system will be deadtime free, providing buffers (which are included in the ADB) are provided to store data from 1st level triggers occurring close together.

Because the APSP only operates on data selected by the 1st level trigger the filter operation can be accomplished consuming very little power. This configuration is possible due to the fact that the impulse response of the deconvolution filter is finite and with only a small number of weights.

#### THE APSP CIRCUIT

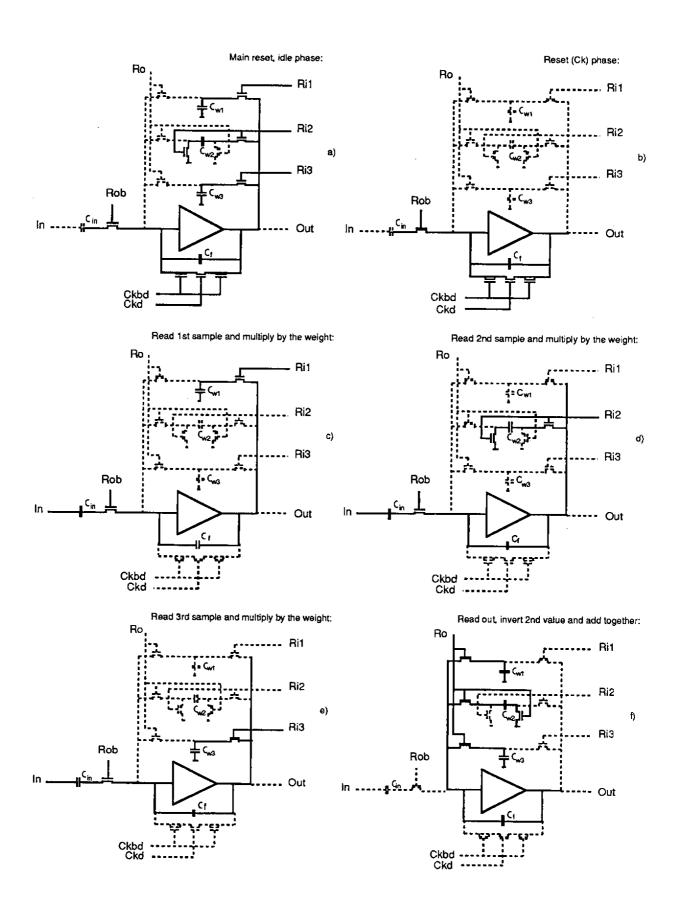

A CMOS circuit has been made to implement the FIR filter. Figure 7 shows the analogue circuit schematic and illustrates the method of operation. The clock runs continuously and has a duty cycle of ~20%. When the circuit is idle or the clock is high, the indicated elements in a) and b) are reset. The operation is sequential and takes 4 clock periods.

The principle is simple. In the first clock period the first analog value is read in, amplified by the ratio Cin/Cf and stored on the uppermost capacitor as shown in c). In the next two periods the same happens with the two subsequent analogue values except now the results are stored on the middle and lowermost capacitor respectively as shown in d) and e). In the fourth clock period the charges from the three capacitors are added together and integrated on the feedback capacitor and the final result appears on the output. In this scheme, the size of the storage capacitors controls the magnitude of the weight and the flipping of the middle capacitor accomplishes the change of polarity.

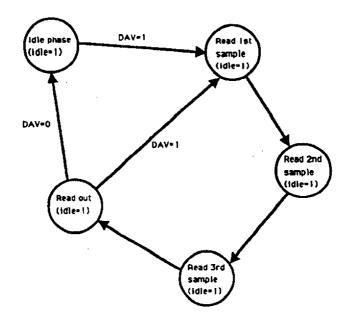

A digital control circuit has been put on the chip to generate all the necessary clock signals and to communicate with the ADB from which the input data comes. The latter is accomplished by the DAV and IDLE signals. The Data AVailable (DAV) signal is generated by the ADB immediately after a 1st level trigger and remains until all the required samples from this event have been read out. If new events appear during the readout of a previous event, DAV will remain until the samples from these are read out. The IDLE signal is generated by the APSP and its main purpose is to make sure that the readout of the ADB is fully synchronized with the read-in of the APSP. The circuit is implemented as a classical finite state machine and the control flow chart is shown in Fig. 8.

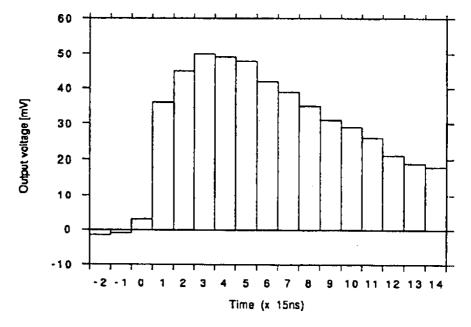

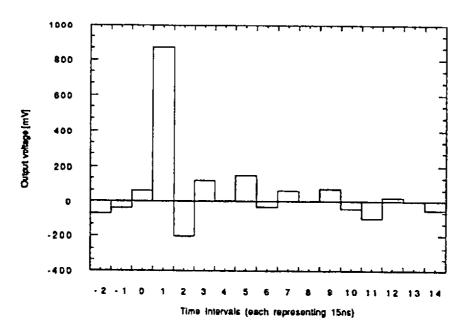

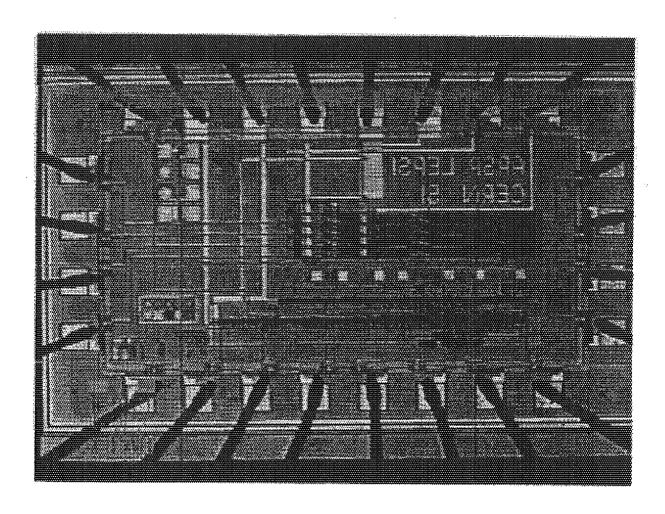

In Fig. 9 a measured output sequence of the circuit is shown for an input signal observed using the amplifier described above. The circuit accomplishes satisfactorily the required function of the FIR filter. The clock frequency used in the measurements was 1MHz, and the total power consumption for the circuit is less than  $100\mu W$ . A chip photograph is shown in Fig. 10.

# **Acknowledgements**

We thank V. Radeka for drawing our attention to the utility of the weighting function and Paul Rensing for information on the SLD CRID deconvolution scheme. Roland Horisberger provided ideas for the APSP circuit. We also thank our colleagues in RD20 for their interest and support and Carole Ponting for the preparation of this paper.

#### **REFERENCES**

- [1] H. Borner et al., The Development of High Resolution Silicon Strip Detectors for Experiments at High Luminosity at the LHC. CERN R&D Proposal CERN/DRDC 91-10 (1991).

- [2] S. Gadomski, G. Hall, T. Høgh, P. Jalocha, E. Nygård, P. Weilhammer The Deconvolution Method of Fast Pulse Shaping at Hadron Colliders. CERN-PPE/92-24 (1992).

- [3] T. Bienz. Ph.D thesis. SLAC Report SLAC-369 (1990).

- [4] P. Antilogus et al. SLAC PUB-5120.(1990). To be published in IEEE Trans. Nucl. Sci. .

- [5] N. Bingefors. University of Uppsala internal note. TSL/ISV-92-0062 1992)

- [6] V. Radeka. Optimum signal processing for pulse-amplitude spectrometry in the presence of high rate effects and noise. IEEE Trans. Nucl. Sci. NS-15 (1968) 455.

- [7] G. Hall, T. Høgh, W. Lange, E. Nygård, P. Weilhammer, K. Yoshioka. Paper presented at this conference.

- [8] G. Hall, M. Raymond, R. Sachdeva. Imperial College internal note IC/HEP/92/3 (1992).

- [9] V. Radeka. Signal, Noise and Resolution in Position Sensitive Detectors. IEEE Trans. Nucl. Sci. NS-21 (1974) 51.

## **FIGURE CAPTIONS**

- 1. The weighting function for the CR-RC shaper and deconvolution system.

- 2. (a) The measured impulse response of the CMOS amplifier.

- (b) The result of deconvoluting the signal measured in (a).

- 3. The system used to verify the noise calculations.

- 4. Noise distributions before and after deconvolution.

- 5. (a) Parallel noise measurements compared with the theory.

- (b) Series noise measurements compared with the theory.

- 6. A schematic diagram of the system proposed to implement the deconvolution method

- 7. The APSP circuit and the operating sequence.

- 8. A finite state flow chart of the APSP.

- 9. Measurements on the APSP-circuit:

- shows the input sequence which is a measured output sweep from the CR-RC shaper.

- b) shows the response of the APSP.

- 10. A photograph of the prototype APSP chip.

Fig. 1

Fig. 2

Fig. 3

Fig. 4

Fig. 5 (a)

Fig. 5 (b)

Fig. 6

Fig. 7

Fig. 8

Ç

Fig. 9 a

Fig. 9 b

Fig. 10