# Prometeo: A portable test-bench for the upgraded front-end electronics of the ATLAS Tile calorimeter

```

Daniel Bullock<sup>*a</sup>, Fernando Carrió<sup>b</sup>, Moruga Govender<sup>c</sup>, Ivan Hofsajer<sup>c</sup>, Bruce

Mellado<sup>c</sup>, Pablo Moreno<sup>bc</sup>, Robert Reed<sup>c</sup>, Xifeng Ruan<sup>c</sup>, Charles Sandrock<sup>c</sup>, Carlos

Solans<sup>d</sup>, Reto Suter<sup>c</sup>, Giulio Usai<sup>a</sup>, Alberto Valero<sup>b</sup>

```

<sup>a</sup>The University of Texas at Arlington 701 S. Nedderman Drive, Arlington, TX USA 76019 <sup>b</sup>The University of Valencia Av. Blasco Ibàñez, 13. 46010 Valencia. Spain <sup>c</sup>University of the Witwatersrand, Johannesburg 1 Jan Smuts Avenue, Braamfontein 2000, Johannesburg, South Africa  $^{d}CERN$ CH-1211 Geneva 23, Switzerland E-mail: daniel.bullock@cern.ch, fernando.carrio@cern.ch, vicent.govender@wits.ac.za, iwh@ieee.org, bruce.mellado.garcia@cern.ch, pablo.moreno@cern.ch, robert.reed@cern.ch, ruanxf.ruan@cern.ch, charles.john.sandrock@cern.ch, carlos.solans@cern.ch, reto.josef.suter@cern.ch, giulio.usai@cern.ch, alberto.valero@cern.ch On behalf of the ATLAS Tile Calorimeter System

Prometeo is a portable test-bench for full certification of the front-end electronics of the ATLAS Tile calorimeter, designed for the upgrade phase-II. It is a high-throughput electronic system designed to simultaneously read out all the digitized samples from 12 channels at the LHC bunch crossing frequency and assess the quality of the data in real-time. The core of the system is a Xilinx Virtex 7 evaluation board extended with a dual QSFP FMC module to read out and control the on-detector electronics. The rest of the functionalities of the system are provided by a HV mezzanine board that supplied the HV to the photo-multipliers, an LED board that sends light to illuminate them, and a 12 channel ADC board that samples the analog trigger output of the front-end. The system is connected by ethernet to a GUI client from which QA tests are performed on the electronics such as noise measurements and linearity response to an injected charge.

Technology and Instrumentation in Particle Physics 2014, 2-6 June, 2014 Amsterdam, the Netherlands

<sup>\*</sup>Speaker.

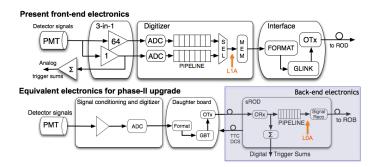

Figure 1: The phase-II upgrade of TileCal.

# 1. Introduction

The Tile Calorimeter (TileCal) is a hadronic sub-detector in the ATLAS experiment at CERN[1]. TileCal is divided into four parts including a long central barrel (LBA and LBC) and two extended barrels (EBA and EBC), and is capable of covering the pseudorapidity ( $\eta$ ) range  $|\eta| < 1.7$ . Each cylinder is further separated azimuthally ( $\phi$ ) into 64 modules, and each module is segmented in  $\eta$  and depth by cells. Each cell in TileCal consists of alternating steel plates and plastic scintillator tiles. The particle energy is sampled by the scintillators and signals are collected from the photomultipliers (PMTs) by the front-end electronics in the outermost part of the detector module (the drawer).

Each module in TileCal must be independently serviced and evaluated for quality assurance to ensure that TileCal is ready for data-taking periods. The current certification test-bench for TileCal (MobiDICK) has been the result of operational service and upgrades since 2003.

The High Luminosity LHC upgrade is planned for the 2022 long shutdown (LS3)[3], which demands a complete replacement of both on- and off-detector electronics in the ATLAS experiment. This upgrade places several requirements on the future of the detector[4] (see Figure 1), including improved radiation tolerance, smaller independent modules (mini-drawers) to reduce consequences of malfunctions, an increase in the number of point-to-point links with the front-end electronics, a digital trigger for more precise measurements, a higher read-out bandwith due to higher energy, higher luminosity, more pileup, and more data by several orders of magnitude.

Because of the overhaul in all of the electronics systems, a new test-bench system is undergoing design and prototyping to replace MobiDICK. Prometeo (Portable ReadOut ModulE for Tilecal ElectrOnics) is required to: analyze data from 12 PMTs at the LHC bunch crossing frequency, assess the quality of the data in real-time, diagnose malfunctions in each mini-drawer, be self-contained and portable for maintenance inside the detector, be low-cost but easy to upgrade when components become obsolete, and be scalable for network usage.

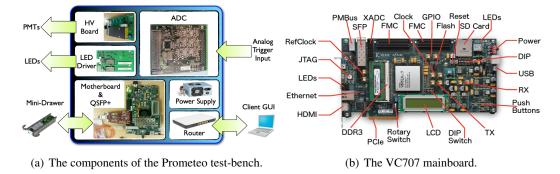

To accomodate these upgrades, Prometeo contains (Figure 2(a)) a VC707 mainboard, an ADC board to digitize the trigger signal, an HV board to provide high voltage to the PMTs, an LED board to pulse the PMTs, a QSFP+ module to communicate with the mini-drawers, a router to communicate with the user, a power supply. A dedicated client software is also maintained to meet the needs of the end-user.

### 2. Hardware Design

The core of the system is a Xilinx Virtex7 VC707 evaluation board with a XC7VX485T-

Figure 2: The hardware design of the Prometeo test-bench.

2FFG1761 FPGA (Figure 2(b)). The board is equipped with 1GB DDR3 RAM and two FMC connectors to interface with the mezzanine QSFP+ and ADC.

The on-board flash is programmed with an IPbus protocol[5] that is capable of storing samples by memory address and retrieving them upon trigger request. This protocol has been adapted from the IPbus suite developed by the CMS collaboration[6] to reduce its complexity in regards to code management and package dependency, streamline its performance, and ensure that it can be compiled on any system. This implementation of IPbus does not require an on-board operating system and does not place a requirement on the user's choice of client operating system.

To interface with the current analog calorimeter/muon trigger system, a hybrid test-bench includes an ADC board that digitizes the analog Level 1 trigger signals and sends Trigger and Timing Control (TTC) commands to the mini-drawer.

The HV board, which is identical to the one used in MobiDICK version 4[2], receives +24 V input voltage and +3.3 V transistor-transistor logic (TTL) from the mainboard to turn on/off the high voltage to the mini-drawers. Inside the mini-drawers, the bias voltage applied to each PMT is controlled via dedicated cards.

Optical communication through a dual FMC to QSFP+ module (HTG-FMC-X2QSFP+) allows the system to control the front-end boards of the mini-drawer and read out samples. This optical read-out is capable of operating at 40 Gb/s (or 80 Gb/s with dual redundancy) to match the design specifications of the future TileCal super Read-Out Driver (sROD).

The LED driver is also borrowed from the MobiDICK version 4 design to provide a sharp voltage peak to a LED device that illuminates the PMTs. Two negative pulses (for two sides of the mini-drawer) are generated with an amplitude of -17 V and a width of 20 *ns* at the LHC orbit frequency by the rising edge of a pulse from the mainboard.

The test-bench also contains its own ATX power supply for the mainboard and all mezzanines, as well as a router to communicate with the user through an ethernet connection. All components are assembled into an aluminum box that is  $50 \ cm \times 35 \ cm \times 20 \ cm$  in size and has a total weight of approximately 8 kg. The test-bench was designed to be lightweight and portable to accomodate the conditions under which maintenance teams will operate the test-bench and certification procedures.

#### 3. Software

The system is based on a client-server architecture, where Prometeo acts as a server that com-

municates via ethernet through a VHDL module with an IPbus implementation. The client connects via UDP protocol using a modular framework with plug-ins of panels for different tests of the mini-drawer. This architecture is client-driven, allowing the client direct control and on-the-fly modification of the functionalities of the server.

The software communicates with the server through the IPbus protocol to perform read/write functions on a specified memory address or to a FIFO memory. The list of registers is maintained by the firmware to configure the commands, status, position in data, number of samples, calibration parameters, etc.

The IPbus software is written in C++ and a Python extension is included to improve the enduser scripting abilities, which is frequently used in writing new tests. Alternatively, the user may also use the Java GUI to interactively manage the test results. The C++ implementation and its Python extension can be compiled on any platform, and a Java GUI is also portable to any operating system. In any case, the core of the software is a set of algorithms that wrap the commands of the IPbus protocol into functions for dedicated tests of the mini-drawer.

Many of the tests written for Prometeo are similar to those that are present in the MobiDICK system (Willy). The user is able to test communication with the mini-drawer, to execute control over front-end cards, LEDs, and HV power, and to manage data storage/retrieval from FIFO or address-specific memory. Tests of the charge injection, PMT noise, and triggering have also been rewritten for the new system.

#### 4. Conclusion

Prometeo is designed for the certification of the phase-II TileCal front-end electronics. The test-bench is capable of performing multiple tests inspired by the success of the MobiDICK systems in the maintenance of the TileCal super-drawers. Prometeo is currently in a prototyping phase where it serves a hybrid demonstrator of the future phase-II electronics. All components of this demonstrator are in-hand and undergoing tests as they are added to the system. Charge-injection tests have been successful and pulses have been measured. A test of the linearity of fast-pulse response for a range of charges has also been successful. Further tests are being developed and tested in parallel with the development of the demonstrator.

## References

- [1] The ATLAS Collaboration, ATLAS detector and physics performance: Technical Design Report, 1, CERN Document Server CERN-LHCC-99-014.

- [2] F. Carrió et al., The ATLAS Collaboration, Design of an FPGA-based embedded system for the ATLAS Tile Calorimeter front-end electronics test-bench, CERN Document Server ATL-TILECAL-PROC-2013-017.

- [3] The ATLAS Collaboration, Letter of Intent for the Phase-II Upgrade of the ATLAS Experiment, CERN Document Server CERN-LHCC-2012-022.

- [4] F. Carrió et al., The ATLAS Collaboration, *The sROD Module for the ATLAS Tile Calorimeter Phase-II Upgrade Demonstrator*, *CERN Document Server* ATL-TILECAL-PROC-2013-020.

- [5] R. Frazier et al., The IPbus Protocol: An IP-based control protocol for ATCA/µTCA, 2013, Draft 6.

- [6] R. Frazier et al., Software and firmware for controlling CMS trigger and readout hardware via gigabit *Ethernet*, *Physics Procedia*, 37 (2012) 1892-1899.