# System Electronics for the ATLAS Upgraded Strip Detector

Release 2.0 - 05 Feb 2013

T. Affolder<sup>a</sup>, F. Anghinolfi<sup>b</sup>, A. Clark<sup>f</sup>, W. Dabrowski<sup>c</sup>, J. Dewitt<sup>d</sup>, S. Diez Cornell<sup>k</sup>, N. Dressdant<sup>e</sup>, V. Fadeyev<sup>d</sup>, P. Farthouat<sup>b</sup>, D. Ferrere<sup>f</sup>, A. Greenall<sup>a</sup>, A.A. Grillo<sup>d</sup>, J. Kaplon<sup>b</sup>, M. Key-Charriere<sup>g</sup>, D. La Marra<sup>f</sup>, E. Lipeles<sup>e</sup>, D. Lynn<sup>b</sup>, M. Newcomer<sup>e</sup>, F. Pereira<sup>b</sup>, P. Phillips<sup>g</sup>, E. Spencer<sup>d</sup>, K. Swientek<sup>c</sup>, M. Warren<sup>i</sup>, A. Weidberg<sup>j</sup> <sup>a</sup> University of Liverpool Liverpool L69 3BX, United Kingdom <sup>b</sup> CERN, 1211 Genève 23, Switzerland <sup>c</sup> AGH University of science and technologie Krakow, Poland <sup>d</sup> University of California, Santa-Cruz, 1156 High Street, Santa Cruz, Ca 95064, USA <sup>e</sup> University of Pennsylvannia Department of Physics & Astronomy, 209 South 33rd Street, Philadelphia, PA 19104-6396, USA University of Geneva DPNC, 24 Quai Ernest-Ansermet, 1211 Genève 4, Switzerland <sup>g</sup> Rutherford Appleton Laboratory Harwell Oxford, Didcot, OX11 0QX, United Kingdom <sup>h</sup> Brookhaven National Laboratory P.O. Box 5000, Upton, NY 11973-5000, USA University College of London Department of physics and astronomy, Gower Street, London, WC1E 6BT, United Kingdom University of Oxford Physics department, Clarendon Laboratory, Parks Road, OXI 3PU, Oxford, United Kingdom <sup>k</sup> Lawrence Berkelev National Laboratory 1 Cyclotron Road, Berkeley, CA 94720, USA

E-mail: Alexander Grillo <agrillo@ucsc.edu>

ABSTRACT: This document describes the architecture of the readout electronics of the ATLAS upgraded silicon strips detector and the design of the front-end electronics system and ASICs.

**KEYWORDS**:

# **Release History**

| Rel. No. | Date      | Pages | Description of Changes                                 |

|----------|-----------|-------|--------------------------------------------------------|

| 1.0      | 30-Jun-12 |       | Initial Release                                        |

| 2.0      | 05-Feb-13 | 5-7   | Figure 1 and Table 1 changed to agree with LOI layout. |

|          |           | 9     | Power numbers changed to agree with LOI layout.        |

|          |           | 10-11 | Clarified buffering scheme.                            |

|          |           | 12    | Clarified Data Compression Logic hit reporting.        |

|          |           | 13    | Expanded description of data packets.                  |

|          |           | 25-26 | Refined description of action at L0A signal.           |

|          |           | 26    | Clarified output bandwidth options for HCC.            |

|          |           | 29    | Corrected bandwidth requirement per stave-side.        |

|          |           | 32-33 | Added section 3.5 on Redundancy.                       |

|          |           | 36,44 | Corrected numbers in Tables 18, 19 & 20.               |

|          |           | 44    | Corrected services line counts for LOI layout.         |

# Contents

| 1. Introduction                                                 | 5  |

|-----------------------------------------------------------------|----|

| 2. Overview of the readout system                               | 5  |

| 2.1 Detector Lay-out                                            | 5  |

| 2.2 Tracker parameters and environmental conditions             | 6  |

| 2.2.1 Number of channels for the strips detector                | 6  |

| 2.2.2 Working temperature                                       | 6  |

| 2.2.3 Radiation levels                                          | 6  |

| 2.3 Readout units for the strip detector                        | 8  |

| 2.4 Rough estimate of the total power in the strip detector     | 9  |

| 2.5 Interface to the trigger DAQ                                | 9  |

| 2.5.1 Level-1 Accept rate                                       | 9  |

| 2.5.2 Possible tracking as part of the Level-1 trigger          | 10 |

| 2.5.3 Regional Readout Request (R3) scheme                      | 10 |

| 2.6 Policy for fighting SEU                                     | 11 |

| 3. Data readout chain                                           | 11 |

| 3.1 Front-end ASIC: ABC130                                      | 12 |

| 3.1.1 Control Signals                                           | 14 |

| 3.1.2 Bi-Directional Signals                                    | 15 |

| 3.1.3 Fast Cluster block for self-seeded track tracker          | 15 |

| 3.2 Hybrid controller ASIC: HCC                                 | 17 |

| 3.2.1 Description of the HCC I/Os                               | 18 |

| 3.2.2 GBT Generated Signals                                     | 20 |

| 3.2.3 Hybrid Side Common Signals                                | 22 |

| 3.2.4 Hybrid Side Data collection                               | 22 |

| 3.2.5 Stave side Data Out                                       | 22 |

| 3.2.6 Autonomous Monitoring                                     | 23 |

| 3.3 Data correlator chip for self-seeded track trigger          | 23 |

| 3.4 End of stave electronics                                    | 25 |

| 3.4.1 Using the GBT                                             | 25 |

| 3.4.2 The Versatile Link                                        | 27 |

| 3.5 Redundancy                                                  | 32 |

| 4. Power distribution                                           | 33 |

| 4.1 Low voltage distribution                                    | 33 |

| 4.1.1 Power model of a short strip single sided stave           | 34 |

| 4.1.2 Effect of a 1.2V Vdd and of additional LDOs in the ABC130 | 35 |

| 4.1.3 DC-DC physical implementation                             | 37 |

| 4.1.4 Serial power physical implementation and Serial Power and Protection ASIC | 37 |

|---------------------------------------------------------------------------------|----|

| 4.1.5 Off-detector low voltage bulk supply                                      | 42 |

| 4.2 High voltage distribution                                                   | 42 |

| 4.3 Cable plant for power distribution                                          | 43 |

| 4.3.1 High voltage cable plant                                                  | 43 |

| 4.3.2 Low voltage cable plant                                                   | 43 |

| 4.3.3 Power distribution cable plant summary                                    | 44 |

| 5. DCS & Interlocks                                                             | 45 |

| 5.1 The DCS architecture                                                        | 45 |

| 5.2 The detector safety and interlocks                                          | 46 |

| 5.3 Control                                                                     | 47 |

| 5.4 The monitoring stages                                                       | 48 |

| 6. Development plans                                                            | 49 |

# List of Figures

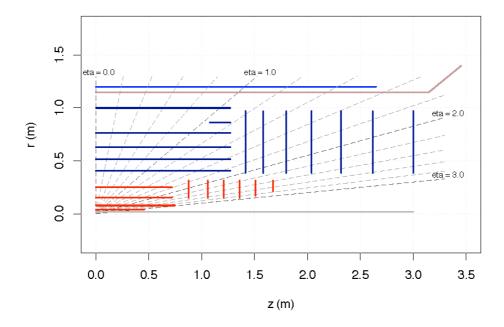

| Figure 1: LOI Layout – one quadrant.                                                                 | 6  |

|------------------------------------------------------------------------------------------------------|----|

| Figure 2: 1 MeV neutron equivalent fluence for 3000 fb-1 integrated luminosity                       |    |

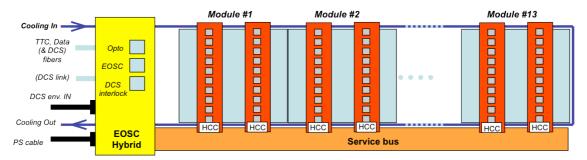

| Figure 3: Sketch of a single-sided stave of short strips.                                            |    |

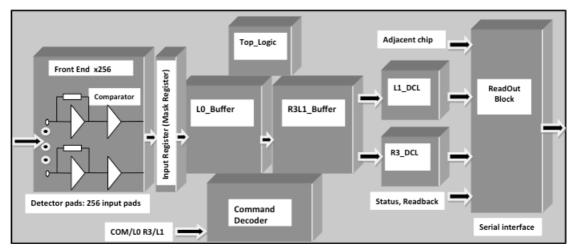

| Figure 4: Block diagram of the ABC130 readout part with the R3 capability                            |    |

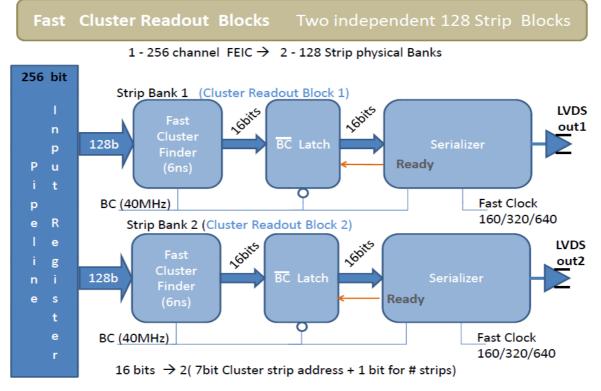

| Figure 5: Block diagram of the fast cluster blocks in ABC130                                         |    |

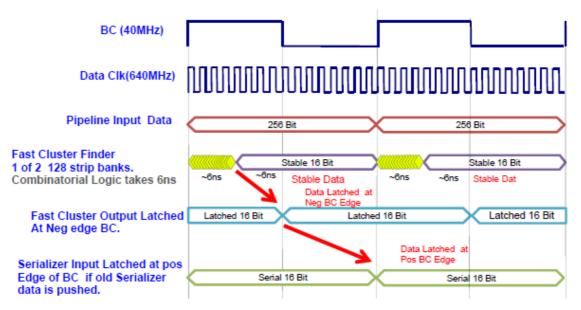

| Figure 6: Cluster finding Logic Data synchronization                                                 |    |

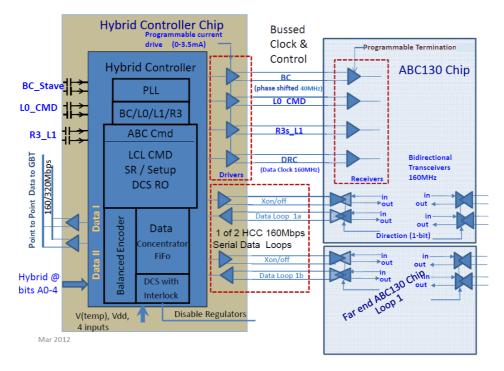

| Figure 7: Block diagram of the Hybrid Controller Chip (HCC) and related I/O lines                    | 20 |

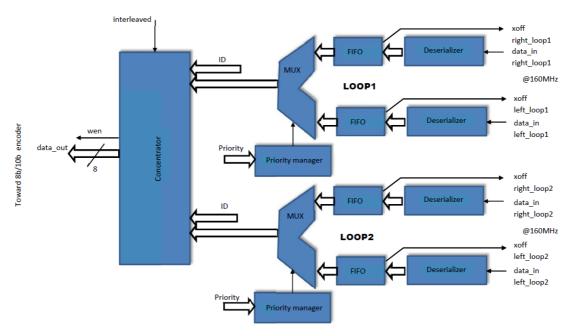

| Figure 8: Block diagram of the HCC data concentrator.                                                |    |

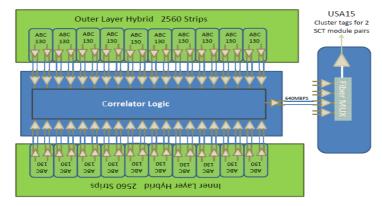

| Figure 9: Notional schematic of the hookup of the Correlator chip.                                   |    |

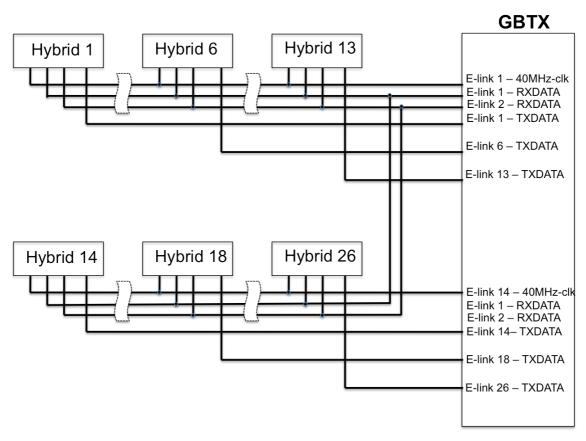

| Figure 10: View of the GBTx and 26 readout hybrids.                                                  |    |

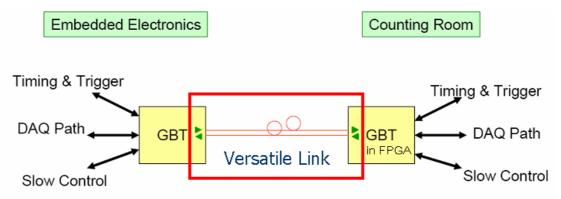

| Figure 11: GBT and VL system                                                                         |    |

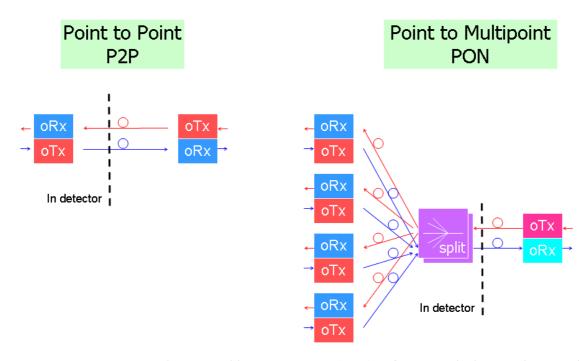

| Figure 12: VL P2P and PON architectures                                                              |    |

| Figure 13: VTRx prototype.                                                                           |    |

| Figure 14: Power model of a short strip single sided stave.                                          |    |

| Figure 15: The DC-DC powered stavelet.                                                               |    |

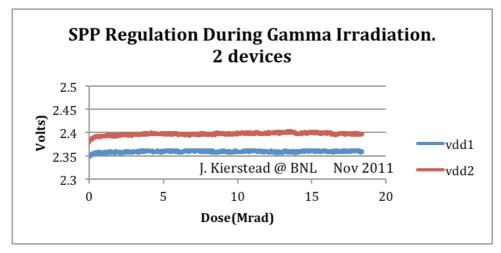

| Figure 16: Measured variation of the SPP internal shunt regulator Vdd up to 18 MRad                  |    |

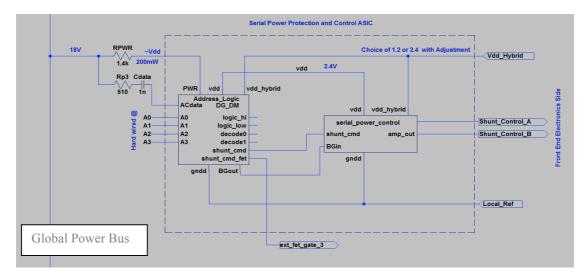

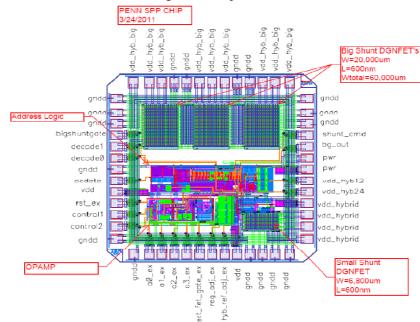

| Figure 17: Block Level Schematic of the SPP ASIC.                                                    | 39 |

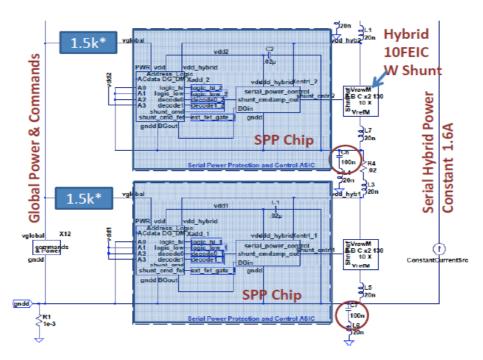

| Figure 18: The schematic of the hookup of two SPP ASICs on a serially powered stave                  |    |

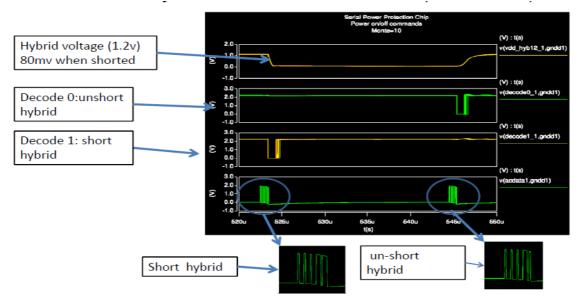

| Figure 19: Simulation of 12 hybrids demonstrating the shorting of a hybrid using external pulse widt | th |

| modulation.                                                                                          |    |

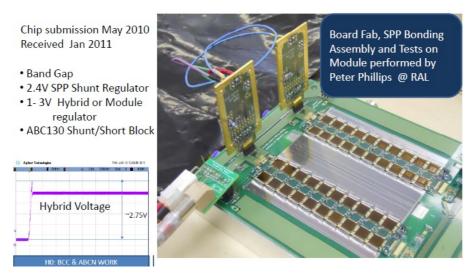

| Figure 20: Two SPP analogue only prototype boards powering a module.                                 | 41 |

| Figure 21: The SPP Version 0.                                                                        | 41 |

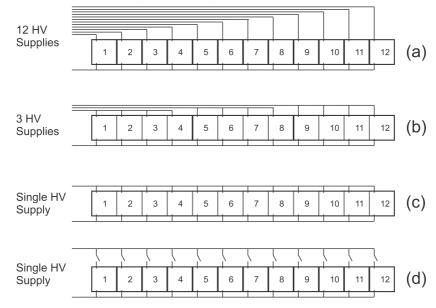

| Figure 22: Possible HV distribution schemes for barrel staves.                                       | 43 |

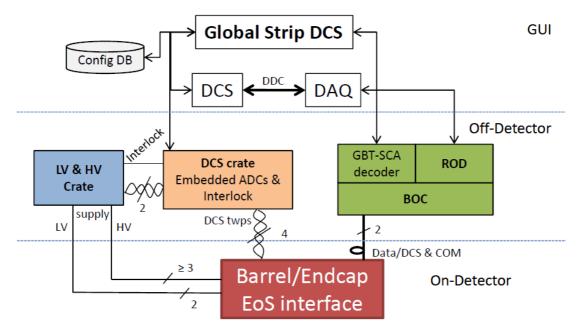

| Figure 23: Proposed strip DCS architecture.                                                          |    |

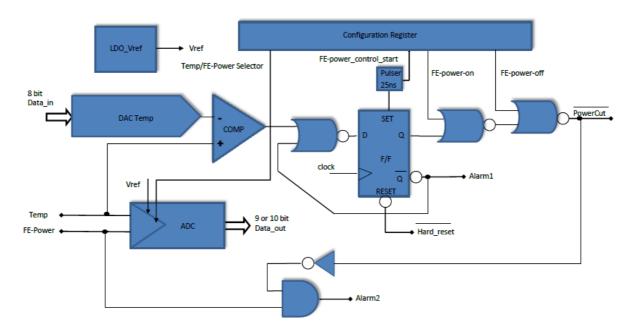

| Figure 24: Proposal of a DCS block diagram to be integrated into the HCC for temperature monitorin   | ıg |

| and FE power control                                                                                 | 47 |

| Figure 25: DCS inputs integrated into the readout chain                                              | 49 |

|                                                                                                      |    |

# List of Tables

| Table 1: Number of modules and channels for the strip detector assuming double-sided modules           |    |

|--------------------------------------------------------------------------------------------------------|----|

| everywhere and the layout of Figure 1.                                                                 | 7  |

| Table 2: Total ionising dose in kGy for 3000 fb-1 integrated luminosity at various radii               | 7  |

| Table 3: ABC130 Packet Format                                                                          |    |

| Table 4: ABC130 Packet Header                                                                          |    |

| Table 5: ABC130 Packet Payload, R3 packet                                                              | 13 |

| Table 6: ABC130 Packet Payload, 1BC-L1 Packet                                                          |    |

| Table 7: ABC130 Packet Payload, 3BC-L1 Packet                                                          | 14 |

| Table 8: ABC130 Packet Payload, 32 bits register packet.                                               | 14 |

| Table 9: Control signals                                                                               | 14 |

| Table 10: Bi-Directional Data Communication Signals                                                    |    |

| Table 11: Stave Side HCC Inputs and Outputs                                                            |    |

| Table 12: Hybrid Side HCC Inputs and Outputs                                                           |    |

| Table 13: GBT Generated Signals                                                                        |    |

| Table 14: Hybrid Side HCC Common Signals                                                               |    |

| Table 15: Expected RIA for fibres from the tracker to USA15                                            | 32 |

| Table 16 Electrical power consumption for the components of one VTRx.                                  |    |

| Table 17: Power consumption per readout hybrid and per stave for short and long strips                 |    |

| Table 18: Details of the currents at different stages, assuming 80% efficiency for the 12 V-1.3 V DC   |    |

| converters and a 1.2 V Vddd and Vdda delivered by LDOs in ABC130                                       |    |

| Table 19: Details of the currents at different stages for serial powering, assuming 85% efficiency for |    |

| main shunt regulator and a 1.2 V Vddd and Vdda.                                                        |    |

| Table 20: Number of power "lines" with their voltage and current for the two powering options          |    |

| Table 21: Total cross-section of copper needed for different schemes of HV and LV powering             | 44 |

|                                                                                                        |    |

#### 1. Introduction

The basic concept of the front-end system of the Silicon Strip Detector in the Atlas Detector upgraded for the HL-LHC is being elaborated and proposed. The readout electronics of this new detector is based on front-end chips (ABC130), Hybrid Controller chips (HCC) and End of Stave Controller chips (EOSC). This document defines the basic functionality of the front-end system and of the different ASICs.

For purposes of this document, a "link" refers to either an optical transmission line (i.e. a single fibre) or an electrical transmission line using LVDS complementary specifications (i.e. a single pair of electrical conductors). "Data" will refer to the information flow heading off detector, i.e. ABC130 to HCC to EOSC to off-detector. "Trigger, Timing and Control" (TTC) will refer to information flow heading to the detector even though some commands will include data such as register settings, i.e. to EOSC to HCC to ABC130. "DCS" refers to the Detector Slow Control, which includes the local monitoring, the interlock devices, and the related signal transmissions. A "module" refers to the readout unit associated with a single sensor wafer. A "hybrid" refers to an interconnect circuit that has multiple ABC130s. There are one or two hybrids per module.

#### 2. Overview of the readout system

#### 2.1 Detector Lay-out

This section gives a short overview of the organisation of the detector in order to determine the maximum size of modules and staves in terms of channels and later the maximum data rate needed for the readout and the number of TTC links needed.

Figure 1 shows the basic features of the LOI layout [1] used for the basis of the readout organization of the strip barrel and end-cap designs. The layout may evolve between now and the completion of the Technical Design Report if simulations point to possible performance improvements. The general aspects of the readout architecture described here will still be applicable as the layout evolves, however, some details (e.g. exact number of bits in certain fields) may require change. Such changes to layout may also affect the power and material budgets, which will need to be included in the analysis of the resulting changes in performance.

The barrel is organized into staves. While mechanically each stave typically runs from some +z coordinate to a symmetrical –z coordinate, for purposes of the readout architecture, we will use the term "stave" to refer to the half of that full stave since the readout will be collected at both extreme ends. Likewise, the present layout calls for double sided staves, so care must be taken when discussing attributes such as channel count, power, etc. to be clear about a single side or both sides of a stave. The strip modules can host up to 20 256-channel ABC130 chips per side and a stave can gather up to 13 modules of 10 ABC130 each (long strips) or 13 modules of 20 ABC130 each (short strips) per side. These numbers are per side and must be doubled for a double-sided stave.

The end-cap is organized into disks and each disk into wedges often referred to as petals. For purposes of the readout architecture, these petals are equivalent to the barrel staves and each petal will gather data from all its modules at its outer radius as the equivalent of end of stave.

In the following, the worst case in terms of number of channels will be considered (i.e. only double-sided staves will be considered).

**Figure 1:** LOI Layout – one quadrant. There are 4 barrel layers and 6 disks of pixels, 3 barrel layers of short strips, 2 full barrel layers and one stub layer of long strips and 7 disks of strips per end.

#### 2.2 Tracker parameters and environmental conditions

This section summarises the main parameters of the tracker from a system point of view (number of channels, total power, etc.) as well as the environmental conditions (radiation level, working temperature).

#### 2.2.1 Number of channels for the strips detector

Assuming double-sided modules are used everywhere, and using the layout shown in Figure 1, the total number of modules of 256-channel ABC130s and the total number of channels are given in Table 1. These numbers are subject to change with the layout but the order of magnitude is certainly correct.

## 2.2.2 Working temperature

For a safe long-term operation of the tracker it is necessary that the sensors and electronics have good contact to the cooling pipe at -35°C. This requires a system for thermal monitoring with high granularity. Some of the signals in that system will be used for hardware interlock. Due to various heat sources within the thermal enclosure the average ambient temperature will be several degrees above this, but the exact amount is difficult to estimate now.

#### 2.2.3 Radiation levels

The upgraded detector will run until a 3000 fb<sup>-1</sup> integrated luminosity will be obtained. The detector and its electronics have to be designed for twice as much, i.e. 6000 fb<sup>-1</sup>. The TID will be about a factor 10 higher than that of the current detector and is given in Table 2.

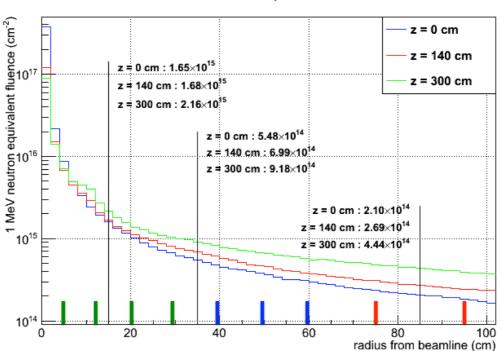

The amount of highly energetic neutrons, very damaging for the sensors, has to be reduced. This will be done by adding some moderating material that will have the effect of decreasing the neutron energy. Figure 2 gives the expected fluence in the tracker volume. At the level of

|                                     | Layer                                                  | Type of Strip               | F Segmentaion<br>per Stave | Number of Single<br>Sided Modules in<br>Z per Half Barrel | Number of 256-<br>channel ABC130<br>per Module | Number of<br>ABC130 per Half<br>Stave |

|-------------------------------------|--------------------------------------------------------|-----------------------------|----------------------------|-----------------------------------------------------------|------------------------------------------------|---------------------------------------|

|                                     | 0                                                      | Short Strips                | 28                         | 2x13                                                      | 20                                             | 2x260                                 |

| <b>D</b>                            | 1                                                      | Short Strips                | 36                         | 2x13                                                      | 20                                             | 2x260                                 |

| Barrel                              | 2                                                      | Short Strips                | 44                         | 2x13                                                      | 20                                             | 2x260                                 |

|                                     | 3                                                      | Long Strips                 | 56                         | 2x13                                                      | 10                                             | 2x130                                 |

|                                     | Stub                                                   | Long Strips                 | 64                         | 2x2                                                       | 10                                             | 2x20                                  |

|                                     | 4                                                      | Long Strips                 | 72                         | 2x13                                                      | 10                                             | 2x130                                 |

|                                     |                                                        | Total nur                   | nber of staves for t       | he Barrel                                                 |                                                | 300                                   |

|                                     |                                                        | Total number of             | ABC130 ICs for t           | he Entire Barrel                                          |                                                | 184'000                               |

|                                     | Disk                                                   | F Segmentation<br>per Petal | Ring                       | Hybrid                                                    | Number of 256-<br>channel ABC130<br>per Hybrid | Number of<br>ABC130 per<br>Petal-Ring |

|                                     | 0-6                                                    | 32                          | 0                          | HO                                                        | 8                                              | g                                     |

|                                     | All Disks Identical                                    |                             | -                          | H1                                                        | 9                                              |                                       |

|                                     |                                                        |                             |                            | H2                                                        | 9                                              |                                       |

|                                     |                                                        |                             |                            | НЗ                                                        | 10                                             | 36                                    |

|                                     |                                                        |                             | 1                          | H4                                                        | 11                                             |                                       |

| End-cap                             |                                                        |                             |                            | H5                                                        | 11                                             | 22                                    |

| -                                   |                                                        |                             | 2                          | H6                                                        | 12                                             | 12                                    |

|                                     |                                                        |                             | 3                          | H7                                                        | 7                                              | 14                                    |

|                                     |                                                        |                             | 4                          | H8                                                        | 8                                              | 16                                    |

|                                     |                                                        |                             | 5                          | Н9                                                        | 9                                              | 18                                    |

|                                     |                                                        | 236                         |                            |                                                           |                                                |                                       |

|                                     |                                                        | 7'552                       |                            |                                                           |                                                |                                       |

|                                     |                                                        | 52'864                      |                            |                                                           |                                                |                                       |

|                                     |                                                        | 105'728                     |                            |                                                           |                                                |                                       |

|                                     | Total Number of ABC130 ICs for the Barrel and End-caps |                             |                            |                                                           |                                                |                                       |

| Total Number of Channels of Readout |                                                        |                             |                            |                                                           |                                                | 74'170'368                            |

the pixel detector, more than  $10^{15}$  n.cm<sup>-2</sup> are expected while for the strip detector it is in the range  $10^{14} - 10^{15}$  n.cm<sup>-2</sup>.

**Table 1:** Number of modules and channels for the strip detector assuming double-sided modules everywhere and the layout of Figure 1 but subject to change for other layouts.

| Radius in cm | Dose in kGy |

|--------------|-------------|

| 5.05         | 4500        |

| 12.25        | 1000        |

| 29.9         | 300         |

| 43.9         | 200         |

| 51.4         | 100         |

| 108          | 40          |

Table 2: Total ionising dose in kGy for 3000 fb-1 integrated luminosity at various radii.

# 1 MeV neutron equivalent fluence

**Figure 2:** 1 MeV neutron equivalent fluence for 3000 fb-1 integrated luminosity. Vertical bars show the positions of the pixel layers (green), short strips (blue) and long strips (red) for the original straw-man layout. [1]

#### 2.3 Readout units for the strip detector

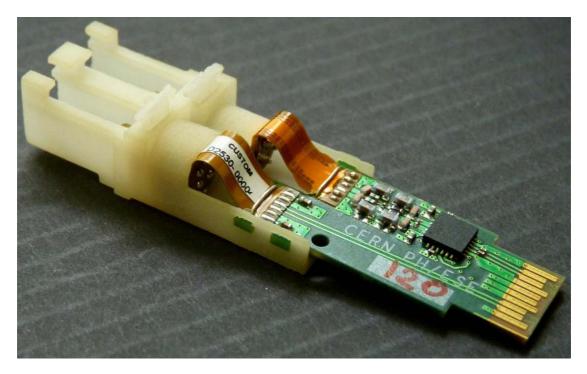

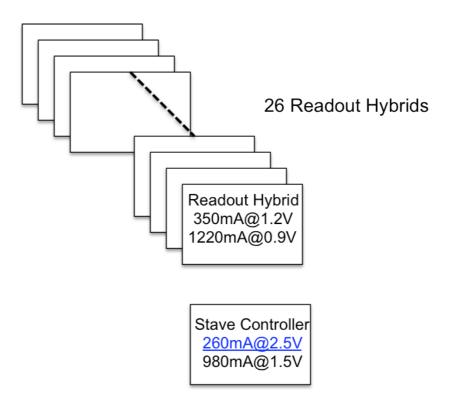

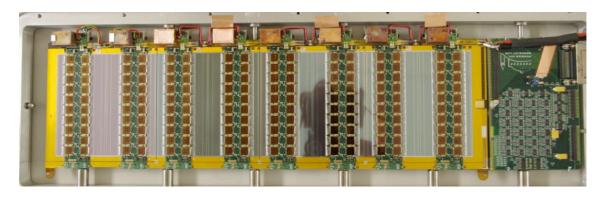

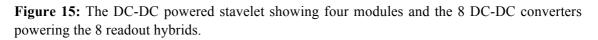

The detector is organised in staves with up to 26 modules counting both sides (a module being a 10x10 cm<sup>2</sup> sensor wafer and its front-end electronics). Each stave is made of two layers in order to have a double-sided detector. These two layers will be treated separately from the readout point of view. It is assumed that the data of a single-sided stave will be collected by the end of stave (or service) controllers (EOSC) located at each end of the staves; each EOSC will readout up to 13 modules. Each module on the stave has either one (long strips) or two (short strips) readout hybrids. In both cases, the readout unit is the readout hybrid. The readout hybrid will host 10 ABC130 for both short strips and long strips and a so-called hybrid controller chip (HCC) that will gather the data of the hybrid and transmit them to the EOSC. The short-strip hybrid will readout two rows of 2.5-cm long strips and the long-strip hybrid will readout two rows of 5-cm long strips. In both cases the two rows of strips are interleave connected into the input channels of the ABC130 chips. It could in addition contain specific power components (Serial Power Protection or DC-DC converters).

Figure 3 is a sketch of a single-sided stave of short strips.

**Figure 3:** Sketch of a single-sided stave of short strips. Up to 13 modules are readout by 26 hybrids of ten 256-channel ABC130s each. An end of stave controller gathers the data from all module hybrids and interfaces to the off-detector electronics. Each hybrid houses a hybrid controller that interfaces the ABC130s to the EOSC. The DCS data can either be sent together with the readout data or be sent on a dedicated link.

### 2.4 Rough estimate of the total power in the strip detector

Recent detailed estimations have shown that the maximum power consumption per channel should be of the order of 0.7 mW. Assuming a pessimistic 1 mW per channel for the strip ABC130 and a 1.2 V working Vdd, one needs to feed about 210 mA per 256-channel ABC130. Hence, one has to feed a total current (for the barrel and both end-caps) of order 61 kA to the front-end. The power dissipated in the front-end will depend on the powering scheme but will in any case include some inefficiency because of the embedded regulators or converters. 80% efficiency would lead to about 93 kW dissipated in the tracker volume, while 70% efficiency would lead to about 106 kW. These numbers show the extreme attention one has to pay to the design of the different power components so that their efficiency is maintained as high as possible.

The current SCT and TRT detectors are fed with about 12 kA through the available cables. Assuming that the amount of services cannot be increased (not because it is planned to reuse existing service but because the volume available will not dramatically change), the powering scheme to be used must limit the amount of current to be fed at that level. That is about 1/5<sup>th</sup> of the current needed by the front-end electronics. Either at least a factor of 5 reduction by DC-DC conversion or a serial powering scheme of at least 5 modules could be used.

### 2.5 Interface to the trigger DAQ

The requirement document [2] remains valid although some parameters could change because of the difficulties that could be encountered by the level-1 trigger system to maintain a maximum 200 kHz L1A rate.

### 2.5.1 Level-1 Accept rate

This document assumes that the level-1 (L1A) rate will not exceed 200 kHz. This is doubled from the original 100 kHz specification when the Upgrade R&D first started. Simulations run so far indicate that the architecture described in this document will handle the resulting data rates. Some discussion includes descriptions of alternate solutions should more bandwidth be required. For example, see section 3.4 covering end of stave electronics. These solutions require either doubling the number of links or exploiting more advanced IC technologies. The former would represent increases in material and power; the latter is certainly possible as our R&D work continues.

#### 2.5.2 Possible tracking as part of the Level-1 trigger

In case that the calorimeter and muon level-1 trigger electronics cannot efficiently select events and that some information from the tracker is needed to either improve the cuts on muon momentum or to improve the electron isolation process, two main roads are possible:

- 1. Add specific trigger layers to produce a self-seeded track trigger;

- 2. Use the higher rate Level-0 trigger (L0) coupled with region of interest information to extract a limited amount of track data in time to be used by the Level-1 trigger logic thus reducing its rate to a manageable level. This scheme is called Regional Readout Request (R3).

The second solution is certainly the less difficult one to be implemented, as it only requires some extra buffer management in the front-end electronics and some reasonable increase of bandwidth for the data readout.

Although at the time this document is written it is not clear whether or not such a "track trigger" feature is necessary, it is deemed safer to specify and design the system assuming the R3 scheme is used. In addition some extra circuitry will be provided in the first ABC130 iteration to allow possible testing of the self-seeded track trigger. See section 3.1.3.

### 2.5.3 Regional Readout Request (R3) scheme

It is assumed that a very first level trigger called L0 is generated at a maximum rate of 500 kHz together with region of interest (RoI) addresses. It is assumed that there are up to 4 RoI's per L0 and that the total of the ROI's for one L0 covers about 10% of the detector. The L0 signal must be received within a fixed, but programmable to a maximum  $6.4 \,\mu$ s, latency (currently 6.4 us) after the event of interest such that the data for the event is at the end of the pipeline (named L0 Buffer). Upon receipt of the L0 signal, event data along with the associated BCID are transferred into a Random Access Memory, the second stage buffer named the R3L1 Buffer, at an address specified by a local 8 bit L0 counter (L0ID). A matching counter is maintained by the central trigger system, the value of which is sent as part of RoI and L1A readout requests to select the event address in the R3L1 Buffer. These memory access reads are non destructive so that data may be requested multiple times. Occasionally an RoI will overlap with a L1A selection. Those ABC130s that are part of a RoI will send the associated data to the hybrid controller (which will send them to the end of stave controller, etc.) so that the off-detector triggering process can continue. After some time (undefined yet but less than 256µs) the level-1 trigger electronics will issue a decision. There is no need for having a fixed latency between an event occurrence and the availability of RoI or L1A signals. The L1A rate is expected to be lower than 200kHz. The L1A signal together with the associated L0ID is sent to the front-end. The ABC130s will extract the corresponding data and send them to the readout system. The data in the second stage buffer, which can hold 256 events, will be overwritten when the buffer is full, the oldest L0ID first. For a L0 trigger rate of 500 kHz, the buffer will hold data for up to roughly 500 µs, but the exact maximum will depend upon the L0 rate. It is also assumed that the ROI and L1A signals will arrive with time ordered L0IDs. Therefore, the ABC130s will also delete from their second stage buffer the data corresponding to preceding L0IDs. Figure 4 gives a rough sketch of the R3 Scheme and it is discussed in more detail in section 3.1.

**Figure 4:** Block diagram of the ABC130 readout part with the R3 capability. All the ABC130s receive L0A and extract the corresponding data from the pipeline (L0\_Buffer). These data are stored together with a L0ID in the R3L1\_Buffer. Only those in the region of interest receive R3 signal and send immediately the corresponding data. L1A comes later together with the L0ID to which it refers. This L0ID is used to select data in the R3L1\_Buffer and send them. The TTC system requires higher bandwidth for the R3 Scheme as some additional information is to be sent together with L0A and L1A.

## 2.6 Policy for fighting SEU

The amount of energetic hadrons (more than 20 MeV) susceptible of generating SEU is very high and hence SEUs will appear everywhere. The following policy will be adopted:

- The static registers holding thresholds, masks, etc. will be implemented with a triple redundant logic;

- The "physics data" themselves will not be protected, as a SEU acts as a small excess of noise and because the data do not stay for a long time in the ABC130s;

- Level-1 identifier (L1ID) and Bunch Crossing identifier (BCID) will not be protected as they stay a very short time in the front-end. In addition an error is very easily detected in the off-detector electronics and the policy of periodic resets will be maintained (There is a Bunch counter reset every 90 µs and an Event counter reset at a relatively high frequency [order of Hz] which can be used to reconfigure the front-end.);

- Special care will have to be taken for the transmission to the front-end of the trigger and control (TTC), as the receiving PIN diodes are very sensitive to SEU. Specific measurements have shown that SEU can generate multi-bit errors in high-speed links [3]. Adapted error detection and correction must be implemented.

# 3. Data readout chain

As shown in Figure 3, the readout chain consists of readout hybrids housing the ABC130 and the HCC ASICs, a service bus to the end of stave control board, the latter housing an EOSC and a DCS ASIC as well as the opto-electrical devices interfacing to two optical fibres. In addition, in case a self-seeding track trigger is to be implemented, a concentrator ASIC would be needed. The following sections will describe the different ASICs and their interfaces.

#### 3.1 Front-end ASIC: ABC130

This chip provides all functions required for processing the signals from 256 strips of a silicon strip detector employing the binary readout architecture. The simplified block diagram of the hookup of the chip is shown in Figure 4. The main functional blocks are: front-end, input register, pipeline, derandomizing buffer, data compression logic blocks, command decoder, readout logic, threshold & calibration control, power regulation.

The architecture chosen for the ABC130 allows a multi-trigger data flow control retaining the Beam Crossing synchronous pipeline transfer signal (L0 here) from previous ABC versions and a new asynchronous Regional Readout Request (R3 here) and a second level asynchronous data readout intended for a global readout (L1 here).

The ABC130 contains 256 analogue preamplifier-shapers followed by discriminators with individual threshold trimming capabilities. The shaping time should allow 0.75 fC pulse detection separated by 75 ns. The binary outputs of the discriminators (data) are sampled at the bunch crossing clocking rate (BC) and stored for 6.4 µs in the "pipeline" or L0\_Buffer memory bank. At the reception of a L0 signal, the data in the memory that were stored at some fixed latency time before the L0 signal are extracted from the pipeline and transferred to the derandomizing buffer (R3L1\_Buffer) and stored. The data corresponding to 3 consecutive time slots are transferred for each L0 and form an event. There is enough room in the R3L1\_Buffer for 256 events. After 256 events are stored, new events overwrite the R3L1\_Buffer content.

At reception of a "R3" signal (R3s\_L1 output from the HCC), which carries a L0 identifier, the event that has the same L0 number is extracted from the R3L1\_Buffer and processed through the R3 Data Compression Logic block that performs zero suppression and cluster identification. The same happens at the reception of a "L1" signal (R3s\_L1 output from the HCC), but the event with the correct L0 number is processed through the L1 Data Compression Logic block.

The R3 and L1 Data Compression Logic (DCL) differ in their algorithms to detect clusters and perform cluster identification, however, both algorithms will apply the same hit criteria as the present ATLAS-SCT chip, the ABCD. That is, a hit channel can be defined by the time sequence X1X, 01X, or XXX where 0 is no-hit, 1 is hit and X is don't care and the three bits represent the discriminator result for three consecutive beam crossings centered on the trigger BC. Which criteria to use is set by the configuration register. The information extracted from the 2 DCLs is different, for example the R3 unit is limited to identify 4 clusters at maximum and produces one data packet. The L1 unit is not limited in the number of clusters and number of packets produced.

The information extracted from the DCL contains a channel number to identify each cluster and bits that represent the cluster shape. The data are stored in local FIFOs to be transferred at the proper time to the Readout block.

The Readout block contains a packet builder and a fast serializer. The packet builder gets the data from either:

- The adjacent chip (external)

- The R3\_DCL (internal)

- The L1\_DCL (internal)

- The internal registers (internal)

The priority of data is set according to this order. The data from an adjacent chip is already formatted and is simply transferred to the serializer. The data from the R3\_DCL, L1\_DCL or from internal registers are formatted in packets of 60 bits as shown in Table 3. As

soon as there is some formatted data packet ready, it is sent out through the fast serializer running at the RCLK clock rate (nominal 160 MHz).

There are four types of data packets, each having the same header format but slightly different payload formats as shown in Table 5 through Table 8. The R3 packet can contain up to four clusters and only reports the address of the first channel of each cluster. Only the single beam crossing of the L0 trigger is considered for this cluster finding. This abbreviated data with only one packet per R3 and at most four clusters is used to minimize transmission time for data to be included in the L1 trigger decision.

The 1BC-L1 packet can contain up to three clusters with the address of the first hit channel in the cluster and a bit pattern showing hit or no-hit in the three adjacent channels. Clusters of more than 4 channels are reported as multiple clusters and multiple packets per event are transmitted if necessary.

The 3BC-L1 packet contains only one cluster of four consecutive channels with three beam crossings per channel reported (the trigger BC plus one BC before and one after the trigger). Sufficient packets will be sent to report all found clusters. This packet format, selectable by the configuration register, is intended for commissioning or timing studies.

The payload of the Internal Register packet is just the 32-bit contents of the register.

|   | 26 bits Header | 34 bits Payload |

|---|----------------|-----------------|

| ĺ | 60 bits pa     | acket size      |

| Table 3: A | ABC130 Packet Format |

|------------|----------------------|

|------------|----------------------|

| Start Bit | ChipID | ТҮР | L0ID | BCID |

|-----------|--------|-----|------|------|

| 1         | 5      | 4   | 8    | 8    |

Table 4: ABC130 Packet Header

| Address | Address | Address | Address | OvF | Stop<br>Bit |

|---------|---------|---------|---------|-----|-------------|

| 8       | 8       | 8       | 8       | 1   | 1           |

Table 5: ABC130 Packet Payload, R3 packet

| Address | Hit | Address | Hit | Address | Hit | Stop<br>Bit |

|---------|-----|---------|-----|---------|-----|-------------|

| 8       | 3   | 8       | 3   | 8       | 3   | 1           |

Table 6: ABC130 Packet Payload, 1BC-L1 Packet

| Address | Hit | Hit | Hit | Hit | TBD | End<br>Bit |

|---------|-----|-----|-----|-----|-----|------------|

| 8       | 3   | 3   | 3   | 3   | 13  | 1          |

Table 7: ABC130 Packet Payload, 3BC-L1 Packet

| Data | TBD | End Bit |

|------|-----|---------|

| 32   | 1   | 1       |

Table 8: ABC130 Packet Payload, 32 bits register packet.

The time interval between transmissions of packets out of a single chip is variable and depends on the arrival time of the R3 or L1 signals and on the presence of packets in adjacent chips. A "Xoff" mechanism prevents the adjacent chip to transmit its packet to the current chip if the latter is not ready to accept it (internal FIFO Full).

There are two sets of bi-directional signals for communicating with adjacent chips, XOFF1 and DATA\_1 for communication with the chip to one side and XOFF2 and DATA\_2 for communication with the chip on the other side. This is to allow data to flow in either direction through the chain of ABC130s on a hybrid. All of the data can flow in one direction or the other or the ABC130s can be split into two chains or loops on the hybrid. The latter case can be used to eliminate a malfunctioning chip from the readout by breaking the chain at that point.

The ABC130 ASICs contains addressable registers to configure:

- The analogue front-end (bias and threshold)

- The channels calibration

- The channels mask

- The prioritization of packets and other configurations of the digital functions

- Select which set of bi-directional lines to use for data readout

- The DCS local features

All the registers can be read-back, also during data taking: the registers data packets are treated with the lowest priority. One specific register can be set so that it is read with the highest priority: this register may contain the critical error flags.

#### **3.1.1 Control Signals**

The control signals are given in Table 9.

| Name       | Туре   | Description                                                          |  |

|------------|--------|----------------------------------------------------------------------|--|

| In1- In256 | Analog | Preamplifier Inputs from silicon strip sensors                       |  |

| RCLK       | LVDS   | (80 or ) 160 MHz Clock input primarily intended for Data             |  |

| BC         | LVDS   | Beam Crossing Clock at 40MHz                                         |  |

| L0_CMD     | LVDS   | L0 Synchronous Trigger with BC falling edge, CMD with BC rising edge |  |

| R3s_L1     | LVDS   | R3L0ID with BC falling edge, L1L0ID with BC rising edge              |  |

Table 9: Control signals

**RCLK** - The data clock determines the rate at which data is clocked out of the chip. It is expected that this will be either 80 or 160 MHz. This clock will be delayed by an arbitrary amount with respect to the incoming stave clock to accommodate a hybrid wide phase shift to align sensor signals with the BC.

**BC** - The 40 MHz LHC beam crossing clock.

- L0\_CMD This 80 Mb/s signal is comprised of two time-multiplexed 40 Mb/s components:

- L0 A one bit BC synchronous signal signaling that data in the pipeline has been identified as an event to store into the R3L1\_Buffer. The resultant action is to transfer the data from the pipeline into the R3L1\_Buffer with a BC tag and a L0 tag generated internally.

**CMD** - The input for the Command Decoder that will be processing commands. Commands can be received independently of the status of the triggering system and during physics data taking. The normal length of a command is 53 bits.

R3s\_L1 - This 80 Mb/s signal is comprised of two time-multiplexed 40 Mb/s components:

**R3L0ID** - The Regional Readout Request (R3L0ID) signal is delivered on one phase of the BC clock and has two fields and a length of 11 bits: 3 bits act as start bit pattern (101), followed by 8 bits containing the L0ID identifier of the event to retrieve in the L1Buffer.

**L1L0ID** - The second trigger level (L1L0ID) signal is delivered on one phase of the BC clock and has two fields and a length of 11 bits: 3 bits act as start bit pattern (110), followed by 8 bits containing the L0ID identifier of the event to retrieve in the R3L1 Buffer.

## **3.1.2 Bi-Directional Signals**

Table 10 lists the bi-directional signals of the ABC130.

| Name   | Туре | Description                           |

|--------|------|---------------------------------------|

| XOFF1  | LVDS | Chip to Chip Data Packet Flow control |

| XOFF2  | LVDS | Chip to Chip Data Packet Flow control |

| DATA_1 | LVDS | Chip to Chip Data Packet Input/Output |

| DATA_2 | LVDS | Chip to Chip Data Packet Input/Output |

**Table 10:** Bi-Directional Data Communication Signals

**XOFF1/XOFF2** - When true, the chip is not ready to receive data from the adjacent chip in the serial chain. XOFF will be controlled by a priority encoder set by the chip position number as well as data in the queue in the local ASIC. Can be set as input or output.

DATA\_1/DATA\_2 - Serialized Data passing from chip to chip. Can be set as input or output.

# 3.1.3 Fast Cluster block for self-seeded track tracker

The Fast Cluster block is a prototyping block included on the ABC130 that, when enabled, will provide prompt, beam clock synchronous, cluster position data to an external device that will correlate clusters between tracking layers and select high PT coincidences to send to the Trigger processor. The fast cluster algorithm assumes that the ABC130 is bonded with the two rows of strips interleaved as described in section 2.3. Strip data is provided from the input of the ABC130 pipeline after the mask register. This allows noisy channels to be masked off to avoid having a cluster registered at most or all beam crossings from improperly functional channels. Data from these banks is processed independently in parallel.

Its block diagram is shown on Figure 5 and its main feature are:

- Parallel processing of cluster finding from each 128 strip bank

- One dedicated High Speed Serialized output per bank of 128 strips (2 per ABC130)

- Rejection of Low momentum tracks by limiting the number of hit strips in a cluster to 2

- Half Strip Precision achieved by listing how many strips were hit (1 or 2)

- Fixed Delay from BC Serialized data will be sent with a fixed delay from cluster's BC

- 5 BC delay with a 160 MHz Serializing Clock

- 2 BC, dead timeless, delay with a 640 MHz clock

- Power (when enabled) with Drivers

- Logic + Serializer 4.5 mW + 9 mW for two Drivers @160 MHz

- Logic + Serializer 5.5 mW + 12 mW for two Drivers + 3 mW for receiver @ 640 MHz

Figure 5: Block diagram of the fast cluster blocks in ABC130

Fresh strip data is loaded into the pipeline at the rising edge of the BC. This data (odd channels to one cluster finder and even channels to the other) is evaluated using combinatorial logic in 6 ns. The Cluster Finder output consists of two 8-bit words for each bank, where the 8-bit word represents a 7-bit address plus one bit to indicate the number of hit strips (1 or 2). Given the 80  $\mu$ m strip pitch for the upgraded strip detector this will effectively yield a phi resolution of 40  $\mu$ m. In the event that fewer than two clusters are found, the output 8 bits are set to an illegal combination, all 1's. The BC bar latch will record the Cluster Finder data if the serializer is ready. The serializer will start on the next rising edge of the BC clock. When serialized at 640Mbps, the 16 bits of cluster finder data will be lost. Figure 6 shows a timing diagram of this process. In the event of more than two qualifying clusters in a single BC, the

two clusters nearest the edges of the bank (lowest and highest addresses) are sent out and clusters between these are lost.

A special framing mode is provided when a bit is set by the command decoder. In this mode the serializer outputs send 8 1's followed by 8 zeros to establish the data frame according to the local clocks. The correlator will need a corresponding mode to establish a proper read delay for each incoming channel.

**Figure 6:** Cluster finding Logic Data synchronization. Data Latched at the serializer input (bottom trace) is immediately sent out serially.

#### 3.2 Hybrid controller ASIC: HCC

The HCC is the interface between the stave service bus (stave side) and the front-end ASICs on the strip detector hybrids (hybrid side). Figure 3 depicts its position in the readout architecture. Each HCC in the inner barrel will service one half of a sensor for inner layer short strips, 2560 strips with ten 256-channel FEIC's (ABC130), and one whole sensor or module for outer layer sensors with long strips.

Five, hard wired, hybrid address bits (A0-4) uniquely identify each HCC on the stave; these may be set by bonding or by an Efuse. The latter requires two additional ASIC mask steps. All active control and data lines use a form of Low Voltage Differential Signalling (LVDS like). The stave side control lines are HCC input signals generated by the EOSC (GBT Elinks) and bussed to all stave resident HCC's (up to 26). Stave side control signals are received, interpreted and redistributed as required to the hybrid by the HCC. The hybrid side control signals are bussed to all ABC130s and each has a single differential pair termination. The HCC differential signal drivers will be current programmable in 8 steps to allow the circuit to be adapted to load and receiver conditions in various implementations. Two independent control signals are time multiplexed (phase encoded) onto each differential I/O pair at 80 Mbps such that each control signal has a 40 Mbps update rate. The HCC interprets stave side commands downloaded on the L0\_CMD input and responds to a subset of these for its setup and response to monitoring requests. Unrecognized commands are sent through to the hybrid side. The HCC monitors the stave side (40 MHz) BC Stave signal generated and sent on a

single differential pair to all HCC chips on the stave by the GBT at the EOSC. The HCC will implement a radiation tolerant PLL that will synthesize binary weighted frequencies up to 640 MHz for use in providing programmable phase hybrid clocks for data and the ABC130 pipeline clocking in time with the arrival of interaction particles at the location of the hybrid sensor. The HCC will provide both a Beam Clock (BC) and a separate hybrid level data readout clock (DRC) with a common phased offset remotely programmed into the HCC. The HCC clocks may be turned off to operate the FEIC's in a power reduction mode. Hard reset is made possible by holding the R3\_L1 in the true state for 16 or more BCs. Each HCC sends data back to the GBT receiver via a private data path. Two drivers in the HCC are connected in parallel to one hybrid specific data line on the stave (26 data pairs/stave). The current drive for each driver is selectable in 8 steps in the range 0 - 3 mA. For low latency operation the data rate can be as high as 320 Mbps corresponding to receiving data from both hybrid data loops at 160 Mbps. When the hybrids are serially powered the operating voltages between the EOSC and the HCC will vary by position, a difference of up to 30 V may be realized depending on the length of the serial chain. AC coupled stave side communications will be necessary. The AC coupled HCC receivers will use internal hysteresis to ensure memory of the last state on the AC coupled side. This idea has been successfully prototyped in the SPI chip, a Serial Power Control ASIC [4]. The HCC data drivers sending data to the GBT will also need AC coupling capacitors. Since the GBT has no provision for hysteresis, area balanced communication techniques will be required to prevent common mode drift of the AC coupled GBT receivers. Either scrambling or the more constrained encoding such as 8b/10b will be used. It is foreseen to make the implementation of the coding technique selectable using a bit in a status register. The HCC can report errors/reduce power (interlock) and by request output monitor data.

## 3.2.1 Description of the HCC I/Os

Figure 7 shows a block diagram of the HCC with the different I/Os.

### **Stave Side HCC Inputs and Outputs:**

The signal connections between the HCC and the stave bus are listed in Table 11.

| Name                | Description                                                                   | Speed   |

|---------------------|-------------------------------------------------------------------------------|---------|

| BC_Stave            | 40 MHz GBT Clock                                                              | 40 MHz  |

| L0_CMD              | Time multiplexed beam synchronous L0 and CMD,                                 | 80 Mbps |

|                     | each @ 40 Mbps. CMD uses inverted logic.                                      |         |

| R3_L1               | Time multiplexed Regional Readout Request (R3)                                | 80Mbps  |

|                     | and second Level Trigger (L1), each @ 40 Mbps.                                |         |

|                     | L1 uses inverted logic.                                                       |         |

| HARD RESET          | ARD RESET Holding R3_L1 True for 16BC initiates a HARD                        |         |

|                     | RESET.                                                                        |         |

| Data_I and Data_II  | <b><i>I</i> and Data_II</b> Stave side point to point output DATA from each   |         |

|                     | HCC to the EOSC. Data I and Data II are separately                            | Mbps    |

|                     | programmable output drivers that may be                                       |         |

|                     | individually enabled.                                                         |         |

| Address Bits (A0–4) | <i>Idress Bits (A0–4)</i> Hard wired static address bits to uniquely identify |         |

|                     | each hybrid on the Stave bus. These may be fuse                               |         |

|                     | programmable.                                                                 |         |

# Hybrid Side Inputs and Outputs:

All the signals are shared among all ABC130 chips on the hybrid and are listed in Table 12. All signals are sent with the same clock phase as the BC by the HCC. Control signals will be encoded on both edges of the 40 MHz local clock.

| Name   | Description                                                   | Speed         |

|--------|---------------------------------------------------------------|---------------|

| BC     | Beam crossing clock phase shifted by programming the HCC,     | 40 MHz        |

|        | used for BCID counting / Pipeline clocking / Phase marker for |               |

|        | L0_CMD and R3s_L1 signals to ABC130s                          |               |

| L0_CMD | Independent CMD and L0 streams each at 40 Mbps                | 80 Mbps       |

| R3s_L1 | Independent L1 and R3s streams each at 40 Mbps                | 80 Mbps       |

| DRC    | Clock generated with an HCC programmed phase                  | 80 or 160 MHz |

Table 12:

Hybrid Side HCC Inputs and Outputs

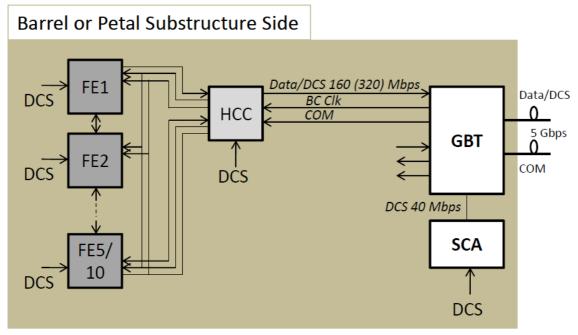

Figure 7: Block diagram of the Hybrid Controller Chip (HCC) and related I/O lines.

# 3.2.2 GBT Generated Signals

The input signals to the HCC, which are generated by the GBT at the EOS, are listed in Table 13. Note that the GBT generated signals L0\_CMD and R3\_L1 are each made up of two multiplexed signals, L0 with CMD and R3 with L1 with one issued on the rising edge of the BC\_Stave clock and the other on the falling edge. The second portions of each, CMD and L1, will be issued with inverted logic in order to maximize the number of transitions during idle periods so that the AC coupled logic will preserve the proper logic levels. When no L0\_CMD or no R3\_L1 signals are being sent their inputs will follow the BC clock. The HCC will eliminate the inversion prior to sending CMD to the hybrid side.

| Name          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Speed or size |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| BC_Stave      | BC clock. Base clock for all HCC and ABC130 operations. A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40 MHz        |

|               | PLL in the HCC will provide a 640 MHz internal clock to be used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

|               | for phasing the clock going to the Hybrid in steps of 1.6 ns.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

| L0_CMD        | <b><i>MD</i></b> L0 (40 Mbps): Issued on the rising edge of BC_Stave. L0 is a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

|               | beam synchronous signal sent a fixed number of BCs following                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |

|               | the event of interest such that the data from that event are at the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |

|               | end of the ABC130 pipeline when the L0 is issued. L0, sent to all                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

|               | ABC130s in parallel, is used by the ABC130 logic to signal the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |

|               | transfer of data from the pipeline to the current LOID memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

|               | address and increment the L0ID memory address counter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |

|               | CMD (40 Mbps): Issued on the falling edge of BC_Stave with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |