# The ATLAS Insertable B-Layer (IBL) Project

J. Bilbao de Mendizabal on behalf of the ATLAS collaboration

University of Geneva, Switzerland

#### Abstract

Preparing for the high luminosity LHC phase, the ATLAS experiment will upgrade its Pixel Detector with the installation of a new pixel layer. The new sub detector, called the Insertable B-layer (IBL), will be installed during the LHC first shut down in 2013-2014, in between the innermost current pixel layer and the beampipe.

To cope with the high radiation and pixel occupancy due to the proximity to the interaction point, a new read-out chip FE-I4 and two different silicon sensor technologies, planar and 3D have been developed. Furthermore, the physics performance should be improved through the reduction of pixel size and a new mechanical support using lightweight staves.

Two pre-series staves were made in order to qualify the assembly procedure, the loaded module electrical integrity and the read-out chain before going into production.

31

32

33

Keywords: ATLAS, Pixel Detector, 3D, IBL, FE-I4, Stave

## 1. The ATLAS Insertable B-Layer

### 1.1. The ATLAS Pixel Detector

The ATLAS detector [1], an experiment at the CERN Large <sup>34</sup> Hadron Collider (LHC), is a general purpose particle detector <sup>35</sup> designed to explore new frontiers of particle physics. It is com- <sup>36</sup> posed of several subdetectors assuring globally the particle re- <sup>37</sup> construction and identification, making the ATLAS experiment sensitive to a wide range of signatures.

The innermost part of the detector assuring the particle tracking, operational since 2009 with a recorded integrated luminosity of 27 fb<sup>-1</sup>, is composed by several subsystems with different detector technologies. Closest to the interaction point, three pixel layers assure a high  $P_T$  resolution and vertex reconstruction (Pixel Detector [2]), which is essential to cope with the high pileup at LHC (<  $\mu$  >=19 pileup event/bunch cross at  $\sqrt{s} = 8$  TeV).

After successful operation in the last three years, the LHC machine will be upgraded during the 2013-2014 long shutdown to increase the instantaneous luminosity and the collision energy to  $\sqrt{s} = 14$  TeV. To ensure the long term physics performance coping with a high occupancy environment and pileup, a detector upgrade will be necessary [3].

#### 23 1.2. The Insertable B-Layer

The Insertable B-Layer pixel detector will be the fourth layer added to the present Pixel Detector between a new beam pipe and the current inner Pixel Detector layer (B-layer). The <sup>38</sup> present beam pipe will be replaced by a smaller one, with an <sup>39</sup> inner radius of R=23.5 mm, allowing for the installation of the <sup>40</sup> IBL at an average radius of 34 mm and an envelope of only 9 <sup>41</sup> mm [4].

Preprint submitted to Nuclear Instruments and Methods A

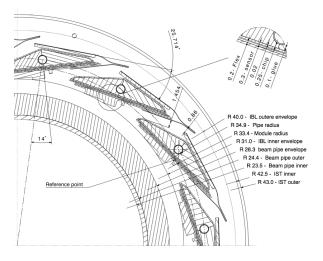

The IBL is composed of 14 staves (64 cm long 2 cm wide and tilted in  $\phi$  at 14 degrees) equipped with 32 front-end chips per stave and sensors facing the beam pipe ( $\eta$  coverage of 2.5). Hermeticity in the transaxial (R- $\phi$ ) plane is ensured by about 20% stave-to-stave overlap as is shown in Figure 1. The overall design has been targeted to reduce the material budget of the total IBL package down to 1.6% X<sub>0</sub>, minimizing the particle scattering at low radius.

Figure 1: Transversal cut of the IBL detector and beam pipe.

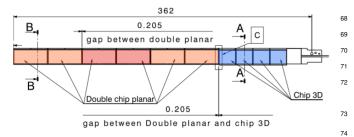

Each IBL stave will be populated with planar pixel technology (12 double chip modules) in the central region and 3D technology (4+4 single chip modules) in the outer one (forward region).

December 14, 2012

Figure 2: Half stave layout and sensor technologies. Module powering sectors <sup>75</sup> are indicated with different colors. The stave being fully symmetric, one side is <sup>76</sup> not represented 77

#### 43 2. The IBL readout and sensor technologies

#### 44 2.1. New FrontEnd FE-I4

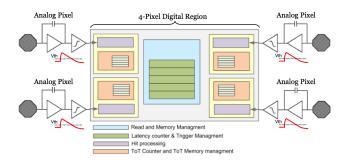

The new IBL front-end (FE) readout FE-I4 has been designed in 130 nm CMOS technology, with an active area of up to 90% [5] (compared to <75% on the current pixel FE, FE-I3[6]). The FE-I4 readout chip, with a total size of 20.2x18.8 mm<sup>2</sup> (5 times larger than the FE-I3), consists of 26880 pixel cells organized in a matrix of 80 columns (50  $\mu$ m pitch) by 336 rows (250  $\mu$ m pitch)

An analog pre-amplification before the pixel comparator, designed for low currents (double stage), reduces the activity in the digital region (Figure 3).

Figure 3: Schematic of the analog and digital 4 pixel matrix functionality

The design relies on a local memory-based architecture (2x2  $_{q_4}$ 55 pixel blocks) with 5 ToT<sup>1</sup> memories (4 bits) per pixel, to ac- $\frac{34}{95}$ 56 commodate the higher hit rate while keeping the busy/waiting 96 57 inefficiency in the order of  $10^{-3}$ . The hits are locally stored <sub>97</sub> 58 with a maximum latency of 5 bunch crosses, and only sent if 98 59 an L1 trigger matches the latency of the event, reducing the DC 99 60 bus traffic and consequently the power consumption which is<sub>100</sub> 61 targeted to 200 mW/cm<sup>2</sup>. 62 101

Beyond the large size and high rate capacity, the FE-I4 radiation tolerance has been improved by implementing thin oxide core transistors, showing efficiencies > 87% after 200 MRad irradiation [5]. To reduce the material budget, the thinned FE is attached to a support wafer (glass substrate) before electroplating underbump metallization and micro-bump deposition. After hybridization the support wafer is removed, leading to a FE thickness of only 150  $\mu$ m.

#### 2.2. Sensors technology

78

79

80

81

82

Silicon 3D n-in-p (processed with double-side technique by FBK<sup>2</sup> and CNM<sup>3</sup>) and Planar n+-in-n (processed by CiS<sup>4</sup>, as for the present Pixel Detector) were retained for the IBL, motivated by their high efficiency after irradiation to NIEL<sup>5</sup> of  $5 \times 10^{15} n_{eq}/cm^2$  and schedule constraints.

Both technologies are assembled with FE-I4 readout chips. The planar sensor layout allows for double chip configuration thanks to its high yield while the 3D sensors are connected to one single chip.

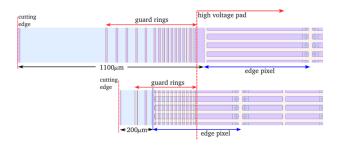

Double chip sensors are fabricated at CiS with a reduced thickness with respect to the current Pixel Detector of 200  $\mu$ m, limiting the material budget while reducing the depletion voltage especially after bulk radiation.

In the back plane, a central pad assures the high voltage distribution surrounded by an optimized arrangement of thirteen guard rings avoiding edge effects [7]. The pixel length in the edge region is two times longer (500  $\mu$ m) and ovelaps with the guard rings in order to maximize the sensitive parts and extend the active region, up to 200  $\mu$ m from the cutting edge (Figure 4).

Figure 4: Planar Pixel sensor edge pixel and guard rings for the current Atlas pixel (top) and new IBL design (bottom)

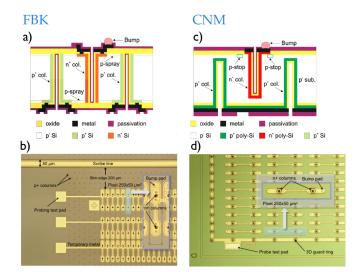

3D sensors produced in FBK and CNM, have micro machined electrodes doped by a thermal diffusion process ( $n^+$  columns on the front side,  $p^+$  from the back side). One of the main differences between both manufacturers is the column depth, full traversing columns (FBK) or double type double face (CNM), as shown in Figure 5.

<sup>67</sup>

<sup>&</sup>lt;sup>1</sup>Time over Threshold, in LHC bunch cross units (25 ns)

$<sup>^2\</sup>mbox{Fondazione}$  Bruno Kessler (FBK), Via Sommarive 18, 38123 Povo di Trento, Italy.

<sup>&</sup>lt;sup>3</sup>Centro Nacional de Microelectronica (CNM-IMB-CSIC), Campus Universidad Autonoma de Barcelona, 08193 Bellaterra (Barcelona), Spain.

<sup>&</sup>lt;sup>4</sup>CiS Forschungsinstitut fur Mikrosensorik und Photovoltaik GmbH, Konrad-Zuse-Strasse 14, 99099 Erfurt, Germany

<sup>&</sup>lt;sup>5</sup>Non ionizing energy loss

Figure 5: Schematic column design for FBK (a) and CNM (c). Details of: pixel, probing pad and edge resistive columns/ guard rings, are shown for FBK (b) and CNM (d)

<sup>102</sup> The FBK slim edge fence consists of 4 resistive rows of  $p^+$ <sup>103</sup> columns that stop the depletions, as opposed to the CNM  $n^+$ <sup>104</sup> 3D guard ring approach. Despite the sensors' differences, both <sup>105</sup> designs will be used indistinguishably. The ~70  $\mu$ m electrode <sup>106</sup> separation makes a low operation voltage (<160 V after irradia-<sup>107</sup> tion) possible, while reducing the drift distance allowing for an <sup>108</sup> efficient tracking at high  $\eta$ .

### 109 2.3. Module qualification after irradiation

With a maximum expected integrated luminosity of 500 fb<sup>-1</sup>, the radiation tolerance of the IBL is of special concern. Both planar and 3D modules have been irradiated and qualified up to doses of 750 MRad and 250 MRad, with a 25 MeV proton beam at KIT<sup>6</sup> and neutron reactors at TRIGA<sup>7</sup> respectively.

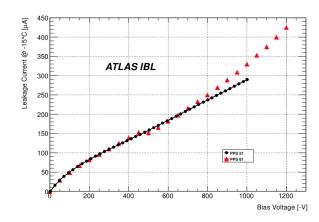

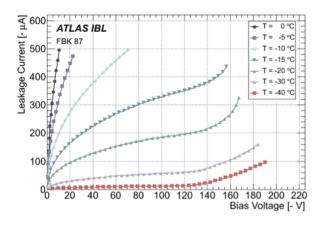

The I-V curves for each of the IBL sensor technologies after irradiation are shown in Figures 6 and 7. Post-irradiated samples show an ohmic behavior, as expected from heavily radiation damaged material, but no breakdown is observed. Due to their ohmic behavior, thermal contact to the cooling surface is of critical importance to avoid thermal runaway, specially at high voltage operation.

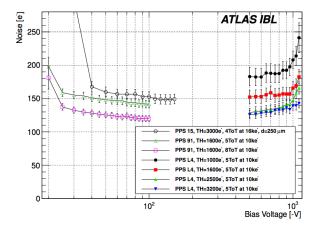

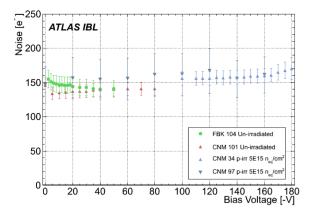

Figure 8 and 9 show the equivalent noise charge as a function of the bias voltage  $(V_b)$ , for different FE-I4 tunings, showing no significant variation after irradiation, for both technologies, which is needed for low threshold operation. After irradiation at 1 kV bias voltage, the planar sensors operate in the quasiavalanche regime, showing an increase in the sensor noise.

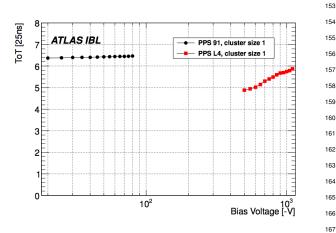

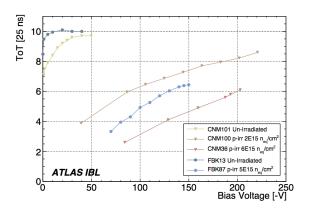

<sup>129</sup> Samples were exposed to a <sup>90</sup>Sr source, measuring ToT value <sup>130</sup> as a function of the  $V_b$ , shown in Figures 10 and 11. For non-<sup>131</sup> irradiated samples no  $V_b$  dependance is observed after deple-<sup>132</sup> tion. Charge collection after irradiation is of ~90% for planars

128

Figure 6: I-V curves for CiS module at  $-15^{\circ}$ , after irradiation to a fluence of  $6 \times 10^{15} neq/cm^2$  [8]

Figure 7: I-V curves for FBK module at different temperatures, after irradiation to a fluence of  $5 \times 10^{15} neq/cm^2$  [8]

Figure 8: Noise as a function of  $V_b$  for CiS modules at different ToT tunings, before and after irradiation [8]

and  $\sim$ 70% for 3D, increasing with the bias voltage as expected due to the charge multiplication at bias being much higher than the depletion voltage.

133

134

135

<sup>&</sup>lt;sup>6</sup>Karlsruhe Institute of Technology, Karlsruhe, Germany

<sup>&</sup>lt;sup>7</sup>TRIGA reactor, Jozef Stefan Institute, Ljubljana, Slovenia

150 Figure 9: Noise as a function of  $V_b$  for FBK and CNM modules at  $-15^o$ , before 151 and after irradiation [8]

Figure 10: ToT charge collection in BC units, using a <sup>90</sup>Sr, of planar sensor<sup>168</sup> before irradiation (PPS 91) and after irradiation to  $5 \times 10^{15} n_{eq}/cm^2$  (PPS L4)<sub>169</sub> as a function of depletion voltage [8] 170

Figure 11: ToT charge collection in BC units, using a <sup>90</sup>Sr, of 3D sensor before<sub>185</sub> irradiation and after irradiation as a function of depletion voltage [8] 186

IBL modules performance has been extensively studied in test-136 beams, understanding and optimizing their operation. Particle 137 tracking accuracy, was measured thanks to an external tracks 138

reconstruction from the EUDET telescope and hit matching, showing an RMS of only 15  $\mu$ m [8]. Tracking reconstruction for edge pixels and hit efficiency after irradiation, confirms that both technologies have only 200  $\mu$ m inactive area from their 142 edge.

#### 3. Stave assembly process and first prototypes

#### 3.1. Stave assembling

139

140

141

143

144

145

146

147

148

149

152

171

172

173

174

175

176

177

178

179

180

181

182

183

184

187

188

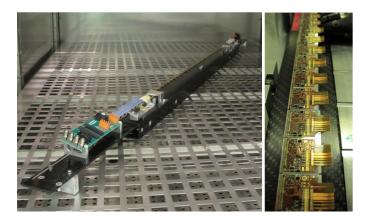

IBL stave components are produced in several ATLAS institutes, and shipped to University of Geneva where the final stave assembly is performed. To ensure good performance, all components follow a strict quality assurance (OA) when received, and all along the module loading, assembly and wire bonding operations. Although 24 staves will be produced, due to the limited reworkability of the components after assembly, the QA is of crucial importance to ensure the best performance of the final IBL detector.

After flex gluing and a connectivity check, the stave and flex assembly is delivered to the Production Center clean rooms. A metrology of the face plate, before and after thermal-cycling<sup>8</sup>, is performed to verify the mechanical integrity before module loading.

Simultaneously, modules from production sites are received and tested with an USBpix setup [9]. The module reception test verifies digital and analog FE response, as well as pixel noise and crosstalk, pointing out any possible damage happened during the shipment. In addition, to fully qualify the modules, an optical inspection is done and an I-V is performed.

The selected modules are loaded onto the stave with a 70  $\mu$ m thermal grease layer and two epoxy glue dots per front-end to hold each module. Each module is electrically connected via the flex wing which is first glued and in the second step wire bonded. Each module is then electrically accessible via temporary PCB and flex savers mounted at the two extremities (Figure 12).

The final assembly is thermally cycled and a metrology survey is performed to check that the mechanical specifications are fulfilled. An electrical test of the full functionality of the stave, similar to the modules reception test, is performed before shipment to CERN, where an extensive burn-in and QA tests will be undertaken before the final integration around the beam pipe.

#### 3.2. Prototype staves: test and results

The behavior of the integrated parts has been studied with the Stave 0-a and Stave 0-b, the first two functional and complete staves. Between the production of the two staves 0, several jigs and components were upgraded fixing potential problems and improving procedures while targeting for the highest production quality.

Although single module operations were well understood, extensive tuning tests and trigger scans have been performed

<sup>&</sup>lt;sup>8</sup>Thermal-cycles performed to the staves consist of 10 cycles from -40° to + 40°, with controlled humidity

on the two staves 0, to characterize their behavior with the new 189 common power scheme and command lines.

Figure 12: Stave 0-a before loading (left) and after loading (right). Non attached wings can be seen on the side of the carbon fiber stave, as well as the stave PCB-saver on the edges, all supported by the stave handling frame 205

191 192 193

190

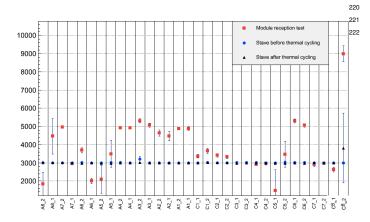

Threshold mean values are shown in Figure 13. Module re-2009 ception test threshold spreads can be explained due to the use<sub>210</sub> of configuration files from production sites, while using differ-211 ent operational temperatures and setups. However, stave results<sup>212</sup> 194 213 were obtained after stave tuning, showing a great FE to FE ho-214 195 mogeneity and low threshold dispersion. 196 215

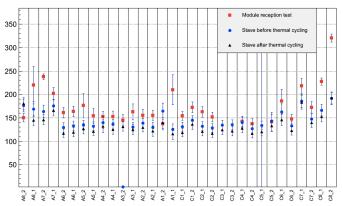

Noise values (Figure 14) remain constant and under IBL spec-216 197 ification for each FE, showing that no damage is done to the<sup>217</sup> 198 modules during production. 199 219

Figure 13: Threshold mean value and dispersion (error bars) of Stave 0-b FE during reception test (squares), after loading before thermal-cycling (circles), after loading after thermal-cycling (triangles)

#### References 200

- [1] ATLAS Collaboration, The ATLAS Experiment at the CERN Large 201 Hadron Collider, JINST 3 S08003 229 (2008) 202

- 203 [2] G. Aad et al., ATLAS Pixel Detector Electronics and Sensors, JINST 3 P07007 (2008) 204

Figure 14: Noise mean value and dispersion (error bars) of Stave 0-b FE during reception test (squares), after loading before thermal-cycling (circles), after loading after thermal-cycling (triangles)

- [3] M. Garcia-Sciveres, ATLAS Experiment Pixel Detector Upgrades, arXiv:1109.4662 [physics.ins-det]. Proceedings of Meeting of the Division of Particles and Fields of the American Physical Society, DFF 2011, September 2011

- ATLAS collaboration, Insertable B-layer technical design report, CERN-[4] LHCC-2010-013, http://cdsweb.cern.ch/record/1291633

- M. Garcia-Sciveres et al., The FE-I4 Pixel Readout Integrated Circuit, [5] Journal of Instrumentation vol. 7 (2012) 1748-0221

- Ivan Peric et al., The FEI3 Readout Chip for the ATLAS Pixel Detector, [6] Nucl.Instr. and Meth. A, 565(1):178187, 2006

- [7] C. Goessling, R. Klingenberg, D. Muenstermann, and T. Wittig, Evaluation of the breakdown behaviour of ATLAS silicon pixel sensors after partial guard-ring removal, Nucl. Instrum. Meth. A624 (2010) 410413

- The ATLAS IBL collaboration, Prototype ATLAS IBL modules using the [8] FE-I4A front-end readout chip, 2012 INST 7 P11010

- [9] Malte Backhaus. Diploma thesis: Development of an USB-based test system for the FE-I3 readout chips of the ATLAS pixel detector and Noise Occupancy Studies. Universitat Bonn - Physikalisches Institut, 2009

206

207

208