TECHNISCHE UNIVERSITÄT GRAZ Kopernikusgasse 24 A-8010 Graz Dekanal der Fakullät für Elektrotechnik und Informationstechnik

# DOCTORAL THESIS

# Design and Characterization of an Analogue Amplifier for the Readout of Micro-Pattern Gaseous Detectors

Gerd Trampitsch

Graz University of Technology Institut für Elektronik

University Supervisors: Em. Univ.-Prof. Dr. Hans Leopold Univ.-Prof. Dr. Wolfgang Pribyl

> CERN Supervisor: Dr. Luciano Musa

Geneva, February 2007

25.000

Universitätsbibliothek

-2. Okt. 2007

der Technischen Universität Graz

This work has been carried out through the Austrian Doctoral Student Program at the European Organization for Nuclear Research, CERN, Geneva, Switzerland

# **Abstract**

This doctorate deals with the development of integrated analog preamplifiers for the readout of micro pattern gaseous detectors. Because of the small detector signals the noise performance of the readout electronics is of greatest significance. The design of analog preamplifiers constitutes a trade-off between bandwidth, noise, power consumption, radiation hardness and chip area.

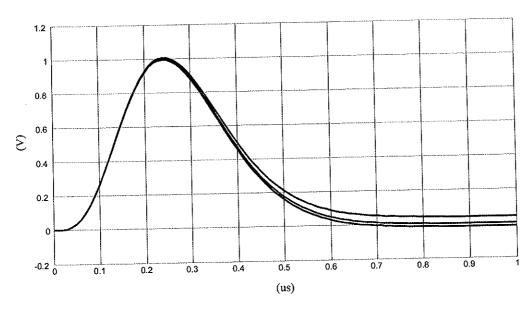

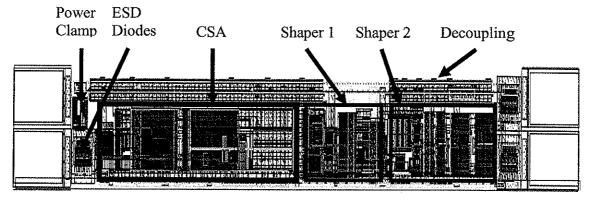

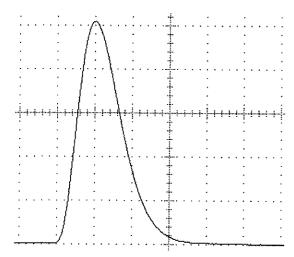

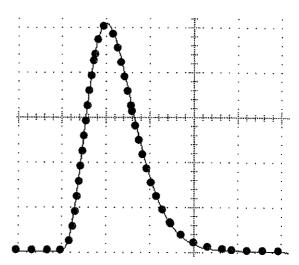

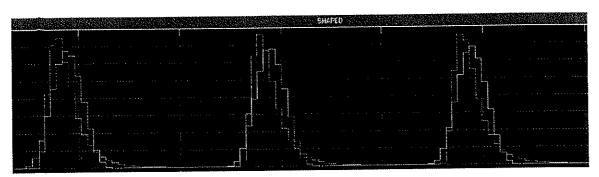

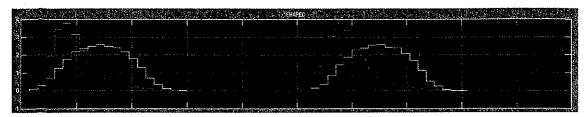

A prototype IC consisting of 12 channels was produced in a 0.13  $\mu m$  CMOS technology. Each channel is comprised of a single ended preamplifier followed by a fully differential shaping amplifier that produces a 4<sup>th</sup> order semi Gaussian pulse. Channels with different peaking time, conversion gain and preamplifier architectures were implemented. Among these a novel rail to rail preamplifier architecture for low voltage operation.

Part of the thesis work was the design of a printed circuit test board and the characterization of the prototype ICs. The measurements show very good correlation with the simulated values and the circuit fulfills all specifications.

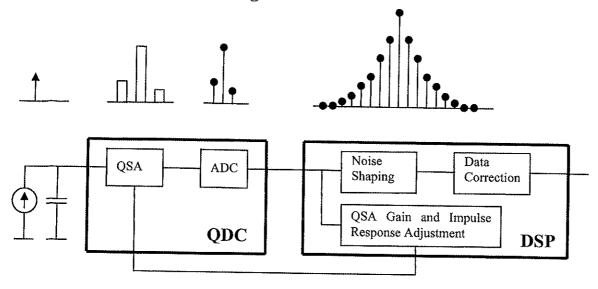

Current state-of-the-art detector readout systems consist of sensitive analogue circuitry, ADCs and high-speed digital processing whereas the low-noise preamplifiers are still kept separately. New R&D is therefore needed to develop cost-effective single chip solutions with a higher degree of integration and programmability and reduction of the power consumption.

Starting from the prototype IC, a programmable 16 channel preamplifier/shaping amplifier was designed as analog front-end for a general purpose charge readout chip.

II

# Kurzfassung

Die vorliegende Doktorarbeit beschäftigt sich mit der Entwicklung von analogen integrierten CMOS Vorverstärkern für die Auslese von Micro Pattern Gasdetektoren. Aufgrund der kleinen Detektorsignale ist das Rauschverhalten der Ausleseelektronik von besonderer Bedeutung. Der Entwurf eines analogen Vorverstärkers stellt einen Trade-Off zwischen Bandbreite, Rauschen, Leistungsverbrauch, Strahlungshärte und Chipfläche dar.

Ein Prototypchip mit 12 Kanälen wurde in einer 0,13 µm CMOS Technologie gefertigt. Die einzelnen Kanäle bestehen aus einem Vorverstärker (single ended) gefolgt von einem differentiellen Pulsformer vierter Ordnung. Die Kanäle unterscheiden sich in Verstärkungsfaktor und Anstiegszeit der Impulsantwort. Verschiedene Vorverstärkerarchitekturen wurden implementiert. Darunter eine neuartige Rail to Rail Architektur für niedrige Versorgungsspannungen.

Teil der Arbeit ist die Charakterisierung des Prototyp-ICs und das Design eines Testboards. Die Messergebnisse zeigen gute Übereinstimmung mit den simulierten Werten, und der Prototyp-IC erfüllt alle gestellten Anforderungen.

State of the Art Auslesesysteme bestehen aus hoch sensitiven analogen Vorverstärkern mit nachfolgenden digitalen Signalprozessoren, wie in Kapitel eins beschrieben. Die gemeinsame Integration von Analog- und Digitalelektronik ermöglicht die Implementierung von schnellen, kosteneffizienten Auslesesystemen mit einer hohen Anzahl von Kanälen bei gleichzeitig kleinem Leistungsverbrauch.

Ausgehend von dem Prototypchip wurde ein programmierbarer Chip mit 16 Kanälen als analoges Frontend für einen General Purpose Charge Readout Chip entwickelt.

# **Summary and Outlook**

This doctorate is within the framework of the R&D activities of the Electronics Design (ED) group at CERN Physics (PH) Department and is carried out under the supervision of Dr. Luciano Musa (CERN) and Univ.-Prof. Dr. Hans Leopold (Graz University of Technology).

The next generation of experiments in hadron physics must be able to measure and identify interesting rare reaction products amongst a very high background of non-interesting events. The high luminosity and multiplicities that will be provided by new facilities at CERN, GSI and BNL, require development of detector techniques based on large area, high granularity and high speed.

Gaseous detectors have been widely used in the field of high energy physics up to now. Features like cost efficiency, fast signals, good energy and spatial resolution make them indispensable for modern detector systems like the Large Hadron Collider (LHC) experiments. Over the last decades many different particle multiplication methodologies have been developed. The use of Multi Wire Proportional Chambers (MWPC) for particle multiplication is still state of the art. An example is the ALICE (A Large Ion Collider Experiment) Time Projection Chamber (TPC) at CERN. Modern lithography and etching technologies triggered the development of Micro Pattern Gaseous Detectors (MPGD). These are high granularity detectors with small distances between anode and cathode. GEM (Gas Electron Multiplier) and MICROMEGAS (MICRO MEsh GAseous Structures) are two examples of these new MPGD.

Small signals generated by detectors are amplified by means of highly sensitive low noise analog circuitry. Current state-of-the-art readout systems consist of analogue preamplifiers and high-speed digital signal processing whereas the low-noise preamplifiers are still kept separately.

This thesis focuses on the design of analog front-end electronics and consists of the following main steps:

- Research on analog front-end electronics for detector readout

- Feasibility study of a shaping filter in the discrete time domain

- o Feasibility study of a charge sampling circuit

- O Studies on the analog front-end for a general purpose charge readout chip

- o Studies on a programmable PreAmplifier and Shaping Amplifier (PASA)

- Development of a PASA prototype in a 0.13 µm CMOS technology

- O Specification of the algorithms to be implemented by means of simulation based experimental data

- Development of Matlab and Spice models for the functional verification of the circuit

- Circuit design (schematic and layout)

- o Low power optimization of the various circuits elements

- o Test of the circuit

- Design of a programmable PASA in a 0.13 μm CMOS technology

The demand of high granularity, high speed, low cost and low-power electronics calls for a close integration of analogue and digital circuits. Therefore, a major research challenge is to integrate high-speed digital electronics with low-noise analogue electronics in a single chip. R&D is needed to develop a cost-efficient single chip solution with higher degree of integration and programmability. This new IC, a General Purpose Charge Readout Chip, has to be very flexible in order to be able to cover as many different applications as possible. To cope with this requirement programmability has to be added to the analog signal processor which results in an increase of complexity. Various different architectures were investigated:

## Sensitivity to Input Signals of both Polarities

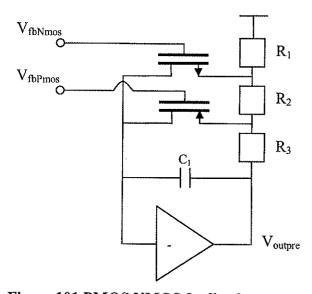

It is absolutely necessary for a general purpose charge readout chip that its analog front-end is capable of processing input signals of both polarities. Therefore a circuit was developed that allows setting the internal DC voltages according to the expected input signal polarity.

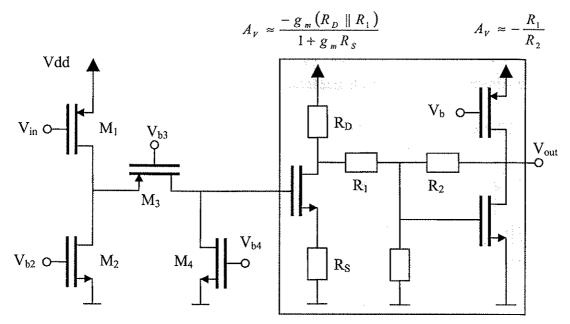

#### **Conversion Gain**

The primary object of changing the conversion gain is to make the circuit suitable to a wide range of detectors. It is mandatory to adapt the gain of the first stage to the expected maximum input charge to avoid saturating the amplifier. Due to process imperfections gain calibration is of great significance to achieve a homogenous behavior of all channels. Therefore a circuit was developed that allows calibrating the conversion gain.

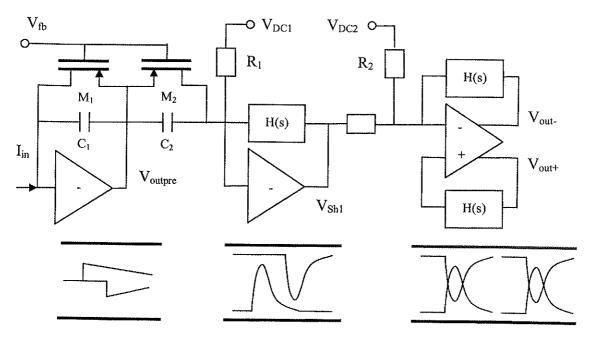

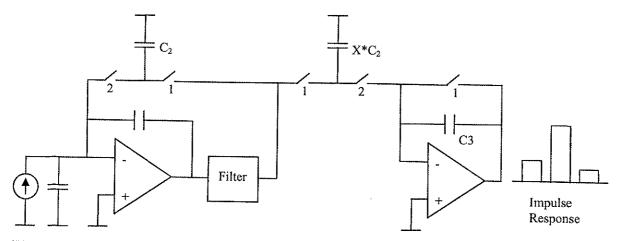

#### **Peaking Time**

The choice of the correct peaking time is a trade off between several factors like noise, pulse pile-up, time resolution and charge collection time. There is no doubt that different applications have the need of different and constant peaking times over all channels. Modifying the peaking time changes the cut off frequency of the shaping filter that can be realized by an active RC-filter or a GmC filter. The RC-filter profits from higher linearity and the GmC approach promises a wider tuning range of the cut off frequency. At this point, we should not neglect that if one considers the shaping amplifier as an anti-aliasing filter, accurate shaping can also be performed by the digital processor.

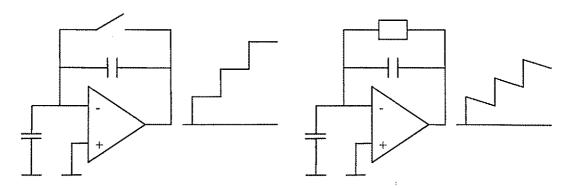

#### Feasibility Study of a Shaping Filter in the discrete Time Domain

A switched capacitor filter would allow very accurate shaping. The filter's frequency behavior is mainly determined by the ratio of capacitors and the clock frequency which could be varied according to the desired shaping time. Unfortunately this approach suffers from the demand for a high clock frequency, especially at short shaping times. A switched capacitor circuit is by definition a sampled data system that has to be preceded by an antialiasing filter that would additionally increase the complexity and also the power

consumption. Filtering in the discrete time domain can also be performed by the digital processor.

## Resistance of Feedback Resistor

The demand for low noise pushes the value of the discharging resistor into the mega ohm region. To realise a highly ohmic path a transistor that is biased in weak inversion or operates in the linear region is used. The feedback resistance can be modified by changing the biasing conditions of the feedback element. The choice of the feedback resistance is a trade-off between noise performance and possible counting rate.

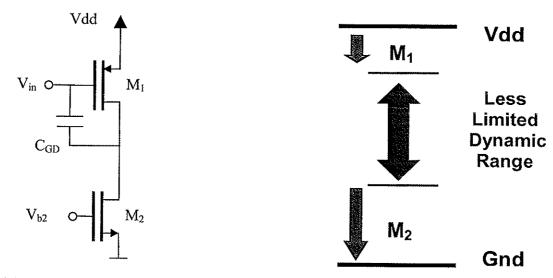

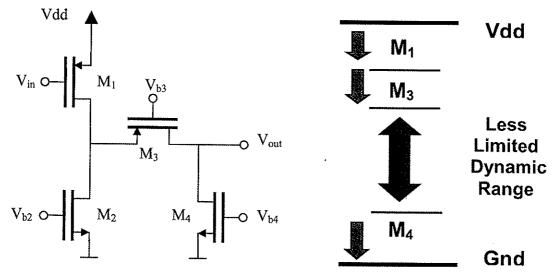

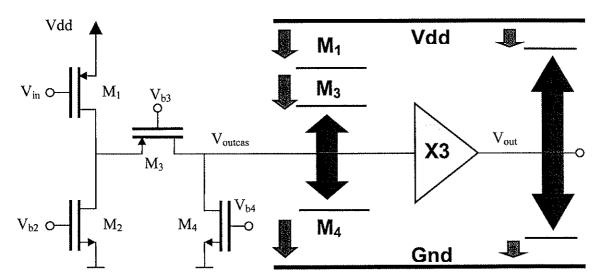

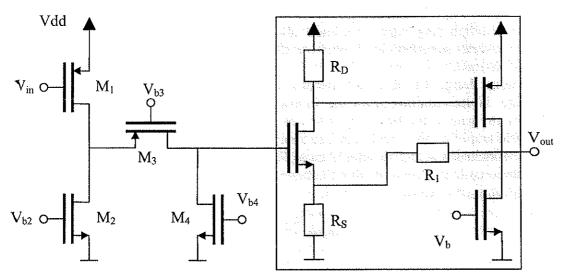

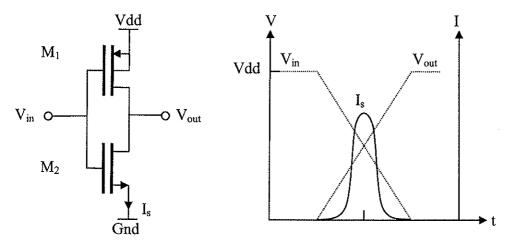

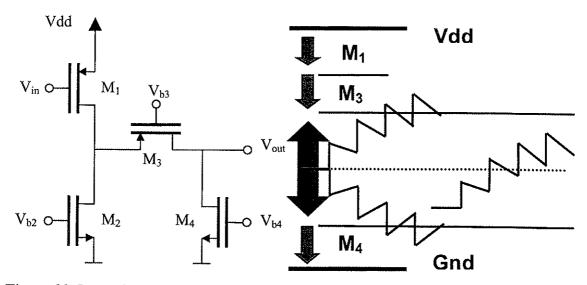

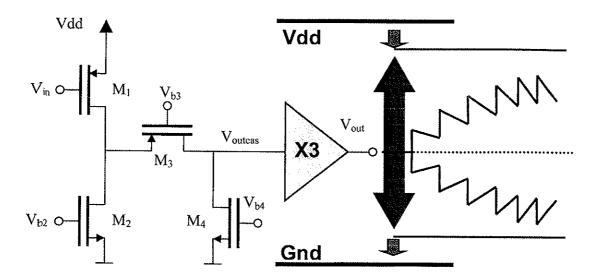

#### Rail to Rail Preamplifier

The classical single ended folded cascade amplifier is widely used in the field of low noise analog electronics for the readout of detectors. Especially at low supply voltages like 1.5 Volt in the 0.13 µm CMOS technology severe restrictions in terms of allowable voltage swings arise. In order to fully exploit the available voltage room, a rail to rail preamplifier was developed. This extra voltage swing increases the circuit's high pulse rate capability.

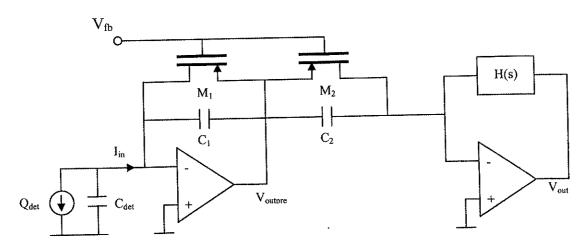

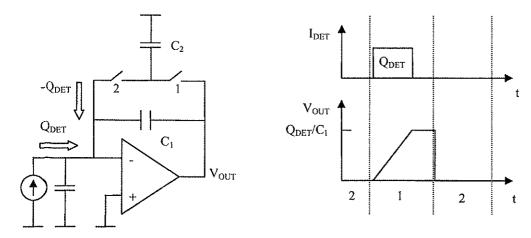

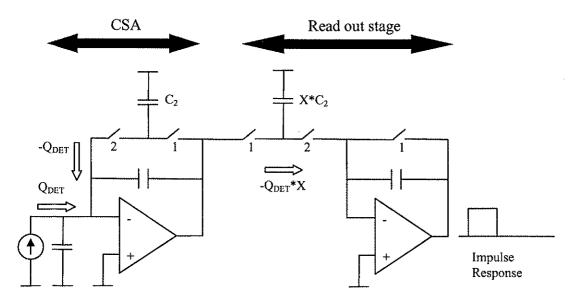

# Feasibility Study of a Charge Sampling Circuit

The charge sampling circuit was developed with the idea of having a circuit which gives information about the charge released by the detector within one clock cycle. Simulations have shown that this approach shows comparable charge resolution. Limitations in terms of time resolution can be overcome by modifying the basic principle.

## **Prototype**

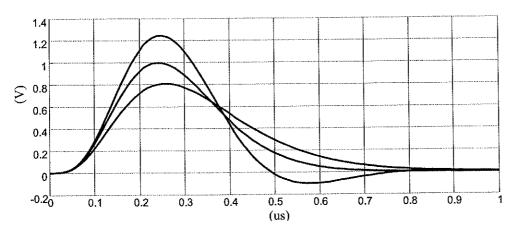

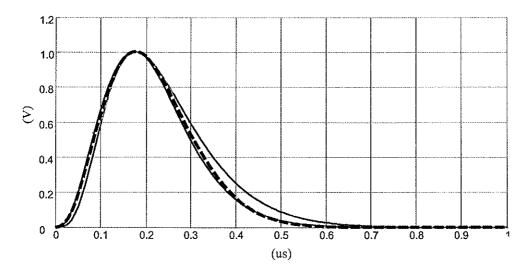

The prototype circuit consists of a single ended charge sensitive amplifier that is followed by a fully differential 4<sup>th</sup> order shaping filter that produces a semi Gaussian pulse with a peaking time of 100 ns. The circuit is designed in a 0.13 µm IBM technology. In order to reduce the complexity and gather some more experience with the new technology a non programmable architecture was chosen. It is sensitive to the opposite signal polarity like the actual preamplifier and has very similar pinout. Small modifications of the ALICE-FECs (Front End Cards) are necessary to use the prototype-IC for the readout e.g. of GEM (Gas Electron Multiplier) detectors.

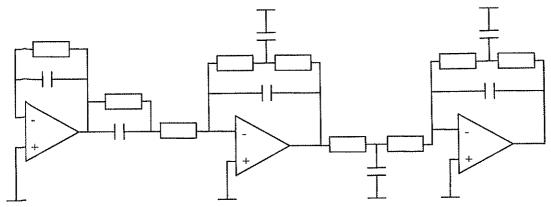

The available silicon area of the prototype run was 3 mm<sup>2</sup>. Due to this limitation only 12 of the previously planned 16 channels were implemented. The prototype circuit is based on 5 different channel-architectures that differ in preamplifier architecture, peaking time and gain:

- 7 channels pmos folded cascode preamplifier, 100 ns shaping amplifier

- 1 channel thin oxide pmos regulated folded cascode preamplifier, 100ns shaping amplifier

- 2 channels pmos input rail to rail preamplifier, 100 ns shaping amplifier

- 1 channel pmos input rail to rail preamplifier, triple gain, 100 ns shaping amplifier

- 1 channel pmos folded cascode preamplifier, 50 ns shaping amplifier

40 dies were fabricated and packaged by an external company.

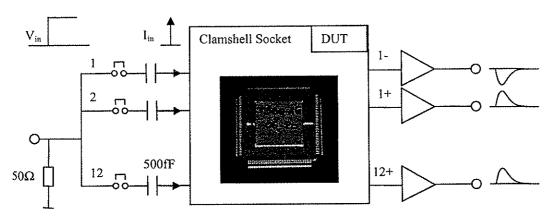

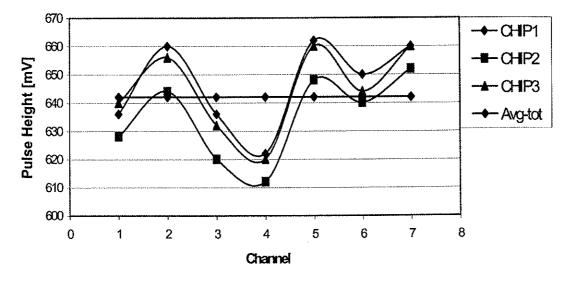

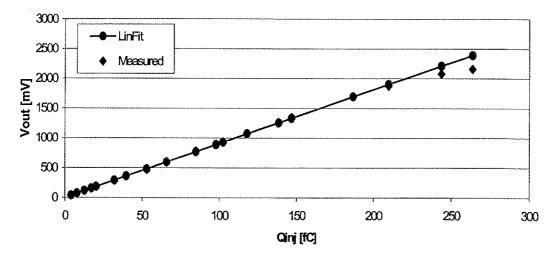

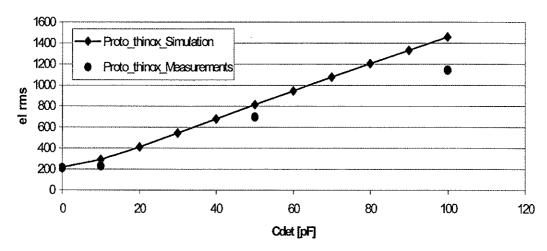

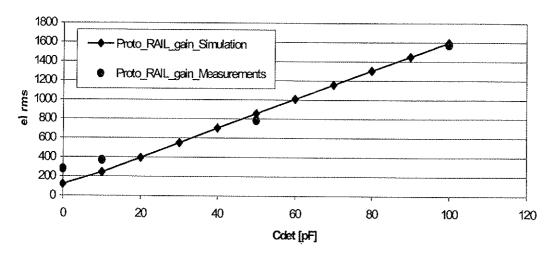

Part of the thesis work has been the design of the test board and the characterization of the prototype circuits. The measurements show very good matching with the simulated values and the circuit fulfills all given specifications.

Starting from the first prototype, the design of a new chip is currently in progress. The submission is planned for the 2<sup>nd</sup> quarter of 2007. The programmable amplifier includes some of the programmability features presented in this thesis and offers a standby mode.

Specifications of the Programmable Charge Amplifier:

Conversion gain: Programmable in the range of 10-30 mV/fC

• Peaking time: Programmable in the range of 30-100 ns

Signal polarity: Programmable for positive and negative pulses

• Power consumption: < 8 mW/channel (<1 mW in standby mode)

• Area: 0.2 mm<sup>2</sup>/channel

• Number of channels 16

Technology CMOS 130 nm

This circuit will be employed for the readout of the Large Prototype TCP of the International Linear Collider in the year 2008. Furthermore, this new circuit will become the analog front-end for the General Purpose Charge Readout Chip described above.

# **Table of Content**

| ABSTRACT                                                                                                                                                                               | ı                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| KURZFASSUNG                                                                                                                                                                            | [[]                        |

| SUMMARY AND OUTLOOK                                                                                                                                                                    | ٧                          |

| TABLE OF CONTENT                                                                                                                                                                       | IX                         |

| CHAPTER 1 INTRODUCTION                                                                                                                                                                 | 1                          |

| 1.1.1 Gaseous Detectors 1.1.1 Time Projection Chamber – TPC 1.1.2 Energy Loss 1.1.3 Multi Wire Proportional Chamber (MWPC) 1.1.4 Alice TPC Readout 1.1.5 Gas Electron Multiplier (GEM) | 1<br>1<br>2<br>3<br>5<br>7 |

| CHAPTER 2 NOISE THEORY                                                                                                                                                                 | 9                          |

| 2.1 Important Noise Sources 2.1.1 Thermal Noise 2.1.2 Shot Noise 2.1.3 Flicker Noise                                                                                                   | <b>9</b><br>9<br>10<br>10  |

| 2.2 MOSFET 2.2.1 MOSFET in Saturation 2.2.2 MOSFET Noise                                                                                                                               | <b>11</b><br>11<br>13      |

| 2.3 Equivalent Noise Charge (ENC)  2.3.1 Parallel Noise  2.3.2 Series Noise  2.3.3 Case Study Triangular Shaping  2.3.4 ENC as a Function of Shaping Time                              | 14<br>15<br>16<br>16<br>18 |

| <ul> <li>2.4 Preamplifier Configurations</li> <li>2.4.1 Pure Capacitive Feedback</li> <li>2.4.2 Current Sensitive Configuration</li> <li>2.4.3 CSA with Discharge Resistor</li> </ul>  | 20<br>20<br>22<br>23       |

| CHAPTER 3 DESIGNING IN A 0.13 JM CMOS PROCESS                                                                                                                                          | 27                         |

| 3.1              | IBM 0.13 μm CMOS                                    | 27               |

|------------------|-----------------------------------------------------|------------------|

| 3.2              | Short Channel Effects                               | •                |

| 3.2.             |                                                     | 28               |

| 3.2.2            |                                                     | 28<br>28         |

| 3.2.3            | Brain Induced Barrier Lowering (DIBL)               | 28               |

| 3.2.4            |                                                     | 29               |

| 3.2.5<br>3.2.6   | TOTAL TOTAL TOTAL TOTAL                             | 29               |

| 3.2.0            | 5 Flicker Noise                                     | 30               |

|                  | Radiation Effects                                   | 31               |

| 3.3.1            |                                                     | 31               |

| 3.3.2            |                                                     | 32               |

| 3.3.3<br>3.3.4   |                                                     | 34               |

| 3.3.5            | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1             | 35               |

|                  | Edyout Teeningues                                   | 35               |

| 3.4              | Conclusions                                         | 36               |

| СНА              | PTER 4 PROTOTYPE CIRCUIT - DESIGN AND LAYOUT        | 37               |

|                  |                                                     | 37               |

| <b>4.1</b> 4.1.1 | Architecture in Use                                 | 37               |

| 4.1.2            |                                                     | 37               |

| 4.1.3            | - v.v mero custoriusson                             | 38               |

|                  |                                                     | 41               |

| 4.2              | CMOS - Folded Cascode Amplifier                     | 44               |

| 4.2.1<br>4.2.2   | DC-Gain                                             | 44               |

| 4.2.3            | Folded Cascode Frequency Response Noise Calculation | 46               |

| 4.2.4            | Trade-Off Noise Performance vs. Output Swing        | 47               |

| 1,2, 1           | Trade-Off Noise Terrormance vs. Output Swing        | 48               |

| 4.3              | Rail to Rail Preamplifier                           | 50               |

| 4.3.1            | Moderate Gain Amplifier                             | 50               |

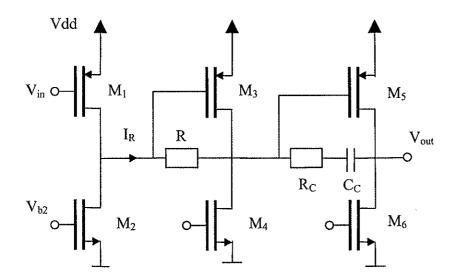

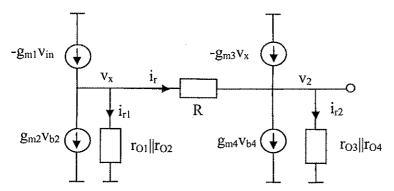

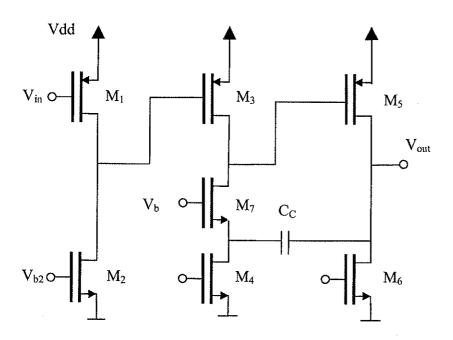

| 4.3.2            | Three Stage Amplifier                               | 52               |

| 4.3.3            | Differential Preamplifier                           | 55               |

| 1.4 N            | Matching the Detector Capacitance                   | 56               |

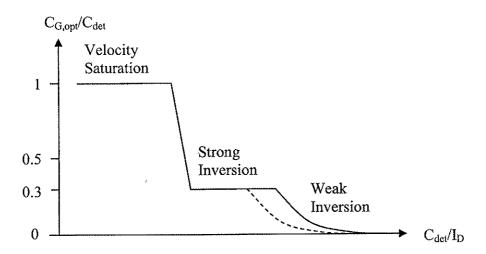

| 4.4.1            | Strong Inversion                                    | 57               |

| 4.4.2            | Weak Inversion                                      | 59               |

| 4.4.3            | Velocity Saturation                                 | 59               |

| 4.4.4            | Optimal Operational Point for the Input Device      | 60               |

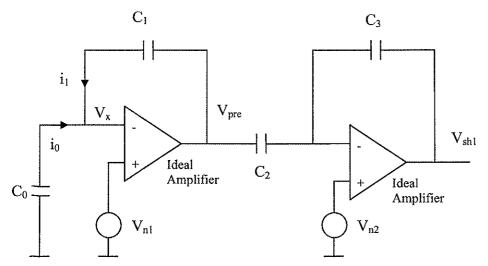

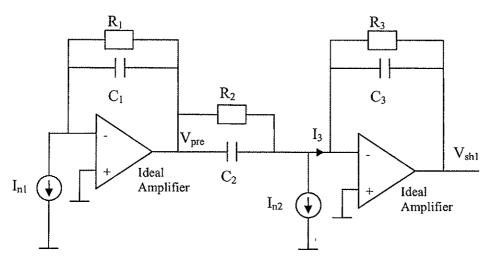

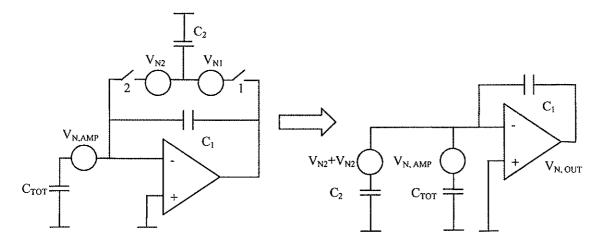

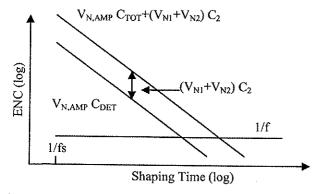

| 4.4.5            | Shaper Noise Contribution                           | 61               |

| .5 P             | PMOS or NMOS Input Device?                          | 64               |

| 4.5.1            | Substrate Noise in Mixed Mode Circuits              | 64               |

| .6 P             | rototype                                            | 70               |

| 4.6.1            | Chip Architecture                                   | 7 <b>0</b><br>71 |

| 4.6.2            | ESD Protection                                      | 72               |

| 4.6.3            | Channel Layout                                      | 73               |

|          | Cest Board Soard Architecture:                   | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - VBC 25 | oura / Monteoturo.                               | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.8 N    | Aeasurement Results                              | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

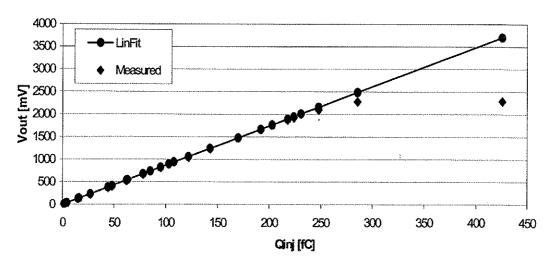

| 4.8.1    | Conversion Gain                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.8.2    | Linearity                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

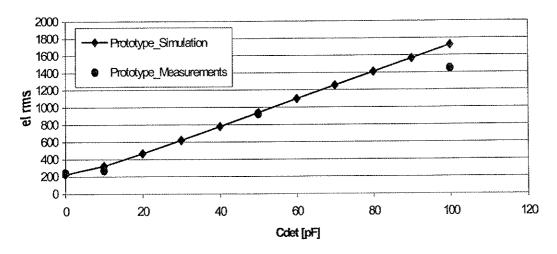

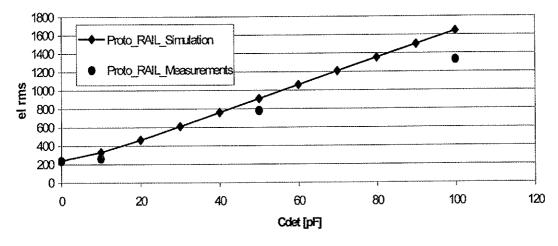

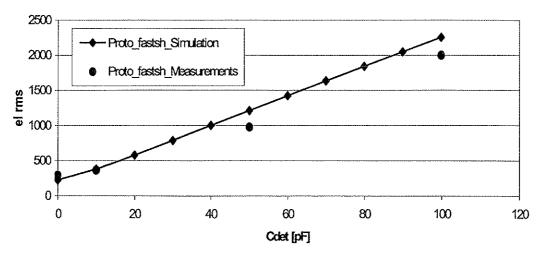

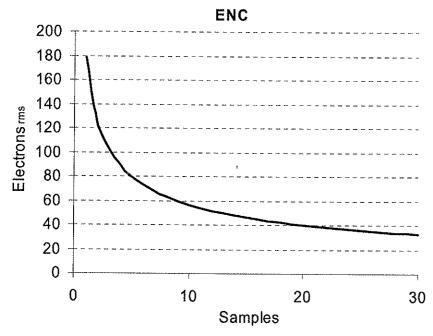

| 4.8.3    | ENC                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

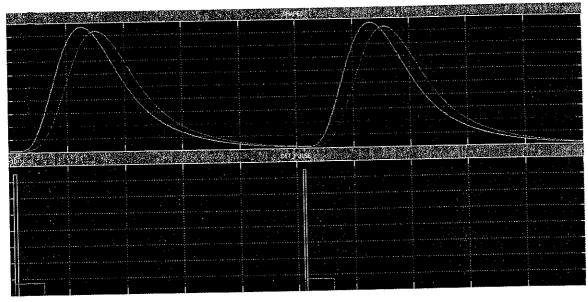

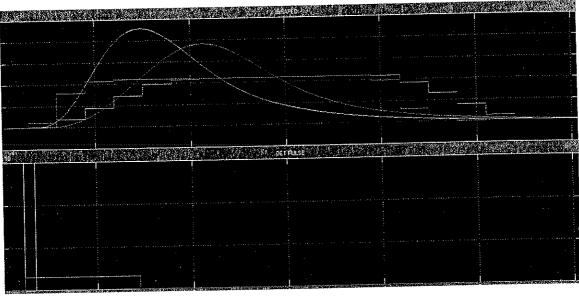

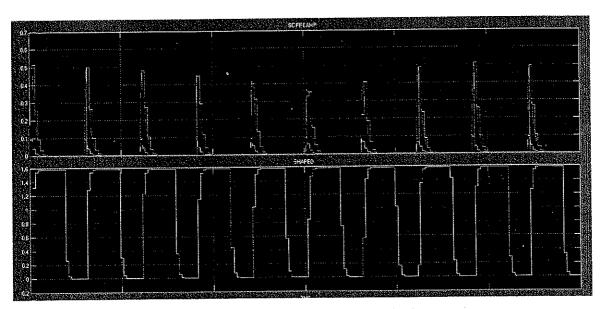

| 4.8.4    | Pulse Shape                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.8.5    | Requirement Simulation Test Results              | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CHAP     | TER 5 PROGRAMMABILITY                            | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.1 B    | oth Polarities                                   | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

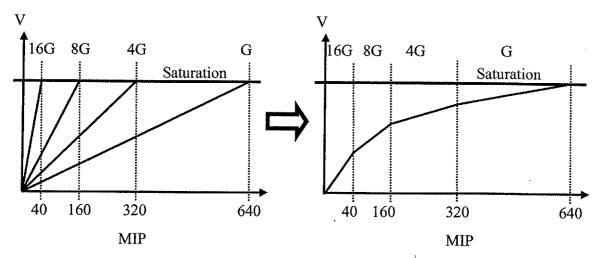

| 5.2 C    | Surrent Division Principle                       | chitecture:  rement Results version Gain arity set Shape sirement – Simulation – Test Results  5 PROGRAMMABILITY 81  Slarities t Division Principle sion Gain – Shaping Time mplifier Gain Adjustment rammable Preamplifier and Shaper mic Range Increase with Redundant Structures  Sampling Amplifier (QSA) Noise specified of Operation Out Analysis al Post Processing Simulation – A Time Domain Approach  BBREVIATIONS  107  GURES  77  88  81  84  85  87  87  88  88  89  90  90  90  90  90  91  92  93  94  95  96  97  98  98  98  98  98  98  98  98  98 |

| 5.3 C    | onversion Gain – Shaping Time                    | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.3.1    | Preamplifier Gain Adjustment                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.3.2    | Shaper Gain and Peaking Time Adjustment          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.3.3    | Programmable Preamplifier and Shaper             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.3.4    | Dynamic Range Increase with Redundant Structures |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

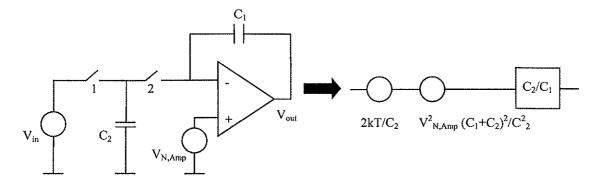

| 5.4 C    | harge Sampling Amplifier (QSA)                   | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.4.1    | KTC Noise                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.4.2    | Principe of Operation                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.4.3    | Read Out                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.4.4    | Noise Analysis                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.4.5    | Digital Post Processing                          | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

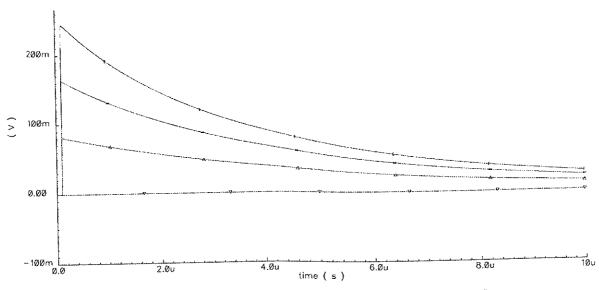

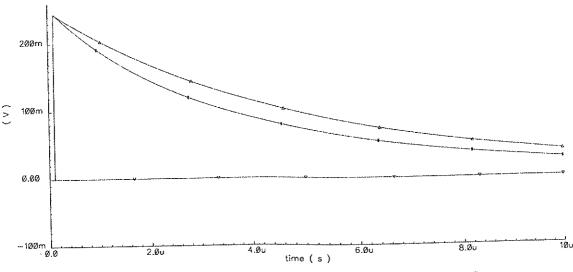

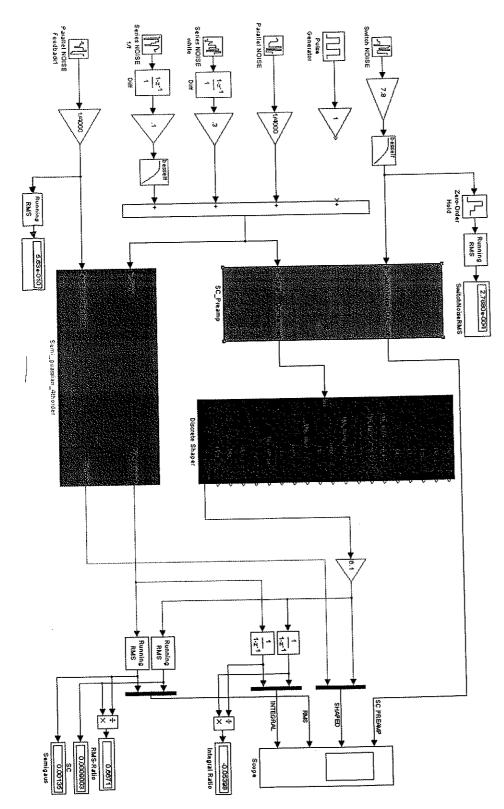

| 5.4.6    | Noise Simulation - A Time Domain Approach        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LIST     | OF ABBREVIATIONS                                 | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LIST C   | 109                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| REFEI    | RENCES                                           | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# Chapter 1

# Introduction

## 1.1 Gaseous Detectors

Gaseous detectors have been widely used in the field of high energy physics up to now. Features like cost efficiency, fast signals, good energy and spatial resolution make them indispensable for modern detector systems like the Large Hadron Collider experiments. Over the last decades many different particle multiplication methodologies have been developed. The use of Multi Wire Proportional Chambers (MWPC) for particle multiplication is still state of the art. An example is the ALICE (A Large Ion Collider Experiment) Time Projection Chamber (TPC) at CERN.

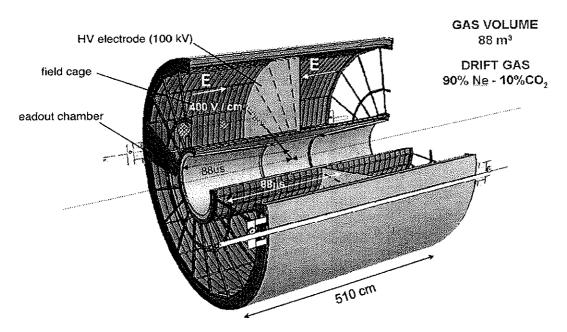

# 1.1.1 Time Projection Chamber – TPC

Figure 1 Alice TPC

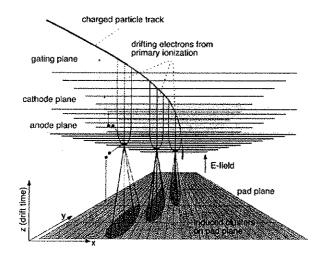

The TPC is the main part of the Alice tracking system. Because of the low mass, the detection medium has very little influence on the particle that has to be detected. This is an example for nondestructive detection of charged particles. A charged particle traversing the detector produces primary electrons by ionizing gas atoms. The applied electric field makes

electrons to move towards the anode whereas the positively charged ions drift towards the cathode. The electrons are detected in highly segmented readout chambers. By applying center of gravity algorithms information about the exact point of arrival is obtained. Through measurement of the arrival time the three dimensional particle track can be reconstructed.

The TPC allows particle identification because the collected charge at the pad plane is a function of the primary particle's energy loss.

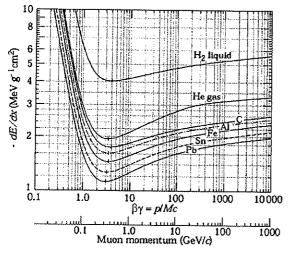

# 1.1.2 Energy Loss

A charged particle traversing a medium looses energy in many different ways. Interactions due to the strong and weak force are much less probable than interactions due to the electromagnetic force. The incoming charged particle leads to excitation and ionization of the medium. The contribution of other effects like Bremsstrahlung, Cherenkov and transition radiation to the total deposited energy is negligible in gas detectors. The energy loss is a statistical process that was described by Bethe and Bloch in the framework of relativistic quantum mechanics. The average differential energy loss per unit length is given by: [1]

$$-\frac{1}{\rho}\frac{dE}{dx} = K\frac{Z}{A}\frac{1}{\beta^2} \left[ \ln(\frac{2mc^2\beta^2 E_M}{I^2(1-\beta^2)}) - 2\beta^2 \right]$$

(1.1)

$$K = \frac{2\pi Nz^2 e^4}{mc^2}$$

(1.2)

$$E_M = \frac{2mc^2\beta^2}{1-\beta^2}$$

(1.3)

Figure 2 Energy loss [3]

0.12 x10<sup>4</sup>

0.10

0.08

0.06

phot

0.02 electron

10<sup>-1</sup>

P (GeV/c)

Figure 3 STAR TPC; Energy loss [4]

N Avogadro number m, e Electron mass and charge  $Z, A, \rho$  Atomic number, mass and density of the medium

E<sub>M</sub> Maximum allowed energy transfer

z, β Projectile's charge and velocity (in units of the speed of light, c)

# 1.1.3 Multi Wire Proportional Chamber (MWPC)

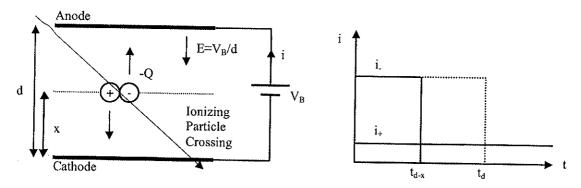

A common feature for many detectors is that they can be regarded as capacitive sources from a signal processing point of view. Moving charge in electric fields induces a current on the capacitor electrodes:

$$i = \frac{dQ_S}{dt} = \frac{QE}{V_B} \frac{dr}{dt} = \frac{QE}{V_R} v \tag{1.4}$$

Figure 4 Signal formation in a detector

The charge deposited is given by the integral of the current:

$$Q_{S} = Q_{S+} + Q_{S-} = \int_{x}^{0} \frac{QE}{V_{B}} dr + \int_{x}^{d} \frac{-QE}{V_{B}} dr = \frac{QE}{V_{B}} x + \left[ \frac{-QE}{V_{B}} (x - d) \right] = Q$$

(1.5)

The signal consists of an electron- and an ion-induced part. Due to higher mobility, electrons drift much faster to the anode than ions to the cathode. Note that the total charge deposited equals Q.

In many detectors the energy loss is not big enough to generate a signal that can be directly detected by the readout electronics. In such cases the primary electrons have to be further amplified. One of the possible solutions is given by the multi wire proportional chamber. The primary electron drifting towards the anode gets into regions of high electric fields. Ionizing collisions take place if the electron's energy is larger than the ionization energy of the gas. Furthermore through the excitation of gas atoms UV photons provoke photo electrons. An avalanche process is generated that is characterized by the multiplication factor (M). For a cylindrical proportional chamber the electric field around the anode wire is given by: [5]

$$E(r) = \frac{V_B}{\ln \frac{b}{a}} \frac{1}{r} \tag{1.6}$$

$$V(r) = \frac{V_B}{\ln \frac{b}{a}} \ln \frac{r}{a}$$

(1.7)

a Anode wire radius b Cathode radius

$$dq = \frac{Q}{V_R} \frac{dV}{dr} dr \tag{1.8}$$

Figure 5 Cylindrical proportional Chamber

Assuming that the entire avalanche process takes place at the distance  $\lambda$  from the anode wire, the deposited charge is given by:

$$Q_{-} = \frac{MQ}{V_{B}} \int_{a}^{a+\lambda} \frac{dV}{dr} dr = \frac{MQ}{\ln \frac{b}{a}} \ln \frac{a+\lambda}{a}$$

(1.9)

$$Q_{+} = \frac{MQ}{V_{B}} \int_{a+\lambda}^{b} \frac{dV}{dr} dr = \frac{MQ}{\ln \frac{b}{a}} \ln \frac{b}{a+\lambda}$$

(1.10)

$$Q_{S} = Q_{+} + Q_{-} = MQ {(1.11)}$$

The electric field is only high enough to initiate the avalanche process close to the anode wire. The distance that electrons drift towards the anode wire is much shorter than the way of the ions. In this case the induced signal is dominated by the ion drift.

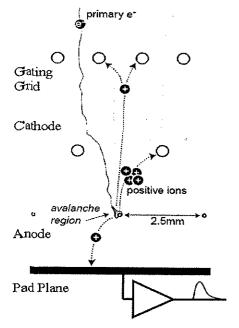

## 1.1.4 Alice TPC Readout

Figure 6 Alice TPC –MWPC [6]

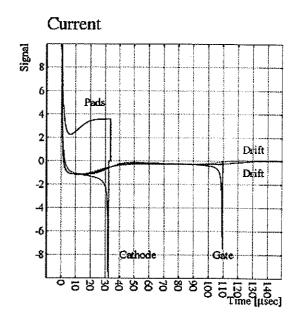

Figure 7 Induced current signal [7]

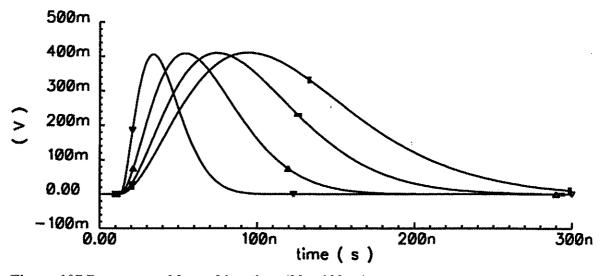

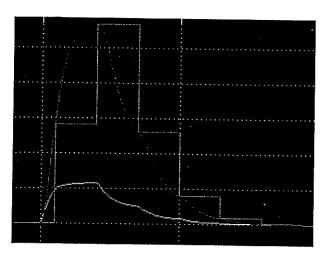

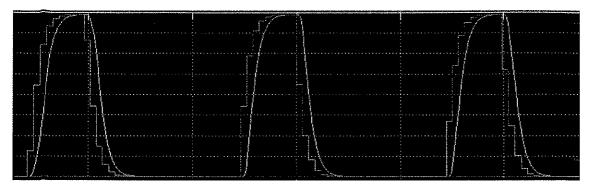

Figure 7 shows simulation results for the induced current signal at pad, cathode and gate wire. The pad plane is used for the readout. An avalanche process starts at approximately  $400~\mu m$  from the anode wires. The electron induced signal has a rise time of some ps whereas the ions take between 30 and  $110~\mu s$  to reach their destination. The ion induced current has a long tail with a rather complex shape.

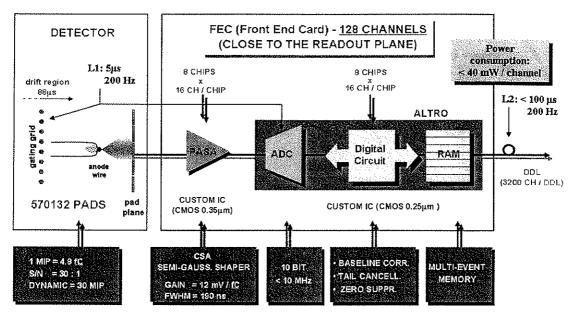

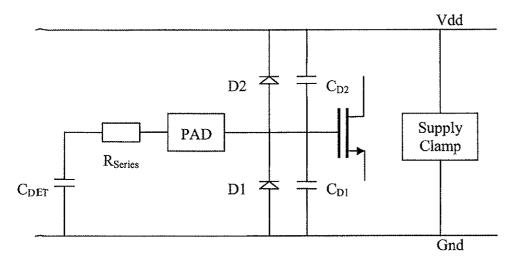

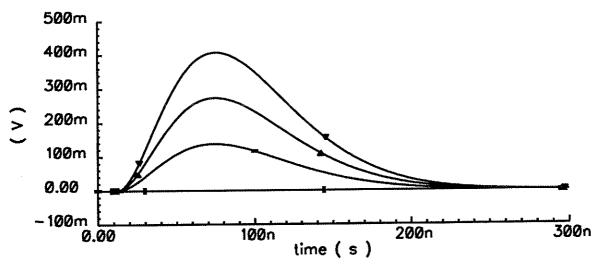

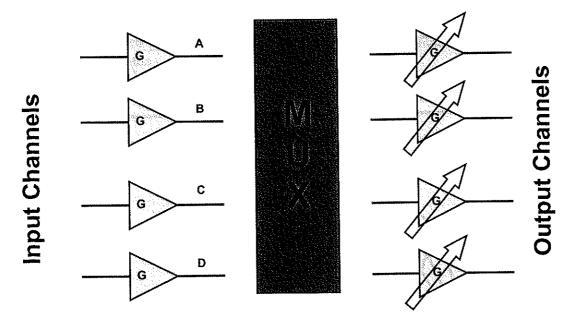

Printed circuit boards (front end cards) that are connected to 128 pads are used to process the detector data. Figure 8 depicts the front end card that is comprised of 8 CSA (PASA) followed by digital signal processors (ALTRO). Each PASA IC has 16 channels. The ALTRO contains an ADC, a multi event buffer and a digital processor that performs tail cancellation, zero suppression, baseline correction and data formatting.

Figure 8 Front-end electronics architecture [7]

Several front end cards are connected to the RCU (Readout Control Unit), another printed circuit board that ships TPC raw data optically to a computer farm where data analysis (e.g. track recognition) is performed.

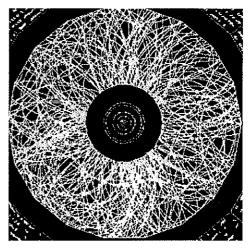

Figure 9 Track reconstruction [7]

Figure 10 Tracks produced by Pb - Pb collisions [6]

## 1.1.5 Gas Electron Multiplier (GEM)

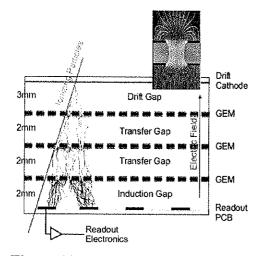

Modern lithography and etching technologies triggered the development of Micro Pattern Gaseous Detectors (MPGD). These are high granularity detectors with small distances between anode and cathode. GEM (Gas Electron Multiplier) and MICROMEGAS (MICRO MEsh GAseous Structures) are two examples of these new MPGD.

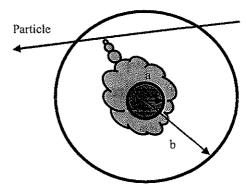

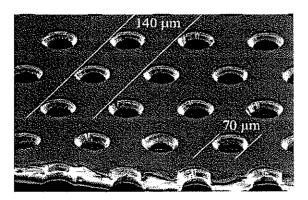

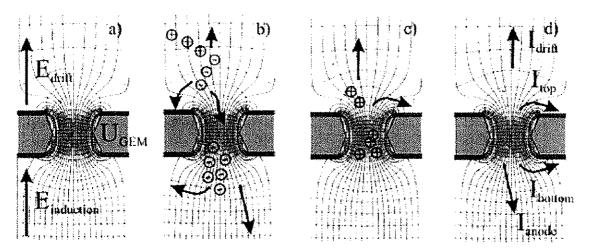

Figure 11 GEM foil, Electron microscope

The gas electron multiplier was first introduced by F. Sauli. A thin insulating polymer foil with metal on both sides constitutes the basic structure. An etching process forms holes through the metallized foil. A potential difference between the two sides is applied. Electrons drifting along the field lines towards the anode plane have to pass the GEM. The holes are places of high electric fields where the electron multiplying takes place by an avalanche process. The generated ions should be absorbed by the upper metal plane whereas the electron cloud drifts towards the anode. Hence only electrons induce a signal. GEM signals are fast and have no ion tail. The anode plane is a highly segmented printed circuit board with an arbitrary pad structure. [8]

Figure 12 Electron multiplication process [3]

Not all generated ions are absorbed at the upper metal plane. Some drift back to the detector volume. This effect is called ion feedback. Also not all of the generated electrons reach the anode plane. Similar to the MWPC where M determines the gas amplification factor, a ratio (M) determining the effective gain can be defined.

$$M = G_{eff} = \frac{\text{Number or electrons reaching the anode}}{\text{Number or electrons reaching the GEM hole}}$$

(1.12)

The gain of a single GEM stage is a function of the applied potential difference. Higher gain can be obtained by a higher voltage difference. An increase in potential difference also enhances the probability of discharge sparks that may damage the detector. Cascading of GEM foils can be applied for cases where high gain is demanded. Each GEM is operated below the discharge limit.

Single GEM

Double GEM

Triple GEM

380 400 420 440 460 480 500  $\Delta U_{GEM}(V)$

Figure 13 Triple GEM [9]

Figure 14 Gain for multiple GEM [9]

## Signal Polarity:

The induced signal at the GEM anode plane has the opposite polarity to a signal at the pad plane of a MWPC. In the case of GEM an electron cloud drifting towards the readout plane induces the signal. In the other case positively charged ions drift towards the readout plane and electrons away.

# Chapter 2

# **Noise Theory**

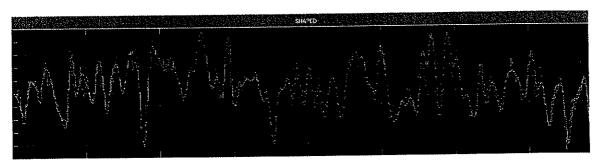

Noise is present in every electronic circuit and sets the minimum signal level that can be processed. This chapter mainly deals with the intrinsic small current or voltage fluctuations that are generated within the electronic device itself. Any kind of noise from external sources is not subject of this chapter. Noise is of greatest significance when designing an amplifier for charge readout from a detector because it sets an ultimate limit to the minimum detectable charge. A trade-off between power consumption and the amplifiers bandwidth determines the minimum detectable portion of charge.

# 2.1 Important Noise Sources

## 2.1.1 Thermal Noise

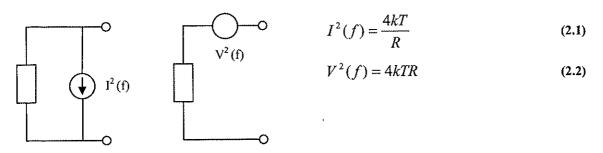

Noise in a resistor is primarily the result of random thermal motion of electrons and is unaffected by the presence or absence of direct currents. Thermal noise is white in the frequency range of interest and can be characterized by a PSD (Power Spectrum Density). [10]

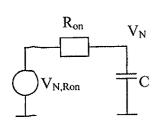

Figure 15 Representation of thermal resistor noise

| k        | Boltzmann constant                                              |

|----------|-----------------------------------------------------------------|

| T        | Temperature in Kelvin                                           |

| R        | Resistance in Ohm                                               |

| $I^2(f)$ | Single sided PSD of thermal noise current in A <sup>2</sup> /Hz |

| $V^2(f)$ | Single sided PSD of thermal noise voltage in V <sup>2</sup> /Hz |

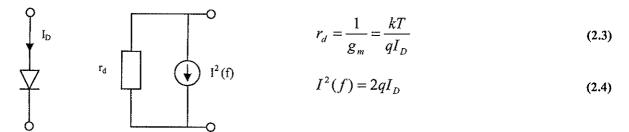

#### 2.1.2 Shot Noise

Shot noise is associated with a direct current flow and is present in diodes and bipolar transistors. It results from the discrete movement of charge across a potential barrier. Thermal noise is present even without a current flowing through a resistor.

In the past shot noise did not play an important role in the noise characterization of MOSFETs. But nowadays the scaling down of the gate oxide thickness entails a gate tunneling current that introduces shot noise. Thermal noise is different from shot noise but is modeled in a similar way. Both show a white frequency spectrum. [11]

Figure 16 Diode small signal equivalent circuit [10]

q Electron charge

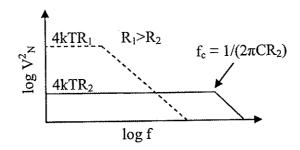

## 2.1.3 Flicker Noise

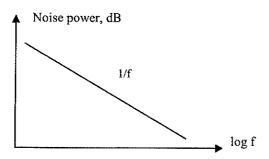

Figure 17 Flicker noise spectral density

Flicker noise is low frequency noise found in all active devices and in many passive components such as resistors. The origin of flicker noise in a MOSFET lies at the interface between the gate oxide and the silicon substrate where many "dangling" bonds appear, giving rise to extra energy states. Charge carriers moving close to the interface are trapped and released randomly which causes current fluctuations. There are several other theories that explain the mechanism of flicker noise. These certainly lie out of the scope of this theses and will therefore not be further considered. [12]

Different from shot and thermal noise the frequency spectrum is not white but pink (1/f behavior). Current or voltage fluctuations caused by flicker noise are concentrated at lower frequencies.

# 2.2 MOSFET

The input MOSFET has large impact on the noise performance, gain, bandwidth and power consumption of preamplifiers.

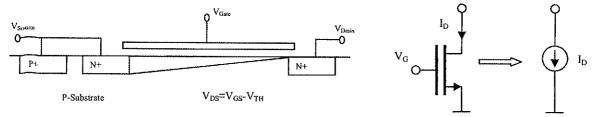

## 2.2.1 MOSFET in Saturation

Figure 18 Pinched off channel of a saturated Figure 19 MOSFET as MOSFET current source

If  $V_{DS}$  exceeds  $V_{GS}$ - $V_{TH}$  the MOSFET leaves the linear operating region, the channel gets pinched off before it reaches the drain side and the transistor starts to operate in the saturated region. For  $V_{GS} > V_{TH}$  the device operates in the strong inversion region and the following equations can be derived: [12]

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2$$

(2.5)

$$g_{m} = \frac{\partial I_{D}}{\partial V_{GS}}\Big|_{V_{DS,const}} = \mu_{n} C_{ox} \frac{W}{L} (V_{GS} - V_{TH})$$

(2.6)

$$g_{m} = \sqrt{2\mu_{n}C_{ox}\frac{W}{L}I_{D}} = \frac{2I_{D}}{V_{GS} - V_{TH}}$$

(2.7)

$$g_{m} = \mu_{n} C_{ox} \frac{W}{L} (V_{GS} - V_{TH}) (1 + \lambda V_{DS}) = \sqrt{\frac{2\mu_{n} C_{ox} (\frac{W}{L}) I_{D}}{1 + \lambda V_{DS}}}$$

(2.8)

I<sub>D</sub> Drain current

$\mu_n$  Mobility of the charge carriers

Cox Gate oxide capacitance per unit area

V<sub>TH</sub> Threshold voltage

W Width L Length

λ Channel length modulation factor

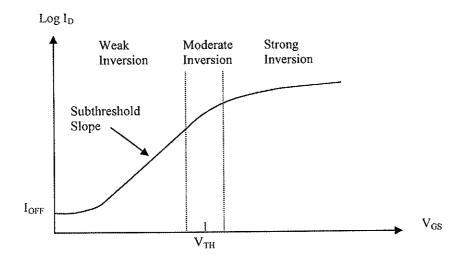

#### 2.2.1.1 MOSFET in Weak Inversion

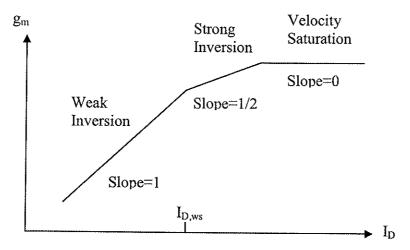

Imagine a device that is operated at constant current. Judging from equation (2.7) it may be assumed that an increase in transistor width would permit to achieve an arbitrarily high  $g_m$ .

But if the current is kept constant, then  $V_{GS}$  will start to drop until it reaches  $V_{TH}$ . At this point the device enters the operating region of subthreshold conduction (weak inversion) and equation (2.7) is no longer valid. The relation between  $V_{GS}$  and  $I_D$  becomes exponential (similar to the bipolar transistor) and can be expressed by the following equations:

Figure 20 Drain current from weak to strong inversion

$$I_D = I_{D0} \frac{W}{L} e^{\frac{V_{CS} - V_{TH}}{nkT}}$$

(2.9)

$$g_m = \frac{I_D}{nV_T} \tag{2.10}$$

$V_{T}$

kT/q

n Inverse of the subthreshold factor [11]

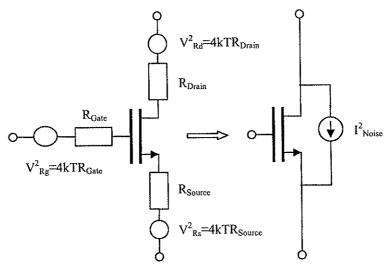

#### 2.2.2 MOSFET Noise

## 2.2.2.1 Poly Gate Noise

Figure 21 Ohmic noise sources

The most important ohmic noise source is the gate resistance. Input devices for low noise amplifiers are usually laid out with a high W/L ratio which results in negligible source and drain resistances but the gate resistance may not be negligible. Special layout techniques like fingering and metal contacts on both sides of the polysilicon gate help to decrease the gate resistance. If the contribution from drain and source resistance is neglected the following equation for the induced noise current can be derived: [12]

$$I_{Naise}^2 = 4kTR_{Gate}g_m^2 ag{2.11}$$

# 2.2.2.2 Thermal Channel and Flicker Noise of a MOSFET

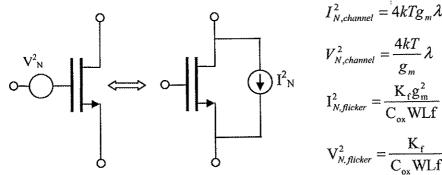

The thermal channel noise is the most significant noise source and can be represented as current source that modulates the drain current or as voltage source that modulates the gate to source voltage. [12]

Figure 22 Noise voltage and current equivalent

$$I_{N,channel}^2 = 4kTg_m\lambda \tag{2.12}$$

$$V_{N,channel}^2 = \frac{4kT}{g_m} \lambda \tag{2.13}$$

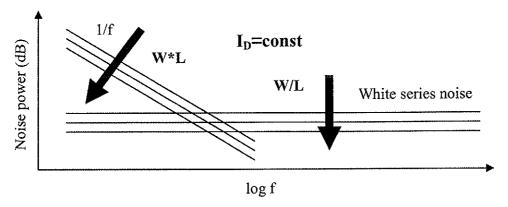

$$I_{N,flicker}^2 = \frac{K_f g_m^2}{C_{ox} WLf}$$

(2.14)

$$V_{N,flicker}^2 = \frac{K_f}{C_{ov}WLf}$$

(2.15)

$\lambda$  1 for linear operation, 2/3 for strong inversion and 1/2 for weak inversion  $K_f$  Technology dependent parameter

Since thermal channel and flicker noise are uncorrelated the total noise  $V_N^2$  or  $I_N^2$  can be represented by the sum of the single noise contributions:

$$V_N^2 = \frac{4kT}{g_m} \lambda + \frac{Kf}{C_{ox}WLf}$$

(2.16)

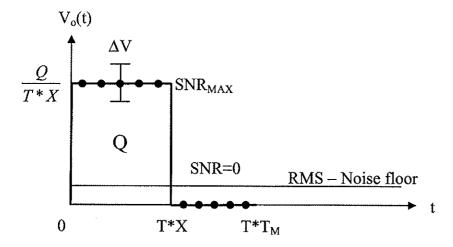

# 2.3 Equivalent Noise Charge (ENC)

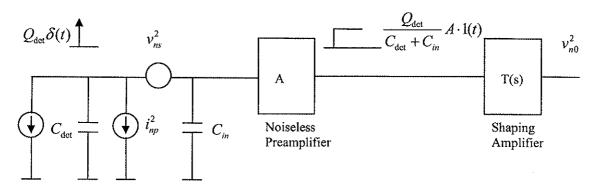

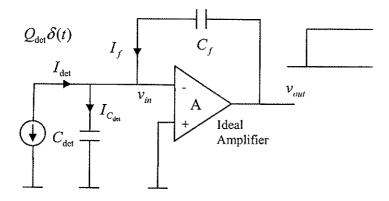

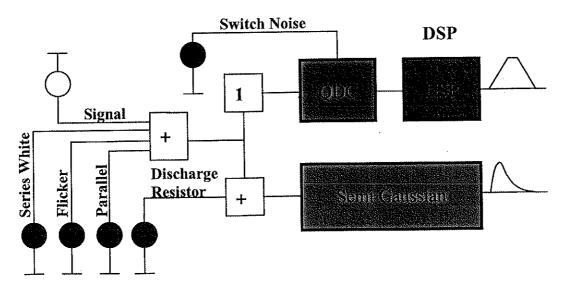

Figure 23 shows a typical system for charge measurement. It consists of a preamplifier that is followed by a shaping amplifier. A charge pulse generated by a detector provokes a voltage step at the output of the preamplifier that is proportional to the amplifier gain and inverse proportional to the sum of the capacitances at the input. The amplifier noise is modeled by a series voltage source  $v_{ns}^2$  that is composed of a white and an inverse proportional to frequency part. A parallel current source  $i_{ns}^2$  models current noise. [13]

Figure 23 Preamplifier followed by a shaping amplifier

$$v_{ns}^2 = a + \frac{c}{|\omega|} \tag{2.17}$$

$$i_{np}^2 = b ag{2.18}$$

$$C = C_{\text{det}} + C_{in} \tag{2.19}$$

For further calculations it proves more useful to convert the parallel current noise into an equivalent series voltage source. The total noise at the preamplifier output is described by  $N(\omega)$ .

$$N(\omega) = A^2 \cdot (a + \frac{b}{(\omega C)^2} + \frac{c}{|\omega|})$$

(2.20)

The system's response to an infinitely short current pulse is given by the shaper step response (integrating behavior of the preamplifier):

$$v_o(t) = \frac{A}{C} \cdot L^{-1}(\frac{T(s)}{s})$$

(2.21)

$L^{-1}$  Inverse Laplace transform operator

In Order to determine the maximum signal to noise ratio the maximum signal amplitude is calculated:

$$MAX[v_o(t)] = MAX\left[\frac{A}{C} \cdot L^{-1}\left(\frac{T(s)}{s}\right)\right]$$

(2.22)

The system's output noise is calculated by:

$$\overline{v_{n0}^2} = \int_{-\infty}^{\infty} N(\omega) \cdot \left| T(j\omega) \right|^2 df = \frac{1}{2\pi} \int_{-\infty}^{\infty} N(\omega) \cdot \left| T(j\omega) \right|^2 d\omega$$

(2.23)

$$SNR = \frac{Q_{\text{det}} \cdot MAX[\frac{A}{C} \cdot L^{-1}(\frac{T(s)}{s})]}{\frac{1}{v_{no}^{2}}}$$

(2.24)

The noise performance of detector electronics is usually expressed in terms of ENC (Equivalent Noise Charge) that is defined by the amount of charge at the input of the amplifier that is needed to produce the amplifier's intrinsic output noise. To calculate ENC, SNR in equation (2.24) is set equal to 1 and the following expression is obtained:

$$Q_{\text{det}} = ENC = \frac{\{\frac{1}{2\pi} \int_{-\infty}^{\infty} \left[C^{2} \cdot (a + \frac{c}{|\omega|}) + \frac{b}{\omega^{2}}\right] \cdot \left|T(j\omega)\right|^{2} d\omega\}^{\frac{1}{2}}}{MAX[L^{-1}(\frac{T(s)}{s})]}$$

(2.25)

Equation (2.25) shows how the contribution of the serial noise sources to the overall ENC scales with the input capacitance.

#### 2.3.1 Parallel Noise

Parseval's Theorem:

$$\iint_{-\infty} X(f)|^2 df = \iint_{-\infty} x(t)|^2 dt$$

(2.26)

$$v_o(s) = \frac{A}{C} \cdot \frac{T(s)}{s} \quad \Rightarrow \quad T(s) = \frac{v_o(s) \cdot s \cdot C}{A}$$

(2.27)

$$\overline{v_{n0\,parallel}^2} = \frac{1}{2\pi} \int_{-\infty}^{\infty} \frac{b}{(\omega C)^2} \cdot \left| T(j\omega) \right|^2 d\omega = \frac{1}{2\pi} \int_{-\infty}^{\infty} \frac{b \cdot \left| (j\omega C) \right|^2}{(\omega C)^2} \cdot \left| v_o(j\omega) \right|^2 d\omega = \int_{-\infty}^{\infty} b \cdot v_o(t)^2 dt \quad (2.28)$$

The output noise due to the parallel input noise is proportional to the area of the pulse.

## 2.3.2 Series Noise

$$v_o(t) = L^{-1}[s \cdot v_o(s)]$$

(2.29)

$$\overline{v_{n0series,white}^2} = \frac{1}{2\pi} \int_{-\infty}^{\infty} a \cdot |T(j\omega)|^2 d\omega = \frac{1}{2\pi} \int_{-\infty}^{\infty} a \cdot |(j\omega C)|^2 |v_o(j\omega)|^2 d\omega = \int_{-\infty}^{\infty} C^2 \cdot a \cdot v_o'(t)^2 dt \qquad (2.30)$$

The output noise due to the series input noise is proportional to the integral of the first derivation of the pulse shape.

$$\overline{v_{n0series1/f}^2} = \frac{1}{2\pi} \int_{-\infty}^{\infty} \frac{c}{|\omega|} \cdot |T(j\omega)|^2 d\omega = \frac{C^2}{2\pi} \int_{-\infty}^{\infty} c \cdot |\omega| \cdot |v_o(j\omega)|^2 d\omega$$

(2.31)

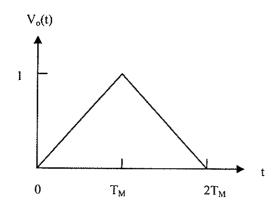

# 2.3.3 Case Study Triangular Shaping

Figure 24 Triangular pulse shape

$$MAX[v_o(t)] = 1$$

$$ENC^2 = \frac{v_{no}^2}{MAX[v_o(t)]}$$

(2.32)

$$\overline{v_{n0serieswhite}^2} = ENC_{serieswhite}^2 = \int_{-\infty}^{\infty} C^2 \cdot a \cdot v_o(t)^2 dt = C^2 \cdot a \cdot \frac{2}{T_M} = C^2 \cdot a \cdot \frac{A_1}{T_M}$$

(2.33)

$$\overline{v_{n0series1/f}^2} = ENC_{series1/f}^2 = \frac{C^2}{2\pi} \int_{-\infty}^{\infty} c \cdot \left|\omega\right| \cdot \left|v_o(j\omega)\right|^2 d\omega = C^2 \cdot c \cdot 0.88 = C^2 \cdot c \cdot A_2$$

(2.34)

$$\overline{v_{n0 \, parallel}^2} = ENC_{parallel}^2 = \int_{-\infty}^{\infty} b \cdot v_o(t)^2 \, dt = b \cdot \frac{2}{3} \cdot T_M = b \cdot A_3 \cdot T_M \tag{2.35}$$

$$ENC^{2} = ENC_{serieswhite}^{2} + ENC_{seriesl/f}^{2} + ENC_{parallel}^{2}$$

(2.36)

From the foregoing calculations a general equation can be derived where A<sub>1</sub>, A<sub>2</sub> and A<sub>3</sub> are constant factors that depend only on the pulse shape geometry. Series noise can be

Noise Theory

suppressed be choosing a longer shaping time but this increases the noise contribution from current noise. A very interesting result is that the series flicker noise contribution is independent of the shaping time. [14]

$$ENC^{2} = C^{2} \cdot a \cdot \frac{A_{1}}{T_{M}} + C^{2} \cdot c \cdot A_{2} + b \cdot A_{3} \cdot T_{M}$$

$$(2.37)$$

|    | Shaping                              | h (t)<br>Function | A2          | YA <sub>1</sub> A <sub>3</sub>    | A2<br>VA1A3 | A1   | A3             | $\sqrt{\frac{A_L}{A_3}}$ |

|----|--------------------------------------|-------------------|-------------|-----------------------------------|-------------|------|----------------|--------------------------|

| 1  | indefinise<br>cusp                   | ett   e-th        | 0.64<br>(2) | 1                                 | 0.64        | 1    | 1              | 1                        |

|    |                                      | k = t/c   k=1     | 0.77        | 1.04                              | 0.74        | 2.16 | 0.51           | 2.06                     |

| 2  | truncated<br>cusp                    | k=2               | 0.70        | 1.01                              | 0.69        | 1.31 | 0.78           | 1.30                     |

|    |                                      | -₹-₹0 ₹ ₹ k=3     | 0.67        | 1                                 | 0.67        | 1.31 | 0.91           | 1.10                     |

| 3  | triangular                           | $\wedge$          | 0.88        | 1.15                              | 0.76        | 2    | 0.67           | 1.73                     |

|    |                                      | Ο τ 2τ            | (4 in 2)    | $\left(\frac{2}{\sqrt{3}}\right)$ |             | -    | $\binom{2}{3}$ |                          |

| 4  | trapezoidal                          | O T 2T 3T         | 1.38        | 1.83                              | 0.76        | 2    | 1.67           | 1.09                     |

| 5  | piecewise<br>parabolic               | ) T 2T            | 1.15        | 1.43                              | 0.80        | 2.67 | 0.77           | 1.86                     |

| 6  | sinusoidal<br>lobe                   | O t 2t            | 1.22        | 1.57                              | 0.78        | 2.47 | 1              | 1.57                     |

| 7  | RC-CR                                |                   | 1.18        | 1.85                              | 0.64        | 1.85 | 1.85           | L                        |

| 8  | semigaussian<br>(n = 4)              |                   | 1.04        | 1.35                              | 0.77        | 0.51 | 3.58           | 0.38                     |

| 9  | gaussian                             | 0 1/2(1/2)        | 1           | 1.26                              | 0.79        | 0.89 | 1.77           | 0.71                     |

| 10 | clipped<br>approximate<br>integrator | 0 037             | 0.85        | 1.34                              | 0.63        | 2.54 | 0.71           | 1.89                     |

| 11 | bipolar<br>triangular                | 2τ                | 2           | 2.31                              | 9.87        | 4    | 1.33           | 1 73                     |

Figure 25 Important parameters for different pulse shapes [14]

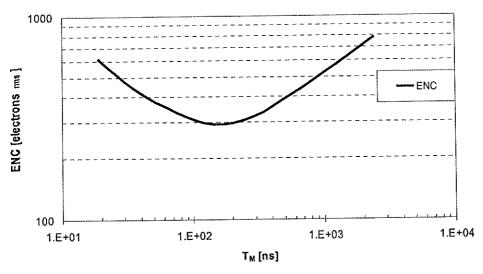

# 2.3.4 ENC as a Function of Shaping Time

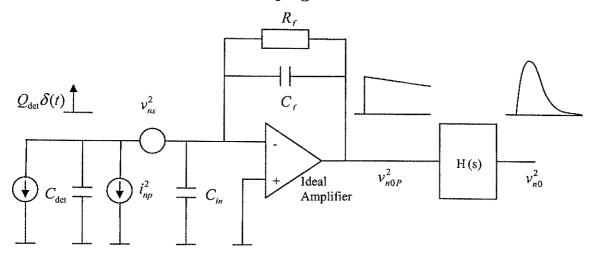

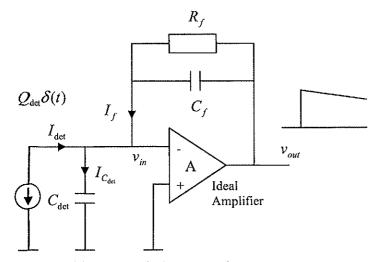

Figure 26 Charge sensitive amplifier followed by a shaping amplifier

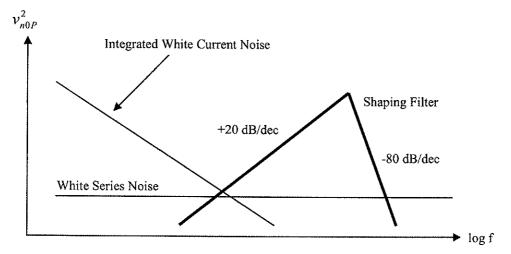

The shaping filter after the CSA improves the signal to noise ratio by suppressing specific frequencies. Current noise is reduced by high pass filtering and white series noise by low pass filtering, suggesting the use of a band pass filter. The system peaking time changes by altering the pass band.

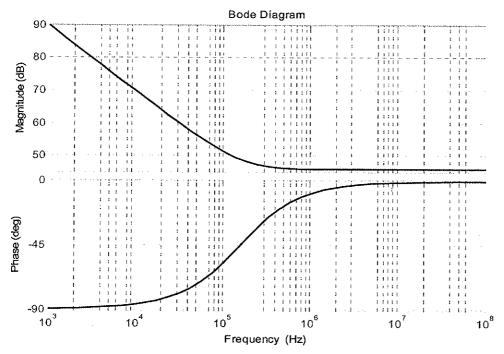

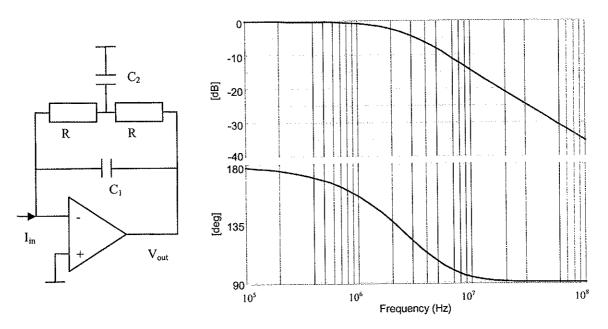

Figure 27 CR-RC<sup>4</sup> Shaper

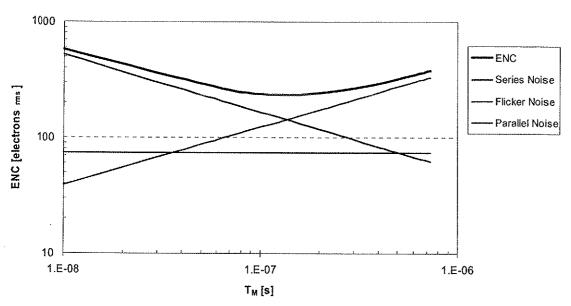

Assuming that the only noise contributors to  $v_{nO}^2$  are the CSA input transistor and the feedback resistor, equation (2.37) can be written as follows: [28]

$$ENC^{2} = (C_{det} + C_{in})^{2} \left( \frac{A_{1} 2kTR_{s}}{T_{M}} + \frac{A_{2}\pi K_{f}}{C_{ox}WL} \right) + T_{M} \frac{A_{3} 2kT}{R_{f}}$$

(2.38)

Figure 28 ENC vs. T<sub>M</sub>

#### Parameters for the calculation of ENC:

| C <sub>det</sub> | Cin  | $g_{m}$ | $R_{\mathrm{f}}$ | K <sub>f</sub> | T     | $A_1$ | $A_2$ | $A_3$ |

|------------------|------|---------|------------------|----------------|-------|-------|-------|-------|

| 12 pF            | 3 pF | 30 mS   | $2 M\Omega$      | 6e-25          | 330 K | 1.85  | 1.18  | 1.85  |

Table 1

$$R_s = \frac{1}{g_m} \lambda = \frac{1}{g_m} \frac{2}{3}$$

(Strong inversion)

$$R_{s} = \frac{1}{g_{m}} \lambda = \frac{1}{g_{m}} \frac{2}{3}$$

(Strong inversion)

$$c = \frac{\pi K_{f}}{WLC_{OX}} \approx \frac{\pi K_{f}}{C_{in}}$$

(2.40)

Calculation of the minimum ENC:

$$ENC^{2'} = (C_{det} + C_{in})^{2} (\frac{A_{1} 2kTR_{s}}{-T_{M}^{2}}) + \frac{A_{3} 2kT}{R_{f}} = 0$$

(2.41)

$$T_{\text{M min}} = (C_{\text{det}} + C_{\text{in}}) \sqrt{\frac{A_1}{A_3} R_s R_f} = 173 \text{ns}$$

(2.42)

$$\tau_{\rm C} = \frac{1}{T_{\rm M_{min}}}$$

(Noise corner frequency) (2.43)

Signals generated by detectors in high energy physics show very large bandwidth. If the detector pulse is approximated by a delta Dirac impulse (white frequency spectrum), current noise and signal will have the same spectrum after the preamplifier. But why do longer peaking times lead to worse ENC if signal and current noise are affected by the shaper in the same way? This is due to the definition of the ENC that is the ratio of peak amplitude to rms noise. Equation (2.28) shows that the noise floor due to current noise is proportional to the area of the pulse itself. Keeping the peak amplitude (conversion gain) constant but increasing the shaping time increases the pulse area. This worsens the ratio of peak amplitude and current noise and therefore the ENC.

# 2.4 Preamplifier Configurations

# 2.4.1 Pure Capacitive Feedback

Figure 29 Charge sensitive amplifier

Charge released by the detector is integrated on the feedback capacitance. A finite gain and unlimited bandwidth amplifier will respond to a Dirac impulse with an instantaneous voltage step at the output. Due to the finite gain not all of the released charge will flow through the amplifiers virtual ground.

$$v_{out} = -v_{in}A \tag{2.44}$$

$$v_{out} - v_{in} = v_{C_f} = -v_{in}A - v_{in} = -v_{in}(A+1)$$

(2.45)

$$C_{in} = \frac{Q_{C_f}}{v_{in}} = \frac{C_f v_{in}(A+1)}{v_{in}} = C_f (A+1)$$

(2.46)

The amplifier input capacitance  $C_{in}$  appears in parallel to the detector capacitance. Making  $C_{in}$  big enough by choosing an appropriate gain will guarantee that nearly all of the released charge gets integrated on the feedback capacitance. But which portion of charge remains on the detector capacitance?

$$\frac{v_{in}C_{\text{det}}}{v_{C_f}C_f + v_{in}C_{\text{det}}} = \frac{v_{in}C_{\text{det}}}{v_{in}C_f(A+1) + v_{in}C_{\text{det}}} = \frac{C_{\text{det}}}{C_f(A+1) + C_{\text{det}}} = \frac{C_{\text{det}}}{C_{in} + C_{\text{det}}}$$

(2.47)

For a detector capacitance of 20 pF, a feedback capacitor of 500 fF and an amplifier gain of 1000 the portion of charge that remains on the detector capacitance is 3.8%.

In reality the amplifier has finite gain and limited bandwidth that has to be taken into account when analyzing the response of the CSA. In the ongoing analysis a first order model for the amplifier will be used. This constitutes a rather good approximation to reality because CSAs in use are usually built around single stage amplifiers that show only one dominant pole.

$$A(s) = \frac{A_{DC}}{1 + s\tau_P} \tag{2.48}$$

$\tau_{P}$  Pole time constant

$$I_{\text{det}} + I_f = I_{C_{\text{det}}} \tag{2.49}$$

$$V_{out}(s) = \frac{-I_{det}}{(\frac{C_{det} + C_f}{A_{DC}}) + C_f} \cdot \frac{1}{1 + s\tau_p \frac{C_f + C_{det}}{C_f + C_{det} + A_{DC}C_f}} \cdot \frac{1}{s}$$

(2.50)

Equation (2.50) shows how the different parameters modulate the amplifier gain and frequency characteristics. The dependence on the detector capacitance is of greatest importance because it is often not exactly known.

$$R_{in}(s) = \frac{I_{det}}{v_{in}} = \frac{\frac{1}{s} + \tau_P}{C_{det} + C_f + A_{DC}C_f + s\tau_P(C_{det} + C_f)}$$

(2.51)

Figure 30 CSA input impedance

$$V_{out}(t) = \frac{-A_{DC}I_{in}}{C_{det} + C_f + A_{DC}C_f} \left( 1 - e^{\frac{(C_{det} + C_f + A_{DC}C_f)t}{(C_{det} + C_f)\tau_p}} \right)$$

(2.52)

For

$$A_{DC} >>:$$

$$V_{out}(s) \cong \frac{-I_{det}}{C_f} \cdot \frac{1}{1 + s\tau_p - \frac{1}{1 + A_{DC}} \cdot \frac{1}{C_f}} \cdot \frac{1}{s}$$

(2.53)

# 2.4.2 Current Sensitive Configuration

Figure 31 Current sensitive

An alternative to the CSA is the current sensitive configuration where the feedback capacitor is replaced by a pure resistance. The input impedance is given by the feedback impedance divided be the amplifier gain. In spite of capacitive feedback the input capacitance will not swamp the detector capacitance. By choosing an appropriate amplifier gain the input resistance can be made small enough so that it is effectively the current signal from the detector that is amplified. Ideally no charge remains on the detector capacitance. Depending on the application a resistance in the  $M\Omega$  region is often mandatory to suppress current noise. In reality it proves difficult to apply highly resistive feedback over a high gain amplifier which results in stability problems.

$$R_{in} = \frac{R_f}{A+1} {(2.54)}$$

$$R_{in}(s) = \frac{R \cdot (1 + s\tau_P)}{1 + A_{DC} + s(C_{det}R + \tau_P) + s^2 C_{det}R\tau_P}$$

(2.55)

$$V_{out}(s) = \frac{-I_{\text{det}} A_{DC} R}{1 + A_{DC} + s(C_{\text{det}} R + \tau_P) + s^2 C_{\text{det}} R \tau_P}$$

(2.56)

In order to avoid stability problems practical transimpedance amplifiers have also a small capacitance in parallel to the resistive feedback.

## 2.4.3 CSA with Discharge Resistor

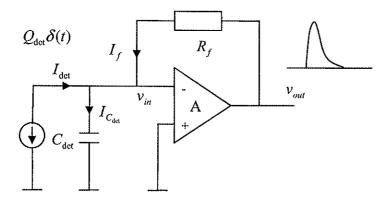

Figure 32 CSA with discharge resistor

The resistor serves as discharge device and sets output and input DC. Depending on the expected event rate the feedback time constant has to be chosen sufficiently small in order to avoid saturating the amplifier. In case of the charge sensitive configuration this resistance can be made very large so that its noise contribution is negligible. This has greatly contributed to the fact that the charge sensitive configuration is widely used in the field of detector readout.

$$R_{in} = \frac{Z_f}{A+1} \tag{2.57}$$

$$R_{in}(s) = \frac{R_f \cdot (1 + s\tau_P)}{1 + A_{DC} + s(C_{det}R_f + C_fR_f + A_{DC}C_fR_f + \tau_P) + s^2\tau_P(C_{det}R_f + C_fR_f)}$$

(2.58)

$$V_{out}(s) = \frac{I_{\det} A_{DC} R_f}{1 + A_{DC} + s(C_{\det} R_f + C_f R_f + A_{DC} C_f R_f + \tau_P) + s^2 \tau_P(C_{\det} R_f + C_f R_f)}$$

(2.59)

If the detector signal is an indefinitely short Dirac delta current impulse the charge collection time will be determined by the preamplifier's rise time. The feedback resistance continuously discharges the feedback capacitance resulting in a loss of amplitude and pulse peaking before all of the detector charge got collected. This effect is called ballistic deficit and takes place if the charge collection time is not negligibly short in comparison to the peaking time of the output pulse. But if the detector does not release charge instantaneously the time profile of the detector current will affect the charge collection time. In detectors with a constant charge collection time, relatively large ballistic deficits can often be tolerated because a constant fraction of the amplitude for each pulse is lost. If the charge collection time varies, a variable amount of each pulse will be lost leading to a loss in terms

of charge resolution. This problem is obviously most severe for those detectors with large variations in charge collection time like proportional counters where the shape of the detector signals in a function of angular spread. [2] [1]

### 2.4.3.1 Charge Sensitive Mode

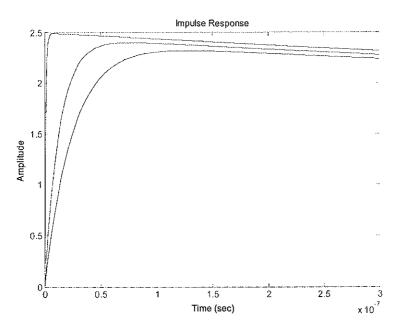

Figure 33 CSA impulse response, increasing CDET

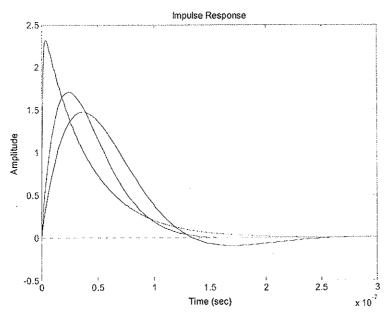

### 2.4.3.2 Transimpedance Mode

Figure 34 Transimpedance amplifier impulse response, increasing CDET

The preamplifier discharge time constant is in the order of the shaping time.

Chapter 2

Noise Theory

# Chapter 3

# Designing in a 0.13 µm CMOS Process

# 3.1 IBM 0.13 μm CMOS

MOSIS offers access to the IBM 0.13  $\mu m$  CMOS technology for prototype and low volume fabrication: [15]

- Twin-well CMOS technology on nonepitaxial p-doped substrate

- Low resistance cobalt-silicide n+ and p+ doped polysilicon and diffusion regions

- Supply voltages are 1.2 V core (1.5 V optional) and 2.5 V I/O.

- Broad range of FET devices to optimize power and performance

- High-value, low-tolerance capacitors

- Low tolerance resistors with low and high sheet resistivity

- Four to eight levels of global copper metal

The available technology of the CERN MPWR in December 2005 was the CMOS 8SFG that does not support many components of the analog CMOS 8RF technology.

Selection of available options: [16]

| Thin Oxide + Thick Oxide + 3.3 V I/O's 1.2/2.5/3.3 V                |                       |

|---------------------------------------------------------------------|-----------------------|

| Zero-V <sub>TH</sub> NFET Thin Oxide                                | 1.2 V                 |

| Thin Triple Well NFET                                               | 1.2 V                 |

| Zero-V <sub>TH</sub> NFET Thick Oxide                               | 2.5/3.3 V             |

| Thick Triple Well NFET                                              | 2.5/3.3 V             |

| Regular $V_{TH}$ NFET + Low Power $V_{TH}$ NFET + Low $V_{TH}$ NFET |                       |

| Regular $V_{TH}$ PFET + Low Power $V_{TH}$ PFET + Low $V_{TH}$ PFET |                       |

| PCDCAP Thin Oxide                                                   | Decoupling Capacitor  |

| PCDCAP Thick Oxide                                                  | Decoupling Capacitor  |

| VNCAP                                                               | Vertical natural Cap. |

| OP N+ Diffusion Resistor                                            |                       |

| OP P+ Poly Resistor                                                 |                       |

Table 2

No MIM (Metal Insulator Metal) capacitor was available. Therefore the VNCAP with a capacity density of 1.3 fF/ $\mu$ m<sup>2</sup> (M1-M6) was used as linear capacitor for the filtering stages.

### 3.2 Short Channel Effects

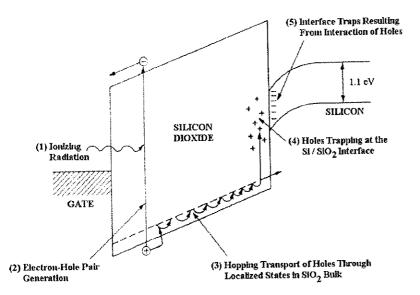

### 3.2.1 Hot Carrier Effect

At high lateral fields (see velocity saturation 4.4.3) the average velocity of carriers reaches a saturation level when the energy gained during the acceleration in the electric field equals the lost energy when hitting atoms in the silicon lattice. Impact ionization takes place if the acquired energy of charge carriers is high enough, thereby creating electron hole pairs. The created electrons are absorbed by the drain and the holes by the substrate (drain-substrate current). Due to the high energy of hot carriers they may be injected in the gate oxide where they can get trapped in the gate oxide itself or in the interface between Si and SiO<sub>2</sub>. These trapped charges have influence on the threshold voltage (reliability). Gate leakage and substrate leakage current are observed as a consequence of hot carrier effects.

In velocity saturation the transconductance is found to be constant and no longer a function of the current.

The high lateral electric field causes carriers not to be in thermal equilibrium with the silicon lattice. The carriers have higher temperature (hot carriers) and cause therefore higher thermal noise (see 3.2.5). [17]

# 3.2.2 Mobility Degradation with Vertical Field

Higher gate voltages force the current to flow closer to the interface between oxide and silicon, resulting in more carrier scattering and hence lower mobility. The following equation is an empirical approach to model the lower mobility due to higher gate voltages. [12]

$$\mu_{eff} = \frac{\mu_0}{1 + \theta(V_{GS} - V_{TH})}$$

$$\theta \qquad \text{Fitting parameter}$$

(3.1)

Decreased mobility degrades the performance of MOS transistors by lowering the achievable transconductance and current capability.

# 3.2.3 Drain Induced Barrier Lowering (DIBL)

In short channel devices the drain potential has an impact on several parameters like threshold voltage and output resistance. Higher drain voltage increases the surface potential, therefore a conducting channel is easier formed. In this way DIBL decreases the threshold voltage.

## 3.2.4 Output Resistance

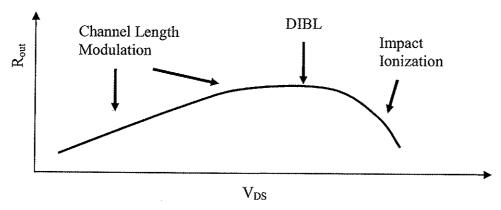

For constant output resistance the channel length modulation is modeled by  $\lambda$  that is inversely proportional to L. In reality the output resistance changes as a function of  $V_{DS}$ . For higher drain voltages the pinch off point in saturation moves towards the source, this increases the output resistance. As  $V_{DS}$  further increases DIBL lowers the threshold voltage and therefore the drain current increases. For even higher drain voltages impact ionization at the drain produces a large current flowing to the substrate and therefore reduces the output resistance.

Figure 35 Output resistance vs. drain voltage for short channel devices [12]

### 3.2.5 Thermal Noise Excess Factor

$$V_{N,channel}^2 = \frac{4kT}{g_m} \Gamma = \frac{4kT}{g_m} \alpha_W n\gamma \tag{3.2}$$

γ Between 1/2 for weak inversion and 2/3 for strong inversion

n Sub-threshold slope factor

Γ Channel thermal noise coefficient [18]

$\alpha_{\rm W}$  Excess noise factor [19]

Effects like velocity saturation, carrier heating, mobility reduction due to the vertical field and channel length modulation are responsible for an increase in thermal channel noise in short channel devices. The effects mentioned above are functions of the biasing conditions. Low  $V_{DS}$  is recommended for minimizing the excess noise. [17]

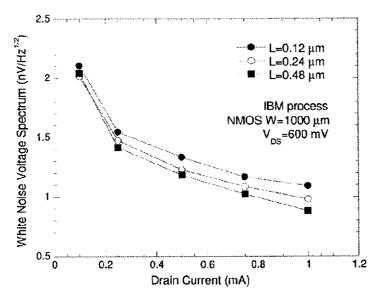

Figure 36 Voltage noise spectrum vs. drain current for three different NMOS transistors

The devices tested in Figure 36 were operated close to weak inversion where the geometry has only little effect on the transconductance as long as the device is kept in weak inversion. Therefore it was assumed that the additional noise component is due to short channel effects. It was observed that  $\alpha_W = 1$ , except for NMOS transistors with shorter channel length where  $\alpha_W = 1.2$ . [19]

### 3.2.6 Flicker Noise

$$V_{N,flic\,ker}^2 = \frac{K_f}{C_{cr}WLf^{\alpha_f}} \tag{3.3}$$

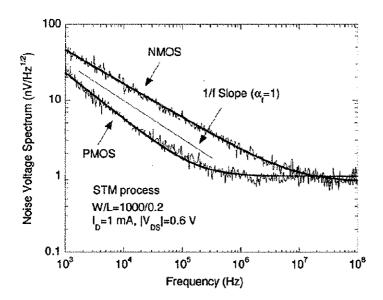

There are different theories about the origin of flicker noise but all of them agree on the formula above where the voltage PSD referred to the gate is inverse proportional to the gate area and frequency. It is expected that PMOS transistors will lose their advantage in terms of flicker noise to NMOS devices in scaling CMOS. The factor  $\alpha_f$  determines the noise slope. Its value is process and device dependent (see Figure 37). [17]

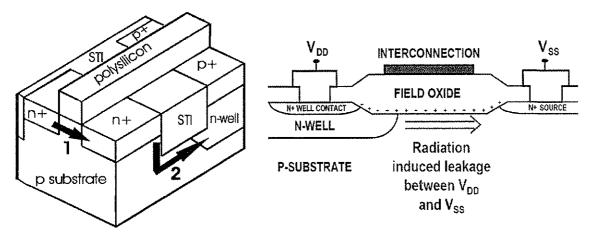

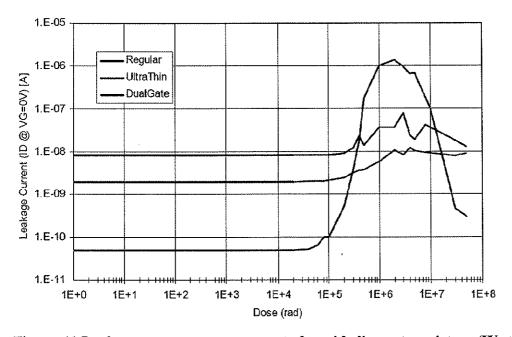

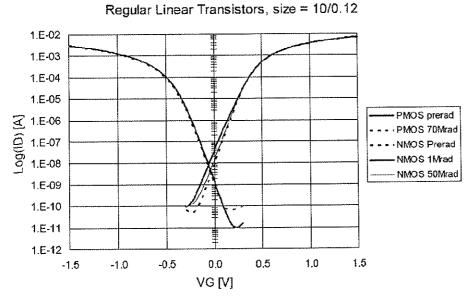

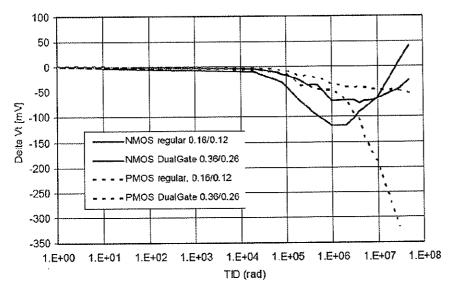

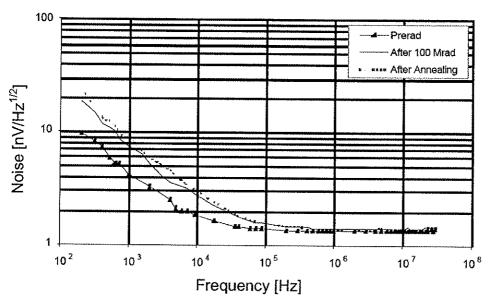

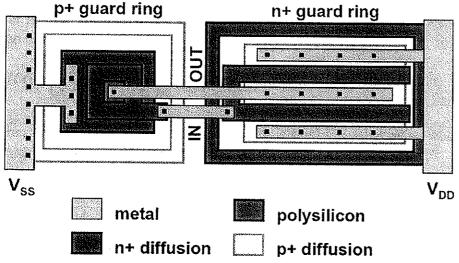

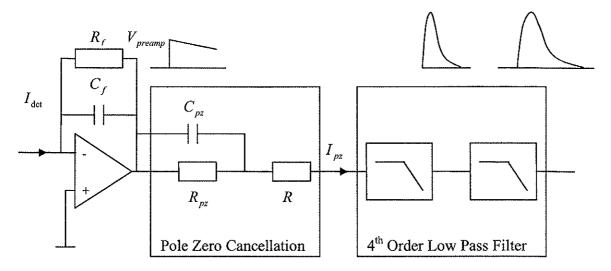

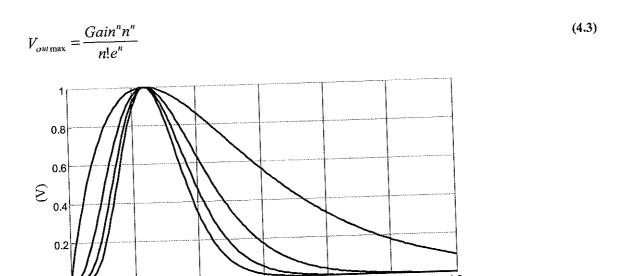

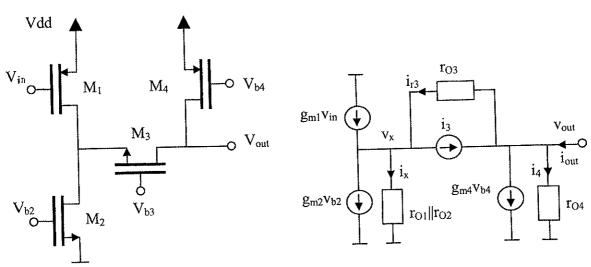

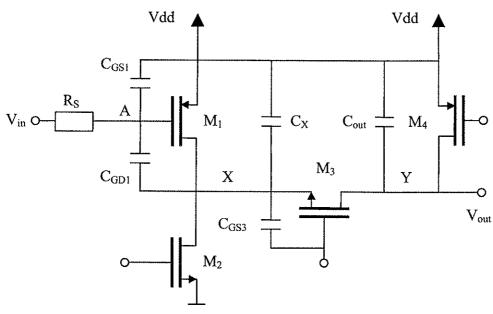

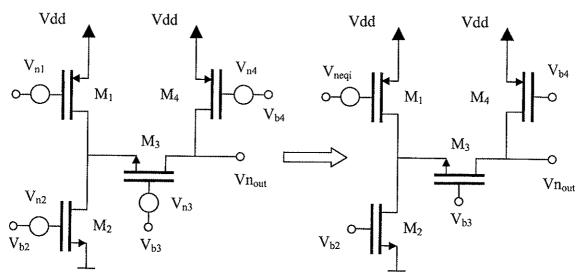

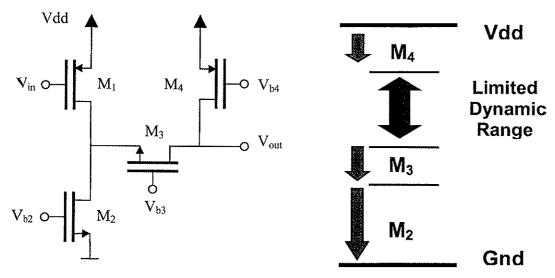

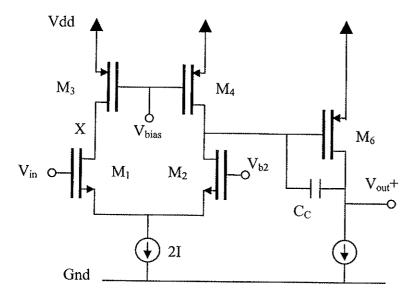

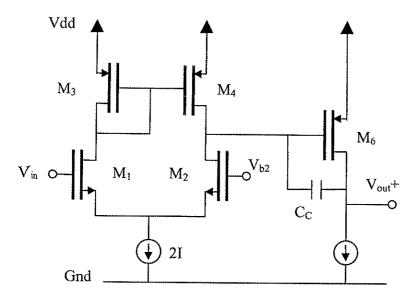

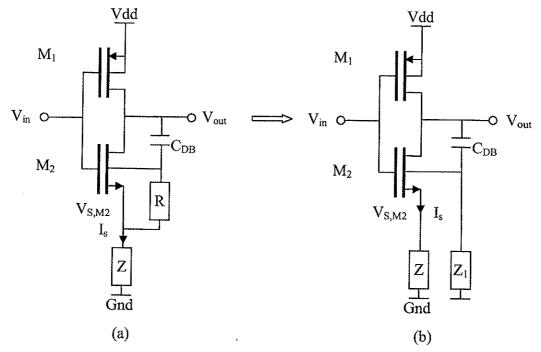

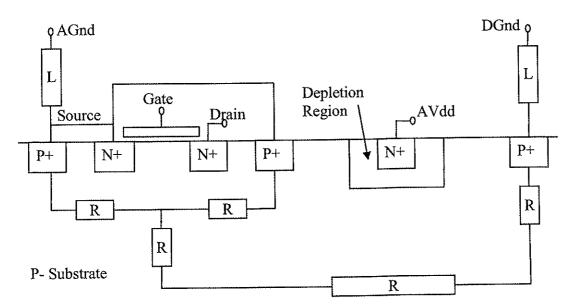

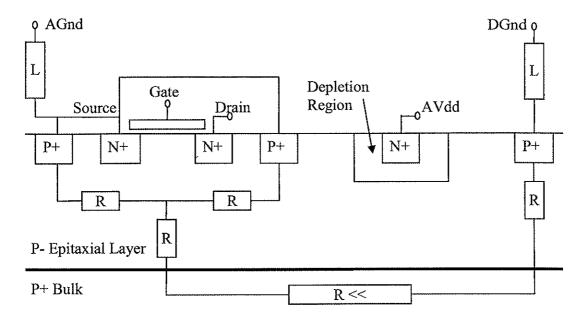

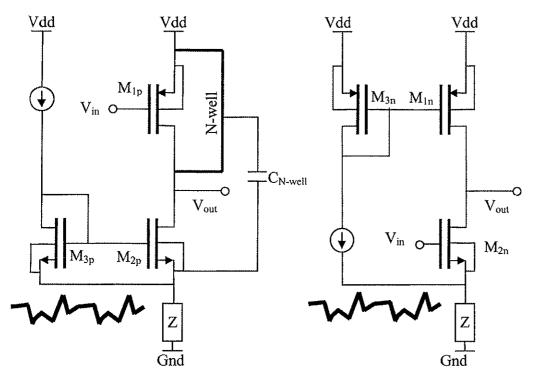

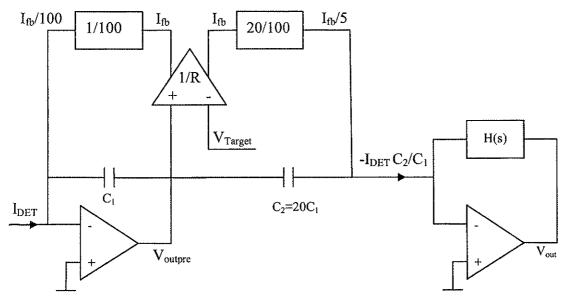

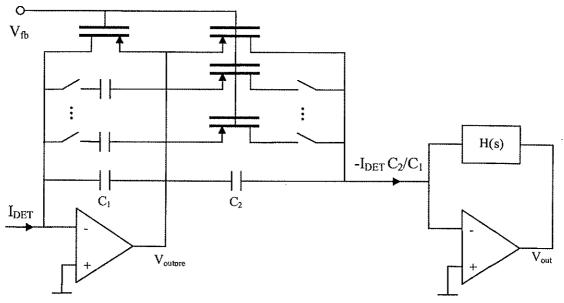

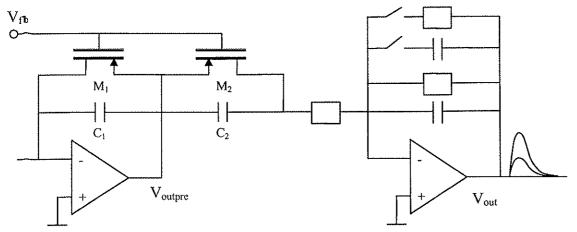

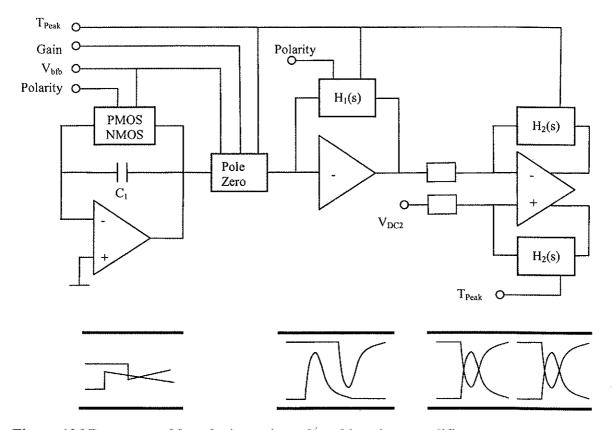

Figure 37 Gate referred noise voltage spectra for NMOS and PMOS devices with the same W/L in a STM 0.13 µm process [19]