European Coordination for Accelerator Research and Development

# **PUBLICATION**

# DEVELOPMENT OF A FAST, SINGLE-PASS, MICRON-RESOLUTION BEAM POSITION MONITOR SIGNAL PROCESSOR: BEAM TEST RESULTS FROM ATF2

Apsimon, Robert (John Adams Institute, Oxford University, UK) *et al*

04 June 2010

The research leading to these results has received funding from the European Commission under the FP7 Research Infrastructures project EuCARD, grant agreement no. 227579.

This work is part of EuCARD Work Package 1: Management.

The electronic version of this EuCARD Publication is available via the EuCARD web site <a href="http://cern.ch/eucard">http://cern.ch/eucard</a> or on the CERN Document Server at the following URL: <a href="http://cdsweb.cern.ch/record/1269663">http://cdsweb.cern.ch/record/1269663</a>

|  | EuCARD-CON-2010-016 |  |

|--|---------------------|--|

|--|---------------------|--|

# DEVELOPMENT OF A FAST, SINGLE-PASS, MICRON-RESOLUTION BEAM POSITION MONITOR SIGNAL PROCESSOR: BEAM TEST RESULTS FROM ATF2

R. Apsimon, D. Bett, P.N. Burrows, G.B. Christian, B. Constance, H. Dabiri Khah, C. Perry, J. Resta Lopez, C. Swinson, John Adams Institute, Oxford University, UK.

#### Abstract

We present the design of a stripline beam position monitor (BPM) signal processor with low latency (c. 10ns) and micron-level spatial resolution in single-pass mode. Such a BPM processor has applications in single-pass beamlines such as those at linear colliders and FELs. The processor was deployed and tested at the Accelerator Test Facility (ATF2) extraction line at KEK, Japan. We report the beam test results and processor performance, including response, linearity, spatial resolution and latency.

#### INTRODUCTION

A number of fast beam-based feedback systems are required at the International electron-positron Linear Collider (ILC) [1]. At the interaction point (IP) a very fast system, operating on nanosecond timescales within each bunchtrain, is required to compensate for residual vibration-induced jitter on the final-focus magnets by steering the electron and positron beams into collision.

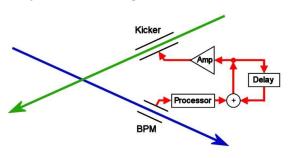

Figure 1: Schematic of IP intra-train feedback system with a crossing angle. The deflection of the outgoing beam is registered in a BPM and a correcting kick applied to the incoming other beam.

The key components of each such system are beam position monitors (BPMs) for registering the beam orbit; fast signal processors to translate the raw BPM pickoff signals into a position output; feedback circuits, including delay loops, for applying gain and taking account of system latency; amplifiers to provide the required output drive signals; and kickers for applying the position (or angle) correction to the beam. A schematic of the IP intratrain feedback is shown in Figure 1, for the case in which the beams cross with a small angle; the current ILC design incorporates a crossing angle of 14 mrad.

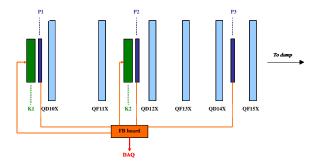

Beam tests of fast, single bunch resolution, analogue BPM processors were made at the Accelerator Test Facility (ATF) at KEK, Japan. A diagram of the feedback setup is shown in Figure 2. The typical beam properties at ATF include dimensions of approximately 7um in y and 70um in x, energy of 1.28 GeV and ~1x10<sup>10</sup> particles per bunch for single bunch operation [2]. The FONT system occupies a low emittance region of the beamline and uses 12cm long stripline BPMs (Figure 3) to measure the vertical position of the incoming beam. The operation of the ILC prototype feedback system is described in [3]. Here we report specifically on the BPM processor development.

Figure 2: Schematic of the FONT5 setup at ATF showing the 3 stripline BPM (P1, P2, P3) locations.

Figure 3: FONT5 stripline BPM in ATF2 extraction line.

#### FRONT END PROCESSOR DESIGN

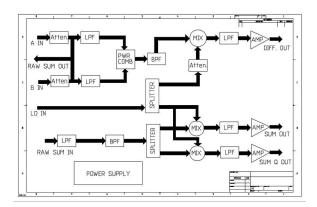

The BPM front-end processing electronics is required to have micron-level resolution with low latency. The design is described in [4,5,6,7]; a schematic is shown in Figure 4

and an actual processor in Figure 5. The top and bottom (y) stripline BPM signals were added and subtracted using a hybrid, to form a sum and difference signal respectively. The resulting signals were band-pass filtered and down-mixed with a 714 MHz local oscillator signal which was phase-locked to the beam. The resulting baseband signals are low-pass filtered. The hybrid, filters and mixer were selected to have latencies of the order of a few nanoseconds, in an attempt to yield a total processor latency of 10ns, figure 6.

Figure 4: FONT analogue signal processor design.

Figure 5: FONT analogue signal processor.

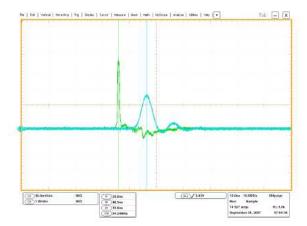

Figure 6: FONT analogue signal processor output (blue) and input signal (green) (Volts) vs. time (each tick is 2ns).

The sum and difference signals are digitised using the fast ADCs on the FONT5 digital feedback board [1]. These ADCs have 14-bit resolution and a maximum sampling rate of 400 MHz. They are clocked at 357 MHz, using a source synchronised to the machine, and have a latency of 3.5 clock cycles. Examples of the digitised sum and difference signals are shown in figure 7. For each channel 164 samples are captured per pulse. The three bunches are clearly seen in the sum signal, and as the beam was approximately centred in the BPM, the difference signal exhibits a residual quadrature component. Before digitisation the sum and difference signals are amplified with 17dB low-noise amplifiers to reduce the contribution of the ADC bit noise to the resolution. The measure of beam position was taken to be the ratio of the digitized difference and sum signals, which is, to first order, independent of the bunch charge.

Figure 7: Example sum (red) and difference (blue) signals showing 3 bunches, for a near zero position in BPM P2.

## **BPM CALIBRATION**

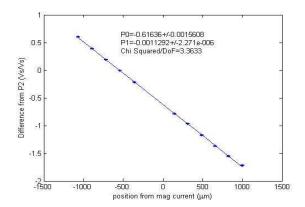

The BPMs were calibrated against upstream dipole corrector magnets. By scanning the current in the corrector magnets, and using knowledge of the optical transfer between the corrector and BPM, the displacement of the beam centroid can be calculated for each magnet current setting. Figure 8 shows an example of such a calibration scan. For beam offsets within a few hundred microns of the electrical centre of the BPM, the BPM processor responds linearly with beam offset, and the calibration constant can be obtained from the gradient of the plotted fit.

## RESOLUTION DETERMINATION

The BPM resolution was calculated from the system of three BPMs, using the measurements from two BPMs to predict the position in the third, and assuming that the three BPMs have similar resolution. For example, the position at BPM P3,  $y_3$ , would be predicted from:

$$y_3 = Ay_1 + By_2 + C$$

where  $y_1$  and  $y_2$  are the positions in BPMs P1 and P2 respectively and A, B, and C are constants determined either from the transfer matrices or from a least-squares fit. The BPM resolution,  $\sigma_{v_1}$  is then given by:

$$\sigma_{v} = \sigma_{resi} / \sqrt{1 + A^2 + B^2}$$

where  $\sigma_{resi}$  is the standard deviation of the residuals from the subtraction of the predicted position from the measured position.

Figure 8: Example BPM calibration: ratio of digitised difference and sum signals vs. position (microns) determined using a corrector (arbitrary zero).

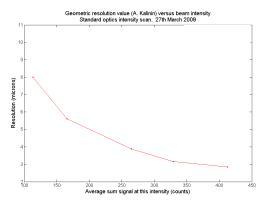

In order to mitigate the effects of beam intensity variation on the position measurement, the measurements were normalized by dividing the difference signal (proportional to the bunch position and bunch charge) by the sum signal (proportional to the bunch charge). The position resolution hence depends on both the position, y, and the charge,  $\Sigma$ , as follows:

$$\sigma_{y} = \frac{1}{\Sigma} \sqrt{\sigma_{\Delta}^{2} + y^{2} \sigma_{\Sigma}^{2}}$$

where  $\sigma_{\Delta}$  and  $\sigma_{\Sigma}$  are the RMS errors on the difference and sum signal respectively. Figure 9 shows the resolution as a function of bunch charge.

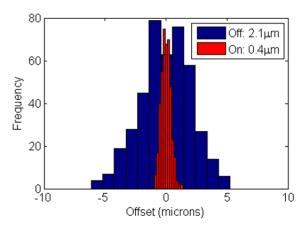

The 3-BPM resolution method routinely yielded consistent resolutions of  $2-3~\mu m$ , for bunch charges ~0.5 x  $10^{10}$  and for beam approximately centred in the three BPMs. However, evidence from the operation of the FONT5 feedback system [1] suggests that the processor resolution must be much lower than this, at least on intrapulse timescales (few hundred nanoseconds). Figure 10, shows the distribution of beam jitter at BPM P2 with the feedback system turned off and turned on. In this case, the uncorrected jitter of 2.1  $\mu m$  is reduced to 0.4  $\mu m$  with the feedback system operating.

To be able to measure this jitter, let alone be able to correct to this level, requires a resolution of less than 0.4 um, and the more stringent condition that the correction must be, at best,  $\sqrt{2}$  times greater than the resolution, implies a resolution of at most 0.3  $\mu$ m. The present hypothesis is that the very low resolution at bunch-to-

bunch timescales (few hundred nanoseconds) is getting washed-out at the timescale at which the 3-BPM resolution measurement is made (a few minutes), due to either or both phase variations in the LO signal, or coherent oscillations of the three bunches, which would affect the processors in different ways.

Figure 9: BPM resolution (microns) vs. bunch charge (ADC counts). 100 counts is equivalent to approximately  $1 \times 10^9$  electrons.

Figure 10: Distribution of vertical beam position at P2 for bunch 2 without (blue) and with (red) feedback. A rolling average is subtracted from each bunch position to remove the effects of position drift from the jitter distributions.

### **REFERENCES**

- [1] ILC: http://www.linearcollider.org/cms/

- [2] http://www-atf.kek.jp/atf/.

- [3] R. Apsimon et al, WEPEB044, these proceedings.

- [4] FONT4: P.N. Burrows et al, Proceedings EPAC06, Edinburgh, UK, June 2006, p. 849.

- [5] FONT4: P.N. Burrows et al, Proceedings PAC07, Albuquerque, NM, June 2007, p. 416.

- [6] FONT4: P.N. Burrows et al, Proceedings EPAC08, Genoa, June 2008, p. 3245.

- [7] FONT4: R. Apsimon et al, Proceedings PAC09, Vancouver, 2009.