DISS. ETH NO. 20930

#### TACKLING OS COMPLEXITY WITH DECLARATIVE TECHNIQUES

A dissertation submitted to

ETH ZURICH

for the degree of

Doctor of Sciences

presented by

#### ADRIAN LAURENT SCHÜPBACH

Master of Science ETH in Computer Science, ETH Zurich

19. April 1981

citizen of Landiswil, BE

accepted on the recommendation of

Prof. Dr. Timothy Roscoe Prof. Dr. Gustavo Alonso Prof. Dr. Hermann Härtig

2012

ii

# Kurzfassung

Diese Dissertation zeigt, dass die erhöhte Betriebssystemkomplexität, die durch die Notwendigkeit entsteht, sich an eine grosse Anzahl unterschiedlicher Rechnersysteme anzupassen, mittels deklarativer Techniken signifikant reduziert werden kann.

Moderne Hardware ist zunehmend unterschiedlich und komplex. Es ist wahrscheinlich, dass sich diese Entwicklung in Zukunft fortsetzt. Diese Entwicklung erschwert den Betriebssystembau. Betriebssysteme müssen sich der Rechnerarchitektur optimal anpassen. Sie müssen den gesamten Funktionsumfang des Rechners ausschöpfen, um die volle Leistung des kompletten Systems zu gewährleisten. Vom Betriebssystem ungenützte, suboptimal genützte oder gar falsch genützte Rechnerfunktionalität führt zu geringerer Leistung des Gesamtsystems. Traditionelle Betriebssystem passen sich durch vorgefertigte Regeln, die im ganzen Betriebssystem verteilt und mit der eigentlichen Betriebssystemfunktionalität vermischt sind, der Rechnerarchitektur an.

In dieser Arbeit argumentiere ich, dass es aus zwei Gründen nicht mehr möglich ist, vorgefertigte Regeln für eine Anzahl bekannter Rechnerarchitekturen mit der Betriebssystemfunktionalität zu vermischen. Erstens garantieren vorgefertigte Regeln nicht, dass alle Rechnerfunktionen vollständig ausgeschöpft werden. Zweitens bedeutet das, dass die Regeln für jede neue Rechnerarchitektur angepasst werden müssen, wobei die Regeln für bisherige Rechnerarchitekturen beibehalten werden müssen. Dies führt zu erheblicher Betriebssystemkomplexität und schliesslich zu einem enormen Anpassungsaufwand. Um dies zu vermeiden, muss das Betriebssystem während der Laufzeit Wissen über die Rechnerarchitektur aufbauen und daraus, durch logische Schlussfolgerungen, die bestmöglichen Anpassungsregeln ableiten. Dies führt zu einfacheren, verständlicheren, pflegeleichteren und leichter anpassbaren Betriebssystemfunktionen und stellt sicher, dass die Rechnerfunktionalität vollständig ausgeschöpft wird.

Der Wissensaufbau und das Ableiten von Anpassungsregeln durch logische Schlussfolgerungen sind mit hoher Programmierkomplexität verbunden. Dies gilt insbesondere, wenn dafür maschinennahe Programmiersprachen, wie zum Beispiel C, verwendet werden. Deklarative Techniken erlauben hingegen, angestrebte Regeln durch eine einfache und verständliche Beschreibung der gewünschten Art der Anpassung, basierend auf Wissen über die Rechnerarchitektur, abzuleiten. Durch die natürliche Beschreibung in höheren Programmiersprachen wird die Programmierkomplexität stark verringert.

Um den Vorteil deklarativer Techniken im Zusammenhang mit Komplexität und Anpassungsfähigkeit in Betriebssystemen zu beweisen, stelle ich in dieser Dissertation verschiedene Fallstudien vor, die, basierend auf deklarativen Techniken, Regeln für die Anpassung an die Rechnerarchitektur, mittels logischer Schlussfolgerungen, ableiten. Die Fallstudien setzen kein Wissen über die Rechnerarchitektur voraus, sondern eignen sich dies während der Laufzeit an.

Das Wissen wird in einem zentralen Wissensdienst des Betriebssystems aufgebaut. Regeln werden in diesem Wissensdienst durch logische Schlussfolgerung abgeleitet. Dadurch, dass die Fallstudien, und somit die verschiedenen Betriebssystemkomponenten, diesen Wissensdienst benützen können, wird ihre Komplexität nochmals deutlich verringert. Es ist somit nicht nötig, dass sich jede einzelne Betriebssystemkomponente mit der Wissensgewinnung und der Ableitung von Regeln beschäftigt. Mit dieser Implementation beweise ich die praktische Anwendbarkeit deklarativer Techniken in Betriebssystemen.

# Abstract

This thesis argues that tackling the increased operating systems complexity with declarative techniques significantly reduces code complexity involved in adapting to a wide range of modern hardware.

Modern hardware is increasingly diverse and complex. It is likely that this trend continues further. This trend complicates the operating system's construction. Operating systems have to adapt to the hardware architecture and exploit all features to guarantee the best possible overall system performance. Not exploiting all hardware features, or using them in a suboptimal or even wrong way, results in lower overall system performance. Traditionally, operating systems adapt to the underlying architecture by predefined policies, which are intermingled with the core operating system's functionality.

In this thesis I argue that for two reasons it is no longer possible to encode predefined policies for a set of known hardware architectures into the operating system. First, predefined policies do not automatically guarantee that hardware features are fully exploited on all hardware platforms. Second, for this reason, predefined policies would need to be ported to many different hardware platforms, while, at the same time, it would be necessary to keep the policies suitable for older platforms. This leads to a significant complexity of operating systems and finally to a high engineering effort, when porting the operating systems must gain hardware knowledge at runtime and derive policies suitable for the current architecture through online reasoning about the hardware. This leads to operating systems code that is simpler, better understandable, more maintainable and easier to port, while ensuring that the operating system exploits the hardware features as best as possible.

Reasoning about hardware and deriving policies is a complex task. This is especially the case, if low-level languages like C are used. Instead, declarative techniques allow deriving policies through a simple description of how to adapt to the hardware based on hardware knowledge gathered at runtime. The natural description in a high-level declarative language reduces code complexity significantly.

To prove the usefulness of declarative techniques in the context of adaptability of operating systems and handling of complexity, I present several case studies in this thesis. The case studies are based on declarative techniques. They reason about hardware and derive policies based on hardware knowledge. The case studies do not assume any a priori knowledge about the current hardware platform. Instead, they gain knowledge at runtime by online reasoning about the hardware.

A central knowledge service stores hardware knowledge and allows the operating system and applications to derive policies according to declarative rules. Because the case studies, and therefore the operating system components, can use the central service, their complexity is again reduced significantly. It is not necessary, that every single component deals with knowledge gathering and deriving policies by itself. It pushes this part to the knowledge service. With this implementation I prove the practical feasibility of applying declarative techniques in real operating systems.

# Acknowledgments

First of all, I would like to thank my advisor, Prof. Dr. Timothy Roscoe, for all his help, for interesting technical discussions and for his invaluable advises and feedback on this thesis. I would also like to thank the entire Barrelfish team for the interesting discussions and nice time. Furthermore I would like to thank Simonetta Zysset for proofreading my thesis and for giving me valuable feedback on the language.

Fortunately, I had the chance of discussing problems with several members of the Systems Group, either in the office, or during lunch. The discussions helped me to look at a problem from a different angle. Special thanks go to Michael Duller, Jan S. Rellermeyer, René Müller, Jens Teubner, Louis Woods, Qin Yin, Philip Frey and Ionut Subasu.

During my time at ETH I also had to do many months of "Zivildienst", causing me a complicated time management. I would like to thank Spital Davos, especially the IT department and the Spitalleitung for their flexibility and also for allowing me to go to conferences during this time. Special thanks go to Florian Steiger, Peter Driedijk, Luzius Valär, Markus Hehli and Monika May. Furthermore, I would like to thank Andi Roveretto and Nadine Krättli for the joyful and funny time at Spital Davos.

Most importantly, I would like to thank my mother Anna, my father Laurent, my sister Letizia and my girlfriend Nadine Duivenstijn for their continuous support and motivation and for always believing in me.

Finally, I would like to thank Dr. Arnold Spescha for always listening to me and for "pushing" me through the Gymnasium, which was the basic step towards this thesis.

## ACKNOWLEDGMENTS

viii

# Contents

| 1 | Intr | oduction 1                                                |

|---|------|-----------------------------------------------------------|

|   | 1.1  | Motivation                                                |

|   |      | 1.1.1 Diversity                                           |

|   |      | 1.1.2 The interconnect network                            |

|   |      | 1.1.3 Managing Hardware                                   |

|   |      | 1.1.4 Managing Applications                               |

|   | 1.2  | Problem Statement and Hypothesis                          |

|   | 1.3  | Goals                                                     |

|   | 1.4  | Contributions                                             |

|   | 1.5  | Structure                                                 |

| 2 | Bac  | ground 19                                                 |

|   | 2.1  | Declarative Techniques                                    |

|   |      | 2.1.1 What is declarative programming?                    |

|   |      | 2.1.2 Declarative languages                               |

|   |      | 2.1.3 Constraint logic programming                        |

|   |      | 2.1.4 CLP programming in ECL <sup>i</sup> PS <sup>e</sup> |

|   | 2.2  | Barrelfish                                                |

|   |      | 2.2.1 The Multikernel                                     |

|   |      | 2.2.2 A Barrelfish "node" 28                              |

|   |      | 2.2.3 Explicit access to physical resources               |

|   |      | 2.2.4 Messaging                                           |

|   |      | 2.2.5 Drivers and services                                |

## CONTENTS

|   | 2.3 | Reason  | ning in operating systems                           | 33 |

|---|-----|---------|-----------------------------------------------------|----|

|   |     | 2.3.1   | Hardware representation                             | 33 |

|   |     | 2.3.2   | Declarative hardware access and configuration       | 34 |

|   |     | 2.3.3   | Resource allocation                                 | 35 |

|   | 2.4 | Declar  | ative reasoning in networks                         | 37 |

|   | 2.5 | Summ    | ary                                                 | 38 |

| 3 | The | system  | knowledge base                                      | 39 |

|   | 3.1 | Introdu | uction                                              | 40 |

|   | 3.2 | Backg   | round                                               | 41 |

|   |     | 3.2.1   | Knowledge                                           | 41 |

|   |     | 3.2.2   | Knowledge bases                                     | 43 |

|   | 3.3 | How d   | loes the SKB help the operating system?             | 45 |

|   |     | 3.3.1   | Purpose                                             | 45 |

|   |     | 3.3.2   | Examples                                            | 46 |

|   |     | 3.3.3   | Common patterns of resource allocation descriptions | 47 |

|   |     | 3.3.4   | When to use the SKB                                 | 49 |

|   | 3.4 | Desigr  | 1                                                   | 50 |

|   |     | 3.4.1   | Design principles                                   | 50 |

|   |     | 3.4.2   | Overall architecture                                | 53 |

|   |     | 3.4.3   | Core                                                | 55 |

|   |     | 3.4.4   | Interface                                           | 56 |

|   |     | 3.4.5   | Facts, schema and queries                           | 58 |

|   |     | 3.4.6   | Data gathering                                      | 59 |

|   |     | 3.4.7   | Algorithms                                          | 62 |

|   |     | 3.4.8   | A note on security                                  | 64 |

|   | 3.5 | Impler  | nentation                                           | 65 |

|   |     | 3.5.1   | Implementation of the SKB server                    | 66 |

|   |     | 3.5.2   | Facts and schema                                    | 67 |

|   |     | 3.5.3   | Datagatherer                                        | 69 |

|   |     | 3.5.4   | Common queries                                      | 70 |

|   |     | 3.5.5   | Startup                                             | 70 |

|   | 3.6 | Client  | library                                             | 71 |

|   |     | 3.6.1   | Using and initializing the library                  | 71 |

|   |     | 3.6.2   | Interacting with the SKB                            | 72 |

|   |     |         |                                                     |    |

Х

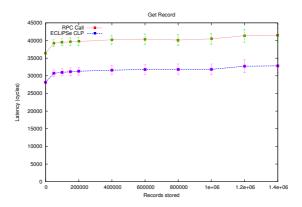

|   | 3.7  | Evalua   | ntion                                         |

|---|------|----------|-----------------------------------------------|

|   |      | 3.7.1    | Code complexity                               |

|   |      | 3.7.2    | Memory overhead                               |

|   |      | 3.7.3    | Performance                                   |

|   | 3.8  | Discus   | ssion                                         |

|   |      | 3.8.1    | Advantages                                    |

|   |      | 3.8.2    | Disadvantages                                 |

|   |      | 3.8.3    | Approaching a configuration problem in CLP 88 |

|   | 3.9  | Summ     | ary                                           |

| 4 | Coo  | rdinatio | on 91                                         |

|   | 4.1  | Introd   | uction                                        |

|   | 4.2  |          | round                                         |

|   | 4.3  | U        | ach                                           |

|   |      | 4.3.1    | Design principles                             |

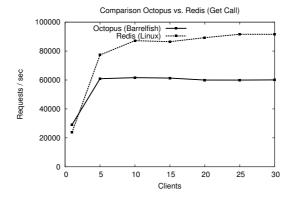

|   |      | 4.3.2    | Octopus                                       |

|   |      | 4.3.3    | Records and Record Queries                    |

|   |      | 4.3.4    | Record Store                                  |

|   |      | 4.3.5    | Publish-subscribe                             |

|   |      | 4.3.6    | Implementation                                |

|   | 4.4  | Use-ca   | ases                                          |

|   |      | 4.4.1    | Synchronization primitives                    |

|   |      | 4.4.2    | Name service                                  |

|   |      | 4.4.3    | Application coordination                      |

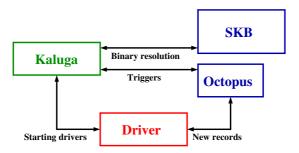

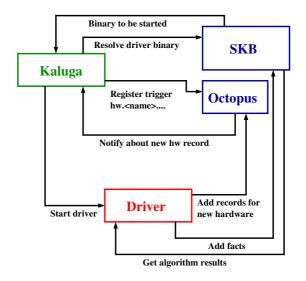

|   |      | 4.4.4    | Device management and system bootstrap 104    |

|   | 4.5  | Evalua   | ntion                                         |

|   |      | 4.5.1    | Code complexity                               |

|   |      | 4.5.2    | Performance                                   |

|   | 4.6  | Summ     | ary                                           |

| 5 | Devi | ice man  | agement 109                                   |

|   | 5.1  |          | a                                             |

|   |      | 5.1.1    | Architecture                                  |

|   |      | 5.1.2    | Driver mapping files                          |

|   |      | 5.1.3    | Hardware records                              |

|   |      |          |                                               |

## CONTENTS

|   | 5.2 | Hardw  | are discovery                                   | . 114 |

|---|-----|--------|-------------------------------------------------|-------|

|   |     | 5.2.1  | Hardware discovery life-cycle in Barrelfish     | . 114 |

|   |     | 5.2.2  | View hotplugging as the default case            | . 117 |

|   |     | 5.2.3  | Minimize basic architecture and platform infor- |       |

|   |     |        | mation                                          | . 117 |

|   |     | 5.2.4  | Device information                              | . 118 |

|   | 5.3 | System | n Bootstrap                                     | . 119 |

|   | 5.4 | Evalua | ution                                           | . 119 |

|   |     | 5.4.1  | Correctness                                     | . 120 |

|   |     | 5.4.2  | Code complexity                                 | . 120 |

|   | 5.5 | Relate | d work                                          | . 121 |

|   | 5.6 | Summ   | ary                                             | . 122 |

|   |     |        |                                                 |       |

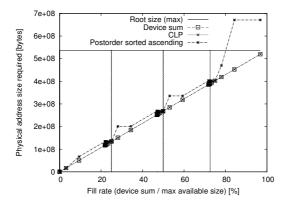

| 6 |     |        | PCI configuration                               | 125   |

|   | 6.1 |        | uction                                          |       |

|   | 6.2 | U      | round: PCI allocation                           |       |

|   |     | 6.2.1  | PCI background                                  |       |

|   |     | 6.2.2  | Basic PCI configuration requirements            |       |

|   |     | 6.2.3  | Non-PCIe devices                                |       |

|   |     | 6.2.4  | Fixed-location PCIe devices                     |       |

|   |     | 6.2.5  | Quirks                                          |       |

|   |     | 6.2.6  | Device hotplug                                  |       |

|   |     | 6.2.7  | Discussion                                      |       |

|   | 6.3 |        | esource allocation                              |       |

|   |     | 6.3.1  | Approach                                        |       |

|   |     | 6.3.2  | Formulation in CLP                              |       |

|   |     | 6.3.3  | Quirks                                          |       |

|   |     | 6.3.4  | Device hotplug                                  |       |

|   | 6.4 |        | pt allocation                                   |       |

|   |     | 6.4.1  | Problem overview                                |       |

|   |     | 6.4.2  | Solution in CLP                                 | 153   |

|   | 6.5 |        | ution                                           |       |

|   |     | 6.5.1  | Test platforms                                  | . 157 |

|   |     | 6.5.2  | Performance                                     |       |

|   |     | 6.5.3  | Code size                                       | 158   |

xii

|   |       | 6.5.4 Handling quirks                                |

|---|-------|------------------------------------------------------|

|   |       | 6.5.5 Postorder traversal comparison                 |

|   | 6.6   | Summary 16-                                          |

| 7 | Effic | ient Multicast Messaging 16                          |

|   | 7.1   | Introduction                                         |

|   | 7.2   | Background                                           |

|   |       | 7.2.1 Multicast messaging                            |

|   |       | 7.2.2 TLB shootdown                                  |

|   |       | 7.2.3 Summary                                        |

|   | 7.3   | Design                                               |

|   |       | 7.3.1 Design principles                              |

|   |       | 7.3.2 Hardware-aware multicast tree                  |

|   | 7.4   | Implementation                                       |

|   | 7.5   | Evaluation                                           |

|   |       | 7.5.1 Adaptability                                   |

|   |       | 7.5.2 Code complexity                                |

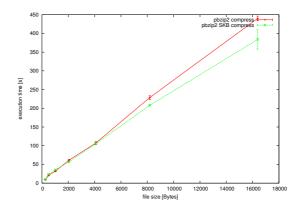

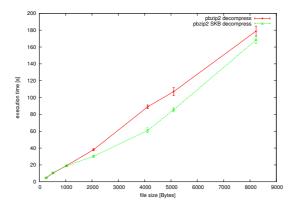

|   |       | 7.5.3 Execution time                                 |

|   |       | 7.5.4 Effective multicast performance                |

|   | 7.6   | Summary                                              |

| 8 | Gloł  | pal Resource Management 18                           |

|   | 8.1   | Introduction                                         |

|   | 8.2   | Background and related work                          |

|   | 8.3   | Model hardware and global allocation                 |

|   |       | 8.3.1 Hardware model                                 |

|   |       | 8.3.2 Application model                              |

|   |       | 8.3.3 Application requirements                       |

|   |       | 8.3.4 Translating requirements to constraints 19     |

|   |       | 8.3.5 Decision variables and concrete topology-aware |

|   |       | allocation                                           |

|   | 8.4   | Resource manager                                     |

|   | 8.5   | Framework to register parallel functions             |

|   |       | 8.5.1 Using the framework                            |

|   |       | 8.5.2 Terminating threads                            |

## CONTENTS

| Bil | oliogr | aphy    |                                    | 233 |

|-----|--------|---------|------------------------------------|-----|

|     | 9.2    | Directi | ons for future work                | 230 |

|     | 9.1    |         | ary                                |     |

| 9   | Conc   | lusion  |                                    | 229 |

|     | 8.9    | Summa   | ary and future work                | 226 |

|     |        | 8.8.2   | Execution time                     |     |

|     |        | 8.8.1   | Code complexity                    | 224 |

|     | 8.8    | Evaluat | tion of the allocation policy code | 223 |

|     |        | 8.7.5   | Summary                            | 222 |

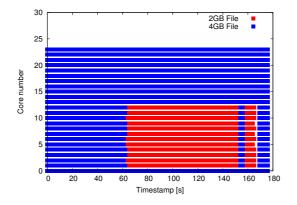

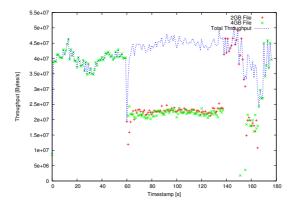

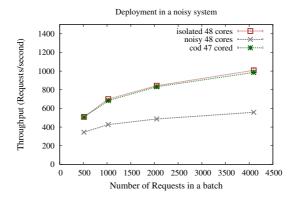

|     |        | 8.7.4   | Evaluation                         | 219 |

|     |        | 8.7.3   | Registering scanning function      | 219 |

|     |        | 8.7.2   | Internal knowledge                 |     |

|     |        | 8.7.1   | Problem                            |     |

|     | 8.7    | Use cas | se 2: Column store                 |     |

|     |        | 8.6.3   | Summary                            |     |

|     |        | 8.6.2   | Evaluation                         |     |

|     |        | 8.6.1   | Architecture                       |     |

|     | 8.6    | Use cas | se 1: pbzip2                       |     |

|     |        | 8.5.4   | Use-cases                          |     |

|     |        | 8.5.3   | Overall architecture               | 208 |

## Chapter 1

# Introduction

This thesis argues that operating systems face a significant challenge to adapt to a wide range of diverse hardware found already today. As the diversity and heterogeneity of hardware is likely to increase, the complexity involved in adaptability and smart decision taking is growing. From a portability and software engineering aspect, it is therefore not possible anymore, to intermangle policies throughout the operating system code. Further, generic policies are not an option, because they do not automatically yield to optimal hardware usage on every platform.

This thesis further argues that the operating system needs to reason online about the current underlying hardware to adapt as best as possible to every platform. Reasoning involves deep knowledge of hardware and can quickly lead to high complexity. Typically, there is a lot of data about hardware. According to Niederliński[97], *data* in a specific context provides *information* about it. The ability to use the information to achieve a specific goal, like, for example, adapting to hardware, leads to *knowledge* about hardware, which can be used to derive informed policies (see also section 3.2.1 for the complete definition).

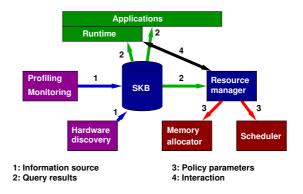

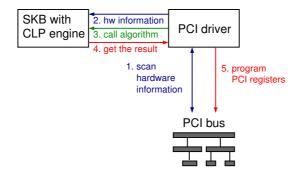

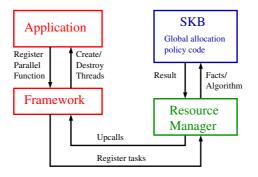

The complexity involved in reasoning and decision taking has to be taken out of the operating system code to enable adaptability and portability to a large set of diverse hardware. This thesis presents the design and implementation of the system knowledge base (SKB), the reasoning facility of the operating system with the goal to reduce code complexity in both, the operating system's mechanism code and the policy code. It is the central place to store knowledge and derive policy parameters online, based on hardware information of the current underlying platform. A clear policy/mechanism separation throughout the complete system enables the programmer to implement policy code and mechanisms separately leading to a much lower complexity and higher portability. Reasoning algorithms rely on high-level knowledge in a machine-independent format and mechanism code is simple, because it does not need to take decisions based on hardware information. For this thesis I chose the ECL<sup>i</sup>PS<sup>e</sup> constraint logic programming system to implement reasoning algorithms, because it is an expressive high-level declarative language and it is easy to port.

The thesis presents concrete use-cases for the SKB, showing what type of data is needed to derive policies and how algorithms transform this data into context-specific knowledge. I introduce and motivate the specific use-cases in the respective chapters while also providing the necessary background and a short use-case-specific evaluation.

The thesis is part of the Barrelfish project[15], a joint work between ETH Zürich, Microsoft Research Cambridge, Microsoft Research Redmond and Microsoft Research Silicon Valley. Parts of the thesis have been published in several papers[17, 18, 48, 49, 106, 107, 116, 117, 118, 144] and I refer to the concrete ones on a per chapter basis. Together with Andrew Baumann and Simon Peter, we created the basic system and formed it into a solid and stable basis for doing operating systems research on top of it. Andrew Baumann contributed mainly on the distributed nature of Barrelfish, including the Multikernel and the capabilities[17] and on Barrelfish's message passing[18]. Simon Peter's PhD thesis[105] is mainly about scheduling in a Multikernel and he also contributed to the capability system, the Multikernel and Barrelfish's message passing. Timothy Roscoe contributed to the Multikernel, the capability system and the message passing while specifically working on Mackerel[114], a device description language and Hake[113], a build system for heterogeneity support. Akhilesh Singhania worked on routing of messages and contributed to the Multkernel and capability system. Jan S. Rellermeyer contributed to the message passing and worked on a name service for named communication endpoints lookups. Pierre-Evariste Dagand contributed an interface description language for message passing[32, 33]. Tim Harris worked on language constructs to facilitate using the asynchronous message passing interface for programmers by avoiding the necessity of "stack-ripped" code[55, 56]. Paul Barham and Rebecca Isaacs mainly worked on message passing and the Multikernel. Pravin Shinde is currently working on high-performance networking based on low-level demultiplexing, new hardware features provided by NICs and user-space network stacks. Kornilios Kourtis is mainly working on scalable file systems. Stefan Kästle is working on possible hardware designs for hardware-based message passing with demultiplexing facilities in hardware providing isolation between message channels on the same core.

## 1.1 Motivation

This section introduces the main reasons for the increased diversity and heterogeneity of current and future hardware. It motivates the need for adaptability to hardware at the operating system's level by showing hardware diversity already found in today's machines.

To improve execution performance of applications on desktop machines and servers, in the past few years the clock frequency of processors could be raised, while keeping the architecture mostly the same. As a consequence, applications ran faster without having had to change them. Now, a critical point has been reached, where it is not possible anymore to simply raise the clock frequency due to physical limitations like, for instance, the heat produced[128, 129]. Instead, a higher degree of parallelism in terms of multiple cores is offered by the hardware to improve performance of applications[22]. This, however, has consequences in the whole hardware design (which I show below), such as specialization of computing units and increased heterogeneity, interconnect topologies and memory hierarchies. This again has implications on the operating system's design.

Nowadays, we have commodity machines with up to 128 hardware

execution contexts (for example four Intel Xeon E7-4870 CPU packages with a total of 80 hardware execution contexts or a SPARC T3 processor with 128 hardware execution contexts) and they are mostly homogeneous in terms of CPU type per system. Current operating systems can deal with this number of cores, even if they originally were not designed for many-core machines. In the future, machines with hundreds of cores are expected to improve the performance even more by providing a high degree of parallelism[22, 58]. This allows desktop machines to run a wide range of compute-intensive applications like, for example, RMS workloads[58]. This trend has implications on the hardware construction side.

Cores are expected to be more specialized to certain functions. Computations will need to be placed on the right core to execute on by the operating system. Not only processor cores, but also special devices like offloading hardware of smart NICs[96], cryptographic accelerators (for example in Sparc T3 processors), FPGAs and GPUs[51] will participate in the computation. The hardware is becoming increasingly heterogeneous and this trend is likely to continue in this direction.

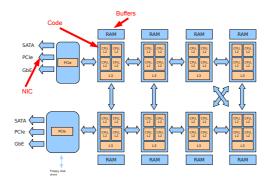

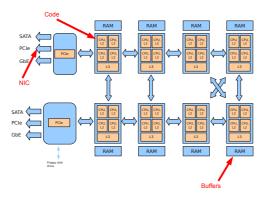

The interconnect between different cores, caches, memory and devices are much more complicated even nowadays and looking at recent trends, the complexity is likely to grow even further. Current interconnects look more like a network than like a bus[18]. Some devices will be near together while the communication between others might be routed over several bridges and switches of the interconnect. Different paths have different characteristics in terms of latency, bandwidth and throughput. Section 1.1.1 shows that there are already clear latency differences in the networklike interconnect.

It is the task of the operating system to assign hardware resources such as CPU cores, memory, accelerators, offloading hardware, devices, disk, interconnect bandwidth or network connections, to applications. The operating system not only needs to multiplex hardware safely, but it also needs to derive smart allocations to exploit hardware features, meet applications' expectations on hardware and finally improve hardware utilization. This is an increasingly difficult task on heterogeneous hardware.

Smart *policies* decide *which* parts of the resources are to be assigned to which computation. The policies become more complex, because, as I

#### 1.1. MOTIVATION

show in chapter 8, they need to include hardware topology knowledge, hardware feature information, and application requirements in order to achieve optimal performance for the overall system.

The operating system is an important part of the software stack. As the thesis argues in the next paragraph and in section 1.2, it is impossible to manually tune software to a set of known hardware. Instead, software needs to adapt automatically to a wide range of divers hardware, where the hardware configuration is not known in advance. Because the operating system is itself an important part of the complete software stack, it also has to adapt itself automatically to the underlying hardware. The operating system must never be the bottleneck in terms of scalability, because its scalability directly affects applications' scalability. Chapter 7 clearly shows how application scalability is affected by the scalability of performing a globally coordinated operating system operation. A poor, nonhardware-aware implementation of an operating system operation, which executes on behalf of the application, limits the application's scalability. Further, it must not prevent applications to extensively use the complete available hardware, even if it is highly heterogeneous. Instead, the operating system's task is to actively support applications to use all hardware as much as possible.

Nowadays, it is not practical anymore to manually tune operating systems and applications for specific many-core systems when deploying them. In a mass-market deployment scenario, there are too many different kinds of hardware types available. Generic policies are not suitable for all kinds of hardware types and do not automatically lead to optimal hardware utilization in all the cases. Instead, operating systems, language runtimes and applications, with help from the operating system, have to automatically adapt to the current hardware in a sensible way. Additional resources should improve performance or at least not decrease it. Additional cores should not cause contentions in the memory system such that performance decreases. Sensible allocations of cores and memory by the operating system is important, independently of the type of hardware the system is currently running on. Furthermore, hardware is shared by many applications. The system has to manage a dynamic set of different long running and interactive applications and cannot statically partition the machine to a fixed set of applications. As I argue in chapter 8, the operating system has to decide how many and which cores to allocate to which application. Similarly it has to decide on memory region allocations per application. The set of hardware systems, on which an operating system and applications might run, increases over time and therefore the topology, available features and characteristics are not known in advance. Applications, and more importantly the operating system and language runtimes, have to adapt at boot-up and runtime to the underlying hardware. Adapting to hardware means deriving the best allocation policies per application according to application provided requirements. Therefore, the operating system needs a smart way to *reason* about the hardware features. These challenges require a smart and general way of incorporating online hardware discovery information and application requirements to derive allocation and hardware usage policies.

So far, there has been little work on commodity operating systems to support heterogeneity from the ground up. This thesis explores techniques to support heterogeneity and, furthermore, to deal with the increased complexity caused by heterogeneity.

The following sections describe the various dimensions of diversity and heterogeneity already found in current commodity systems.

## 1.1.1 Diversity

In this section I define the three dimensions of "diversity" used in this thesis. The classification is important, because in this thesis I explore to what extend the SKB can help the operating system to adapt to the hardware in each dimension. I term the three dimensions *non-uniformity*, *core diversity* and *system diversity*.

#### Non-uniformity

*Non-uniformity* traditionally refers to non-uniform memory access (NUMA) for scalable multiprocessing. The classical definition means that memory

#### 1.1. MOTIVATION

regions are grouped into NUMA nodes and a group of cores belongs to one NUMA node. It is still possible to access memory of a different NUMA node, but at a higher latency. The latency of performing an operation on memory depends on the core performing it. The latency is therefore non-uniform and depends on the combination of core and memory address. Table 1.1 in section 1.1.2 shows that the latency differences are significant.

Nowadays the concept of non-uniformity becomes wider. A hierarchy of cache levels where some cores share a certain cache leads to a nonuniform cache architecture and non-uniform access latencies to cached values.

Multiple cores in a system generate an increased number of memory transactions. Obviously, the memory system has to scale with the number of cores. Therefore, most of today's multi-socket systems are NUMA systems, where a separate memory controller per socket, or even per core, handles memory transactions to a specific NUMA-domain. This leads to fast local memory access, if OS and applications only access local memory.

Caches reduce the number of memory transactions and significantly reduce access latencies. Typical systems today have three levels of caches where the third level is shared by some or all cores of a socket. The cachesharing property is important when the OS has to decide which threads to place on which cores, especially if the operating system would know from the application, whether threads would benefit from a shared cache or not. Also, as I show in chapter 7, some operations are significantly faster, if the fact, that some cores share a cache, is exploited.

Overall, the memory hierarchy including NUMA-domains, caches and cache-sharing is becoming more complex to handle properly by the OS. Only detailed knowledge allows the full benefit of the memory system's design by the OS and applications to be exploited.

#### Core diversity

*Core diversity* refers to the different types of cores within a single system on which a single-image OS will run. Nowadays, most systems still have

uniform cores, but trends are towards having different cores in a single system in terms of power and performance tradeoffs. The ARM big.LITTLE architecture[52] provides four cores of the same instruction set. Two of them are high performance cores and the other two consume low power. The operating system can choose to execute a computation on a highperformance core or on a low-power core. In order to do so, it needs detailed knowledge about the cores, but also about the type of computation. Further, it needs to know, whether the goal at any given moment, is to save power or provide high performance. Instruction set extensions are a another step towards heterogeneity in terms of performance and power tradeoffs[58]. The IBM Cell processor[53] has radically heterogeneous cores. Projects such as HeraJVM[85] and CellVM[99] show how difficult it is to use such a heterogeneous processor. The Intel SCC[62] is itself a homogeneous system in terms of cores, but not in terms of its memory system. An SCC connected to a x86\_64 host provides an additional set of x86\_32 cores on which the OS can run. Barrelfish runs as a single-image OS on an x86\_64 host and the attached SCC[86, 107]. GPGPUs (General-Purpose computation on Graphics Processing Units) is becoming an increasingly hot topic[51]. GPUs are becoming more general-purpose and participate in the computation. CUDA[100] and OpenCL[71] are frameworks which allow the offloading of general-purpose computations to the GPU. The GPU is treated as a device and can only be used by one application at a time. To handle multiple GPUs in the same system, a more advanced task scheduling on GPUs is necessary[125]. The netronom netowrk interface card provides an ARM core on which the OS can run[96]. A while ago, the SunPCi cards[127] provided an x86 based system on a PCI card plugged into a Sun SPARC system. Windows applications run together with the Windows operating system on the SunPCi card. The user interacts with Windows application through a window of the common desktop environment (CDE) or through a separate monitor connected to the SunPCi card. This form of heterogeneity allows users to run applications with different ISA requirements on the same machine, but a single application cannot run partly on both types of processors.

The work in this thesis does currently not place computations according to CPU core features, but it attempts to provide CPU core features (like

#### 1.1. MOTIVATION

floating point capabilities, streaming extensions, power-saving modes) in a high-level abstract and CPU core-independent format, such that future extensions can reason about them at a high-level, without needing to first query every core separately.

#### System diversity

In contrast to non-uniformity and core diversity, the term *system diversity* refers to the fact that two completely separate systems are diverse, even if they are of the same base architecture, like, for example, x86\_64 systems. The number of cores and NUMA regions, the cache hierarchy including cache sharing and the interconnect topology potentially differ significantly between any two systems. Additionally, the available set of devices and accelerators might be significantly different. Therefore, it is impossible to manually tune code for specific machines. Instead, the software, including the operating system, has to adapt to the hardware features in an automated way, such that even future hardware types will be automatically supported. This removes the engineering effort of porting software to future hardware. As I show in chapter 7 and chapter 8, the high-level languages approach allows reasoning about hardware in an abstracted way, such that software automatically adapts to the underlying hardware.

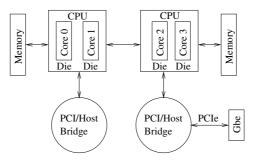

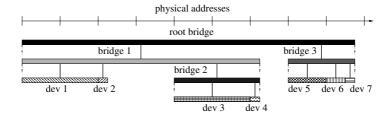

This type of diversity is already present in today's systems. Figure 1.1 shows three different commodity systems available nowadays with completely different interconnects and memory hierarchies.

#### 1.1.2 The interconnect network

Many-core systems often consist of multiple CPU packages which contain multiple cores per package where cores might provide simultaneous multithreading (SMT)<sup>1</sup>. Cores within and between CPU packages communicate over point-to-point links<sup>2</sup>, where local communication within the package is much faster than communication between packages. Additionally, the interconnect graph is not a full mesh and therefore multihop-

<sup>&</sup>lt;sup>1</sup>HyperThreads in AMD

<sup>&</sup>lt;sup>2</sup>QPI for Intel, HyperTransport for AMD

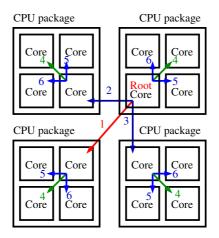

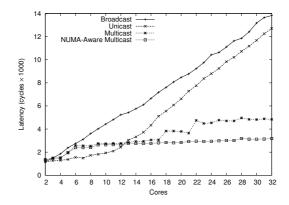

communication is necessary for non-neighbor cores (see figure 1.1(b) for example). Different latencies and the non-fully connected nature of the interconnect graph form a sort of diversity in terms of latency. With these characteristics, the interonnect becomes a network between cores, caches, memory and devices and is not a bus anymore[18]. In this thesis I argue that consequently, the interconnect has to be treated as such and network-type characteristics have to be part of the knowledge about the system. As chapter 7 shows, treating it as a network and performing the right communication optimizations has significant performance impacts. Of course, to derive the right optimizations, not only network characteristics, but also communication pattern knowledge is important.

Figure 1.1 shows three examples of commodity systems with different interconnect topologies and different types of cache hierarchies. Figure 1.1(a) is a Tyan Thunder n6650W board with two dual-core AMD Opteron 2220 processors and 8GB RAM across 2 NUMA nodes. They are interconnected by HyperTransport[64] point-to-point links. Figure 1.1(b) is a TyanThunder S4985 board with M4985 daughtercard and 8 quad-core 2GHz AMD Opteron 8350 processors and 16GB RAM across 8 NUMA nodes. The cores are interconnected by HyperTransport[64] point-to-point links. Figure 1.1(c) is an Intel s5000XVN workstation board with two Intel Xeon X5355 quad-core processors with 8GB RAM on 1 NUMA node. The cores and the memory are connected by the front side bus (FSB) which is a traditional non-NUMA topology. Point-to-point communication over HyperTransport[64] or QuickPath[146] links mean that the inside of a general-purpose computer resembles a network with non-uniform messaging latencies due to different numbers of hops and the different routing depending on the source and destination of messages.

As earlier measurements show[118], there is a significant difference in terms of memory access latencies between access of the local and the remote NUMA nodes (see table 1.1). The increased latency on a remote access is a result of crossing the interconnect to reach the remote memory.

A similar experiment in[18] shows cache access latencies for the sys-

#### 1.1. MOTIVATION

(a) 2x AMD Santa Rosa dual-core processors.

(b) 8x AMD Barcelona quad-core processors.

(c) 2x Intel Clovertown quad-core processors.

Figure 1.1: Different x86-based commodity systems.

| Memory region | Core 0 | Core 1 | Core 2 | Core 3 |

|---------------|--------|--------|--------|--------|

| 0–2GB         | 192    | 192    | 319    | 323    |

| 2–4GB         | 192    | 192    | 319    | 323    |

| 4–6GB         | 323    | 323    | 191    | 192    |

| 6–8GB         | 323    | 323    | 191    | 192    |

Table 1.1: Memory access latencies (in cycles)

| Access      | cycles | normalized to L1 | per-hop cost |

|-------------|--------|------------------|--------------|

| L1 cache    | 2      | 1                | -            |

| L2 cache    | 15     | 7.5              | -            |

| L3 cache    | 75     | 37.5             | -            |

| Other L1/L2 | 130    | 65               | -            |

| 1-hop cache | 190    | 95               | 60           |

| 2-hop cache | 260    | 130              | 70           |

Table 1.2: Latency of cache access for the PC in Figure 1.1(b).

tem in figure  $1.1(b)^3$ . The results in table 1.2) show that accessing caches at deeper levels, or even remote caches, have significantly higher latencies. Boyd-Wickizer *et al.* report similar numbers for a 16-core machine[23].

#### 1.1.3 Managing Hardware

Starting at the bottom, the operating system has to discover, enumerate and initialize hardware resources in such a way that it can best be used by the operating system and finally by applications.

Designing hardware with scalability at the hardware level in mind, increases its complexity. Apart from having many cores and NUMAdomains in systems, other hardware components are replicated for similar reasons (scalability with the size of the system). Nowadays, hardware sys-

<sup>&</sup>lt;sup>3</sup>This experiment has been conducted by Simon Peter

tems have multiple PCIe buses where lots of, increasingly address-space hungry, cards can be plugged-in, even at runtime. Handling address space allocation in PCIe requires a deep understanding of the bus and plugged-in cards, including quirks to apply. Chapter 6 shows how much knowledge about PCIe buses s required in order to correctly configure them. This knowledge has to be created at bootup time, since every system might be different and the bus configuration is not known in advance. Fortunately, the high-level language algorithm, to configure PCIe buses, presented in chapter 6, handles the high complexity of this configuration process well. The increased interrupt load is handled by distributing it through different configurable IOAPIC controllers. Typical systems today have multiple IOAPICs which again have to be initialized and controlled by the operating system. IOAPICs deliver interrupts to specific cores. The destination is configured by the operating system. The destination has to be the core, where the receiver of the interrupt (typically a driver) runs. How to correctly route interrupts is shown in chapter 6. While this chapter discusses how to configure the interrupt hardware with few lines of high-level code, it does not talk about where to run the driver. Deciding where to run a driver depends on its associated device and on which PCIe bus the device is. Each PCIe root bridge is attached via a point-to-point link at the interconnect and therefore is closest to a specific CPU socket. Ideally, the device manager starts the driver on a core close to its associated device. Although the current implementation does not do that, chapter 5 discusses how to decide, where to run the driver based on topology knowledge, in more detail

The operating system not only needs to adapt to CPUs and memory systems, but also to varying PCIe bus configurations, interrupt controller configurations and many more hardware specifics. Again, this stresses the fact that the operating system needs a reasoning facility to derive correct hardware initializations, which are automatically adapted to the hardware configuration found on the platform. The goal is to reduce the code complexity as much as possible.

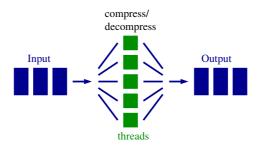

### 1.1.4 Managing Applications

Obviously applications need to be implemented in a multithreaded fashion to benefit from the available hardware parallelism. While this is a challenge by itself, it also imposes requirements on the operating system. First of all, the operating system has to direct applications to create a useful number of threads. I argue in chapter 8 that this requires the operating system to have a global knowledge of the number of cores available, the number of applications and how many threads they wish to run at the same time. Second, the operating system has to place threads on available cores, taking different properties of threads, like, for example, communication between threads, into account.

## **1.2** Problem Statement and Hypothesis

Hardware is changing fast and getting increasingly diverse. The operating system needs to adapt to the underlying hardware, correctly initialize it and exploit it effectively, even if the hardware's architecture is not known at the operating system's implementation time. Traditional operating systems face significant challenges in adapting to the underlying hardware, because often policies are encoded throughout the operating system's code. This is, however, increasingly problematic. First, it is impossible to encode suitable policies for future, not yet known, hardware platforms. Second, encoding policies throughout the operating system's code increases complexity and makes it harder to port the operating system to future hardware platforms, which, however, will be necessary in order to support them.

This thesis investigates how an operating system can adapt to current and future diverse hardware while keeping the complexity low and portability high. This thesis is guided by the following hypothesis:

If the operating system had a facility for reasoning about hardware and software, it could better adapt to a large set of diverse hardware, exploit hardware features and configure software modules to improve overall system utilization, while reducing code complexity in both, the operating system and application components.

## 1.3 Goals

This section defines the main goals of the thesis and lists the main enabling factors to build a facility which allows the operating system to adapt to a wide range of diverse hardware. These goals are important, because they guide design decisions and implementations of the SKB and the use cases. Consequently, the remaining chapters refer to the goals and discuss to what extend they could be achieved. The thesis tries to achieve the goals by building a reasoning facility with the system knowledge base, which can be used by the operating system and by applications.

The main goals are as follows:

- Enable the operating system to adapt to the current underlying hardware

- Reduce code complexity involved in decision taking

- Increase portability to current and future hardware platforms

The main enabling factors are:

- Clear policy/mechanism separation

- High-level declarative language to derive policies

- Central global knowledge processing

## 1.4 Contributions

The thesis investigates how complexity can be handled by applying highlevel declarative language techniques to reason about the underlying hardware. It investigates how a reasoning facility, based on constraint logic programming, is useful to build an adaptive operating system, which automatically adapts to diverse hardware. Further, the thesis investigates how a reasoning facility helps to built services on top of it, which themselves reduce complexity.

The thesis presents several use cases to prove that reasoning in a highlevel declarative language greatly reduces code complexity, both, in policy code and also in the mechanisms. Reasoning about hardware makes the operating system adaptable to the underlying hardware with few lines of code.

The contributions of the thesis are the following:

**High-level reasoning facility helps to build adaptive OSs** The thesis proves that a high-level reasoning facility using a constraint logic programming language (CLP) is useful to build an operating system, which automatically adapts to the underlying hardware. Such a reasoning facility allows deriving hardware knowledge at runtime and deriving policies with low code complexity, such that the operating system adapts to the underlying hardware. The SKB presented in chapter 3 is the software module used to prove that high-level languages are useful to build an operating system which is adaptive to hardware.

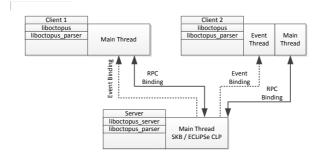

**Services benefit from reasoning and further reduce complexity** The thesis shows that services built on top of a high-level declarative reasoning facility directly benefit from its logical unification and constraint satisfaction techniques. Services become much simpler to build. They exploit the high-level language, store and process knowledge, and further reduce code complexity in the operating system by taking over functionality which otherwise would be intermingled in individual software modules. Chapter 4 presents a name service and synchronization and coordination services built in this way. Chapter 8 explains a resource allocation framework which builds on logical unification and constraint satisfaction.

**Declarative languages reduce hardware configuration complexity** The thesis argues and shows, that correct and complete hardware configurations can be derived with few lines of constraint logic programming code. As such, it argues, that this approach is preferable compared to an imperative approach using a low-level language like C. Chapter 6 proves that with the example of PCIe configuration.

**Declarative reasoning facilitates adapting to hardware** Declarative languages allow deriving policies such that the operating system and applications easily adapt to the underlying hardware. The hardware can be exploited much better, which leads to higher performance. Chapter 7 shows how a hardware-aware algorithm adapts communication within the operating system to the underlying hardware topology in such a way, that communication performance is high and scales well with the number of participants.

## 1.5 Structure

The rest of the thesis is structured the following way. The background for the thesis is given in chapter 2. The system knowledge base is presented in chapter 3. First, the chapter discusses the design principles and then the implementation. Also, the client interface is explained and examples show how to interact with the SKB. Finally, the SKB is evaluated in terms of code complexity and resource usage. Octopus, the coordination service presented in chapter 4, is an extension of the SKB providing distributed coordination facilities within the operating system.

After presenting the SKB and Octopus, four use-cases demonstrate their usefulness. Chapter 5 shows how to build a device manager on top of the SKB and Octopus. Declarative PCI configuration is explained in chapter 6. Chapter 7 shows how to derive a hardware-aware multicast messaging tree declaratively. Chapter 8 presents a framework and a declarative way to allocate CPU cores to a set of running applications. Finally, the thesis concludes in chapter 9.

CHAPTER 1. INTRODUCTION

## Chapter 2

# Background

The first part of this chapter discusses declarative techniques and, in particular, provides some deeper background about constraint logic programming, because this thesis builds on this technique. A better understanding of the basic concepts helps understanding design decisions of the SKB, the policy code shown in the use case sections and the interaction with the mechanism code of the operating system.

The second part of this chapter gives an overview of Barrelfish, because its structure and mechanisms are enabling factors to build a reasoning facility to derive policies outside the operating system's mechanisms. Only the parts relevant for this thesis are discussed to provide the necessary operating system background.

Finally, the chapter surveys successful applications of declarative techniques in the operating systems and networks fields.

## 2.1 Declarative Techniques

As the work of this thesis heavily relies on declarative techniques, this section provides the necessary related background. After an overview of declarative programming in general, the ECL<sup>i</sup>PS<sup>e</sup> [10, 30] constraint logic

programming (CLP) system, in which the work in this thesis is implemented, is explained in more details.

### 2.1.1 What is declarative programming?

Declarative programming is a programming paradigm where the programmer describes *what* he wants, but not *how* to get there[54, 81, 97]. The program describes potential solutions by logic rules without defining the control flow[54, 81]. Complete problems can be described in terms of variables, relations between variables and logic transformation rules to finally achieve a state the programmer would like to get, i.e. the solution to the problem. Typically, problems are described in terms of values, ranges and their dependencies.

Typically, declarative programming eliminates side effects, since the problem can only be described, but no concrete steps to be taken can be defined by the programmer. The concrete steps to be taken are typically defined by the implementation. This allows the implementation to use different techniques like loops or backtracking to search for a solution without exposing the actual technique used to the programmer. It also allows the implementation to change the internal technique, as long as the final solution meets the programmer's expectations. In some cases, the implementation can automatically parallelize the search for solutions, because the control flow is not specified by the programmer and, due to the description, there are no side effects possible<sup>1</sup>.

High-level declarative programming allows expressing complex problems in a descriptive way with few lines of code. It reduces the code complexity significantly, while being extremely expressive. This is one of the main reasons to chose declarative programming techniques when dealing with complexity. As long as a complex problem can be described in terms of rules, a declarative language is a good choice.

There are different classes of declarative programming techniques and corresponding languages, which are explained in more detail in the next

<sup>&</sup>lt;sup>1</sup>In practice, most of the languages allow explicit side effects by providing permanent variables on a heap. This, however, is not the common use of declarative languages.

#### 2.1. DECLARATIVE TECHNIQUES

section.

#### 2.1.2 Declarative languages

This section surveys common declarative programming techniques, which may be suitable in the context of an operating system. As such, it is not a complete list of all declarative programming techniques and languages available, but it helps to understand the reasons why this work builds on constraint logic programming.

The paradigm "declarative programming" includes a range of subparadigms where each of which has a number of languages or programming systems.

*Logic programming* is a well-known form of declarative programming. Prolog[24, 36, 120, 130], as the programming system for logic programming, allows the programmer to describe a problem in terms of information, variables and logical unification rules. The goal is to reason about information and derive knowledge in a specific context. Facts store known pieces of information inside the Prolog runtime. The facts can be accessed by each rule during its complete execution. Variables are unified to constants or facts and possibly to other variables until a solution can be found such that all requirements on all variables are met, or the system recognizes that there is no solution to the problem. Internally, Prolog makes extensive use of backtracking to search the complete search space. Whenever it has to chose a value to assign to a specific variable, it creates a choice point on the stack and follows down a branch of the search tree. It will either output a solution, if there is one, and then backtrack to the choice point or, if there is no solution in the subtree, it will backtrack to the choice point immediately. At every choice point it assigns a new value to the variable and tries another subtree of the search space[2]. Obviously, when the search space is huge, Prolog needs to create a large number of choice points, which will make the search time consuming (or in fact slow). Datalog has its roots in logic programming and is similar to Prolog. Compared to Prolog, there are a number of restrictions in terms of allowed argument complexity and binding of variables, for example. Datalog was designed originally for declarative databases[28].

*Constraint programming* allows the description of a problem in terms of variables and constraints. Constraints relate variables to a range of possible values which the system is allowed to assign to them. This includes restricting a variable to a given set of constant values, but also applying constraints which relate two (or more) variables to each other. Constraints between two (or more) variables create dependencies between them. The dependencies can be created even before any of the variables has a concrete value assigned, which is an important feature on which the algorithms in this thesis rely. An example is a variable whose value has to be greater than the value of some other variable. The constraint is applied to the two variables, before concrete values are known. The solver takes all variables and all constraints into account and only assigns values such that all constraints are met. If there is a solution, it outputs all possible assignments to all variables. Otherwise, it outputs, that there is no solution to the problem.

In *functional programming* the programmer defines *how* a goal should be reached, by defining a sequence of functions to apply to a given input. Functional programming typically has no side-effects. Functions purely operate on input parameters and return the function's output. There is not global state which gets modified by any function during execution<sup>2</sup>. Because there are typically no side effects, the compiler has freedom for radical optimizations, including parallelizing parts of the execution without the programmer having to know about it. In fact, many tools in Barrelfish are implemented in Haskell[57], a purely functional language. For this thesis, functional languages are less appropriate, because the thesis' goal is to reason about information and deriving knowledge, rather than applying functions on information in a well-known order.

### 2.1.3 Constraint logic programming

This section explains why constraint logic programming is suitable to hardware configuration and allocation problems. It lays out why the work

$<sup>^2\</sup>mathrm{In}$  practice, functional languages offer means to store global variables, if really necessary.

### 2.1. DECLARATIVE TECHNIQUES

in this thesis is based on this technique.

*Constraint logic programming* (CLP) unifies constraint programming and logic programming. A CLP system allows the use of logical unification in combination with constraints applied to some of the variables. The logic unification rules prepare the necessary knowledge about the problem to be solved, and the constraints define ranges of valid solutions to the problem.

Programs in CLP are formalized in terms of free variables, facts, logical rules, and constraints. Free variables can be unified to other variables or to stored facts. In CLP, free variables can also be constrained to certain ranges of values assignable to a variable. Constraints indirectly influence the unification process, because only some values can be assigned to a constrained variable. If the unification process tries to assign a value outside the range, it fails and triggers a backtrack. To search a valid solution, the solver enumerates possible values and temporarily unifies a variable to them, until it finds one. Backtracking is expensive, as for regular Prolog programs. The programmer might chose to reduce the number of choice points to limit the number of backtracks performed by the system. This can lead to a much lower execution time.

As for regular constraint programming, variables in CLP can be used and constrained even before concrete values are assigned to them. It is possible to express calculations based on variables with no values yet assigned and constraining the result of the calculation to a range of values. The solver will then search concrete values such that the calculation leads to a result in the given constrained range. Of course, also the result range might come from a calculation of other variables.

When implementing a CLP program, the programmer defines a set of variables and logical unification rules which unify them to stored facts. This step provides the necessary knowledge about the problem. Second, he constrains the variables (possibly just by relating them somehow) to define valid solutions of the problem. Then, the programmer causes the program to invoke the solver which produces valid solutions in the requested ranges and based on knowledge coming from stored facts and unification.

CLP programming forms an ideal basis for hardware resource allocations. Logical unification rules derive hardware knowledge and constraints relate dependencies between pieces of hardware. By understanding hardware properties through the logical reasoning and by relating several pieces of hardware in terms of constraints in variables representing the hardware, the solver is able to find an overall valid resource allocation. The PCIe bus driver in chapter 6 makes extensive use of this technique. The multicast tree construction in chapter 7 and the global resource allocation in chapter 8 also make use of logical reasoning and constraint solving.

## 2.1.4 CLP programming in ECL<sup>i</sup>PS<sup>e</sup>

This section introduces the ECL<sup>i</sup>PS<sup>e</sup> CLP programming system, as the work in this thesis is based on it. The three phases described here need to be followed exactly, otherwise ECL<sup>i</sup>PS<sup>e</sup> might behave in an unexpected way. The technical report on developing applications with ECL<sup>i</sup>PS<sup>e</sup> explains in detail how to correctly develop applications[121].

ECL<sup>i</sup>PS<sup>e</sup> is a Prolog-based CLP system with constraints extensions. It implements an extended version of the "Warren abstract machine" (WAM)[2]. Facts are stored on the heap. Code can be uploaded to the system in source form or can be precompiled byte code. On the first execution, the source code or byte code gets compiled to machine code.

CLP programs in ECL<sup>i</sup>PS<sup>e</sup> follow three phases. First of all, the appropriate data structure with necessary variables should be constructed in such a way, that the data structure models the problem in a natural way. This includes rules to match variables with stored facts. In a second step, constraints should be applied to the variables. During this step, no back-tracking should be performed, as that would cause the system to create new variables. While this is fine for pure Prolog, where facts are unified to the new variables, it does not work for ECL<sup>i</sup>PS<sup>e</sup> programs. Constraints are attached to concrete variables and do not get attached automatically to newly created variables by the system, even if the new variable logically holds the same value. Therefore, a programmer has to be careful about that. In the last step, a rule has to invoke the solver and tell it which variables should be instantiated with concrete values. This means, that the solver enumerates the passed set of variables with the valid range of val-

### 2.2. BARRELFISH

ues according to the constraints. Potentially, this trigger backtracks until a solution can be found. During that phase, the logical unification rules provide the necessary knowledge such that the solver can relate variables to each other and to stored facts.

As soon as the system finds a solution, it outputs it and stops searching for further ones. The choice points, however, remain and the caller has the option to trigger the solver to search for further solutions. Alternatively, all solutions can be searched by using the goal findall/3. This produces a list of all possible solutions. The risk is, that this takes a lot of time as the search space might be large and the number of valid solutions might be huge.

## 2.2 Barrelfish

Barrelfish has the right operating system structure to run on a large, possibly non-coherent, heterogeneous hardware system. Its structure further allows deriving policy parameters outside the core operating system code, a property which is important for the work in this thesis. The thesis therefore uses Barrelfish to evaluate the declarative language approach to make an operating system adaptable to the underlying hardware. The declarative reasoning algorithms in this thesis derive policy parameters which can directly be used in Barrelfish's mechanisms. The techniques presented in this thesis are however not bound to Barrelfish. They can be used in other operating systems in a similar way if the mechanisms of the operating system allow using policy parameters derived outside the mechanism code.

Because the thesis uses Barrelfish to evaluate the declarative language approach for reasoning about hardware and for adapting to it, this section explains Barrelfish's structure and its most important properties relied on by this thesis.

Barrelfish is a new operating system for heterogeneous many-core systems written from scratch. It implements a new OS architecture, the *mul-tikernel*[17], presented in the next section.

## 2.2.1 The Multikernel

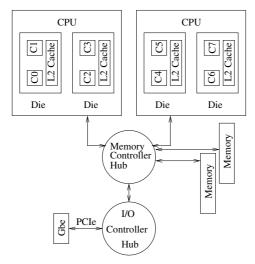

The multikernel[17] is a new OS architecture designed for modern and future heterogeneous many-core systems. It is structured as a distributed system where one operating system node runs on one specific CPU core. This structure naturally matches the underlying hardware, which increasingly resembles a network[18]. Furthermore, it naturally supports hardware heterogeneity, as every core runs a separate operating system node (see section 2.2.2).

The multkernel is guided by the following three design principles:

- Make all inter-core communication explicit

- Make OS structure hardware-neutral

- View state as replicated instead of shared

These three design principles allow structuring an OS in a way that it naturally supports hardware heterogeneity, scalability and the ability to adopt distributed systems principles to improve performance and interconnect usage. The multikernel builds the foundation of running on heterogeneous hardware. It provides mechanisms to execute tasks on the available CPU cores, but it does not decide by itself, on which core a task should be executed. The decision has to be made outside the operating system. This is one feature on which the work in this thesis relies.

Figure 2.1 shows the multikernel model. The three design principles are explained in more detail in the following sections.

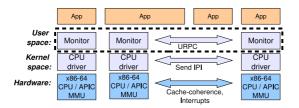

### Make all inter-core communication explicit

The multikernel makes all communication explicit. State is kept completely local and no memory is shared between code executed on different cores. Explicit messaging facilitates reasoning about the interconnect usage. The knowledge of *who* is accessing *what* parts of states and *when* it is accessing the state, is exposed. In contrast, a shared-memory-based

### 2.2. BARRELFISH

Figure 2.1: The multikernel model

system with implicit messaging, such as the shared memory itself or the cache coherence messages, does not have this explicit knowledge.

The explicit knowledge of when messages are sent over the interconnect allows creating efficient communication primitives by deriving policies defining from which source to which destination messages should be sent. Because it is explicit, messages are only sent as requested by the policies. Chapter 7 makes use of this explicit communication between cores.

## Make OS structure hardware-neutral

The multikernel is structured such that most of the operating system is separated from the hardware. Only two aspects are specific to a target architecture. The first aspect is the message transport mechanism and the second aspect is the interface to devices and CPUs. Having only these two aspects hardware dependent, has a number of advantages.

Running the OS on a different architecture with different characteristics in terms of performance or hardware interface, including message transport mechanism, there is no radical code change necessary to make the system work well. Messaging can be implemented as user-level RPC or on hardware message facilities, in case the hardware supports this feature. The higher-level interface to the messaging system does not need to change, and especially the OS structure does not change, if a new message transport is used.

Moving to a completely new architecture requires modifying drivers according to the new hardware interface. In the multikernel model, CPUs are treated as devices and their device driver is a small kernel, called the *CPU driver* (see section 2.2.2). Therefore, it is sufficient to exchange all drivers and ensure that the appropriate message transport is used to make the system run on a new target architecture.

In the future, these benefits are increasingly important as diversity in hardware is likely to grow, which makes it impossible to radically restructure the OS on every deployment. A multikernel is prepared to easily adapt to diverse hardware.

## View state as replicated instead of shared

By keeping all state local to every core, there is no shared state at all. Decisions are based on local data structures and updates are performed on the same local data structures. In case that multiple cores have to coordinate and maintain a global view, messages are exchanged between them to update the same piece of information in the respective local data structures. By making replication a part of the multikernel, heterogeneity support comes naturally. Cores with different endiannesses, for example, can communicate by messages and do not need to take care of the different endianness, as no sharing occurs. A second advantage is that cores can be hotplugged or shut down to save power without complicating the maintenance of shared data structures. A limited amount of sharing, for example between cores on the same package, could be seen as a local optimization of replication.

## 2.2.2 A Barrelfish "node"

This section briefly describes Barrelfish's implementation of the multikernel, because the thesis is about heterogeneity support and builds on the concrete structure of Barrelfish. Further, the hardware discovery process,

### 2.2. BARRELFISH

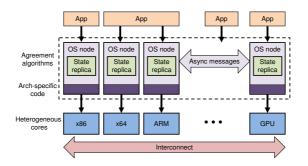

Figure 2.2: The structure of Barrelfish

described in section 5, requires a basic understanding of the actual implementation of a Barrelfish node.

Barrelfish is an implementation of the multikernel model. As such, it runs one separate operating systems node per core without sharing any memory between nodes. The implementation of an operating system consists of two parts. There is the *CPU driver* running in supervisor mode and on top of it, there is the *monitor* running in user mode. Figure 2.2 shows the structure of Barrelfish.

The *CPU driver* is capable of executing privileged instructions. Traditionally, it would be called kernel, but in Barrelfish, a CPU core is treated as any other device and therefore the kernel is the driver of a CPU core. The CPU driver offers a small number of system calls, for example to map a physical memory page into an application's virtual address space. The CPU driver checks first, whether the right to perform the operation has previously been granted to the application. All state is kept purely local to the core, meaning that no memory is being shared with other CPU drivers. Also, the CPU driver does not perform any communication to remote cores.

The *monitor* is the user-level part of a Barrelfish node. It is responsible for maintaining a consistent view of the whole operating system. It does not share any memory with other cores, but instead uses messages to synchronize state among the cores. The monitor offers additional functionality to applications. Applications can ask monitors to forward messages to applications on other cores. Finally, the monitor is able to send capabilities to a remote core.

Because neither the CPU driver nor the monitor share memory with other cores, Barrelfish does not rely on cache coherence. It only needs a way to send messages from one core to another. This may be implemented on shared memory, but hardware messaging features may also be used. As such, Barrelfish is ready to run on future hardware, which is potentially not fully cache-coherent.

## 2.2.3 Explicit access to physical resources