### **OECD** publishing

## CHIPS, NODES AND WAFERS A TAXONOMY FOR SEMICONDUCTOR DATA COLLECTION

August 2024

This paper was approved and declassified by written procedure by the Digital Policy Committee (DPC) and the Committee on Industry, Innovation and Entrepreneurship (CIIE) on 26 July 2024 and prepared for publication by the OECD Secretariat.

#### Note to Delegations:

This document is also available on O.N.E. Members & Partners under the reference code: DSTI/DPC/CIIE(2024)1/FINAL

This document, as well as any data and map included herein, are without prejudice to the status of or sovereignty over any territory, to the delimitation of international frontiers and boundaries and to the name of any territory, city or area.

Cover image: © HAKINMHAN/Shutterstock.com

© OECD 2024

The use of this work, whether digital or print, is governed by the Terms and Conditions to be found at: <u>https://www.oecd.org/termsandconditions</u>

## Foreword

The semiconductor value chain is susceptible to disruptions that pose a considerable risk for modern economies. Better data are essential for policy makers to identify bottlenecks, monitor the balance between demand and supply of specific semiconductor types, and manage disruptions. This paper sets out a common taxonomy for semiconductor types and production facilities, to facilitate harmonised data collection and sharing. The taxonomy distinguishes semiconductor products into four broad categories – "logic", "memory", "analog" and "others" – and sub-categories based on their prevalence and specific functions. Semiconductor production facilities are classified according to the technology used and ability to produce different types of semiconductors, the installed production capacity, as well as other relevant plant (and firm) characteristics. This taxonomy will be the basis for a semiconductor production database and will be revised in the future, keeping up with developments in semiconductor technology.

This paper was written by Chiraag Shah, Charles-Édouard Van de Put and Filipe Silva, under the direction of Audrey Plonk, Guy Lalanne and Verena Weber. The authors gratefully acknowledge feedback provided by the Semiconductor Informal Exchange Network participants as well as Angela Attrey, Gallia Daor, Gregory LaRocca, David Kanter, Jan-Peter Kleinhans, Tobias Proettel, Lea Samek, Sara Romaniega Sancho and Andy Sellars on the draft taxonomy and earlier versions of this document. The authors also thank Anaísa Gonçalves and Shai Somek for their support.

## **Table of contents**

| Foreword                                                                                                                                                                                                              | 3                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Executive summary                                                                                                                                                                                                     | 6                          |

| Introduction                                                                                                                                                                                                          | 7                          |

| 1 Scope for the taxonomy and semiconductor production database<br>A primer on the semiconductor value chain<br>Goals and policy questions<br>Principles for a semiconductor production database                       | 8<br>8<br>10<br>12         |

| 2 Semiconductor manufacturing: Process, technologies and products<br>Main types of technologies<br>Types of semiconductors                                                                                            | 14<br>14<br>17             |

| 3 Existing taxonomies for semiconductors<br>SEMI<br>World Semiconductor Trade Statistics (WSTS)<br>Compound Semiconductor Applications (CSA) Catapult<br>IEEE Taxonomy of Emerging Memory Devices<br>Other taxonomies | 20<br>20<br>22<br>22<br>23 |

| 4 Proposed taxonomy for semiconductors<br>Building the evidence base: a taxonomy for a semiconductor production database<br>A taxonomy for semiconductor types                                                        | 25<br>25<br>30             |

| 5 Future work                                                                                                                                                                                                         | 32                         |

| References                                                                                                                                                                                                            | 33                         |

| Annex A. HS codes relevant to semiconductors                                                                                                                                                                          | 36                         |

| Endnotes                                                                                                                                                                                                              | 37                         |

#### **FIGURES**

| Figure 1. Semiconductor production stages                             | 8  |

|-----------------------------------------------------------------------|----|

| Figure 2. Share of semiconductor and primary value added demand, 2018 | 10 |

| Figure 3. Transistor types: Planar vs FinFETs vs. GAAFETs             | 16 |

| Figure 4. Memory types of semiconductors                              | 19 |

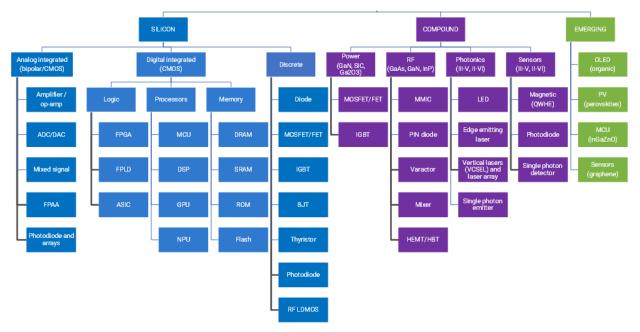

| Figure 5. Catapult semiconductor taxonomy                             | 22 |

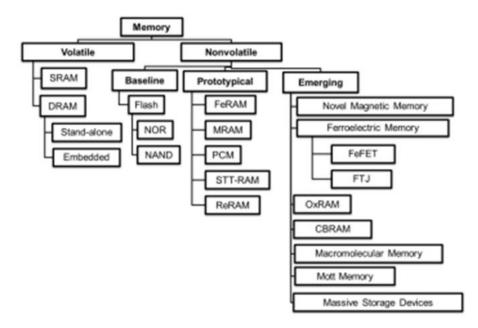

| Figure 6. IEEE's memory taxonomy                                      | 23 |

| Figure 7. OECD's proposed semiconductor production taxonomy           | 27 |

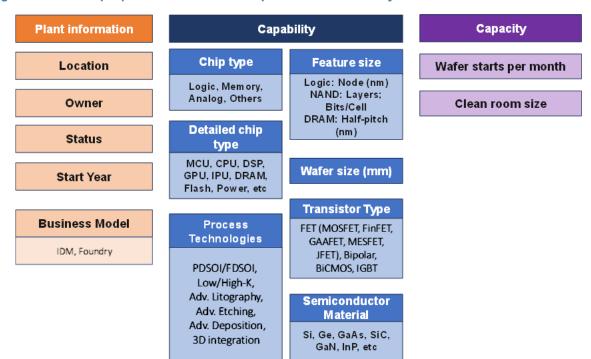

| Figure 8. Capability in chips fabs                                    | 27 |

| Figure 9. Aggregated and detailed taxonomy for semiconductor types    | 30 |

| TABLES                                                                |    |

| Table 1. Summary of WSTS' categorisation and product definitions      | 21 |

| Table 2. Semiconductor production database variables and definitions | 28 |

|----------------------------------------------------------------------|----|

| Table 3. Attributes of transistor type and process technologies      | 29 |

|                                                                      |    |

Table A A.1. HS codes relevant to semiconductor products

36

## **Executive summary**

Semiconductors power modern economies and are integral to a myriad of advanced industrial products. Semiconductors are present in smartphones, computers, cars, home appliances, medical equipment, LED lights, or lasers, just to name a few. They encompass a diverse range of complex components, from advanced logic semiconductors enabling advanced computing and memory semiconductors for data storage, to basic sensors used in temperature measurement. Semiconductor manufacturing can be extremely complex, for example requiring advanced lithography machines to print on features measured in nanometres and cleanrooms with strict control over airborne particles.

In spite of its critical importance, the semiconductor value chain is susceptible to disruptions. The semiconductor value chain is highly segmented into production stages taking place in different geographies, but with each stage often characterised by high geographical concentration. This poses a considerable risk for modern economies.

Enhancing the resilience of the semiconductor value chain, requires evidence-based policy making. Better data are essential for policy makers to identify bottlenecks, monitor the balance between demand and supply of specific semiconductor types, and manage disruptions in value chains.

The OECD Semiconductor Informal Exchange Network (hereafter the Network), convened in June 2023, brings together senior government officials to facilitate transparency and information exchange on semiconductor value chains. Informed by its exchanges and in view of different semiconductor taxonomies used across different economies, this paper sets out a common taxonomy for semiconductor types and production facilities (plants), to facilitate harmonised data collection and sharing.

The taxonomy was developed by the Network and distinguishes semiconductor products into four broad categories – "logic", "memory", "analog" and "others" — and sub-categories based on their prevalence, specific functions and end-uses. Semiconductor production facilities are classified according to the technology used and ability to produce different types of semiconductors (capability), as well as the installed production capacity. It also includes information on geographic, demographic and other relevant plant (and firm) characteristics.

This taxonomy will be the basis for a semiconductor production database. The taxonomy may therefore need to be revised in the future, keeping up with developments in semiconductor technology. Future extensions to the taxonomy could include, conditional on data availability, additional information on semiconductor firms, on end uses for semiconductors, or on semiconductor substitutability.

## Introduction

The work of the OECD Semiconductor Informal Exchange Network (hereafter the Network)<sup>1</sup> pointed to the importance of developing a taxonomy for types of semiconductors and production facilities (plants) to allow for harmonised data collection and sharing. A harmonised approach to data collection supports the objectives of the Network to increase the understanding about semiconductors and help members move towards more resilient semiconductor value chains. This paper provides the common semiconductor taxonomy developed by Network and lays down future work based on semiconductor production data.

The complexity and distributed nature of the semiconductor value chain is one of the key challenges to improving transparency and understanding. Developing a taxonomy for classifying semiconductor data that enables data integration and covers all stages of the production process is both important but also a challenging and resource-intensive endeavour. Therefore, the Network is pursuing a two-pronged approach to the work on semiconductor data: i) conduct analyses focused on semiconductor fabrication/front-end manufacturing stage; ii) map the semiconductor ecosystem, including key upstream and downstream activities in the semiconductor value chain.

This paper provides a taxonomy for front-end manufacturing, laying the basis for analytical work on facilities, processes and products from this stage. Experience from the recent 2020-2022 semiconductor shortages and related analysis suggest that this stage can be an important bottleneck in the value chain (Haramboure et al., 2023<sup>[1]</sup>). Nevertheless, other segments in the value chain can also present bottlenecks, notably when the supply of certain inputs is found to be highly concentrated.

After describing the scope and objectives for the chips and fabs taxonomy and the semiconductor production database (Section 1), this paper provides an overview of the semiconductor production process (Section 2), including the key inputs, technologies, chip types, and the end-use markets to help inform the taxonomy. Section 3 outlines different approaches to classifying semiconductor production facilities and products. Section 4 presents the Network's proposed taxonomy for classifying semiconductor *product types (chips)*<sup>2</sup> and *plants (fabs)*, and the elements of a semiconductor production database to support the Network's objectives described previously in Section 1. Information on statistical classifications relevant to the semiconductor industry is provided in Annex A.

# **1** Scope for the taxonomy and semiconductor production database

This section briefly defines the semiconductor value chain. It then explains the purpose of the chips and plants taxonomy and the principles for a semiconductor production database.

#### A primer on the semiconductor value chain

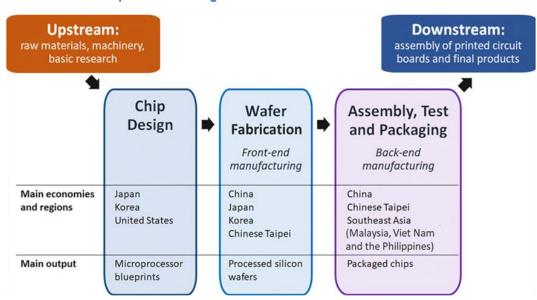

The semiconductor value chain consists of three core stages described in Figure 1:

- *Design*: This stage includes setting the requirements of the chip, designing its architecture, and validating its design on a test bench.

- Fabrication: Building on a wafer of semiconductor material (typically silicon, see Section 2 for other materials), this stage consists in printing (or "etching") the integrated circuit designed in the previous stage on the wafer. Occurring at a wafer fabrication plant ("fabs"), fabrication relies on many complex advanced manufacturing processes using manufacturing equipment and chemicals.

- Assembly, Test and Packaging (ATP): This stage involves slicing the wafers into individual chips, packaging the chips into frames or resin shells, and testing them.

#### Figure 1. Semiconductor production stages

Source: Haramboure, A. et al. (2023), "Vulnerabilities in the semiconductor supply chain", OECD Science, Technology and Industry Working Papers, No. 2023/05, OECD Publishing, Paris, https://doi.org/10.1787/6bed616f-en.

Semiconductor firms have different business models. Integrated Device Manufacturers (IDMs) integrate all three core production stages while other firms specialise in a single stage, as part of out-sourcing and specialisation strategies. For example, "contract foundries" (also known as "pure-play foundries") specialise in the fabrication of chips (front-end) designed by other firms. "fabless" firms focus only on chip design. Similarly, Outsourced Semiconductor Assembly and Test (OSAT) firms focus only on the third and last production stage (back-end).<sup>3</sup>

The core semiconductor value chain relies on critical upstream inputs, including: specialised software (Electronic-Design Automation, EDA), intellectual property necessary to design processor architecture, raw materials (e.g. silicon, rare earth minerals, platinum group metals, gallium, germanium), chemicals and gases, and capital equipment (deposition and lithography tools, metrology, and inspection equipment) – see Haramboure et al. (2023<sub>[1]</sub>); Kleinhans and Baisakova (2020<sub>[2]</sub>) for further details.

The Emerging Technology Observatory's Semiconductor Supply Chain Explorer (ETO, 2022<sub>[3]</sub>) provides an interactive overview of the essential inputs involved at each stage of the chip manufacturing process.<sup>4</sup>

#### Steps in the front-end manufacturing/semiconductor fabrication process

Key steps in the fabrication process for chips include the following (Timings, 2021[4]):

- 1. *Deposition*: Depositing thin films of conducting, isolating or semiconducting materials on a silicon wafer.

- 2. Photoresist coating: Covering the wafer with a light-sensitive coating.

- 3. *Lithography*: A photolithography tool passes light through a photomask to draw patterns into the silicon wafers, creating the tiny circuits that comprise semiconductors.

- 4. *Etching*: Removing the degraded photoresist to reveal the intended pattern, using either gases (dry etching) or chemicals (wet etching).

- 5. *Doping*: Introducing impurities into the semiconductor crystal to deliberately change its conductivity. This can be achieved by diffusion (inducing the movement of impure atoms from areas of high concentration to low concentration) or ion implantation (bombarding the silicon wafer with positive or negative ions to create transistors).

#### Advanced packaging blurs the line between front- and back-end manufacturing

The introduction of advanced packaging techniques, such as heterogeneous integration and silicon stacking, allows for multiple integrated circuits (IC) in the same package, enhancing chip performance beyond traditional geometric scaling. The trend for increasing integration within a single chip package (as an alternative to multiple chips on a circuit board) is also driven by product cost engineering (Bailey, 2024<sub>[5]</sub>).

The advanced packaging market is dominated by fan-out wafer-level packaging with about 60 percent market share (Burkacky, Kim and Yeom, 2023<sub>[6]</sub>), but newer technologies include 2.5-D or 3-D stacking, integrated fan-out (InFO), and system-on-chip technologies, enabling the stacking of chips or wafers vertically with an interposer connecting the stacked chips (Burkacky, Kim and Yeom, 2023<sub>[6]</sub>). There are several categories of 2.5-D and 3-D stacking, based on the kind of interposer used, and different manufacturers use different interposer technologies (Patel, 2022<sub>[7]</sub>; Burkacky, Kim and Yeom, 2023<sub>[6]</sub>). TSMC leads the market with their chip-on-wafer-on-substrate (CoWoS) technology, which is the most popular packaging technology for advanced logic chips, including those used in artificial intelligence (AI) applications.

Advanced packaging is relevant to front-end manufacturing because the interposer must be fabricated, which can be done in-house by foundries (Patel, Xie and Wong, 2023[8]), in addition to OSAT firms.

Recent developments in technology also include '3D integration', which consists in bonding directly the chips at the front-end stage (e.g. copper-to-copper bonding). 3D-integration also requires a specific design of the bonded chips. Developments in low-temperature bonding and ultra-thin device layer stacking are examples of a fast-moving technological frontier for 3D-ICs.

#### End-uses for semiconductors

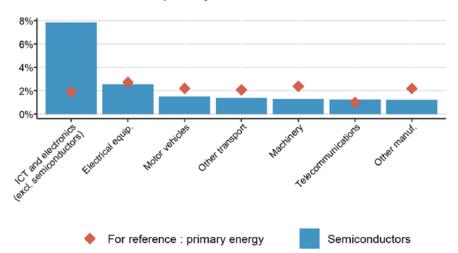

Semiconductors are a critical input into production in a wide range of industries. For example, in telecommunication equipment or motor vehicles, the value of semiconductors embodied is about as important as energy costs (Figure 2).

Note: The semiconductors share of value added to final products in each industry is shown in blue, with the red dot indicating the value added of primary energy (includes coal, oil and gas) in that industry for comparison purposes. The sample is restricted to the 20 leading purchase economies. For instance, semiconductors represent 1.5% of the value added in motor vehicles, only slightly less than primary energy (2%). Source: Haramboure, A. et al. (2023), "Vulnerabilities in the semiconductor supply chain", OECD Science, Technology and Industry Working Papers, No. 2023/05, OECD Publishing, Paris, <u>https://doi.org/10.1787/6bed616f-en.</u>

Generally, most analysis of semiconductor demand focuses on six main end-use markets: computing/data processing, consumer goods, communications, automotive, industrial goods, government/military.<sup>5</sup> Computers and other consumer electronics account for most of the demand for all semiconductors. Electrical equipment, followed by the automotive sector, other transport equipment, industrial machinery, as well as telecommunications are key chips using sectors. The production of medical devices is also an important using sector (OECD, 2019<sup>[9]</sup>).

#### Goals and policy questions

By focusing on improving transparency and information sharing on front-end manufacturing, the taxonomy presented in this paper provides the basis for a database underpinning analyses to address the following key questions.

#### Where are the production facilities for front-end manufacturing located?

Analysis under this workstream would draw on fab data to help shed light in which countries semiconductor production capacity is located. Answers to this question would contribute to understand the extent of market concentration and thus identify potential bottlenecks. Moreover, data on the location of front-end manufacturing facilities currently being planned or underway could provide insights on whether recent policy efforts (e.g. policy strategies and instruments) are helping diversify semiconductor production and reduce the risks of bottlenecks in the future.

#### How is the balance between semiconductor demand and supply expected to evolve?

These data could also help identify segments where installed capacity is growing faster than demand, and therefore creating risks of excess capacity and unnecessary redundancies, based on the availability of demand data. This analysis would help policy makers understand in which types of chips investments should be encouraged, with a view building a more resilient overall value chain.

Building on front-end manufacturing capacity information and semiconductor demand developments and forecasts, the analysis could help monitor industry cycles and anticipate shortages and gluts. Furthermore, the taxonomy will facilitate distinguishing between different semiconductor product types (Section 4), with the level of product type granularity depending on the availability of both production capacity and demand data at the same level of granularity.

#### What is the potential for substitution?

It is important to understand if and where production is substitutable between fabs in order to build more resilient value chains.

Addressing this question would help better understand the degree of flexibility in front-end chip manufacturing to cope with supply-demand imbalances for certain chips, including in the event of localised disruptions and other shocks.

Comprehending substitutability is critical when planning for managing worst-case disruption scenarios. There are two important dimensions to substitutability:

- **Chip substitutability** refers to whether one specific chip in an end-product can be substituted by another to perform the same functions with a minimal loss in performance.

- **Fab substitutability** refers to whether the production of one chip can be switched to another plant, and if so, the range of chips that can be produced with the same available fab equipment and facilities (or with minor tweaks).

#### Chips substitutability

Substitutability across chips — i.e. whether a specific chip can be replaced by a different chip for performing the same functions in an end-use product — is dependent on their use in downstream industries and products. Substituting one chip for another is not straightforward and often requires re-designing the system — either the printed circuit board (PCB) and/or re-writing software. In addition, trust in suppliers and security concerns are key considerations for downstream industry users that might also limit the ability to substitute specific chips (Sperling, 2022<sub>[10]</sub>).

Substitutability might be less challenging for simpler chips, for mature chip types and for uses where software has evolved at a slower pace, and future work could consider whether there are readily available substitutes within certain types of simpler and mature chip types. Part of the analyses on substitutability

would also need to take into account the dependence on critical semiconductors of certain applications and industries. Moreover, chip performance (and that of the end-use product) would need to consider efficiency, capacity and capability, for example building on well-established standard performance tests and benchmarks.<sup>6</sup> However, a detailed analysis based for example on metrics on chemical resistance and operating temperature range would be deemed too technical and outside the scope of this Workstream.

#### Fab substitutability

Whereas understanding chip substitutability would provide insights on alternative sources of chips in the event of a value chain disruption, the key to managing disruptions is substitutability across fabs, including information on where potential substitute fabs are located.

While part of the analyses required to understanding fab substitutability relate to technological capacity, economic considerations also play an important role. Economic considerations include, for example, capital investments required, lead time to change production lines and production costs of the relevant fabs.

#### Principles for a semiconductor production database

This section presents a set of proposed principles for developing the semiconductors production database. These principles reflect a prioritisation that would help attain the objectives outlined above.

- Trust. The taxonomy, any data sharing activities and resulting databases developed in the context

of the Network should build on co-operation and trust amongst governments and stakeholders in

the semiconductor industry to ensure that data and related analyses meet shared goals.

Respecting constraints associated with sharing granular industry data would be particularly

important to building trust with stakeholders.

- Availability. The taxonomy should reflect available data. Areas for which data are not available

are not included. Areas for which data availability is very limited are identified as such and, as in

any database, there may be numerous missing values. Data analyses are only possible insofar as

data are available. Any data collection efforts should complement and rely on, rather than duplicate,

existing data efforts by governments, industry and other stakeholders.

- **Comparability**. Comparison across classifications used in different economies and jurisdictions should be as simple and easy as possible. A taxonomy should also be consistent over time, thus allowing for analysis that can build on historical data.

- **Tractability**. Semiconductor manufacturing processes are highly complex. The taxonomy should strive to simplify as much as possible to obtain a tractable taxonomy, noting that this may lead to nuanced differences in semiconductor manufacturing processes and products being obscured.

- Adaptability. The taxonomy should be able to adapt as semiconductor production processes and products evolve, keeping abreast of innovation and limiting the needs for revisions of the taxonomy, but without prejudice to the above principle of comparability (through time).<sup>7</sup>

- Granularity. Allow for the highest level of disaggregation possible with available data. More granular data offers additional information and allows for more detailed analysis, noting that a higher level of granularity might increase complexity. Input from the Network during its second meeting on 19-20 September 2023 highlighted the importance of ensuring that policy makers can draw meaningful insights from the data. This suggests that availability and tractability should be prioritised over granularity. Granularity should not hinder efforts to build trust and ensure the longstanding engagement of stakeholders. Granularity can be increased in further versions of the taxonomy, if needed and upon availability of the corresponding data and sufficient resources.

These principles may be reviewed in the future to ensure that they remain applicable in practice and wellsuited for the objectives of the Network — e.g. granularity might become more relevant with the development of the resulting semiconductor production database. The relative importance of the different principles may also change depending on how critical different chips are — e.g. when analysing more critical/vulnerable and non-substitutable chips it might be worth considering putting more weight on granularity and adaptability.

## 2 Semiconductor manufacturing: Process, technologies and products

Explaining the key steps, process and technologies in the front-end manufacturing stage is critical to developing a useful taxonomy that provides transparency on production capability and capacity. The review contained in this section is the basis for the taxonomy laid out in Section 4.

#### Main types of technologies

Technology is key to the semiconductor production process. Machines and equipment used in photolithography determine a manufacturer's fabrication capabilities, specifically the minimum node size attainable (OECD, 2019<sup>[9]</sup>).<sup>8</sup> Additionally, advances materials science and semiconductor materials, in the technology of circuit elements (e.g. transistors) and in chip packaging increasingly determine chip performance (Singh, Sargent and Sutter, 2023<sup>[11]</sup>; OECD, 2019<sup>[9]</sup>).

#### Semiconductor materials

Semiconductor materials refers to materials with semiconductor properties that serve as the base upon which microelectronic devices are built, with some chips combining different thin slices of semiconductor materials. Semiconductor materials are often classified in three categories — see Section 0 and Sellars (2023<sub>[12]</sub>): silicon, compounds and emerging materials. Typically, the layers of the semiconductor material are grown on a substrate through deposition (e.g. epitaxy for more complex materials focused on crystal orientation) to prepare the wafers that serve as the basis for printing the desired circuit.

Each semiconductor material lends itself to specific applications. Typically, silicon semiconductors run software, while compound semiconductors, comprising other elements from the periodic table, provide specialist functions for sensors and power management. New 'emerging' materials are being developed to provide additional functions such as user displays. A typical electronic product may comprise silicon (70-80%), compound (10-20%) and emerging (10%) semiconductors (Sellars, 2023<sub>[12]</sub>).

The most common material used to make semiconductor wafers is silicon (Si), which is highly abundant and thus possible to scale. Eighty percent of the world's semiconductors use silicon (U.K. Compound Semiconductor Applications Catapult, 2023<sup>[13]</sup>).

The remaining 20% use compound semiconductors, which combine two or more elements, for example gallium arsenide (GaAs), gallium nitride (GaN), indium-phosphide (InP) and silicon carbide (SiC). Compound semiconductors are more complex to manufacture than silicon ones, but outperform silicon for some applications (U.K. Compound Semiconductor Applications Catapult, 2023<sub>[13]</sub>):

• **Power**. For example, SiC has higher breakdown voltages than traditional power chips, which is needed to extend the range of electric vehicles;

- **Speed.** For example, GaN can conduct electrons more efficiently than silicon, needed for increased speeds and lower latency for 5G mobile communication;

- **Light.** For example, Groups III-V and II-VI compounds offer superior photonics needed for optic fibre communications.

Germanium is also an important substrate material used in optoelectronic devices, such as solar cells.

#### Equipment

Each of the different production steps outlined in Section 1 use specific equipment, which is customised and calibrated according to a customer's needs (Singh, Sargent and Sutter, 2023, p. 15<sub>[11]</sub>).

Lithography equipment is the key piece of machinery that has determined the advancement in semiconductor technology. Today, leading-edge chips (< 10 nm) use extreme-ultraviolet (EUV) photolithography technology, requiring equipment currently only manufactured by ASML in the Netherlands. Other types of lithography technology include deep-ultraviolet photolithography (DUV) for wafer fabrication. Technologies such as electron-beam, laser, and ion beam lithography are used in the production of photomasks (layers). While these technologies are still needed for leading-edge chips, without EUV they are currently incapable or ill-suited to mass production of chips with the lowest node sizes (Khan, Mann and Peterson, 2021<sub>[14]</sub>).

In front-end manufacturing, other types of machinery and systems are required for oxidation, physical and chemical vapour deposition and ion implantation, etching and cleaning, diffusion, process control, wafer handling, planarisation (i.e. smoothing out wafer surfaces), and metrology. In particular, chemical vapour deposition is a key stage in the chip fabrication process that requires complex tools that can be differentiated, for example epitaxy reactors and atomic layer deposition (a highly controlled deposition technique that deposits one atomic layer at a time) tools (ETO, 2022<sub>[3]</sub>). Metrology equipment such as optical tools and advanced etching (e.g. atomic layer etching) may also be important differentiators for advanced chips.

The adoption of advanced packaging technologies in advanced chips has required front-end fabs to offer services necessary for this process. For example, TSMC may fabricate chips with electroplating for interposers in advanced packaging, and thus needs to incorporate necessary back-end equipment into its fabs (Shilov, 2023<sup>[15]</sup>).

#### Transistor types and process technologies

Transistor types, with their different purposes and use cases, and the evolution in transistor architectures and materials are key parameters that drive Moore's Law and thus continued advancement in chips technology. These are therefore important considerations for developing the proposed semiconductor taxonomy.

A transistor is the basic component in semiconductor manufacturing, used for switching or amplifying electricity. Most chips today contain billions of transistors.

Transistor dimensions determine speed (typically MHz or GHz), voltage and current, and the number of transistors on the chip (Sellars,  $2023_{[12]}$ ). Transistor performance is evaluated on the maximum amount of current able to flow through it when switched on, the amount of current leakage when off, and the speed at which it switches on and off (Hofman,  $2022_{[16]}$ ). Reducing the transistor size allows manufacturers to increase transistor concentration on chips, thereby delivering a performance boost and power consumption reduction at lower device area and cost – commonly referred to as PPAC (power, performance, area, cost) scaling (Draeger,  $2020_{[17]}$ ).

There are two basic families of transistors: **Field-Effect Transistors (FET)** and **Bipolar Transistors** (Hofman, 2022<sub>[16]</sub>; Cadence, 2022<sub>[18]</sub>; Cadence, 2021<sub>[19]</sub>).

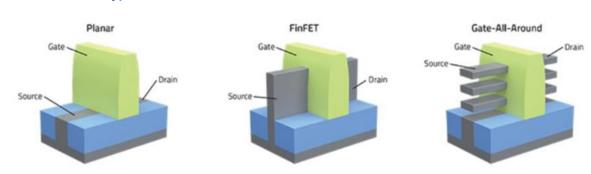

**Field-Effect Transistors (FET)** operate by carrying either a positive or a negative current (i.e. unipolar) through two junctions (a 'source' and a 'drain') with a third junction used for control (the 'gate'). They can have distinct configurations that are constructed differently and have differing scalability, including junction-gate (JFETs), metal-semiconductor (MESFET), planar metal-oxide-semiconductor (planar MOSFETs), vertical fin (FinFETs), and gate-all-around (GAAFETs) — see Figure 3.

#### Figure 3. Transistor types: Planar vs FinFETs vs. GAAFETs

Source: Draeger, N. (2020[17]), FinFETs Give Way to Gate-All-Around, Lam Research, https://newsroom.lamresearch.com/FinFETs-Give-Wayto-Gate-All-Around.

JFETs are the simplest form of FET and are used as electronically controlled switches, voltage-controlled resistors, and as amplifiers. They are formed of a source, a drain, and the gate is in contact with a highly doped semiconductor layer.

MESFETs operate identically to JFETs but have a different channel. The gate is in direct contact with the semiconductor substrate, without the highly doped semiconductor layer used in JFETs. It remains difficult to fabricate circuits containing a large number of MESFETs. Nevertheless, the MESFET is still the dominant active device for power amplifiers and switching circuits in the microwave spectrum.

Planar MOSFETs have a two-dimensional structure and a single gate controlling the source-drain channel. They were the first transistor configuration to be suitable for mass production and miniaturisation in the 1950s and 60s, giving rise to Moore's Law.<sup>9</sup>

Floating gate MOSFETs are commonly used in non-volatile memory chips because of their ability to trap and store an electrical charge on the floating gate for extended periods of time, without a connection to a power supply.

Complementary metal-oxide-semiconductors (CMOS), first invented in the 1960s, combine several MOSFETs of different polarities and performs the basic binary operations that form the basis of any logic chip. CMOS is now the preferred process technology for digital integrated circuits and accommodates different types of transistor architectures (planar or not). Continued scaling of CMOS devices has been made possible with the development and adoption of new materials (e.g. Low-K/High-K dielectrics) that improve transistor performance and process technology innovations such as Fully-Depleted- or Partially-Depleted-Silicon-on-Insulator (FDSOI & PDSOI) that improve the flow of electrons between source-drain over conventional bulk planar technology (IEEE, 2022<sub>[20]</sub>; Liu and Wu, 2003<sub>[21]</sub>). However, dimensional

scaling will eventually approach fundamental limits, and new 'beyond-CMOS' technologies will be needed for the new era of computing (IEEE, 2022<sub>[20]</sub>).

FinFETs were the next major breakthrough in transistor design, when it was discovered that raising the channel above the plane of the silicon and surrounding the channel with a 3D gate made it possible to exert more control over the flow of current (Figure 3 above). FinFETs are three-dimensional structures with vertical fins forming a drain and source, and a gate that surrounds three sides of the channel. Compared to planar MOSFETs, this has the advantages of having less current leakage as the length of the gate shrinks (i.e. the node size decreases), a lower gate voltage needed to operate the transistor, and faster switching times. FinFETs' vertical geometry enables easier fabrication of multi-gate devices (where there are multiple gates on a single transistor that can be controlled by a single gate electrode or independent gate electrodes)<sup>10</sup> and for more transistors to be incorporated onto a single chip, sustaining Moore's Law (Cadence, 2021<sub>[19]</sub>).

However, FinFETs are currently reaching the limit of how high fins can go and how many fins can be placed side by side to boost current-carrying capacity without suffering from electrical challenges.

GAAFETs are considered the next evolution of FETs. They use stacked nanosheets so that the gate surrounds the channel on all four sides, further reducing leakage and increasing drive current. GAAFETs exhibit high potential for further downsizing transistors while offering better capabilities.

**Bipolar Transistors** consist of two mutually connected Positive(P)-Negative(N) junctions (forming either NPN or PNP configuration) with three connections (the 'emitter', 'base' and 'collector'), and are capable of carrying *both* positive and negative electric signals. Although bipolar junction transistors (BJTs) are cheaper to manufacture and can offer greater current output, which makes them popular for amplifier circuits, they are larger in size and less widely used than FETs.

FET and BJTs can be combined – for example, BiCMOS is a process technology that combines the highspeed analogue capability of bipolar and the low-power, high-packing density of CMOS. Integrated circuits that combine different types of transistors can benefit from the advantages of each transistor type but can be more complex and expensive to produce. Insulated-gate bipolar transistors (IGBT) differ from BiCMOS in that they are a single transistor that features a functional integration of MOS and bipolar physics and have wide application in power electronics systems (Baliga, 2023<sub>[22]</sub>).

Transistor types and process technologies continue to evolve rapidly, driven by a quest for more performance and lower costs, trying to keep up with "Moore's Law". There are several examples amongst technologies currently being deployed such as backside power delivery<sup>11</sup> or recent discoveries that might take years to develop and deploy commercially such as quantum-interference transistors.<sup>12</sup>

#### **Types of semiconductors**

The semiconductor industry produces a wide variety of chips designed for precise functions. Different types of chips are typically produced in separate facilities, and often by specialised firms using unique manufacturing processes.

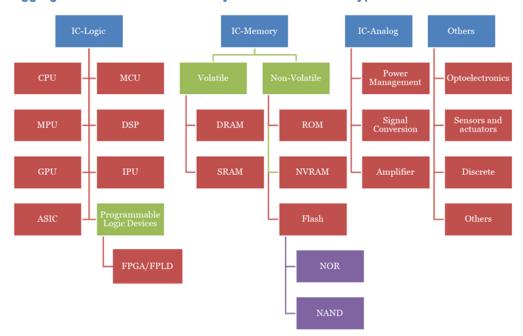

Generally, there are considered to be four main types of semiconductors: logic, memory, analog and others (Haramboure et al., 2023<sub>[1]</sub>; Kleinhans and Baisakova, 2020<sub>[2]</sub>; Singh, Sargent and Sutter, 2023<sub>[11]</sub>).

#### Logic

Logic chips process binary information and include microprocessors (e.g. central processing units, CPUs and graphics processing units, GPUs), microcontrollers (MCUs) and connectivity chips.

Amongst logic chips, Programmable Logic Devices (PLDs) are integrated circuits that can be configured by the user to perform different functions. PLDs differ in the placement of programmable connections and can be differentiated based on the complexity of their architecture. One group is Field Programmable Logic Devices (FPLD), which are integrated circuits that assist in the execution of digital systems and are suited for simpler applications (Advanced Micro Devices, 2021<sub>[23]</sub>). A more complex but flexible group is the Field Programmable Gate Array (FPGA), a generic chip based around a matrix of configurable logic blocks (e.g. MCUs, digital signal processors, DSPs, etc.) connected via programmable interconnects that can be reprogrammed or reconfigured to desired application or functionality requirements after manufacturing (Advanced Micro Devices, n.d.<sub>[24]</sub>).

FPGAs can be distinguished from Application-Specific Integrated Circuits (ASICs), which are custom manufactured for specific compute tasks.

The most advanced generations of logic chips are produced using leading-edge processes and technologies. Node sizes range from the most advanced 3nm node to mature generation nodes over 250nm.

- The UK Compound Semiconductor Applications Catapult's taxonomy (c.f. Section 3 below) references the evolution of logic chips from MCUs to DSPs a specialised version of an MCU optimised to process digital signals such as voice or video), to GPUs (optimised DSPs designed to process high resolution video signals), and then to intelligent processing units (IPUs a specialised version of a GPU optimised to run AI computation).

- The IEEE's 2022 International Roadmap for Devices and Systems (IRDS), the foundational plan for the semiconductor industry regarding the development of electronic devices and systems, forecasts that logic devices will scale to less than 1nm by the 2030s using GAAFET and 3-D integration/ vertical stacking of circuits (IEEE, 2022<sub>[20]</sub>).

#### Memory

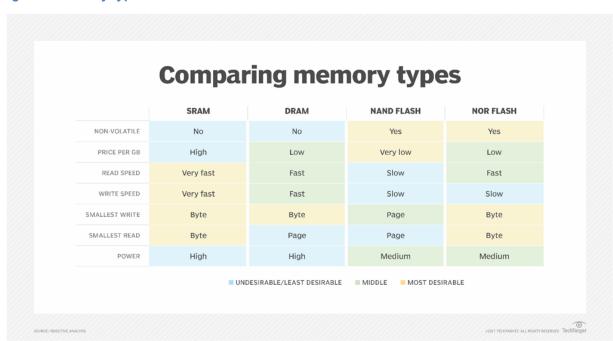

Memory chips store data. Different types of memory chips serve different functions and are separated by their ability to retain data without power (Figure 4). For example, Dynamic Random-Access Memory (DRAM) and Static Random-Access Memory (SRAM) are volatile memory technologies, meaning they only temporarily store information while switched on, making them suitable for short-term storage. DRAM is more power intensive, slower, but cheaper than SRAM.

In contrast, non-volatile memory retains data even after the system is switched off, making it suitable for long-term storage. Flash memory is considered the baseline non-volatile memory because it is highly mature. There are two main types of flash memory – *Not And* (NAND) and *Not Or* (NOR), that differ in their architectures and cell size. It is easier to increase the storage capacity of NAND flash and it is faster in writing and erasing data, while NOR flash is faster at reading data (Samsung, 2013<sub>[25]</sub>). Other types of non-volatile memory are Read-Only Memory (ROM) and Non-Volatile Random-Access Memory (NVRAM).

#### Figure 4. Memory types of semiconductors

Source: Bigelow and Jones (2023<sub>[26]</sub>), *NAND Flash Memory*, TechTarget, <u>https://www.techtarget.com/searchstorage/definition/NAND-flash-memory</u>.

There are prototypical and emerging non-volatile memory technologies that are expected to have speed, density and power advantages over flash memory (IEEE, 2022<sub>[20]</sub>) (see also Figure 6). Advanced memory technology uses a 3-D approach to vertically stacking layers of memory cells built with floating gate MOSFETs produced using more mature process nodes. Today flash memory chips are packing close to 200 memory cell layers, and are forecasted by certain manufacturers to be over 1000 layers by 2030 (IEEE, 2022<sub>[20]</sub>). Memory chips typically have node sizes between 10nm and 50nm.

#### Analog

Analog chips convert and modify signals from the physical world with continuous parameters (e.g. temperature, speed, pressure, etc.) into digital signals, and power management functions. Designed for specific tasks in specific markets, they usually do not rely on shrinking node sizes.

#### Others

Other types of chips include for example "discrete" chips which typically perform a single electrical function (e.g. diodes, rectifiers, thyristors) and are produced using mature-node technology, as well as optoelectronics (e.g. LEDs), sensors and actuators.

# **3** Existing taxonomies for semiconductors

Different entities have adopted different approaches and methodologies for classifying semiconductor data, largely reflecting the purposes of, and limitations of data availability.

#### SEMI

SEMI is the global industry association representing the microelectronics manufacturing and design supply chain. Its members include companies at all stages of the semiconductor value chain.

SEMI's World Fab Forecast tracks front-end (fab) spending, construction, capacity, and technology trends at the level of an individual fab, covering over more than 1 450 facilities worldwide. Published quarterly, information is compiled from various industry sources, including publicly available information, and verified with industry contacts. Key parameters of semiconductor fabrication facilities tracked by SEMI include (SEMI, 2023<sub>[27]</sub>):

- Fab owner

- Fab location

- Status (under construction, operational, upgrading)

- Wafer capacity

- Clean room size and class

- Fab product types, based on the top-two product types produced in the fab (e.g. Analog/Linear, Discrete/Opto, Logic/MCU, Memory/Flash)

- Fab technology (e.g. CMOS, FinFET, EUV, system-on-a-chip, Low-K)

- Geometry, or the minimum feature size the fab is capable of producing, as reported by the company.

#### World Semiconductor Trade Statistics (WSTS)

WSTS is an industry-led organisation with the purpose of collecting and publishing semiconductor trade net shipments and forecasts for the global semiconductor industry. Statistics are compiled based on confidential billings data submitted by companies responding to a monthly market survey. Reported data include all aggregated monthly net billings between semiconductor manufacturers and their end customers, according to customer shipment location (i.e. chips consumption).

Shipment data is aggregated at the level of five macro regions of the world market (WSTS, 2022<sub>[28]</sub>). Production data are not collected at the fab-level and firm-level data are not available to maintain the confidentiality of the collection process.

The WSTS' *Product Classification 2023* (summarised in Table 1) is the methodology describing the classifications and definitions of semiconductor products used by WSTS in its data reporting. It is perhaps the most comprehensive and detailed taxonomy publicly available. The classification is reviewed on a regular basis, while ensuring that data are comparable across time.

| Product<br>(category) | Туре     | Product Type<br>(detailed)                                                 | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------|----------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Discretes             |          |                                                                            | General purpose signal and switching diodes, zener diodes, transient protection diodes, and radiofrequency and microwave diodes.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Optoelectror          | nics     |                                                                            | Includes displays, lamps, couplers, and other opto-sensing and emitting semiconductor devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Sensors<br>Actuators  | and      |                                                                            | Semiconductor devices whose electrical properties are<br>designed to correlate to temperature, pressure,<br>displacement, velocity, acceleration, stress, strain or any<br>other physical, chemical or biological property.                                                                                                                                                                                                                                                                                                                                    |

| Integrated<br>(ICs)   | circuits |                                                                            | Circuits combining digital and analog techniques are<br>classified into digital circuits or analog circuits according to<br>the chip area devoted to the respective technique.                                                                                                                                                                                                                                                                                                                                                                                 |

|                       |          | Analog<br>- General Purpose<br>Analog<br>- Application-<br>Specific Analog | The essential function of the device is to process analog<br>signals (signal that is continuously varying over time).<br>General Purpose Analog is further sub-divided into specific<br>functional sub-categories of Amplifiers, Signal Conversion,<br>Interface, and Power Management ICs, according to their<br>primary or dominant function.<br>Application-Specific Analog is sub-divided by the specific<br>end application/market for which the device is designed for<br>(e.g. Consumer, Computer, Communications, Automotive,<br>Industrial & Others). |

|                       |          | MOS Micro                                                                  | All MOS and BiMOS logic ICs that are microcomputer related (e.g. MPU, MCU and DSP).                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       |          | Total Logic (MOS &<br>Bipolar)                                             | All non-Micro MOS Logic ICs and Bipolar Logic ICs.<br>Includes sub-categories: Digital Bipolar, MOS General<br>Purpose Logic, MOS Gate Arrays, MOS Standard Cells and<br>Field Programmable Logic, MOS Display Drivers, MOS<br>Touch Screen Controller, and MOS Special Purpose Logic.                                                                                                                                                                                                                                                                         |

|                       |          | MOS Memory                                                                 | All monolithic Memory devices made with NMOS, PMOS or<br>CMOS, or any combination of MOS technologies. Includes<br>sub-categories of DRAM, SRAM, Mask Programmable<br>ROM, and Flash Memory.                                                                                                                                                                                                                                                                                                                                                                   |

#### Table 1. Summary of WSTS' categorisation and product definitions

Source: WSTS (2022), WSTS Product Classification 2023, World Semiconductor Trade Statistics.

#### **Compound Semiconductor Applications (CSA) Catapult**

The United Kingdom's (UK) Compound Semiconductor Applications (CSA) Catapult was established in 2018 by Innovate UK to help the UK become a global leader in compound semiconductors through collaboration with both large companies and start-ups to develop and commercialise new applications. CSA Catapult is the UK's authority on compound semiconductor applications and commercialisation.

The CSA Catapult developed a semiconductor taxonomy, shared with the Semiconductor Informal Exchange Network by the UK.<sup>13</sup> This taxonomy segments semiconductors by substrate material (silicon, compound, emerging) and then function (e.g. analog, digital, discrete, power, photonics, sensors, etc.) (Figure 5).

The CSA Catapult taxonomy distinguishes between analog integrated, digital integrated and discrete categories of chips. It then identifies sub-categories within chip types.

#### Figure 5. Catapult semiconductor taxonomy

Source: Sellars, A. (2023), Semiconductor Primer, Internal Working Document, Catapult Semiconductor Applications.

It is worth noting that for digital integrated circuits these sub-categories are logic, processors and memory semiconductors. Logic chips and processors are distinguished on the basis that the former are programmable or customisable using software while processors have fixed, general purposes/functionality. Chip types under the logic sub-category are further divided into FPGA, Field Programmable Logic Device (FPLD), and ASIC. Chip types under the processor sub-category are MCUs, DSPs, GPUs and IPUs.

#### **IEEE Taxonomy of Emerging Memory Devices**

The IEEE categorises current and emerging memory technologies (Figure 6). IEEE's taxonomy distinguishes between volatile and non-volatile memory technologies (see Section 2, above). For non-volatile memories it further distinguishes between baseline, mature flash technologies, prototypical

technologies that are commercially available but for niche applications, and emerging technologies that have significant potential benefits if various scientific and technological hurdles can be overcome.

#### Figure 6. IEEE's memory taxonomy

Source: IEEE (2022<sub>[20]</sub>), International Roadmap for Devices and Systems (IRDS™) 2022 Edition", <u>https://irds.ieee.org/editions/2022</u>. © 2022, IEEE

#### Other taxonomies

The United States CHIPS Program Office is implementing the CHIPS and Science Act. In its Notice of Funding Opportunity for the CHIPS Incentives Program, the CHIPS Program Office uses a categorisation system for commercial fabrication facilities based on the maturity of their processes, in addition to a distinction based on product type or the service provided.<sup>14</sup> Categories include:

- Leading-edge facilities for logic or memory chips that utilise the most advanced front-end fabrication processes, which achieve the highest transistor and power performance. For logic chips, this currently includes facilities that produce semiconductors at high volumes using EUV lithography tools. For memory chips, this currently includes facilities capable of producing 3-D NAND flash chips with 200 layers and above, and/or DRAM chips with a half-pitch of 13nm and below.

- **Current generation facilities** that produce semiconductors that are not leading edge, up to 28nm process technologies, and include logic, analog, radio frequency, and mixed-signal devices.

- Mature-node facilities that fabricate generations of: (a) logic and analog chips that are not based on FinFET, post-FinFET transistor architectures, or any other sub-28nm transistor architectures;

(b) discrete semiconductor devices such as diodes and transistors; (c) optoelectronics and optical semiconductors; and (d) sensors.

The United States Department of Commerce, in its 2021 *Notice of Request for Public Comments on Risks in the Semiconductor Supply Chain* also includes a categorisation of semiconductor product capabilities, distinguishing technology nodes (in nanometres), semiconductor material types, and device types.<sup>15</sup>

In the recent European chips survey report (EC, 2022, p. 11<sub>[29]</sub>), the European Commission (EC) distinguishes amongst different types of chips, including logic and microprocessors, memory chips, analog chips, discrete chips, optoelectronics, and sensors, as well as chips designs that allow for the combination of different functions – system-on-a-chip (SoC).<sup>16</sup> This report also distinguishes seven different classes of node sizes from 5-7nm to node sizes larger than 280 nm. The business model was also deemed relevant information to help map the semiconductor value chain.

The World Customs Organisation's Harmonised System (HS) codes also classifies semiconductor products under two 4-digit labels (see Annex A). However, the product classification might be too aggregated for the purposes of the Network.

# **4** Proposed taxonomy for semiconductors

The OECD's proposed common taxonomy for semiconductor product types and production facilities aims to provide policy makers with useful, disaggregated information for the purposes of improving understanding of the semiconductor value chain and helping identify alternative sources for the different types of semiconductors in the event of disruptions.

The taxonomy for semiconductors proposed in this document builds on existing taxonomies described in Section 3 as well as several underlying principles described in Section 1.

The proposed taxonomy applies only to semiconductor products and fabrication/foundry manufacturing processes detailed in defined in Section 2. It excludes the *Design* and *ATP* stages described as part of the semiconductor value chain in Section 1, as well as other upstream or downstream activities. Work on the *Design* and *ATP* production stages, as well as on key upstream and downstream activities that present bottlenecks in the value chain (e.g. specialised equipment and select raw materials) will be explored in more detail in the future.

This section summarises the taxonomy at the fab-level, describing plant information, capabilities and capacities. Capabilities includes technical information on e.g. process technologies, transistor types and chip types. While the subsection containing Figure 9 corresponds to a chips taxonomy per se, the framework laid out in this section is much broader and covers the relevant fab-level information.

### Building the evidence base: a taxonomy for a semiconductor production database

Building the evidence base for semiconductors requires comparable data on semiconductor types as well as their production facilities/fabs. Understanding semiconductor value chain bottlenecks, vulnerabilities and substitutability requires information on what the different fabs are capable of producing, which is determined by a number of fab characteristics. The key characteristics of semiconductor fabs that could help determine how production/supply can adjust to disruptions include:

General Company/Plant information. As identified in recent OECD work (Haramboure et al., 2023<sub>[1]</sub>), semiconductor manufacturing is geographically concentrated and horizontally differentiated, meaning the location of the plant, the company producing the chips, and the home economy of this company is important information when considering substitutability. The operational status of fabs (including whether it is being retooled/upgrading) is important to understanding both current as well as future production location and capacity. Fab ownership and general information on the company that owns the fab, such as the business model — i.e. whether the plant belongs to an IDM or operates as a foundry will be included. Company financials, as well as other relevant company-level variables that might be available, would be important dimensions to consider in future analyses.<sup>17</sup>

Capability. This refers to what an individual semiconductor fab/production facility is capable of producing, in terms of chip type (see the subsection below for a detailed classification of chip types), process technology, equipment and tools, transistor type, substrate, wafer size and feature size. These variables are key to identifying potential substitutability. The feature size, which differs for logic (node) and memory chips (DRAM memory in terms of half-pitch measured in nanometres and NAND measured in stacked layers of memory cells and bits per cell) is a proxy for the technological advancement or maturity of the chips the fab is capable of producing. Certain chip types (e.g. analog and sensors) also use semiconductor materials other than silicon.

Information on the types of end-products that build on the chips that a plant can produce (chip uses), will be included if available. Further work on this in collaboration with the Network and stakeholders could help shed further light on semiconductor uses and the potential for downstream disruptions.<sup>18</sup>

Capacity. The production capacity of the facility based on the equipment capacity of a fab, typically

measured in terms of wafer starts per month. The actual number of wafers being processed at any

given time (i.e. yield) may change depending upon business conditions, product development and

testing needs, maintenance schedules and product change overs. Availability of fab-level data on

yield rates and capacity utilisation over time appears to be a challenge.

The size of the clean room, the engineered space free of airborne particulates, is also a proxy for production capacity as a larger clean room can accommodate larger and more equipment.

Based on the characteristics outlined above, Figure 7 summarises the main elements that could be envisaged in a semiconductor production taxonomy. The most challenging elements to reflect in the taxonomy are the technological elements under "Capability" given that they interact in sometimes complex ways.

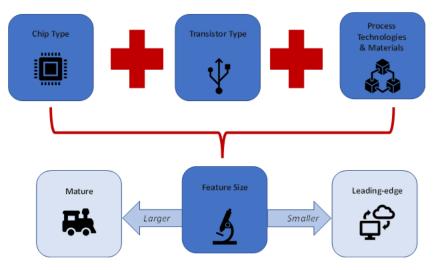

Figure 8 below illustrates how the different elements interact to produce chips at different levels of technological content and maturity, distinguishing between leading-edge and mature chips in this particular illustration. The Network discussed whether it would be worth to have an explicit distinction between Leading-Edge and Mature chips. On the one hand, making such distinction explicit would provide additional clarity and provide for an easier identification of these chips, thus allowing for more detailed analysis (possibly including trends). On the other hand, such a distinction would considerably increase complexity, could result in heightened data availability challenges and be prone to regular updates as semiconductor technologies advance very rapidly. It is suggested that the taxonomy remains flexible to allow for different approaches to distinguishing leading-edge from mature chips based on the different elements outlined in Figure 8.

#### Figure 7. OECD's proposed semiconductor production taxonomy

Note: Please note that the attributes under each variable are examples, pending confirmation of data availability, notably for transistor type and Process Technologies. More details about these attributes are available in Table 3.

#### Figure 8. Capability in chips fabs

The semiconductor production taxonomy will serve as the basis for developing a database of semiconductor production facilities and their characteristics to support analyses on value chain disruptions. Based on the elements described above and conditional on any changes proposed by the network, and most importantly data availability, the semiconductor production database would strive to include as much data as possible to populate the database variables listed in Table 2.

Additional types of information might be considered in the future, including for example company financial information, workforce and human capital, and perhaps information on the environmental footprint (e.g. energy use, waste, water use) and on downstream dependencies (fab customers and geographies). Inclusion of such extensions would require first and foremost the availability of those data, and then an assessment of the feasibility of combining such data with the semiconductor production database.

| Category                 | Variable                       | Description of the categories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | Location                       | The location of the plant (city, state/region, and economy).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                          | Owner                          | The name of the company that has a majority shareholding in the plant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                          | Owner<br>headquarters          | The economy where the majority shareholder company headquarters are located.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| General company          | Ultimate Owner                 | Any available information on the ultimate parent company's name.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| and plant<br>information | Ultimate Owner<br>headquarters | Any available information on the ultimate parent company's headquarters.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                          | Status                         | Whether the plant is operating, in planning stages, under construction or upgrading/ expanding.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                          | (Start) Year                   | The year in which the fab began (or is expected to begin) volume production.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                          | Business Model                 | Whether the plant is a pure-play foundry or part of an IDM's operations.<br>R&D centres that could produce chips for commercial purposes may also be identified in the<br>database and the nature of such types of plants recorded in this variable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                          | Chip type –<br>aggregated      | Whether the plant produces IC- Logic, IC- Memory, IC-Analog, Other chips — see Figure 9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                          | Chip type –<br>detailed        | The sub-category of chip type within the five aggregate categories (e.g. MCUs, GPUs, IPUs, FPGA, etc. in the logic chip category) see Figure 9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                          | Wafer size<br>(mm)             | The maximum size (diameter) of the silicon wafers that the plant is setup for, which determines the number of chips per wafer, the cost per chip, and the number of chips that can be fabricated per annum. Standard wafer sizes are 50mm, 100mm, 150mm, 200mm 300mm and 450mm.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                          | Feature size                   | The minimum feature size possible on each layer of the chips produced in nanometres [OR for flash memory, the number of stacked layers or bits per cell].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Capability               | Transistor type                | The type(s) of transistors the fab is capable of producing. See Table 3 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |