# Tight ZK CPU:

# Batched ZK Branching with Cost Proportional to Evaluated Instruction

Yibin Yang\* David Heath<sup>†</sup> Carmit Hazay<sup>‡</sup> Vladimir Kolesnikov<sup>§</sup>

Muthuramakrishnan Venkitasubramaniam<sup>¶</sup>

September 6, 2024

#### Abstract

We explore Zero-Knowledge Proofs (ZKPs) of statements expressed as programs written in high-level languages, e.g., C or assembly. At the core of executing such programs in ZK is the repeated evaluation of a CPU step, achieved by branching over the CPU's instruction set. This approach is general and covers traversal-execution of a program's control flow graph (CFG): here CPU instructions are straight-line program fragments (of various sizes) associated with the CFG nodes. This highlights the usefulness of ZK CPUs with a *large* number of instructions of varying sizes.

We formalize and design an efficient *tight* ZK CPU, where the cost (both computation and communication, for each party) of each step depends only on the instruction taken. This qualitatively improves over state of the art, where cost scales with the size of the *largest* CPU instruction (largest CFG node).

Our technique is formalized in the standard commit-and-prove paradigm, so our results are compatible with a variety of (interactive and non-interactive) general-purpose ZK.

We implemented an interactive tight arithmetic (over  $\mathbb{F}_{2^{61}-1}$ ) ZK CPU based on *Vector Oblivious Linear Evaluation* (VOLE) and compared it to the state-of-the-art non-tight VOLE-based ZK CPU Batchman (Yang et al. CCS'23). In our experiments, under the same hardware configuration, we achieve comparable performance when instructions are of the same size and a 5-18× improvement when instructions are of varied size. Our VOLE-based tight ZK CPU (over  $\mathbb{F}_{2^{61}-1}$ ) can execute 100K (resp. 450K) multiplication gates per second in a WAN-like (resp. LAN-like) setting. It requires  $\leq 102$  Bytes per multiplication gate. Our basic building block, ZK *Unbalanced Read-Only Memory*, may be of independent interest.

<sup>\*</sup>Georgia Institute of Technology, yyang811@gatech.edu.

<sup>&</sup>lt;sup>†</sup>University of Illinois Urbana-Champaign, daheath@illinois.edu.

<sup>&</sup>lt;sup>‡</sup>Bar-Ilan University and Ligero Inc., Carmit.Hazay@biu.ac.il.

<sup>§</sup>Georgia Institute of Technology, kolesnikov@gatech.edu.

<sup>¶</sup>Ligero Inc., muthu@ligero-inc.com.

# Contents

| 1 | Introduction                                              | 1    |

|---|-----------------------------------------------------------|------|

|   | 1.1 Our Focus: Pay for the Active Branch                  |      |

|   | 1.2 Our Contribution                                      |      |

|   | 1.3 Intuition of Our Construction                         |      |

|   | 1.4 Related Work                                          | . 4  |

| 2 | Preliminaries                                             | 5    |

|   | 2.1 Notation                                              | . 5  |

|   | 2.2 Security Model                                        | . 6  |

|   | 2.3 Commit-and-Prove Zero-Knowledge                       | . 6  |

|   | 2.4 Zero-Knowledge Read-Only Memory                       | . 8  |

|   | 2.5 ZKP via Topology Matrices                             | . 10 |

| 3 | Our Target Functionality: $\mathcal{F}_{ZKCPU}$           | 11   |

| 4 | Technical Overview                                        | 12   |

|   | 4.1 Boundary Strings and Helper Notation                  | . 12 |

|   | 4.2 More Powerful Topology Matrices                       |      |

|   | 4.3 Reducing a Tight ZK CPU to a ZK UROM                  |      |

|   | 4.3.1 Special Case: No Registers                          | . 14 |

|   | 4.3.2 Handling Constant 1                                 | . 16 |

|   | 4.3.3 Supporting Registers                                | . 17 |

|   | 4.3.4 Committing to the Topology Vector                   |      |

|   | 4.4 ZK Non-Zero-End Unbalanced ROM                        |      |

|   | 4.4.1 Using ZK UROM with Topology Vectors                 | . 20 |

| 5 | Formalization                                             | 21   |

|   | 5.1 Ideal ZK Non-Zero-End UROM: $\mathcal{F}_{CPZK-UROM}$ | . 21 |

|   | 5.2 Our Protocols: $\Pi_{CPZK-UROM}$ and $\Pi_{ZKCPU}$    | . 21 |

|   | 5.3 Optimization and Cost Analysis                        | . 27 |

| 6 | Support for Advanced Operations                           | 29   |

|   | 6.1 Equality Gates                                        | . 29 |

|   | 6.2 Support for LOAD and STORE Gates                      | . 30 |

| 7 | Evaluation                                                | 30   |

| A | Deferred Complete Proofs                                  | 40   |

|   | A.1 Complete Proof of Theorem 1                           |      |

|   | A.2 Complete Proof of Theorem 2                           |      |

| B | Fine-grained Cost Analysis                                | 44   |

| _ | B.1 $\Pi_{CPZK-UROM}$ in $\mathcal{F}_{CPZK-ROM}$ -hybrid |      |

|   | B.2 $\Pi_{ZKCPU}$ in $\mathcal{F}_{CPZK-UROM}$ -hybrid    |      |

|   |                                                           |      |

#### 1 Introduction

Zero-Knowledge (ZK) Proofs (ZKPs) [GMR85] allow a prover  $\mathcal{P}$  to convince a verifier  $\mathcal{V}$  that a given statement is true without revealing anything beyond this fact. With recent advances in efficiency, ZKP has become one of the most active areas in cryptographic research. Example applications include private blockchain [BCG<sup>+</sup>14], private programming analysis [FDNZ21, LAH<sup>+</sup>22], private bug-bounty [HYDK21, YHKD22], privacy-preserving machine learning [LXZ21, WYX<sup>+</sup>21], and many more.

Most generic ZK schemes prove statements represented as circuits or constraint systems. While these formats support arbitrary statements, they do not align with how computational tasks are often described or developed in practice – using a high-level language, such as C/C++/assembly/etc.

A promising path towards efficient ZKP for general programs is to mimic what plaintext computers do. An assembly (or C/C++ or other high-level) program can be broken into straight-line blocks; the resulting program control-flow graph (CFG) describes how program control can transfer between the blocks.

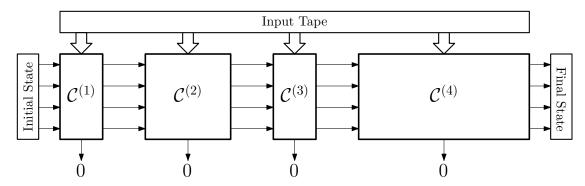

Casting this to ZKP (and for efficiency, omitting the plaintext-world step of compiling to a hardware CPU fixed instruction set), instead of agreeing on a single public circuit,  $\mathcal{P}$  and  $\mathcal{V}$  agree on B circuits, each corresponding to (i.e., implementing a straight-line program of) a CFG block. Viewed this way, the objective of ZKP is to execute the program from a public initial state to a public final state via a circuit constructed by privately "soldering" these (potentially repeated) basic CFG blocks (see Figure 1). This approach can be viewed as executing steps of a Zero-Knowledge Central Processing Unit (ZK CPU) whose instruction set is defined in terms of the target program's complex CFG blocks. An MPC version of this approach is explored by recent VISA MPC [YPHK23].

Of course, a ZK CPU must be able to access a *random-access memory* (RAM); this technical task is external to our focus. We show that the state-of-the-art ZK RAM [YH24] can be efficiently integrated with our ZK CPU (see Section 6.2).

**ZK disjunctions.** The sequence of executed CFG blocks (instructions) must remain hidden from  $\mathcal{V}$ . This can be trivially achieved by  $\mathcal{P}$  and  $\mathcal{V}$  executing *each* instruction in each step – the circuit for computing such a step would be a disjunction of all instructions (in the instruction set), and the top-level proof statement would simply be a sufficient number of repetitions of the disjunction.

This approach incurs a glaring overhead: parties execute – and pay for – a large number of inactive (i.e., not taken in plaintext execution) clauses in each disjunction. To make matters worse, many programs have large CFGs, so each disjunction is over a large number of clauses, causing corresponding overhead.

A recent line of work ([BMRS21, GGHAK22, GHAK23, GHAKS23, HK20, Kol18, YHH<sup>+</sup>23]) aims to avoid paying for inactive clauses in a disjunction. [HK20] described the possibility of reusing the cryptographic *material* of the active branch to evaluate (to garbage and privately discard) inactive branches. This limits communication to the cost of a single (longest) branch but still requires processing all branches. Very recent work [GHAK23, YHH<sup>+</sup>23] shows how to limit both communication and computation to that of the single longest branch for our setting, where the same disjunction (of all instructions in the instruction set) is executed repeatedly.

To summarize, the state of the art pays for the longest branch.

Figure 1: Example ZK CPU execution.  $\mathcal{P}$  and  $\mathcal{V}$  agree on B public (sub)circuits  $I = \{\mathcal{C}_1, \dots, \mathcal{C}_B\}$ .  $\mathcal{P}$  demonstrates to  $\mathcal{V}$  that an initial state evaluates to a final state via a *private* circuit  $\mathcal{C} \triangleq \mathcal{C}^{(4)} \circ \cdots \circ \mathcal{C}^{(1)}$ , where each  $\mathcal{C}^{(i \in [4])} \in I$ .  $\mathcal{V}$  learns the size of  $\mathcal{C}$  but does *not* learn the number or identity of specific subcircuits used. Each subcircuit's output is fed as input to the subsequent subcircuit. We refer to the wires that pass from subcircuit to subcircuit as *registers*. Each subcircuit can read private input from  $\mathcal{P}$ , and each subcircuit outputs a "checking output", which evaluates to 0 when  $\mathcal{P}$  is honest. The checking output can be used to, e.g., force  $\mathcal{P}$  to use  $\mathcal{C}_1$  when the first register is 1. See Section 3 for formal details.

#### 1.1 Our Focus: Pay for the Active Branch

We are motivated by scenarios where instructions (or branches) differ significantly in size, possibly by orders of magnitude. In such cases, it is unacceptable to incur the cost of the longest branch. While instructions in hardware CPUs are roughly the same size by design, this is *not the case* in CFGs, where blocks correspond to straight-line program segments.

**Tight ZK CPU emulation.** We mostly adhere to the ZK CPU notation and vocabulary. We choose this over other equivalent vocabularies, such as CFG and blocks, discussed above. This is for simplicity, clarity, and consistency, since prior ZK work already uses the CPU and CPU-emulation terminology and definitions (e.g., [BCG<sup>+</sup>13, FKL<sup>+</sup>21, HYDK21, YHH<sup>+</sup>23]).

Extending the existing ZK CPU vocabulary, in this work, we introduce and focus on *tight* ZK CPU emulation (or just tight ZK CPU) – one whose cost of executing each instruction is proportional to the size of *that* instruction. This is in contrast to all prior work on efficient ZK CPU emulation, where the cost of executing a CPU step is proportional to the *total cost of all* instructions in the CPU or, more recently, to the largest instruction in the CPU.

It is challenging to achieve tight ZK CPU concretely efficiently because instruction boundaries must be hidden from  $\mathcal{V}$ , and corresponding *expensive* instruction set-up and conclusions (which, e.g., handle registers, instruction loads, proof checks, etc.) must be executed at each possible basic step of the ZK proof.

**Spliting large instructions.** It is, of course, possible to equalize instruction sizes by splitting a large instruction  $\mathscr{C}$  into a sequence of small instructions. This incurs the expense of passing *more* registers between instructions more frequently: the current internal state of the larger instruction  $\mathscr{C}$  now must be passed between its consecutive sub-instructions  $\mathscr{C}_i$  and  $\mathscr{C}_{i+1}$ . This internal state corresponds to the width of the circuit implementing  $\mathscr{C}$  and may be large. Crucially, now *all*

instructions must accept this many registers as input to preserve ZK, incurring corresponding overhead.

Our work allows cheaply handling arbitrarily large (and arbitrarily wide!) instructions without incurring the overhead of handling additional registers.

**Privacy guarantees.** The privacy guarantees provided by prior CPU-emulation definitions and constructions are somewhat different from that of our tight ZK CPU. In prior work,  $\mathcal{V}$  learns the number of executed CPU steps; in our work,  $\mathcal{V}$  learns the total number of multiplication gates on the program execution path. Both metrics correspond to (slightly different) notions of program runtime. We stress that revealing the runtime is inevitable when demanding tight prover efficiency, and standard padding techniques can provide finer privacy guarantees.

Depending on instruction sizes, the total number of evaluated gates in executing our tight CPU can indicate to  $\mathcal{V}$  with high confidence which instructions were executed. A similar concern applies to prior ZK CPU work, where a precise runtime (number of instructions) might tell  $\mathcal{V}$  the execution path. Such issues are arguably more relevant in our model since runtime is more granular. As in prior work, this can be addressed by runtime padding.

#### 1.2 Our Contribution

We motivate and formalize the notion of a tight ZK CPU, where the cost (both computation and communication for each party) of each step depends only on the instruction taken, even when the instructions are of varying sizes. We define an ideal functionality  $\mathcal{F}_{\mathsf{ZKCPU}}$  (see Figure 6 and discussion in Section 3) to capture this notion by only sending the length of the entire execution to  $\mathcal{V}$ .

Our protocol realizes  $\mathcal{F}_{\mathsf{ZKCPU}}$  in the commit-and-prove hybrid (defined as  $\mathcal{F}_{\mathsf{CPZK}}$  in Figure 3) model with information-theoretic security. Our protocol is public-coin and constant-round in  $\mathcal{F}_{\mathsf{CPZK}}$ -hybrid model, so it natively supports the Fiat-Shamir transformation [FS87, PS00]. Crucially, our abstraction allows realizing the  $\mathcal{F}_{\mathsf{ZKCPU}}$  via a variety of commit-and-proof ZK protocols, including interactive and non-interactive ones (e.g., [AHIV17, BMRS21, BBB+18, CHM+20, DOT21, DIO21, IKOS07, MBKM19, YSWW21]).

We implement<sup>1</sup> a tight ZK CPU protocol by instantiating the commit-and-proof ZK with VOLE-based ZK [DIO21, YSWW21] and report the performance in Section 7. The cost of our VOLE-based tight ZK CPU scales only *linearly* with the number of multiplication gates along the program execution path. Concretely, this protocol outperforms the state of the art Batchman [YHH<sup>+</sup>23] (a VOLE-based non-tight ZK CPU) in *both* computation and communication commensurately with branch size variation (see Section 7). Our VOLE-based ZK CPU achieves a cost of only a constant factor  $(6-7\times)$  higher than the *non-private* protocol, where the execution path is revealed to  $\mathcal{V}$ .

#### 1.3 Intuition of Our Construction

We present high-level intuition here; Section 4 presents a detailed technical overview of our approach.

Consider a ZK proof expressed as a high-level program composed of basic "control-flow" blocks, which we call *instructions*.  $\mathcal{P}$ 's witness is an input to the program that evaluates to an accepting

<sup>&</sup>lt;sup>1</sup>Our implementation is available at https://github.com/gconeice/tight-vole-zk-cpu.

state. The proof convinces  $\mathcal{V}$  the existence of a sequence of instructions – an execution path – leading to an accepting state. While the execution path, known to  $\mathcal{P}$ , can depend on  $\mathcal{P}$ 's secret witness, a ZK proof must hide the path from  $\mathcal{V}$ .

The recent Batchman protocol [YHH<sup>+</sup>23] demonstrates that it is possible to efficiently encode each program instruction as a randomized vector of field elements. At a high level, each such vector is the product of  $\mathcal{V}$ 's random challenge vector and a matrix that encodes the linear constraints imposed by the instruction; see Section 2.5. Thus, an execution path can be encoded as a vector constructed by concatenating subvectors corresponding to each instruction. Batchman uses this encoding to hide the identity of each instruction from  $\mathcal{V}$ . In particular, this vector encoding the execution path is included in the proof as part of  $\mathcal{P}$ 's (extended) witness.

If  $\mathcal{P}$  is honest, this vector encodes a valid execution path.  $\mathcal{P}$  proves her witness satisfies linear constraints imposed by the vector.

Of course,  $\mathcal{V}$  must check in ZK that  $\mathcal{P}$ 's execution path vector is valid – that each subvector (or, rather, each subvector's hash) is in the set of valid instructions (hashes) of the source program. Batchman's ZK hash check is efficient: each subvector hash is a random linear combination of the subvector's elements based on a fresh challenge from  $\mathcal{V}$ – a single uniform field element sent by  $\mathcal{V}$ , expanded by taking its powers. A crucial detail here is that  $\mathcal{V}$  knows the boundaries of the subvectors, as Batchman's instructions are each padded to the same publicly agreed-upon number of gates.

In our approach, we allow instructions of different sizes. Thus, while our prover also inputs an execution path vector, the subvector (i.e., instruction) boundaries and the lengths of each subvector must be kept private. With this change, the subvector validity check and passing of program state between instructions become a challenge, the resolution of which is core to our contribution. Here, we give high-level intuition underlying our validity check.

To validate the execution path vector,  $\mathcal{P}$  inputs an additional 0-1 vector of the same length, which defines the boundaries of the instruction subvectors. Namely,  $\mathcal{P}$  sets this boundary string to 0 and places 1 only at positions corresponding to the ends of subvectors. Similar to Batchman, our hash check is performed via a random linear combination with a  $\mathcal{V}$ -chosen challenge, but we carefully arrange how parties use the boundary string to construct and verify hash checksums of unknown length to  $\mathcal{V}$ . We capture this with a novel primitive of independent interest – an unbalanced ZK read-only memory (ROM) – a ZK ROM capable of storing vectors of different lengths, but where we do not pay the price of the largest vector for each memory element (by exploiting the boundary string). Based on the above intuition, our unbalanced ZK ROM manages (loads, concatenates and checks) vectors of different lengths.

#### 1.4 Related Work

Efficient handling of disjunctive statements is central to the handling of ZK proofs expressed as high-level programs. High-level-program-based ZK is an intuitive direction that was first concretely explored by [BCG<sup>+</sup>13] and subsequently studied by [BCTV14a, BCTV14b, FKL<sup>+</sup>21, GHAK23, HYDK21, YHKD22].

Early ZK work [CDS94] gave special-purpose techniques allowing proofs of disjunctions. With relatively recent and dramatic improvement to proofs of general-purpose statements, special-purpose disjunction handling was (temporarily) subsumed by general-purpose techniques. Indeed, disjunctions are easily encoded and proved as part of a circuit that processes each branch and then multiplexes the results. While this works, it is expensive. [HK20] – building on the MPC result of [Kol18]

– demonstrated feasibility of paying (in ZK proof size) for only one branch. The [HK20] technique "reuses cryptographic material" of the active branch to evaluate (to garbage and privately discard) inactive branches. This sparked a rich line of work [BMRS21, GGHAK22, GHAK23, GHAKS23, HK20, Kol18, YHH<sup>+</sup>23] that continues to reduce the costs of ZK disjunctions.

Very recent work [GHAK23, YHH<sup>+</sup>23] further improved the handling of disjunctions by showing how to improve not just communication but also *computation*. This task is more challenging and cannot be achieved by prior techniques relying on garbage evaluation of inactive clauses. Leveraging the *batched* setting where a single disjunction is executed repeatedly, these works show how  $\mathcal{P}$  and  $\mathcal{V}$  compute (and hence communicate) proportionally only to the single largest clause of the disjunction. Our work extends and crucially builds on the approach of [YHH<sup>+</sup>23], and our extension enables paying only for the *active* branch. Sections 1.3 and 2.5 summarize [YHH<sup>+</sup>23] and the novel techniques needed for our result. Neither [YHH<sup>+</sup>23] nor [GHAK23] address disjunctions of clauses of varying sizes.

Efficient ZK ROM and RAM are essential to CPU-emulation ZK. We integrate recent ZK ROM [YH24]. We also build on it to design a novel basic primitive *unbalanced ZK ROM*, capable of retrieving variable-size entries in a batch query. We achieve this by extending randomized hashes of [YHH<sup>+</sup>23] to vectors of differing lengths and ultimately use them to execute variable-size instructions.

We note that emulating CPU in SNARK has also been intensively studied recently in, e.g., [KS22, CGG<sup>+</sup>23, DXNT23, ZGK<sup>+</sup>18, HLZ<sup>+</sup>24, KST22, KS24]. Some of these elegant works (e.g., [KS22, KS24, ZGK<sup>+</sup>18, HLZ<sup>+</sup>24]) can indeed achieve tight efficiency while offering attractive features such as non-interactivity and succinctness. However, adding ZK to these works may either require large overheads or break tightness (see, e.g., discussions in [GHAK23] and [LXZ<sup>+</sup>24]). Furthermore, they (at least) reveal the number of instructions to the verifier, while our work reveals only the total number of multiplication gates. See Section 3 for more formal discussions. We suspect that some padding techniques might address the additional leakage in, e.g., [KS22, KS24], and we leave it as valuable future work. Finally, we remark that our protocols can also be instantiated with a succinct and non-interactive commit-and-prove zkSNARK.

#### 2 Preliminaries

#### 2.1 Notation

- $\lambda$  is the statistical security parameter (e.g., 40 or 60).

- The prover is  $\mathcal{P}$ . We refer to  $\mathcal{P}$  by she, her, hers...

- The verifier is  $\mathcal{V}$ . We refer to  $\mathcal{V}$  by he, him, his...

- $x \triangleq y$  denotes that x is defined as y.

- We denote sets by upper-case letters. We denote that x is uniformly drawn from a set S by  $x \in_{\$} S$ .

- We denote  $\{1,\ldots,n\}$  by [n].

- We denote a finite field of size p by  $\mathbb{F}_p$  where  $p \geq 2$  is a prime or a power of a prime. We use  $\mathbb{F}$  to represent a sufficiently large field, i.e.,  $|\mathbb{F}| = \lambda^{\omega(1)}$ . Inverse(x) denotes the multiplicative inverse of  $x \neq 0$  in  $\mathbb{F}$ , i.e., Inverse $(x) \cdot x = 1$ .

- For a vector  $\mathbf{a} \in \mathbb{F}^n$  and an element  $x \in \mathbb{F}$ ,  $x\mathbf{a} \triangleq (xa_1, \dots, xa_n)$ .

- $\mathsf{last}(a)$  denotes the last element of a, i.e.,  $a_n$  if  $a \in \mathbb{F}^n$ . For some  $a \in \mathbb{F}^*$ , if  $\mathsf{last}(a) \neq 0$ , we refer

to **a** as a non-zero-end vector.

- We denote row vectors by bold lower-case letters (e.g.,  $\boldsymbol{a}$ ), where  $a_i$  (or a[i]) denotes the *i*-th component of  $\boldsymbol{a}$  (starting from 1) and  $\boldsymbol{a}[:i]$  the subvector  $(a_1,\ldots,a_i)$ .

- We denote matrices by bold upper-case letters (e.g.,  $\mathbf{A}$ ), where  $\mathbf{A}(i)$  denotes the i-th row vector of  $\mathbf{A}$  (starting from 1) and  $\mathbf{A}[i]$  denotes the i-th column vector of  $\mathbf{A}$  (starting from 1).  $\mathbf{A}(i)[j]$  denotes j-th value in i-th row.

- Let a and b be vectors of equal length.  $\langle a, b \rangle$  denotes the inner product;  $a \odot b$  denotes the element-wise product.

- We denote a multiplication (gate) by MULT.

#### 2.2 Security Model

We formalize our protocol via the universally composable (UC) framework [Can01] and prove its security in the presence of a *malicious*, *static* adversary. For simplicity, we omit standard UC session (and sub-session) IDs.

#### 2.3 Commit-and-Prove Zero-Knowledge

Our protocol is defined in the *commit-and-prove* hybrid model [CLOS02]. This functionality, denoted by  $\mathcal{F}_{\mathsf{CPZK}}$  and formally defined in Figure 3, allows  $\mathcal{P}$  to commit to field elements (over  $\mathbb{F}$ ) and then prove that evaluating a particular circuit on the committed values yields a vector of 0's. We denote by  $\mathsf{com}(\alpha)$  a cryptographic commitment to  $\alpha \in \mathbb{F}$ , and naturally extend this notation to vectors (e.g.,  $\mathsf{com}(\alpha)$ ).

There are several ways to instantiate  $\mathcal{F}_{\mathsf{CPZK}}$  (e.g., [AHIV17, BMRS21, BBB<sup>+</sup>18, CHM<sup>+</sup>20, DOT21, DIO21, IKOS07, MBKM19, YSWW21]). To concretely evaluate our abstraction, we choose to instantiate our protocol via the VOLE-based ZK (e.g., [BMRS21, DIO21, YSWW21], cf. Lemma 1), a proof paradigm known for its fast end-to-end running times and small (constant) computation/communication rates compared to  $|\mathcal{C}|$ . This paradigm employs information-theoretic MACs (IT-MACs) [BDOZ11, NNOB12] as linearly homomorphic commitment schemes over  $\mathbb{F}$ . We describe the computation/communication of VOLE-based ZK in Lemma 1.

**Lemma 1** (VOLE-based ZK). There exists a protocol  $\Pi_{CPZK}$  that UC-realizes  $\mathcal{F}_{CPZK}$  in the  $\mathcal{F}_{VOLE}$ -hybrid model (Figure 2) with the following efficiency:

- Commit requires 1 field element of communication and  $\mathcal{O}(1)$  field operations.

- Linear requires no communication and O(k) field operations.

- Open requires 2 field elements of communication and  $\mathcal{O}(1)$  field operations, with soundness error  $\mathcal{O}(\frac{1}{|\mathbb{F}|})$ .

- For circuit C with m outputs and  $n_{\times}$  multiplication gates, Check requires  $n_{\times} + m + 3$  field elements of communication and  $\mathcal{O}(|\mathcal{C}|)$  field operations, with soundness error  $\mathcal{O}(\frac{|\mathcal{C}|}{|\mathbb{F}|})$ .

- Communication of Check for certain circuits can be improved at the cost of computation and soundness. In particular, for a circuit C that outputs m polynomials  $f_1, \ldots, f_m$  where  $f_{i \in [m]}$  is of degree- $d_i$ , Check can be performed with:

- $\max_{i \in [m]} d_i + 1$  field elements of communication;

#### Functionality $\mathcal{F}_{VOLE}$

$\mathcal{F}_{VOLE}$ , parameterized by a field  $\mathbb{F}$ , proceeds as follows, running with a prover  $\mathcal{P}$ , a verifier  $\mathcal{V}$  and an adversary  $\mathcal{S}$ :

Initialize. Upon receiving (init) from  $\mathcal{P}$  and  $\mathcal{V}$ , if  $\mathcal{V}$  is honest, sample  $\Delta \in_{\$} \mathbb{F}$ , else receive  $\Delta$  from  $\mathcal{S}$ . Store  $\Delta$  and send it to  $\mathcal{V}$ . Ignore subsequent (init).

**Extend.** Upon receiving (extend, n) from  $\mathcal{P}$  and  $\mathcal{V}$ :

- If  $\mathcal{V}$  is honest, sample  $\mathbf{v} \in_{\$} \mathbb{F}^n$ , else receive  $\mathbf{v} \in \mathbb{F}^n$  from  $\mathcal{S}$ .

- If  $\mathcal{P}$  is honest, sample  $\boldsymbol{u} \in_{\$} \mathbb{F}^n$  and compute  $\boldsymbol{w} \triangleq \boldsymbol{v} \boldsymbol{u} \cdot \Delta \in \mathbb{F}^n$ , else receive  $\boldsymbol{u} \in \mathbb{F}^n$  and  $\boldsymbol{w} \in \mathbb{F}^n$  from  $\mathcal{S}$  and compute  $\boldsymbol{v} \triangleq \boldsymbol{w} + \boldsymbol{u} \cdot \Delta \in \mathbb{F}^n$ .

- Send  $(\boldsymbol{u}, \boldsymbol{w})$  to  $\mathcal{P}$  and  $\boldsymbol{v}$  to  $\mathcal{V}$ .

Figure 2: The VOLE correlation functionality.

- $-\mathcal{O}\left((\max_{i\in[m]}d_i)^2\cdot|\mathcal{C}|\right)$  field operations; and

- $-\mathcal{O}\left(\frac{m+\max_{i\in[m]}d_i}{|\mathbb{F}|}\right)$  soundness error.

This is useful, e.g., when we want to prove that  $\mathbf{a} \odot \mathbf{b} = \mathbf{0}$ .

**Testing vector equality.** We apply the *Swchartz-Zippel* lemma as a central tool to prove the equality of two (committed) vectors.

**Lemma 2** (Vector Equality). Consider vectors  $a, b \in \mathbb{F}^n$ . If  $a \neq b$ , then for  $\chi \in_{\$} \mathbb{F}$ :

$$\Pr[\langle (1, \chi, \dots, \chi^{n-1}), \boldsymbol{a} \rangle = \langle (1, \chi, \dots, \chi^{n-1}), \boldsymbol{b} \rangle] \le \frac{n}{|\mathbb{F}|}$$

Specifically, suppose the parties hold committed vectors com(a) and com(b), and  $\mathcal{P}$  wishes to convince  $\mathcal{V}$  that a is equal to b. Lemma 2 states that it suffices for  $\mathcal{P}$  to prove that  $\langle (1, \chi, \dots, \chi^{n-1}), a \rangle = \langle (1, \chi, \dots, \chi^{n-1}), b \rangle$ , where  $\chi$  is some uniform challenge sampled by  $\mathcal{V}$ . Note that zero-end vectors of different lengths (e.g., a = (1, 1) and b = (1, 1, 0)) are not captured by Lemma 2. On the other hand, it does extend to non-zero-end vectors of potentially different lengths (Corollary 1). Looking ahead, we need Corollary 1 because  $\mathcal{V}$  does not know the boundaries of instructions/subvectors whose equality is proven by  $\mathcal{P}$  in the tight ZK CPU.

Corollary 1. Consider vectors  $\mathbf{a} \in \mathbb{F}^{n_a}$ ,  $\mathbf{b} \in \mathbb{F}^{n_b}$  where  $a[n_a], b[n_b] \neq 0$ . If  $\mathbf{a} \neq \mathbf{b}$ , for  $\chi \in_{\$} \mathbb{F}$ :

$$\Pr[\langle (1, \chi, \dots, \chi^{n_a - 1}), \boldsymbol{a} \rangle = \langle (1, \chi, \dots, \chi^{n_b - 1}), \boldsymbol{b} \rangle] \leq \frac{n}{|\mathbb{F}|}$$

where  $n \triangleq \max\{n_a, n_b\} - 1$ .

#### Functionality $\mathcal{F}_{\mathsf{CPZK}}$

$\mathcal{F}_{\mathsf{CPZK}}$ , parameterized by a field  $\mathbb{F}$ , proceeds as follows, running with a prover  $\mathcal{P}$ , a verifier  $\mathcal{V}$ , and an adversary  $\mathcal{S}$ :

**Commitments.** On receiving (Commit, cid, x) from  $\mathcal{P}$  where (a) there is no recorded tuple (cid, ·), and (b)  $x \in \mathbb{F}$ : Record tuple (cid, x) and send (commit, cid) to  $\mathcal{V}$  and  $\mathcal{S}$ .

**Linear Combination.** On receiving (Linear, cid, cid, cid, cid, cod, cod,

- 1. Fetch recorded  $(cid_1, x_1), \ldots, (cid_k, x_k)$ .

- 2. Compute  $x := c_0 + c_1 x_1 + \cdots + c_k x_k$ . Record (cid, x).

- 3. Send (linear, cid,  $cid_1$ , ...,  $cid_k$ ,  $c_0$ , ...,  $c_k$ ) to  $\mathcal{V}$ ,  $\mathcal{S}$ .

**Open.** On receiving (Open, cid) from  $\mathcal{P}$  where cid has a recorded tuple, fetch (cid, x), send (open, cid, x) to  $\mathcal{V}$  and  $\mathcal{S}$ .

**Check.** On receiving  $(\mathsf{Check}, \mathcal{C}, cid_1, \dots, cid_n)$  from  $\mathcal{P}$  where (a)  $\mathcal{C}: \mathbb{F}^{(n)} \to \mathbb{F}^{(*)}$  is an arithmetic circuit, and (b) each  $cid_{i \in [n]}$  has a recorded tuple: Fetch tuples  $(cid_1, x_1), \dots, (cid_n, x_n)$  and compute  $\mathbf{y} := \mathcal{C}(x_1, \dots, x_n)$ . If  $\mathbf{y} = 0^{(*)}$ , send  $(\mathsf{check}, \mathcal{C}, cid, \mathsf{true})$  to  $\mathcal{V}$  and  $\mathcal{S}$ ; else send  $(\mathsf{check}, \mathcal{C}, cid, \mathsf{false})$  to  $\mathcal{V}$  and  $\mathcal{S}$ .

Figure 3: Ideal functionality for commit-and-prove ZK. Each committed element is associated with a unique identifier cid. Linear operation allows  $\mathcal{P}$  to generate a new commitment (associated with cid) via a public affine function over committed elements.

#### 2.4 Zero-Knowledge Read-Only Memory

Our protocol uses an extended version of  $\mathcal{F}_{\mathsf{CPZK}}$  where parties can access a  $\mathit{Zero-Knowledge Read-Only Memory}$  or ZK ROM (e.g., [DdSGOTV22, FKL+21, YH24]). Namely, ZK ROM allows  $\mathcal{P}$  to specify n commitments to initialize a key-value store data structure (K-V store) indexed by the key  $k \in [n]$ . Subsequently, given  $\mathsf{com}(i)$ , where  $i \in [n]$ ,  $\mathcal{P}$  and  $\mathcal{V}$  generate a new commitment  $\mathsf{com}(x)$  where x is the i-th committed value in the K-V store. Our protocol uses a restricted (batch-read) version of ZK ROM formalized in Figure 4. I.e.,  $\mathcal{P}$  is allowed a  $\mathit{single}$  ReadROM call, where  $\mathcal{P}$  specifies an arbitrarily long vector of ROM indices, possibly with repetitions. This will allow  $\mathcal{P}$  to load a sequence of hashes corresponding to the execution path (note, we later introduce a stronger  $\mathit{novel}$  primitive, unbalanced ROM, to load the concatenation of variable-length instruction vectors, realized in the  $\mathcal{F}_{\mathsf{CPZK-ROM}}$ -hybrid model). [YH24] shows the state-of-the-art realization of  $\mathcal{F}_{\mathsf{CPZK-ROM}}$  in the  $\mathcal{F}_{\mathsf{CPZK-hybrid}}$  model (see Lemma 3).

**Lemma 3** (ZK ROM). Let  $n = \text{poly}(\lambda)$ ,  $m = \Omega(n)$ . There exists a protocol  $\Pi_{\text{CPZK-ROM}}$  that UC-emulates  $\mathcal{F}_{\text{CPZK-ROM}}$  (Figure 4) in the  $\mathcal{F}_{\text{CPZK-hybrid}}$  model (Figure 3) with the following efficiency metrics:

- InitROM requires  $\mathcal{P}$  to only send cid to  $\mathcal{V}$ , and n+1 Linear hybrid calls to generate  $com(0), \ldots, com(n)$ .

- ReadROM requires 2m Commit hybrid calls.

- CheckSet requires 2n Commit hybrid calls, followed by V's sending 4 uniform elements in  $\mathbb{F}$  and a Check hybrid call, where C is dominated by two products each has n+m-1 MULTs.

#### Functionality $\mathcal{F}_{CPZK-ROM}$

$\mathcal{F}_{\mathsf{CPZK-ROM}}$ , parameterized by a field  $\mathbb{F}$ , proceeds as follows, running with a prover  $\mathcal{P}$ , a verifier  $\mathcal{V}$  and an adversary  $\mathcal{S}$ :

CPZK

The functionality supports all instructions of  $\mathcal{F}_{\mathsf{CPZK}}$ .

Read-Only Memory

**Initialize ROM.** On receiving (InitROM,  $cid_1, \ldots, cid_n$ ) from  $\mathcal{P}$  where each  $cid_{i \in [n]}$  was recorded: Fetch  $(cid_1, x_1), \ldots, (cid_n, x_n)$ , create a key-value store X where

$$X[1] := x_1, \cdots, X[n] := x_n$$

and set  $f_{rom} := honest$ . Send (initrom, cid) to V and S. Ignore subsequent calls to InitROM.

**Read ROM.** On receiving (ReadROM,  $cid_1, \ldots, cid_m, y_1, \ldots, y_m, cid_1^{(id)}, \ldots, cid_m^{(id)}$ ) from  $\mathcal{P}$  where

- 1. InitROM has been executed; and

- 2. there is no recorded tuple for each  $(cid_{i \in [m]}, \cdot)$ ; and

- 3. each  $y_{i \in [m]} \in \mathbb{F}$ ; and

- 4. each  $cid_{i \in [m]}^{(id)}$  was recorded.

Fetch  $(cid_1^{(id)}, id_1), \ldots, (cid_m^{(id)}, id_m)$ . Record  $(cid_1, y_1), \ldots, (cid_m, y_m)$ . If  $\mathcal{P}$  is honest,  $\forall i \in [m], X[id_i] = y_i$  where  $id_i \in [n]$ . If  $\mathcal{P}$  is corrupted, set  $f_{\mathsf{rom}} := \mathsf{cheating}$  when

- 1. there exists an  $id_{i \in [m]} \notin [n]$ , where n is the size of X; or

- 2. there exists an  $i \in [m]$  such that  $X[id_i] \neq y_i$ .

Send (readrom, cid, cid<sup>(id)</sup>) to V, S. Ignore subsequent ReadROM calls.

Check ROM. On receiving (CheckROM) from  $\mathcal{P}$  where InitROM and ReadROM were executed: If  $\mathcal{P}$  is corrupted and  $\mathcal{S}$  sends Cheat, set  $f_{\text{rom}} := \text{cheating}$ . Send (checkrom,  $f_{\text{rom}}$ ) to  $\mathcal{V}$  and  $\mathcal{S}$ .

Figure 4: Ideal functionality for commit-and-prove zero-knowledge allowing proofs that support a read-only memory.  $\mathcal{P}$  specifies the result of the ReadROM operation. However, if  $\mathcal{P}^*$  provides an incorrect result, the flag  $f_{\text{rom}}$  will be set to cheating.

Figure 5: (a) An arithmetic circuit computing  $(in_1 \cdot in_2) + (in_2 + 3)^2$  and its (b) original and (c) refined topology matrix.

#### 2.5 ZKP via Topology Matrices

Consider a circuit  $\mathcal{C}$  with  $n_{in}$  inputs and  $n_{\times}$  multiplication gates. Note that a ZKP for  $\mathcal{C}$  can be separated into two parts: (1) multiplication gates and (2) linear constraints. Suppose that  $\mathcal{P}$  commits to its input  $\mathsf{com}(in_1), \ldots, \mathsf{com}(in_{n_{in}})$ , and also commits to the values on the  $3n_{\times}$  wires associated with  $\mathcal{C}$ 's  $n_{\times}$  multiplication gates. I.e.,  $\mathcal{P}$  commits to  $\mathsf{com}(\ell_1), \ldots, \mathsf{com}(\ell_{n_{\times}})$ , corresponding to the multiplication left input wires, to  $\mathsf{com}(r_1), \ldots, \mathsf{com}(r_{n_{\times}})$ , corresponding to the right input wires, and to  $\mathsf{com}(o_1), \ldots, \mathsf{com}(o_{n_{\times}})$ , corresponding to the output wires. The full vector of  $\mathcal{P}$ 's input and the multiplication wires (with a constant 1) is called  $\mathcal{P}$ 's extended witness.

Now,  $\mathcal{P}$  first proves to  $\mathcal{V}$  that  $\ell \odot r = o$ , demonstrating that its extended witness satisfies multiplicative constraints. Then, it proves that  $in, \ell, r, o$  indeed respect the linear constraints imposed by circuit  $\mathcal{C}$ . Note that since all multiplication gates were handled in the first step,  $\mathcal{P}$  simply needs to show its extended witness respects a particular linear relation – i.e. a matrix M. This public matrix M is induced by the structure of the circuit  $\mathcal{C}$ , and [YHH<sup>+</sup>23] refers to M as a topology matrix. Namely,  $\mathcal{P}$  proves the following:

$$\mathbf{M} \times (1, i\mathbf{n}, \ell, r, o)^T = \mathbf{0}$$

(1)

Since  $in, \ell, r, o$  are committed, this equality check can be handled by  $\mathcal{V}$ 's sending of a uniform challenge  $\chi \in_{\$} \mathbb{F}$  where  $\mathcal{P}$  uses  $\mathcal{F}_{\mathsf{CPZK}}$  to construct a commitment to

$$\underbrace{(1, \chi, \dots, \chi^{2n_{\times}}) \times \mathbf{M}}_{\text{topology vector}} \times \underbrace{(1, \mathbf{in}, \boldsymbol{\ell}, \mathbf{r}, \mathbf{o})^{T}}_{\text{extended witness}}$$

(2)

and then proves to  $\mathcal{V}$  that this is a commitment to 0. Recall that M is public, so once  $\chi$  is fixed, both  $\mathcal{P}$  and  $\mathcal{V}$  know  $(1,\ldots,\chi^{2n_{\times}})\times M$  (called a *topology vector*). Thus, it suffices to check whether the inner product between the topology vector and the extended witness yields 0. Figure 5b shows an example topology matrix.

**Proving batched disjunctions:** Batchman [YHH<sup>+</sup>23]. The above paradigm is an overkill if we only perform a ZKP for a single public circuit. This is because it is worse than the state-of-the-art VOLE-based CPZK (e.g. QuickSilver [YSWW21]), which only requires committing *in* and

#### Functionality $\mathcal{F}_{ZKCPU}$

$\mathcal{F}_{\mathsf{ZKCPU}}$  runs with a prover  $\mathcal{P}$ , a verifier  $\mathcal{V}$  and an adversary  $\mathcal{S}$ , and is parameterized by a field  $\mathbb{F}$ , an nonnegative integer m, a positive integer B and B m-instructions (Definition 1)  $\mathcal{C}_1, \ldots, \mathcal{C}_B$ , an initial state  $\mathbf{st}^{(0)} \in \mathbb{F}^m$  and a final state  $\mathbf{st}^{(final)} \in \mathbb{F}^m$ . For each  $i \in [B]$ , let m-instruction  $\mathcal{C}_i$  have  $n_{in}^{(i)}$  inputs and  $n_{\times}^{(i)}$  multiplication gates. Note that  $n_{in}^{(i \in [B])} \geq m$ . W.l.o.g., for each  $i \in [B]$ , assume  $n_{in}^{(i)} - m = n_{\times}^{(i)} + m + 2$  and denote this value as  $n^{(i)}$ .  $\mathcal{F}_{\mathsf{ZKCPU}}$  proceeds as follows:

On receiving (Prove,  $\tau, i_1, \ldots, i_{\tau}, in_1, \ldots, in_{\tau}$ ) from  $\mathcal{P}$  where (1)  $\tau$  is a positive integer (i.e., the *private* steps), (2)  $i_{j \in [\tau]} \in [B]$ , and (3) each  $in_{j \in [\tau]} \in \mathbb{F}^{n_{in}^{(i_j)} - m}$  (i.e., the inputs except registers), proceed as follows:

- 1. Set  $st := st^{(0)}$  and f := true. For each  $j \in [\tau]$  in order:

- (a) Let  $st' || f' := C_{i_j}(st || in_j)$  where  $st' \in \mathbb{F}^m$ ,  $f' \in \mathbb{F}$ . I.e., st' is the updated registers and f' is the checking output.

- (b) Set st := st'. If  $f' \neq 0$  (i.e., invalid checking), set f := false.

- 2. If  $st \neq st^{(final)}$  (i.e., incorrect final state), set f := false.

- 3. Let  $n \triangleq n^{(i_1)} + \cdots + n^{(i_{\tau})}$ . If  $\mathcal{P}$  is corrupted,  $\mathcal{S}$  can send (Cheat, n') where  $n' \in \mathbb{Z}^+$ : Set  $f := \mathtt{false}$ , n := n'.

- 4. Send (prove, f, n) to  $\mathcal{V}$  and  $\mathcal{S}$ .

Figure 6: Ideal functionality for a tight ZK CPU.

o. However, this paradigm becomes useful when considering a batch of disjunctions, as observed by Batchman [YHH<sup>+</sup>23].

In detail, Batchman [YHH+23] considers B different circuits  $C_1, \ldots, C_B$  of the same size.  $\mathcal{P}$  wants to repeat the disjunctive proof R times – for each  $i \in [R]$ , she proves that she knows some witness  $\mathbf{w}_i$  and some index  $id_i \in [B]$  such that  $C_{id_i}(\mathbf{w}_i) = 0$ . To achieve this, for the i-th repetition,  $\mathcal{P}$  commits to her extended witness of only  $C_{id_i}$ .  $\mathcal{V}$  then issues a uniform challenge  $\chi$  to compress B topology matrices to B topology vectors. The crucial step is that, for the i-th repetition,  $\mathcal{P}$  can commit to the  $id_i$ -th topology vector. An extra mechanism is needed to prevent  $\mathcal{P}$  from committing to an arbitrary vector that is not a topology vector, which can be built based on a ZK ROM (storing and then loading vectors' hashes). Finally, it suffices to show that the inner product between the extended witness and the topology vector is 0 for each repetition. Batchman can be viewed as a non-tight ZK CPU (with extra constraints to support registers).

Note, topology matrices (combined with multiplication constraints) support efficient branching, and thus is a more convenient program representation than, e.g., R1CS [BCG<sup>+</sup>13], for our setting.

# 3 Our Target Functionality: $\mathcal{F}_{\mathsf{ZKCPU}}$

We define the functionality of a tight ZK CPU realized by our protocol. To define a ZK CPU over  $\mathbb{F}$ , we need to specify: (1)  $B \in \mathbb{Z}^+$  denotes the number of instructions; (2)  $m \in \mathbb{Z}^+$  denotes the number of registers; and (3) each instruction (see Definition 1) is defined as a circuit (over  $\mathbb{F}$ ) mapping  $\geq m$  values to m+1 values.

**Definition 1** (Instruction). An instruction is a circuit  $C : \mathbb{F}^{n_{in}} \to \mathbb{F}^{m+1}$  where  $n_{in} \geq m$ . In particular, we consider standard fan-in 2 circuits over  $\mathbb{F}$  with addition and multiplication gates.

We call an instruction  $C: \mathbb{F}^{n_{in}} \to \mathbb{F}^{m+1}$  a m-instruction, where the first m output wires of C's capture the updated CPU registers, and the last wire is a checking output (0 in a valid execution).

In a tight ZK CPU execution,  $\mathcal{P}$  and  $\mathcal{V}$  agree on the initial/final state of the m registers (called the initial/final state), where  $\mathcal{P}$  demonstrates her ability to execute the initial state to the final state by a sequence of (potentially repeatedly) instructions. We formalize this functionality in Figure 6 with the following remarks:

- 1. For each instruction  $C^{(i)}$  with  $n_{\times}^{(i)}$  multiplications,  $n_{in}^{(i)}$  inputs, and m registers, the size of this instruction is defined as  $n^{(i)} = n_{in}^{(i)} m = n_{\times}^{(i)} + m + 2$ . Essentially,  $n^{(i)}$  reflects the number of the multiplication gates in  $C^{(i)}$ . We note that our protocol introduces m+2 extra multiplication gates, which are used to constrain m input registers, the constant 1 input, and the checking output. The equality can be enforced by simply padding the instruction with dummy inputs or multiplications. Looking ahead, this equality ensures that the total execution path length hides the executed instructions.

- 2.  $\mathcal{F}_{\mathsf{ZKCPU}}$  reveals n the total runtime to  $\mathcal{V}$ . Prior non-tight ZK CPUs achieve a similar functionality where  $\mathcal{V}$  learns the number of executed instructions  $\tau$ . We remark that this implies that  $\mathcal{V}$  cannot learn  $\tau$  directly in the tight ZK CPU.

- 3. In Figure 6,  $\mathcal{P}$  arbitrarily selects which instructions to execute. In some use cases (e.g., when emulating real-world CPUs),  $\mathcal{P}$ 's chosen instructions should be constrained by the current register state. For example, a program counter register might dictate which instruction runs next. Such constraints can be captured by each instruction's checking output wire, which must be 0 in a valid proof (see Sub-step 1b).

- 4.  $\mathcal{F}_{\mathsf{ZKCPU}}$  only supports limited state (i.e., up to m registers) to be passed between instructions. Perhaps surprisingly, we show that by introducing 5 special registers and 2 extra rounds, our protocol can natively support a large (poly-size in  $\lambda$ ) read-write random access memory (see Section 6.2).

#### 4 Technical Overview

In this section, we provide a technical overview of our tight ZK CPU protocol. Full formalization and detailed cost analysis are postponed to subsequent sections. We refer the reader to Section 1.3 for a high-level intuition. The main steps to achieve our target ideal functionality  $\mathcal{F}_{\mathsf{ZKCPU}}$  (Figure 6) are outlined as follows.

$$\mathcal{F}_{\mathsf{CPZK\text{-}ROM}} \overset{\mathrm{Sections}}{\Longrightarrow} \overset{4,4}{\Longrightarrow} \text{ and } \overset{5}{\Longrightarrow} \mathcal{F}_{\mathsf{CPZK\text{-}UROM}} \overset{\mathrm{Sections}}{\Longrightarrow} \overset{4,3}{\Longrightarrow} \text{ and } \overset{5}{\Longrightarrow} \mathcal{F}_{\mathsf{ZKCPU}}$$

#### 4.1 Boundary Strings and Helper Notation

Recall our discussion from Section 1.3 regarding a 0-1 vector of field elements used by our protocol, denoted as a *boundary string*. This section formally defines the boundary strings and introduces useful notations for demonstrating how these strings will be used.

For a vector  $\mathbf{p} \in \mathbb{F}^n$  where  $n \in \mathbb{Z}^+$ , we say that  $\mathbf{p}$  is a boundary string if and only if  $\mathbf{p} \in \{0,1\}^{n-1} \| 1$ . We note that it is efficient to check whether  $\mathsf{com}(\mathbf{p})$  commits to a valid boundary string. Namely, given  $\mathsf{com}(\mathbf{p})$ ,  $\mathcal{P}$  opens  $p_n$  to prove it is 1, and  $\mathcal{P}$  proves  $\mathbf{p} \odot (\mathbf{1} - \mathbf{p}) = \mathbf{0}$  (i.e., each  $p_{i \in [n]}$  is either 0 or 1).

We use  $\mathsf{HW}(p)$  to denote the *Hamming weight* of a boundary string. I.e., the number of ones in p. We now introduce two functions Partition and Filter that we use as analysis tools. We emphasize that we never run these functions inside ZK.

Partition. Consider a length-n boundary string p. p specifies a partition of a length-n vector v into HW(p) subvectors. We define a function Partition:

$$oldsymbol{p} = (\overbrace{0,\ldots,0,1}^{n_1},\overbrace{0,\ldots,0,1}^{n_2},\overbrace{0,\ldots,0,1}^{n_3},\ldots), oldsymbol{v} \in \mathbb{F}^n$$

$\Rightarrow \mathsf{Partition}(oldsymbol{p},oldsymbol{v}) = \left(oldsymbol{v}^{(1)},\ldots,oldsymbol{v}^{(HW(oldsymbol{p}))}\right) \text{ such that }$   $oldsymbol{v}^{(1)} = (v_1,\ldots,v_{n_1}), oldsymbol{v}^{(2)} = (v_{n_1+1},\ldots,v_{n_1+n_2}),\cdots$

Filter. A length-n boundary string p also specifies a way to filter a length-n vector v into a length-HW(p) vector. We define a function Filter:

$$\begin{split} \boldsymbol{p} &= (\overbrace{0,\ldots,0,1}^{n_1},\overbrace{0,\ldots,0,1}^{n_2},\overbrace{0,\ldots,0,1}^{n_3},\ldots), \boldsymbol{v} \in \mathbb{F}^n \\ \Rightarrow & \mathsf{Filter}(\boldsymbol{p},\boldsymbol{v}) = (v_{n_1},v_{n_1+n_2},v_{n_1+n_2+n_3},\ldots,v_n) \end{split}$$

**Expanding random challenges.** In our protocol, V will issue random challenges, which will be composed with P's chosen boundary string. We consider two ways to compose these:

1. For some public challenge  $\chi \in \mathbb{F}$ , let  $s_1 \triangleq 1$ , and for each  $i \in [n-1]$  in order, let  $s_{i+1} := s_i(1-p_i) + \chi^i p_i$ . That is,

$$\mathbf{p} = (0, \dots, 0, 1, 0, \dots, 0, 1, 0, \dots, 0, 1, \dots)$$

$$\Rightarrow \mathbf{s} = (1, \dots, 1, \underbrace{\chi^{n_1}, \dots, \chi^{n_1}}_{n_2}, \underbrace{\chi^{n_1 + n_2}, \dots, \chi^{n_1 + n_2}}_{n_3}, \dots)$$

We denote this procedure by  $s \triangleq \mathsf{Expand}_1(\boldsymbol{p}, \chi)$ .

2. For some public challenge  $\gamma \in \mathbb{F}$ , let  $s_1 \triangleq 1$ , for each  $i \in [n-1]$  in order, let  $s_{i+1} := \gamma s_i(1-p_i) + p_i$ . That is,

$$\begin{aligned} & \boldsymbol{p} = (\overbrace{0, \dots, 0, 1}^{n_1}, \overbrace{0, \dots, 0, 1}^{n_2}, \overbrace{0, \dots, 0, 1}^{n_3}, \dots) \\ \Rightarrow & \boldsymbol{s} = (1, \gamma, \dots, \gamma^{n_1 - 1}, 1, \gamma, \dots, \gamma^{n_2 - 1}, 1, \gamma, \dots, \gamma^{n_3 - 1}, \dots) \end{aligned}$$

We denote this procedure by  $s \triangleq \mathsf{Expand}_2(\boldsymbol{p}, \gamma)$ .

Starting from com(p), we can compute commitments to the above compositions (i.e., com(s)) each via a circuit with n-1 MULTs.

#### 4.2 More Powerful Topology Matrices

This section includes how we adjust and optimize the definitions of the topology matrices (discussed in Section 2.5) for our setting.

We first introduce a  $\approx 2 \times$  optimization to the topology matrix/vector of [YHH<sup>+</sup>23] (see Figure 5c). Note that the order of the multiplication inputs in the [YHH<sup>+</sup>23] topology matrix is fixed (e.g., in Figure 5b, this order is  $\ell_1, \ell_2, r_1, r_2, 0$ ). Based on this observation, there is no need to include the constraints of these fixed order wires internally in the topology matrix (see Figure 5c, refined topology), reducing its size in roughly two and achieving corresponding improvement.

However, neither the topology matrix format of [YHH<sup>+</sup>23] nor the above improvement are suited to our setting because their verifier knows the instruction boundaries, and hence, explicit routing of registers and other wires into instruction entry points is allowed. We must hide this topology from  $\mathcal{V}$ . To facilitate this, we further rearrange the topology matrices of instructions of our ZK CPU (Figure 6). In particular, constants 0 and 1 and instruction (register or non-register) inputs are not processed in a distinguished manner but rather treated like outputs of regular multiplication gates. (We unify constant wires, input, and multiplication gates into a universal gate.) Formally, we use the following topology matrix equation:

$$\mathbf{M} \times (in_1, o_1, \dots, in_n, o_n)^T = (\ell_1, r_1, \dots, \ell_n, r_n)^T$$

(3)

Here, n reflects the size of a m-instruction as a circuit  $\mathcal{C}$  and we define  $n = n_{in} - m = n_{\times} + m + 2$  (see Section 3 especially remark 1). Looking ahead,  $\mathcal{P}$  will privately order committed  $\ell \odot \mathbf{r} = \mathbf{o}$ , starting from  $1 \cdot 1 = 1$  (to capture 1 in the extended witness), followed by m registers, then  $n_{\times}$  multiplication tuples in  $\mathcal{C}$ , and ending with  $1 \cdot 0 = 0$  (to capture the checking output).

Notice that in Equation (3),  $\mathcal{P}$ 's extended witness (or, rather, its topology meta information) is now *compositional* in the sense that if we were to simply concatenate (committed) vectors from two different instructions, we would obtain new vectors of the same form. As we will see next (Section 4.3), a similar form of composition applies to topology matrices (and hence topology vectors), and this enables us to hide from  $\mathcal{V}$  the boundaries between instructions.

#### 4.3 Reducing a Tight ZK CPU to a ZK UROM

This section overviews how a tight ZK CPU can be reduced to a so-called ZK UROM functionality. We consider a tight ZK CPU with B instructions  $C_1, \ldots, C_B$ , each of (potentially) different size, where  $\mathcal{P}$  wishes to execute  $C_1$  followed by  $C_2$  (i.e.,  $C_2 \circ C_1$ ), as an example.

#### 4.3.1 Special Case: No Registers

For simplicity, let us start by considering a special case where our CPU has no registers for passing data between instructions (i.e., m=0). Recall that, w.l.o.g, for each  $\mathcal{C}_{i\in[B]}$ , we assume  $n^{(i)}=n^{(i)}_{in}=n^{(i)}_{\times}+2$  where  $\mathcal{C}_i$  has  $n^{(i)}_{in}$  inputs,  $n^{(i)}_{\times}$  multiplications.

Suppose  $\mathcal{P}$  wishes to first execute  $\mathcal{C}_1$ , then execute  $\mathcal{C}_2$ .  $\mathcal{V}$  should only learn  $n = n^{(1)} + n^{(2)}$ , and  $\mathcal{V}$  learns neither how many instructions, nor which instructions are executed (unless such information is implied by n). Now, imagine a larger circuit  $\mathcal{C}$  that expresses the composition  $\mathcal{C}_2 \circ \mathcal{C}_1$ . In particular,  $\mathcal{C}$  can be described by simply concatenating the gate-by-gate description of  $\mathcal{C}_1$  and  $\mathcal{C}_2$  and appropriately shifting the names (indexes) of  $\mathcal{C}_2$ 's gates and wires by  $n^{(1)}$ . A key observation

is that the topology matrix for C can be constructed by combining the topology matrices for  $C_1$  and  $C_2$ :

$$\boldsymbol{M} = \begin{pmatrix} \boldsymbol{M}^{(1)} & \mathbf{0} \\ \mathbf{0} & \boldsymbol{M}^{(2)} \end{pmatrix} \in \mathbb{F}^{2n \times 2n}, n \triangleq n^{(1)} + n^{(2)}$$

(4)

where  $M^{(1)}$  (resp.  $M^{(2)}$ ) is the topology matrix induced by  $C_1$  (resp.  $C_2$ ). Our approach hides C (and M) from V, even though each  $M^{(i \in [B])}$  and n is public. For this simple case, our proof would proceed as follows:

- 1.  $\mathcal{P}$  commits to n inputs in and n MULT tuples  $\ell, r, o$  in the order described by Equation (3) (and proves  $\ell \odot r = o$ ).

- 2.  $\mathcal{P}$  proves that the first MULT output of both subcircuits is 1 and that both circuits check to 0:

$$o_1 = o_{n^{(1)}+1} = 1$$

and  $o_{n^{(1)}} = o_{n^{(2)}} = 0$

3.  $\mathcal{P}$  proves in ZK that the committed values and M satisfy Equation (3). To achieve this,  $\mathcal{V}$  issues a uniform challenge  $\chi$  and  $\mathcal{P}$  proves in ZK that:

topology vector

$$c$$

committed

$$(1, \chi, \dots, \chi^{2n-1}) \times M \times (in_1, o_1, \dots, in_n, o_n)^T$$

$$= \underbrace{(1, \chi, \dots, \chi^{2n-1})}_{\text{public}} \times \underbrace{(\ell_1, r_1, \dots, \ell_n, r_n)^T}_{\text{committed}}$$

To achieve the above steps while hiding C (and M), P commits to two additional vectors. The first is an appropriate boundary string (see Section 4.1) p:

$$p \triangleq \overbrace{0, \dots, 0}^{n^{(1)}-1}, 1, \overbrace{0, \dots, 0}^{n^{(2)}-1}, 1$$

The second vector id places the index of each branch at that branch's boundary, and elsewhere  $\mathcal{P}$  fills the vector with any values in [B]:

$$id \triangleq \underbrace{n^{(1)}-1}_{n^{(2)}-1}$$

any values in  $[B]$ , 1, any values in  $[B]$ , 2

Looking ahead, these branch IDs will be used as indices to load instruction hashes from a ZK ROM (entries not on boundaries are dummy indices). The definition of id implies that Filter(p, id) outputs a vector of branch IDs (see Section 4.1 for Filter's definition). Informally, p and id jointly form a commitment to a particular execution path.

At a high level, our protocol leverages p and id to cheaply express Steps 2 and 3 as ZK constraints. In detail:

- 1. Step 1 only depends on n and is *independent* of M.  $\mathcal{P}$  commits to her inputs and to well-formed MULT tuples.

- 2. Step 2 can be performed by checking the constraints:

- (a)  $\boldsymbol{p} \in \{0,1\}^{n-1} \| 1$ . I.e.,  $\boldsymbol{p}$  is a boundary string.

- (b) If  $p_{i \in [n]} = 1$ ,  $o_i$  must be 0.

- (c)  $o_1 = 1$ , and if  $p_{i \in [n-1]} = 1$ ,  $o_{i+1}$  must be 1.

The above constraints can be checked very efficiently.

3. To perform Step 3,  $\mathcal{V}$  cannot construct the topology vector  $\boldsymbol{c}$ , as  $\boldsymbol{M}$  is private. Instead, our protocol requires that  $\mathcal{P}$  commits to  $\boldsymbol{c}$ . Of course,  $\mathcal{P}$  might attempt to cheat, so we need extra checks that ensure  $\mathsf{com}(\boldsymbol{c})$  is properly constructed and is consistent with  $\boldsymbol{p}$  and  $\boldsymbol{id}$ . We will soon show how this can be achieved via a so-called ZK unbalanced ROM (Section 4.4). For now, simply assume that  $\mathcal{P}$  commits to the vector:

$$\boldsymbol{c} = (1, \chi, \dots, \chi^{2n-1}) \times \boldsymbol{M}$$

Crucially, private M has a special structure – it has square matrices on the diagonal and 0s elsewhere. In particular, these square matrices are determined and ordered by the private execution path. I.e., it (in order) includes  $M^{(j)}$  for each  $j \in \mathsf{Filter}(p, id)$  in order. Note that each  $M^{(i \in [B])}$  is public. Finally, once we have  $\mathsf{com}(c)$ , it suffices to show that:

$$\langle \boldsymbol{c}, (in_1, o_1, \dots, in_n, o_n) \rangle = \langle (1, \dots, \chi^{2n-1}), (\ell_1, r_1, \dots, \ell_n, r_n) \rangle$$

#### 4.3.2 Handling Constant 1

Recall that the first MULT gate in each instruction should output 1 defined as  $1 \cdot 1 = 1$ , enabling that instruction to manipulate the constant 1. As a remark, it is surprisingly difficult to incorporate constants in our approach, because our constraint systems are merely *linear* (and not affine) over  $\mathbb{F}$ . Sub-step 2c forces that the output of the first MULT gate is 1. Here, we show an optimized way to ensure that the output of this MULT is 1 for free by directly constraining its *inputs*. Our idea is to pass the constant 1 from one instruction to the next and, looking forward, this same handling will be used to enable the passing of m registers.

A naïve (failing) attempt to pass a 1 into an instruction would be to have a fixed wire of C carrying 1, to which each instruction can refer. However, we are working with a fixed instruction set (and we check hashes of executed instructions against the corresponding set of hashes). Informally, we *could* make an instruction reference a fixed wire in C, outside of itself. However, due to our use of topology matrices, under the hood (i.e., in the supporting matrix algebra) such an instruction will access this wire via an offset to its own position on the execution path, resulting in a *unique* instruction (topology matrix) hash. Such an instruction cannot be checked against the fixed instruction set (IS).

Thus, our instructions cannot refer to wires by their absolute position, but they can refer to wires via a fixed offset relative to their own position on the execution path. Indeed, our solution, at the high level, is for each instruction to "push forward" a 1 wire to the next instruction. This is possible because each instruction knows its own length, and can set up the corresponding constraint for the next instruction. Each instruction  $C_{i \in [B]}$  has a fixed offset to access (enforce) input constraints (via left/right wires of MULTs) of the next instruction. Thus,  $C_{i \in [B]}$ 's topology matrix (and hence hash) will be the same anywhere on the execution path. The very first instruction can pick up the 1 from a designated wire of C.

This cleanly translates into our matrix representation. Let us go through our concrete example of  $\mathcal{P}$  proving a circuit  $\mathcal{C}$  consisting of  $\mathcal{C}_1$  followed by  $\mathcal{C}_2$ . Formally, the entire proof will be based on a (slightly) updated equation:

$$egin{aligned} m{M} imes (1, in_1, o_1, \dots, in_n, o_n)^T \ &= (\ell_1, r_1, \dots, \ell_n, r_n, 1, 1)^T \end{aligned} egin{aligned} m{M} riangleq egin{pmatrix} 1 & m{0} & m{0} \ 1 & m{0} & m{0} \ 0 & m{M}_*^{(1)} & m{0} \ 0 & m{0} & m{M}_*^{(2)} \end{aligned} \end{aligned}$$

where each

$$\boldsymbol{M}_*^{(i \in [B])} = \begin{pmatrix} \boldsymbol{M}^{(i)}(3) \\ \cdots \\ \boldsymbol{M}^{(i)}(2n^{(i)}) \\ 0 \ 1 \ 0 \cdots \\ 0 \ 1 \ 0 \cdots \end{pmatrix}$$

is public. (Here  $\boldsymbol{M}_*^{(i \in [B])}$  omits the first two constraints of

$M^{(i \in [B])}$ , which define left/right wires of a MULT generating 1. As a complement, the last two rows of  $M_*^{(i \in [B])}$  constrain the next instruction's left/right wires of the MULT generating 1.<sup>2</sup>) The IS will consist of B instructions  $M_*^{(i \in [B])}$ .

Crucially, while M is private, the first two rows of M are fixed and public. We need to construct the vector commitment of  $(1, \chi, \dots, \chi^{2n+1}) \times M = (1+\chi) \| (\chi^2(1, \dots, \chi^{2n-1}) \times M_*)$ , where

$$M_* = \begin{pmatrix} M_*^{(1)} & \mathbf{0} \\ \mathbf{0} & M_*^{(2)} \end{pmatrix}$$

. Hence, it suffices to construct the commitments of  $(1, \dots, \chi^{2n-1}) \times M_*$ , the problem discussed in Step 3 of Section 4.3.1 and postponed to Section 4.3.4.

Similarly to our importing a 1 = 1.1 into an instruction, we will import registers via reg = 1.reg:

#### 4.3.3 Supporting Registers

Extending our idea of passing 1, we support register passing between two adjacently executed instructions. We view each register as a MULT, where the previous instruction defines MULT's left/right wires. The translation of this into the matrix representation is similar to our handling of  $1 \cdot 1 = 1$ . Consider the case with a single register as a simple example (the order of gates follows Section 4.3.1). We can (re)define the public matrix

$$\boldsymbol{M}^{(i)} \triangleq \begin{pmatrix} \operatorname{define} \ell_{3} \\ \operatorname{define} r_{3} \\ \cdots \\ \operatorname{define} \ell_{n_{\times}^{(i)}+2} \\ \operatorname{define} r_{n_{\times}^{(i)}+2} \\ 0 \ 1 \ 0 \cdots (\operatorname{define} 1) \\ \operatorname{define} \operatorname{checking} \operatorname{output} \\ 0 \ 1 \ 0 \cdots (\operatorname{define} 1) \\ 0 \ 1 \ 0 \cdots (\operatorname{define} 1) \\ 0 \ 1 \ 0 \cdots (\operatorname{define} 1) \\ \operatorname{define} \operatorname{first} \operatorname{register} \end{pmatrix} \in \mathbb{F}^{2n^{(i)} \times 2n^{(i)}}$$

(5)

<sup>&</sup>lt;sup>2</sup>The first MULT  $\ell_1 \cdot r_1 = o_1$  must be  $1 \cdot 1 = 1$  as  $\ell_1 = r_1 = \langle (1, in_1, \ldots), (1, 0, \ldots) \rangle = 1$ .

for each  $i \in [B]$ . Here, the last two rows of  $M^{(i)}$  set the first register (as inputs to a MULT of the next instruction). The prior two rows similarly set a 1 for the next instruction.

Now, suppose  $\mathcal{P}$  wants to prove the execution of  $\mathcal{C}_1$  followed by  $\mathcal{C}_2$ , where the register is initialized to x as  $\mathcal{C}$ 's input and stores y as  $\mathcal{C}$ 's output (x, y) are public.  $\mathcal{P}$  can commit  $n = n^{(1)} + n^{(2)}$  inputs and MULT tuples and show:

$$egin{aligned} m{M} imes (1,x,in_1,o_1,\ldots,in_n,o_n)^T \ &= (\ell_1,r_1,\ldots,\ell_n,r_n,1,1,1,y)^T \end{aligned} m{M} riangleq egin{pmatrix} 1 & 0 & \mathbf{0} & \mathbf{0} \ 1 & 0 & \mathbf{0} & \mathbf{0} \ 1 & 0 & \mathbf{0} & \mathbf{0} \ 0 & 1 & \mathbf{0} & \mathbf{0} \ 0 & 0 & m{M}^{(1)} & \mathbf{0} \ 0 & 0 & \mathbf{0} & m{M}^{(2)} \end{pmatrix}$$

$m{M}$  is private but  $\mathcal{P}$  and  $\mathcal{V}$  can obtain the commitment of  $(1,\chi,\chi^2,\ldots) \times m{M}$  by constructing the commitment of  $(1,\ldots,\chi^{2n-1}) \times m{M}^{(1)} \quad m{0} \\ m{0} \quad m{M}^{(2)} \end{pmatrix}$  (discussed next).

#### 4.3.4 Committing to the Topology Vector

We now show how  $\mathcal{P}$  and  $\mathcal{V}$  can construct  $\mathsf{com}(c)$ , a crucial task postponed from Section 4.3.1. The methodology applies to Sections 4.3.2 and 4.3.3. We explain it on the special case of two instructions  $\mathcal{C}_2 \circ \mathcal{C}_1$ ; our discussion applies generally. We exploit the following equality:

$$c = (1, \chi, \dots, \chi^{2n-1}) \times M$$

$$= (1, \dots, \chi^{2n^{(1)}-1}) \times M^{(1)} \| (\chi^{2n^{(1)}}, \dots, \chi^{2n^{(1)}+2n^{(2)}-1}) \times M^{(2)}$$

$$= (1, \dots, \chi^{2n^{(1)}-1}) \times M^{(1)} \| \chi^{2n^{(1)}} \cdot (1, \dots, \chi^{2n^{(2)}-1}) \times M^{(2)}$$

$$= \left( \mathbf{a} \triangleq (\underbrace{1, \dots, 1}_{2n^{(1)}}, \underbrace{\chi^{2n^{(1)}}, \dots, \chi^{2n^{(1)}}}_{2n^{(1)}}) \right) \odot$$

$$\left( \mathbf{b} \triangleq (\underbrace{1, \chi, \dots, \chi^{2n^{(1)}-1}}_{2n^{(1)}}) \times M^{(1)} \| (\underbrace{1, \chi, \dots, \chi^{2n^{(2)}-1}}_{2n^{(2)}}) \times M^{(2)} \right)$$

Hence, to construct com(c), it suffices to construct com(a) and com(b). Note, a is a structured vector based on  $\chi$  and p (see Section 4.1, Expand<sub>1</sub>). We only need to construct com(b), and the crucial observation is the following vectors are public:

$$\forall i \in [B], \boldsymbol{v}^{(i)} \triangleq (1, \chi, \dots, \chi^{2n^{(i)}-1}) \times \boldsymbol{M}^{(i)}$$

The functionality we need is to "load" from *unbalanced* ROM then "concatenate"  $v^{(1)}$  and  $v^{(2)}$ . This can be viewed as

1.  $\mathcal{P}$  and  $\mathcal{V}$  agree on an unbalanced read-only memory (ROM) storing (public) entries:

$$(1, \mathbf{v}^{(1)}), \dots, (B, \mathbf{v}^{(B)})$$

2.  $\mathcal{P}$  and  $\mathcal{V}$  load-concatenate  $\mathbf{v}^{(i \in [B])}$ s where the ordered indexes are decided by Filter $(\mathbf{p}, i\mathbf{d})$ .

Note that these vectors saved in ROM are randomized by  $\mathcal{V}$ 's uniform challenge sent after p and id have been committed. As are instructions, these vectors are of different lengths. We capture this as a (more generic and novel) hybrid functionality ZK Unbalanced ROM (ZK UROM) and include the overview in Section 4.4. Crucially, the access cost of our ZK UROM is proportional to the length of the data retrieved – this is needed to meet our tight efficiency budget.

#### 4.4 ZK Non-Zero-End Unbalanced ROM

This section overviews how to reduce a ZK UROM to a ZK ROM.

We observe that it suffices to design a ZK UROM supporting only non-zero-end vectors. This simplifies our task, enabling concise soundness checks based on Corollary 1, and can always be achieved, e.g., by padding. (We later show that padding is not needed for us.)

In ZK non-zero-end UROM,  $\mathcal{P}$  and  $\mathcal{V}$  agree on a set of key-value tuples  $(1, \boldsymbol{v}^{(1)}), \ldots, (B, \boldsymbol{v}^{(B)})$ , where  $\boldsymbol{v}^{(i \in [B])}$  are non-zero-end vectors in  $\mathbb{F}$  that can have different lengths. The objective is allowing  $\mathcal{P}$  to commit to a vector  $\boldsymbol{v}$ , a concatenation of several  $\boldsymbol{v}^{(i \in [B])}$ s, e.g.,  $\boldsymbol{v} \triangleq \boldsymbol{v}^{(1)} \| \boldsymbol{v}^{(2)} \| \boldsymbol{v}^{(1)}$ . Crucially,  $\mathcal{V}$  should only learn  $n \triangleq |\boldsymbol{v}|$  and be convinced that  $\boldsymbol{v}$  is a concatenation of vectors from UROM. Prior work (e.g., [YH24], on which we build) only considers ZK ROM over vectors of equal length (see Section 2.4).

Our ZK UROM protocol works in the commit-and-prove paradigm. I.e., we require  $\mathcal{P}$  to directly commit to  $\boldsymbol{v}$  and prove in ZK that  $\boldsymbol{v}$  is a valid concatenation. To support this proof,  $\mathcal{P}$  additionally commits how she wants to partition  $\boldsymbol{v}$ . That is,  $\mathcal{P}$  commits a length-n boundary string  $\boldsymbol{p}$  and a length-n vector  $i\boldsymbol{d} \in [B]^n$  such that for each  $x \in \mathsf{Filter}(\boldsymbol{p}, i\boldsymbol{d})$  and  $\boldsymbol{y} \in \mathsf{Partition}(\boldsymbol{p}, \boldsymbol{v})$  pair (total  $\mathsf{HW}(\boldsymbol{p})$  pairs, unknown to  $\mathcal{V}$ ) in sequence,  $\boldsymbol{y} = \boldsymbol{v}^{(x)}$ .

To begin with, consider a simplified single-read task:  $\mathcal{P}$  commits a vector  $\boldsymbol{w}$  and a single index t and wants to prove that  $\boldsymbol{w} = \boldsymbol{v}^{(t)}$ . This can be checked by  $\mathcal{V}$  issuing a uniform challenge  $\gamma \in \mathbb{F}$  where parties agree on another balanced ROM storing K-V tuples:  $(1, mac^{(1)}), \ldots, (B, mac^{(B)})$  where  $mac^{(i)} \triangleq (1, \gamma, \gamma^2, \ldots) \times \boldsymbol{v}^{(i)} \in \mathbb{F}$  for each  $i \in [B]$ . Now, by accessing the ZK ROM (see Section 2.4), parties convert com(t) into  $com(mac^{(t)})$ . Then, it suffices to show:

- 1.  $last(\boldsymbol{w}) \neq 0$ . This can be proved by requiring  $\mathcal{P}$  to commit a value *inv* and show that  $last(\boldsymbol{w}) \cdot inv = 1$ .

- 2.  $\langle (1, \gamma, \gamma^2, \ldots), \boldsymbol{w} \rangle = mac^{(t)}$ . This can be proved by opening  $\operatorname{\mathsf{com}}(\langle (1, \gamma, \gamma^2, \ldots), \boldsymbol{w} \rangle mac^{(t)})$  (which should be 0). Note that  $\gamma$  is public and parties hold  $\operatorname{\mathsf{com}}(\boldsymbol{w}), \operatorname{\mathsf{com}}(mac^{(t)})$ .

Soundness is reduced to Corollary 1 as  $\mathcal{P}$  is prevented by Step 1 from appending the returned vector with zeros.

Our ZK UROM protocol generalizes the above idea to v with the help of committed p and id. In particular, since p already marks where each subvector ends, and the corresponding committed id includes the index of each subvector, we can perform the above checks only at the position where  $p_i = 1$ . That is,  $\mathcal{P}$  and  $\mathcal{V}$  perform a check for each position, but checks in positions where  $p_i = 0$  are dummy. Formalizing the above, we outline our protocol:

- 1.  $\mathcal{V}$  issues a uniform challenge  $\gamma \in \mathbb{F}$  where  $\mathcal{P}$  and  $\mathcal{V}$  agree on another balanced ROM storing K-V tuples  $\{(i, mac^{(i)})\}_{i \in [B]}$  where (public)  $mac^{(i)} \triangleq (1, \gamma, \gamma^2, \ldots) \times \mathbf{v}^{(i)}$  for each  $i \in [B]$ .

- 2.  $\mathcal{P}$  and  $\mathcal{V}$  generate committed "selected macs"  $\mathsf{com}(smac)$  by "reading" single-element ZK ROM (see Section 2.4) initialized by  $mac^{(1)}, \ldots, mac^{(B)}$  at positions id, where each  $smac_{i \in [n]} = mac^{(id_i)}$ . We remark that id is fixed before  $\gamma$ .

3.  $\mathcal{P}$  and  $\mathcal{V}$  generate commitment of the structured vector  $\mathbf{s}$  based on  $\gamma$  and  $\mathbf{p}$  via  $\mathsf{Expand}_2$  (see Section 4.1):

$$\begin{aligned} & \boldsymbol{p} = (\overbrace{0, \dots, 0, 1}^{n_1}, \overbrace{0, \dots, 0, 1}^{n_2}, \overbrace{0, \dots, 0, 1}^{n_3}, \dots) \\ \Rightarrow & \boldsymbol{s} = (1, \gamma, \dots, \gamma^{n_1 - 1}, 1, \gamma, \dots, \gamma^{n_2 - 1}, 1, \gamma, \dots, \gamma^{n_3 - 1}, \dots) \end{aligned}$$

4.  $\mathcal{P}$  proves that for each  $p_{i \in [n]} = 1$ , it holds  $v_i \neq 0$ . (I.e., each segment ends non-zero.) This corresponds to the check in Step 1 of the single-read task. This can be performed by requiring  $\mathcal{P}$  to commit to another length-n vector inv where

$$inv_i = (v_i)^{-1}$$

if  $p_i = 1$ ;  $inv_i = 0$  otherwise

$\mathcal{P}$  then shows that  $inv \odot v - p = 0$ .

5.  $\mathcal{P}$  proves that for each  $a \in \mathsf{Partition}(p,s), b \in \mathsf{Partition}(p,v), c \in \mathsf{Partition}(p,smac)$  (in order, total  $\mathsf{HW}(p)$  tuples),  $\langle a,b \rangle = \mathsf{last}(c)$ . This corresponds to the check in Step 2 of the single-read task. This can be performed by proving:

$$\forall i \in [n], p_i \cdot (\langle \boldsymbol{s}[:i], \boldsymbol{v}[:i] \rangle - \langle \boldsymbol{p}[:i], \boldsymbol{smac}[:i] \rangle) = 0$$

Note, the above equality trivially holds for all  $p_i = 0$ . Moreover, when  $p_i$  is equal to 1, both  $\langle s[:i], v[:i] \rangle$  and  $\langle p[:i], smac[:i] \rangle$  are accumulating the sum of macs used so far. Importantly,  $\mathcal{P}$  and  $\mathcal{V}$  do not compute these sums for each position separately, which incurs quadratic overhead. Rather, they accumulate a running total, which is being checked at each step. Thus, the total complexity of this check is linear.

#### 4.4.1 Using ZK UROM with Topology Vectors

Recall, our protocol for ZK CPU is reduced to a ZK UROM, where the data are the instructions' topology vectors. In the course of this reduction,  $\mathcal{P}$  and  $\mathcal{V}$  generate commitments to  $\boldsymbol{p}$  and  $\boldsymbol{id}$  (see Section 4.3). We need these commitments for the operation of UROM as well. The low-level format of these vectors is different from what UROM needs: while the vectors, as described in Section 4.3 manage gates, UROM needs to account for two wires for each of these gates. This discrepancy is easily reconciled (by inserting 0 to  $\boldsymbol{p}$  and replicating  $\boldsymbol{id}$ ), and we can work with a single copy of  $\boldsymbol{p}$  and  $\boldsymbol{id}$ .

A more subtle issue is that each topology vector ends with 0. This is because the last column of a topology matrix denotes the contribution of the last output of the instruction to each wire. Note that the last output represents the checking output of the instruction, which is not an input of any wire, resulting in the all-0 last column of the topology matrix (ultimately producing the 0-end topology vector). This does *not* fit the *non-zero-end* requirement!

While this can be resolved by appending 1, we resolve it more efficiently as follows. Since the checking output in a valid instruction is 0, we simply add it into the instruction's first (left) wire. This does not change the function of the instruction, and guarantees that the last column now has a single leading 1. This modification will make each topology vector end with 1. Further, in our proof we need to invert the last position of each topology vector; having set it to 1 optimizes this task. Namely, the vector inv committed by  $\mathcal{P}$  in Step 4 is precisely the boundary string p.

#### 5 Formalization

This section formalizes our approach. See Section 4 for a detailed overview of our approach.

#### 5.1 Ideal ZK Non-Zero-End UROM: $\mathcal{F}_{CPZK-UROM}$

We define the ideal functionality for CPZK with a single read-only memory for unbalanced, non-zero-end vectors, denoted  $\mathcal{F}_{\mathsf{CPZK-UROM}}$  and presented in Figure 7.  $\mathcal{F}_{\mathsf{CPZK-UROM}}$  is defined similarly to  $\mathcal{F}_{\mathsf{CPZK-ROM}}$ . The main difference is that  $\mathcal{F}_{\mathsf{CPZK-UROM}}$  allows  $\mathcal{P}$  to initialize the UROM with different-length vectors (via InitUROM). Furthermore,  $\mathcal{F}_{\mathsf{CPZK-UROM}}$  allows  $\mathcal{P}$  to read a length-n vector  $\mathbf{d}$  from the UROM (via ReadUROM). Vector  $\mathbf{d}$  must partition into subvectors where each subvector is a UROM entry. Before calling ReadUROM,  $\mathcal{P}$  can choose the content it wishes to read via SetProg. This choice is encoded by length-n vectors  $\mathbf{p}$  and  $\mathbf{id}$ , where  $\mathbf{p}$  is the boundary string encoding how  $\mathcal{P}$  wishes to partition  $\mathbf{d}$  and Filter( $\mathbf{p}, \mathbf{id}$ ) is the (ordered) set of indices  $\mathcal{P}$  wishes to read.

#### 5.2 Our Protocols: $\Pi_{CPZK-UROM}$ and $\Pi_{ZKCPU}$

Recall that our tight ZK CPU protocol is designed in the  $\mathcal{F}_{\text{CPZK-UROM}}$ -hybrid model, and our ZK UROM protocol is designed in the  $\mathcal{F}_{\text{CPZK-ROM}}$ -hybrid mode; see Section 4. We formalize our protocols as  $\Pi_{\text{CPZK-UROM}}$  (Figures 8 and 9) and  $\Pi_{\text{ZKCPU}}$  (Figures 10 and 11).

We state the security theorems regarding these two protocols. In this section, we provide only a proof sketch for each theorem for readability. The complete proofs are deferred to Appendix A.

**Theorem 1.** Let the UROM be initialized with B non-zero-end vectors where each i-th vector is of length- $n^{(i)}$ . Let the read-out vector be of length-n. Then, protocol  $\Pi_{\mathsf{CPZK-UROM}}$  (Figure 8 and 9) UC-realizes  $\mathcal{F}_{\mathsf{CPZK-UROM}}$  (Figure 7) in the  $\mathcal{F}_{\mathsf{CPZK-ROM}}$ -hybrid model (Figure 4) with soundness error  $\frac{\max\{n,n^{(1)},...,n^{(B)}\}-1}{|\mathbb{F}|}$  and perfect zero-knowledge, in the presence of a static unbounded adversary.

Proof Sketch. The proof is performed by constructing the simulator  $\mathcal{S}$ . Note that the instructions related to the CPZK part in  $\mathcal{F}_{\text{CPZK-UROM}}$  are the same as  $\mathcal{F}_{\text{CPZK-ROM}}$  (see the "CPZK" box in  $\mathcal{F}_{\text{CPZK-UROM}}$  and  $\mathcal{F}_{\text{CPZK-ROM}}$ ; note this is not the ZK property). Thus, the simulation for these instructions is straightforward. Here, we only focus on constructing the simulator for the instructions in the unbalanced non-zero-end read-only memory part.

For these instructions, we need to show completeness (trivial, omitted); soundness (constructing S for  $\mathcal{P}^*$ ); and Zero-Knowledge (constructing S for  $\mathcal{V}^*$ ).

**Zero-Knowledge,** S for  $V^*$ : Note that the simulator for a malicious  $V^*$  is trivial. This is because (1) P has no output, and (2)  $V^*$  in the real-world execution only receives some commitment IDs (i.e., cids). In particular, these cids are revealed by the  $\mathcal{F}_{\mathsf{CPZK-UROM}}$  to S. (Indeed,  $V^*$  also receives some output from the Check call, but the result is always true.) I.e., the simulation is perfect.