# NON-STATIONARY TRANSPORT EFFECTS IN DEEP SUB-MICRON CHANNEL Si MOSFET'S

by

#### Ghavam Ghavami Shahidi

B.S. Massachusetts Institute of Technology (1981)

M.S. California Institute of Technology (1982)

M.S. Massachusetts Institute of Technology (1984)

E.E. Massachusetts Institute of Technology (1984)

Submitted in Partial Fulfillment of

of the Requirements for the Degree of

Doctor of Philosophy

in Electrical Engineering and Computer Science

at the

Massachusetts Institute of Technology

January 1989

©Massachusetts Institute of Technology, 1989

| Signature of Author |                                                                                                                       |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|

|                     | Department of Electrical Engineering and Computer Science<br>January 1989                                             |

| Certified by _      | Professor Dimitri A. Antoniadis Thesis Supervisor                                                                     |

| Certified by        | Professor Henry I. Smith                                                                                              |

| Accepted by         | Professor Arthur C. Smith Chairman, Departmental Committee on Graduate Students MASSACHUSETTS INSTITUTE OF TECHNOLOGY |

AUG 07 1991

LIBRARIES

# NON-STATIONARY TRANSPORT EFFECTS IN DEEP SUB-MICRON CHANNEL Si MOSFET'S

by

#### Ghavam Ghavami Shahidi

Submitted in Partial Fulfillment

of the Requirements for the Degree of

Doctor of Philosophy

in Electrical Engineering and Computer Science

#### Abstract

This thesis is concerned with conduction in high electric field and high field gradient regions; i.e. modifications in transport due to presence of sharp changes in drift field. As device dimensions are reduced into the submicron range, such devices operate under high electric field and field gradient. Questions about the validity of basic drift-diffusion equation have been raised. The most fundamental issue has been the functional dependence of transport coefficients; i.e. if the transport coefficients (mobility, diffusitivity) are local function of electric field (as is usually incorporated into drift-diffusion) or they are functions of some other variable, which in turn was modified by the field (i.e. energy or temperature). The origin of these issues has been the theoretical prediction of velocity overshoot (by means of Monte Carlo simulation). These effects are caused by the lack of steady state equilibrium between the carrier temperature and the local field when the field gradient is sufficiently large, i.e. the carriers are in a "non-stationary" equilibrium with the applied field. This thesis is concerned with such effects, and their importance.

The ideal device to study such effects is the deep-submicron channel MOSFET: It has a high field region in the channel and a source of cold carriers in the source. Carrier are injected from the source into the high field channel. If the device is sufficiently short, the electric fields in the channel are sufficiently high to observe some of these non-stationary effects. In order to observe these effects at higher temperatures, carrier scattering in the channel must be reduced; i.e. the channel mobility must be high. The first part of this thesis deals with the fabrication of high mobility deep-submicron channel MOSFETs. The basic process already existed, and some slight modifications were used to obtain devices with higher mobility and smaller parasitic resistances.

Once the high mobility MOSFETs were fabricated, velocity overshoot were readily observed at room temperature and 77 K for the first time. This observation proves the existence of non-stationary transport. The magnitude of such an effect is small at room temperature (20% over the bulk value) and high at 77 K (80% over the bulk value). It is not clear if a complicated alteration of simple drift-diffusion is necessary for reliable device modeling. Velocity overshoot is caused by the reduced carrier temperature in the channel

(relative to the one corresponding to local field). Therefore, this prompted investigation of hot electron effects in deep submicron range. Specifically, hot-electron generated substrate current was measured, and a reduction in the substrate current was observed for devices with channel length L< 0.15  $\mu m$ . An increased amount of substrate current reduction was observed at 77 K in short channel devices. It is proposed that a reduction of carrier temperature due to rapid variation in the lateral electric field and a reduction in the carrier density in the high field region because of velocity overshoot, is responsible for the reduction in the substrate current generation in the deep submicron channel length range.

To reduce short channel effects in deep submicron channel devices, indium was used as channel implant for the first time. It is possible to keep the surface doping low and bring the heavy  $p^+$  doping very close to the surface, thus reducing the short channel effects. At the same time, in these devices, both the velocity overshoot and the reduction in substrate current was observed.

These observations, prove the exictance of the so called non-stationary effects, and highlight the need for their inclusion (through higher moments of Boltzmann Equation or use of Monte Carlo method) in modeling of short channel devices.

Thesis Supervisor: Dr. Dimitri A. Antoniadis

Title: Professor of Electrical Engineering

Thesis Supervisor: Dr. Henry I. Smith

Title: Professor of Electrical Engineering

### Acknowledgment

First I would like to thank my thesis supervisors, Professors Dimitri A. Antoniadis and Henry I. Smith for their invaluable guidance, support, and patiance throught this work. Professor Antoniadis had great insight, and always directed me toward the right direction. Professor Smith's guidance in fabrication and excitment about the work were indispensible. I am indebted to them for ever.

I would like to thank the readers, Professors Marc A. Kastner and Terry P. Orlando for their suggestions. This work could not have been done without the smooth operations of Submicron Strautures Lab and Microsystems Lab. I am grateful to Jimmy Carter for his valuable help over many years of both this work and M.S. work. Joe Walsh, Mike Schroth, Paul Maciel, and Bayla Fine always were more than willing (and able) to help. I thank Tim McClure, Robert Cuikay and Velma McClure for their expert assistance throught different stages of fabrication. Phyllis deFano and Cristina Gordy were always more than helpful with the bureaucratic matters.

I am grateful to Jacob Jarvis for setting up MINIMOS and always going out of his way to help, Merit Huang for his excellent plotting routine, and Steve Chou with for his initial help with the masks.

I thank my friends and fellow graduate students: Mehran Mehregany, Anthony Yen, Philip Bagwell, Khalid Ismail, Duane Boning, Alberto Moel, Yau-Chin Que, William Chu, and Chun The, for making our groups such a pleaseant place to work.

This work was supported by the Joint Services Electronics Program, and Air Force Office of Sponsered Research, contract AFOSR-85-0376.

To:

Dr. Amir M. Farhadi

Dr. Mary Farhadi

### Contents

| Abstract                              | 2    |

|---------------------------------------|------|

| Acknowledgement                       | 4    |

| List of Figures                       | 7    |

| List of Tables                        | . 11 |

| 1. Introduction                       | . 12 |

| 2. MOSFET Device Physics              | . 16 |

| 2.1.1 MOSFET Structure                | . 16 |

| 2.1.2 MOS Capacitor Structure         | . 18 |

| 2.1.3 MOSFET Operation                | . 23 |

| 2.2 Mobility in Inversion Layers      | . 25 |

| 2.3 Scaling                           | . 28 |

| 2.4.1 Short Channel Effects           | . 31 |

| 2.4.2 Charge Sharing Model            |      |

| 2.5.1 Velocity Saturation             |      |

| 2.5.2 MOSFET with velocity Saturation | . 36 |

| 3. Fabrication                        | . 38 |

| 3.1 Introduction                      | . 38 |

| 3.2.1 Fabrication of X-ray Mask       | . 39 |

| 3.2.2 X-ray Exposure                  | . 43 |

| 3.3 Device Fabrication                | . 45 |

| 3.4 Results                           | . 48 |

| 3.4.1 Contact and Sheet Resistivities | . 49 |

| 3.4.2 Gate Oxide                      | . 49 |

| 3.4.3 Process Result Summary          | . 49 |

| 4. Non-Stationary Transport           | . 52 |

| 4.1 Non-Stationary Transport           | 53  |

|----------------------------------------|-----|

| 4.2 The Boltzmann Equation             | 54  |

| 4.3 The Hydridynamic Equations         | 56  |

| 4.3.1 Complete Hydrodynamic Equations  | 57  |

| 4.3.2 Solution of Coupled Equations    | 61  |

| 5. Velocity Overshoot                  | 70  |

| 5.1 Velocity Overshoot                 | 71  |

| 5.2.1 Experimental Results             | 73  |

| 5.2.2 Observation of Overshoot         | 77  |

| 6. Hot Electron Effects                | 82  |

| 6.1 Introduction                       | 82  |

| 6.2 Avalanch Multipication             | 83  |

| 6.3.1 Lateral Electric Field           | 84  |

| 6.3.3 Derivation of Lateral Field      | 85  |

| 6.4 Substrate Current                  | 89  |

| 6.5 Experimental Results at 300 K      | 91  |

| 6.6 Experimental Results at 77 K       | 98  |

| 7. Indium Implanted MOSFET Channel     | 102 |

| 7.1 Introduction                       | 102 |

| 7.2.1 Experimental Results             | 105 |

| 7.2.2 Necessity of Deep Implant        | 105 |

| 7.2.3 Mobility                         | 105 |

| 7.2.4 Device Characteristics           | 108 |

| 7.2.5 Hot Electron Behavior            |     |

| 8. Conclusion                          | 116 |

| Appendix A: Laterl Field in MOSFETs    | 119 |

| Appendix B: Detailed Fabrication Steps | 125 |

| Bibligraphy                            | 132 |

# List of Figures

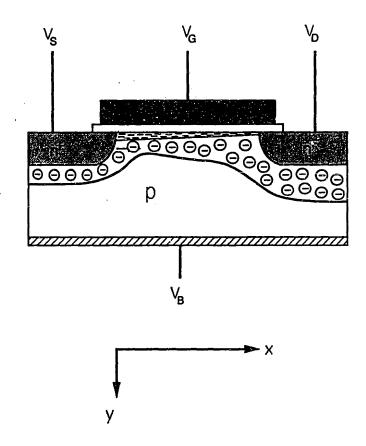

| 2.1 MOSFET cross section                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------|

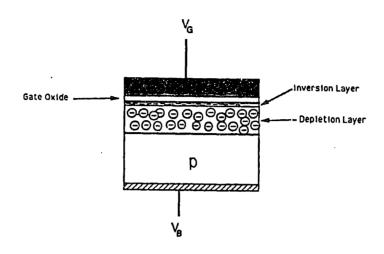

| 2.2 (a) MOS capacitor cross section. (b) MOS capacitor band diagram                                                                         |

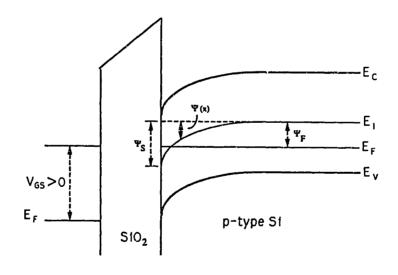

| 2.3 Total charge induced as a function of $\psi_S$                                                                                          |

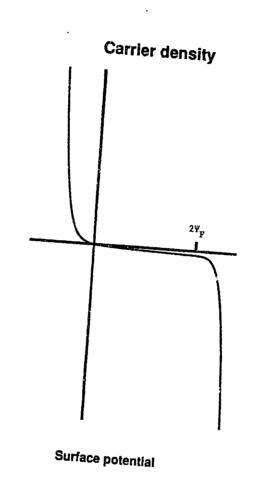

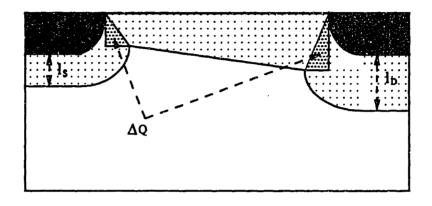

| 2.4 Cross section of a short channel MOSFET, showing the the charge shared, $\Delta Q_B$ 33                                                 |

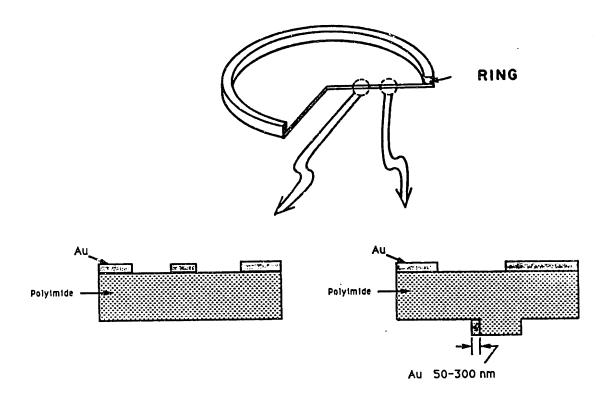

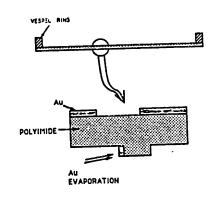

| 3.1 An x-ray mask: A thin polyimide memberane stretched on a vesple ring 41                                                                 |

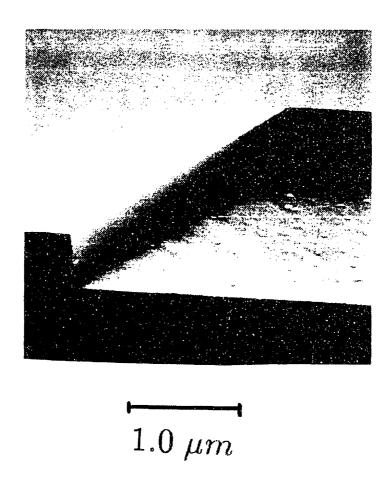

| 3.2 SEM micrograph of a (110) Si wafer in which wells were etched                                                                           |

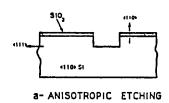

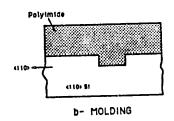

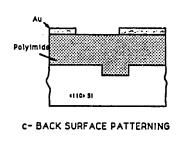

| 3.3 Steps involved in fabrication of x-ray mask                                                                                             |

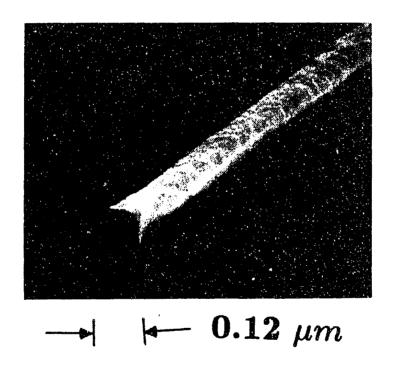

| 3.4 A 0.12 $\mu m$ wide line obtained by x-ray exposure                                                                                     |

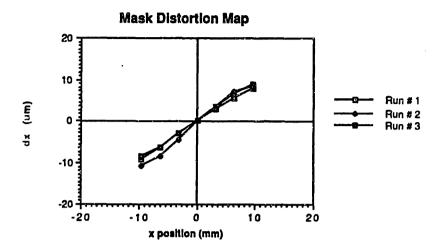

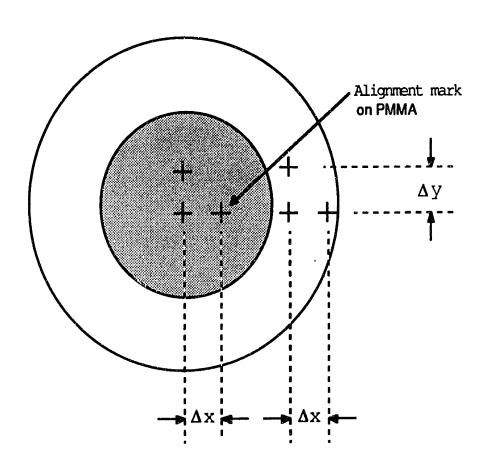

| 3.5 Movement of dies (relative to the center of x-ray mask), as measured by the stepper.                                                    |

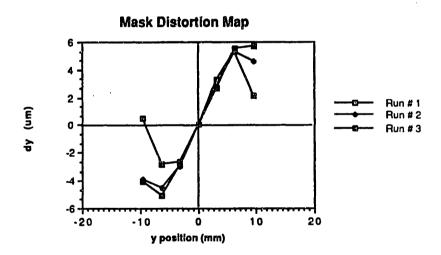

| 3.6 A 0.15 $\mu m$ device produced by our process. This device has the highest $g_m$ reported to date, despite its relatively high $R_{SD}$ |

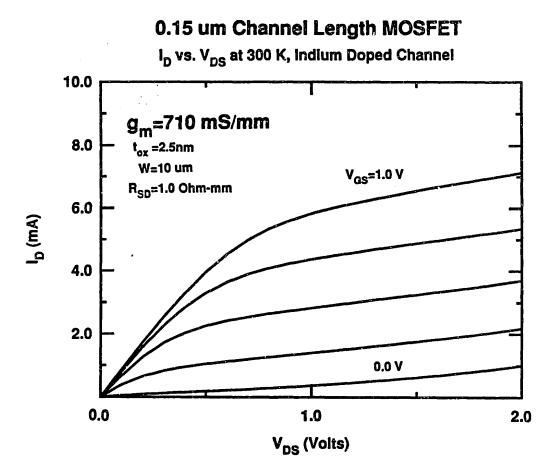

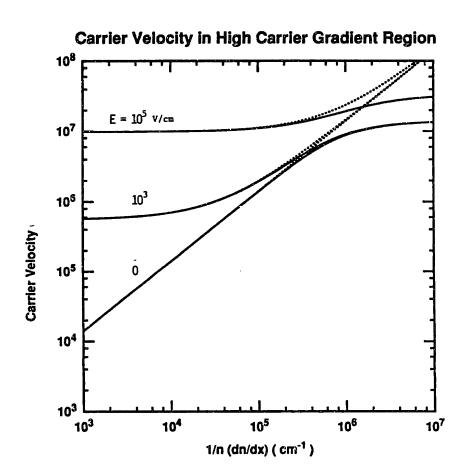

| 4.1 Carrier velocity in region of high carrier gradient as calculated by drift-diffusion and Hyrodynamic equations [Baccarani and Wordeman] |

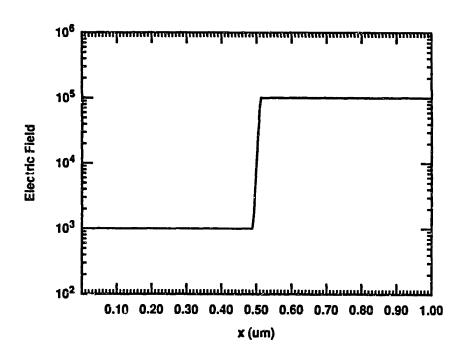

| 4.2Elecctric field profile used to study non-stationary effect caused by rapid variations in electric field                                 |

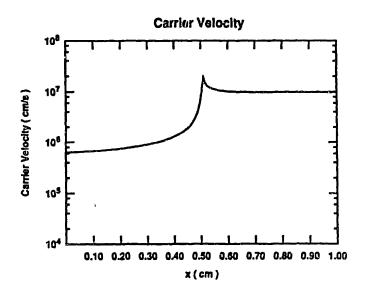

| 4.3 (a) Carrier velocity in a region of sharp electric field discontinuity (Solid line is exact                                             |

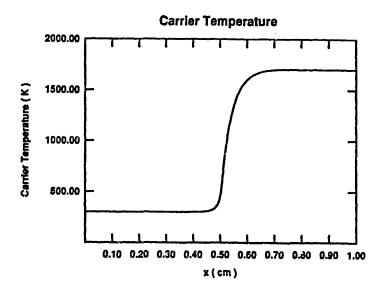

| and dashed line is using effective $D$ ) (b) Carrier temperature in a region of sharp electric field discontinuity                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

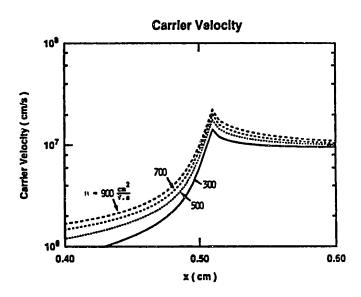

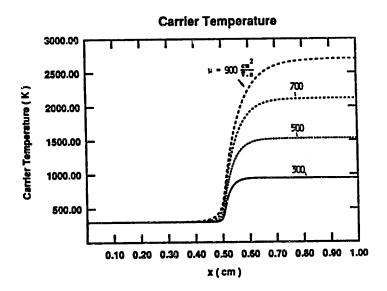

| 4.4 (a) Carrier velocity in a region of sharp electric field discontinuity for different mobilities. (b) Carrier temperature in a region of sharp electric field discontinuity field discontinuity for different mobilities                                                                                                                                        |

| 5.1 (a) Lateral field for a 0.5 $\mu m$ device for $V_{DS}=2.0$ V. (b) Carrier velocity for a 0.5 $\mu m$ device for $V_{DS}=2.0$ V                                                                                                                                                                                                                                |

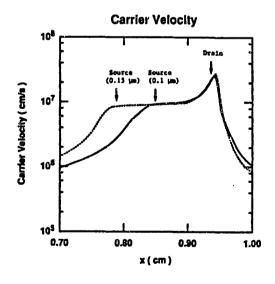

| 5.2 (a) Lateral fields for a 0.1 $\mu m$ and 0.15 $\mu m$ device for $V_{DS}=2.0$ V. (b) Carrier velocities for a 0.1 $\mu m$ and 0.15 $\mu m$ device for $V_{DS}=2.0$ V                                                                                                                                                                                           |

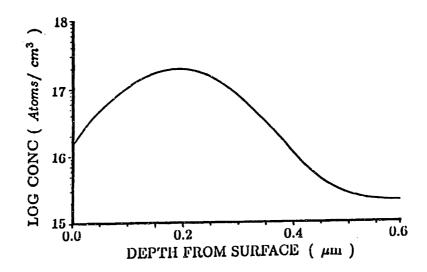

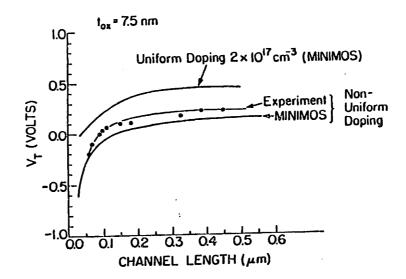

| 5.3 (a) Channel doping used in observation of velocity overshoot. (b) Threshold voltage vs. channel length for uniform and nonuniform substrate doping, as simulated by a two dimensional device simulator. The surface doping for the nonuniform case is $2 \times 10^{16}$ cm <sup>-3</sup> . Experimental results for the nonuniform doping case are also shown |

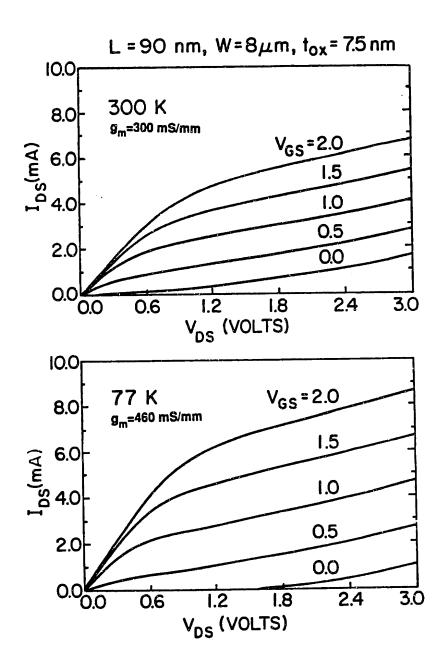

| 5.5 Charactristics of a 90-nm-channel length device at (a)300 K and (b) 77 K 79                                                                                                                                                                                                                                                                                    |

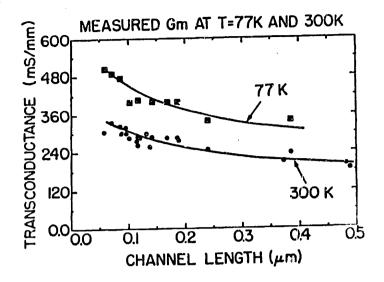

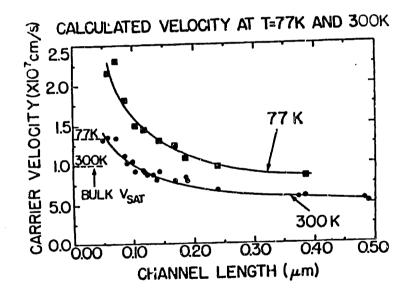

| 5.6 (a) Measured transconductances of devices vs channel lengths at 300 K and 77 K. (b) Calculated average velocities at 300 K and 77 K                                                                                                                                                                                                                            |

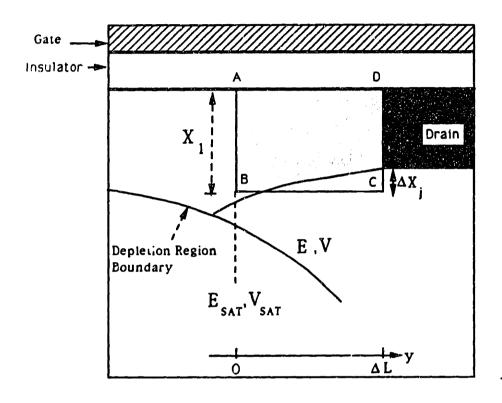

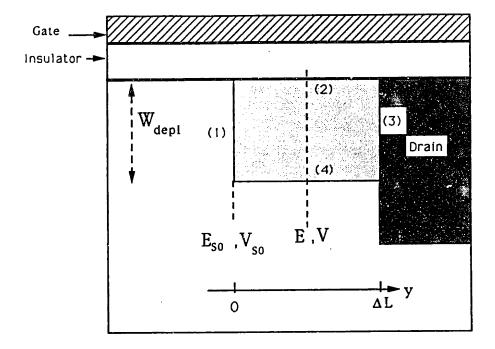

| 6.1 Drain region of a MOSFET as modeled by Ko, showing effect of $x_j$ 88                                                                                                                                                                                                                                                                                          |

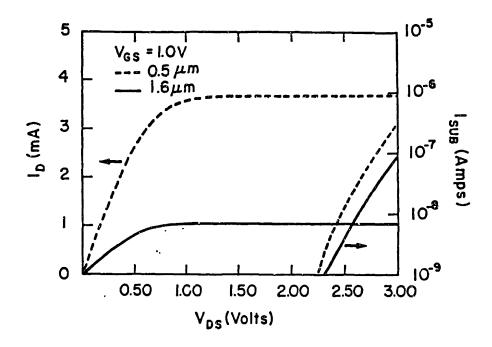

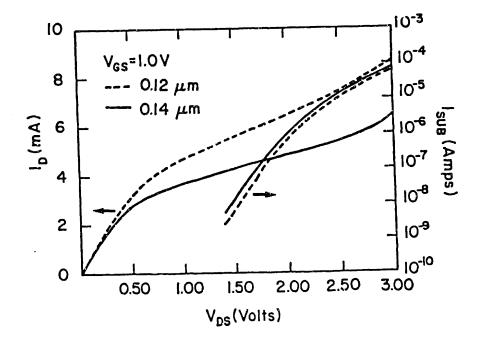

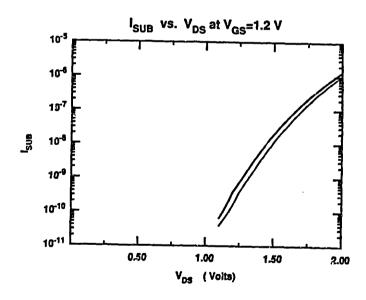

| 6.2 (a) Drain and substrate current at room temperature for two long channel MOSFETs.  (b) Drain and substrate current at room temperature for two two short channel MOSFETs under identical bias as in (a)                                                                                                                                                        |

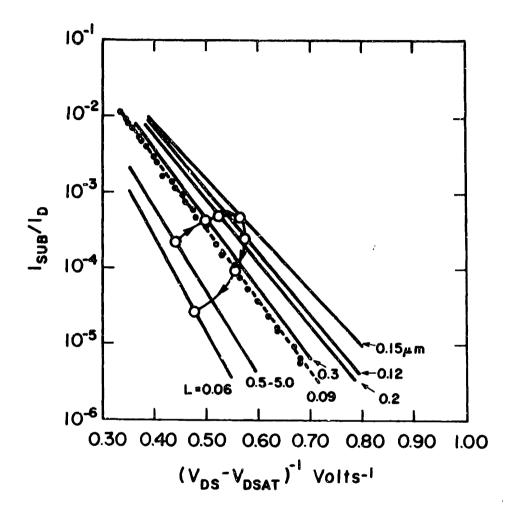

| 6.3 Plots of $log(I_{SUB}/I_D)$ vs. $(V_{DS}-V_{DSAT})^{-1}$ at room temperature for devices with channel lengths from 0.06 $\mu m$ to 5 $\mu m$ . The arrows trace the "evolution" of the plots as channel length is decreased                                                                                                                                    |

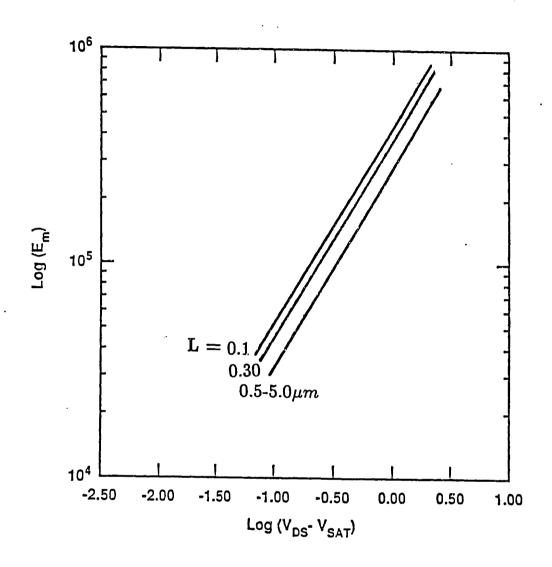

| 6.4 Plots of $E_m$ , the maximum field in the cahannel vs. $(V_{DS} - V_{DSAT})^{-1}$ at room temperature for devices with channel lengths from 0.1 $\mu m$ to 5 $\mu m$ (As calculated by MINIMOS)                                                                                                                                                                |

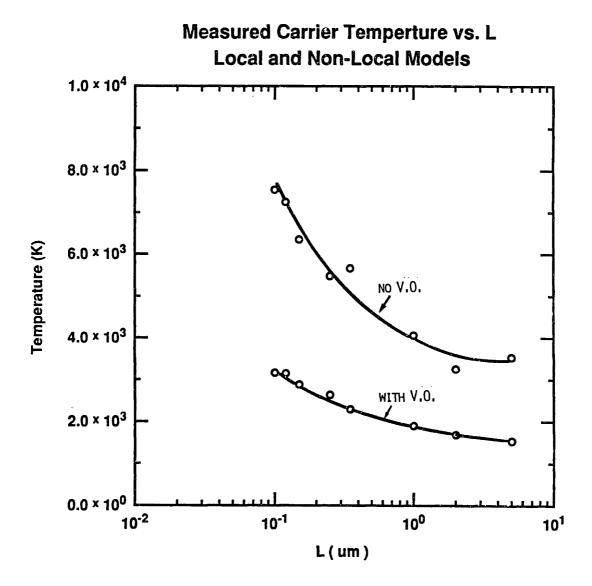

| 6.5 The maximum carrier temperature in the channel at $V_{DS} = 2.0 \text{ V}$ and $V_{GS} = 1.5 \text{ V}$ , at room temperature for devices with channel lengths from 0.08 $\mu m$ to 5 $\mu m$ with and without velocity overshoot                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

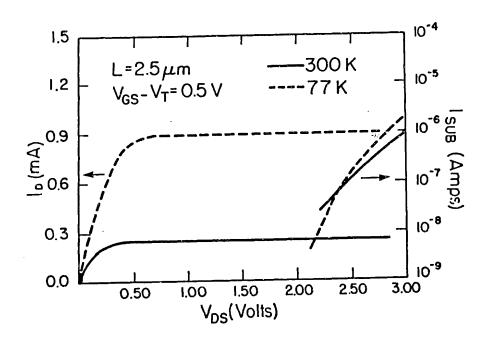

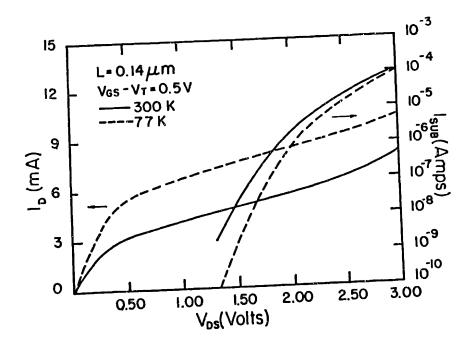

| 6.6 (a) $I_D$ and $I_{SUB}$ vs. $V_{DS}$ at $(V_{GS}-V_T)=0.5V$ for a long-channel device, L= $2.5\mu m$ ( $V_T=0.19~V$ , at 300 K and $V_T=0.46~V$ , at 77 K), at room temperature (solid line) and at 77 K (dashed line). (b) $I_D$ and $I_{SUB}$ vs. $V_{DS}$ at $(V_{GS}-V_T)=0.5V$ for a short-channel device, L= $0.14\mu m$ ( $V_T=0.07~V$ , at 300 K and $V_T=0.33~V$ , at 77 K) |

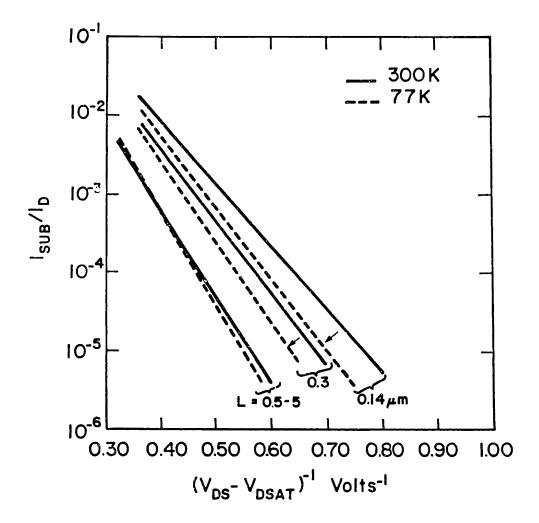

| 6.7 Plots of $log(I_{SUB}/I_D)$ vs. $(V_{DS}-V_{DSAT})^{-1}$ for $0.14\mu m < L < 5\mu m$ , at room temperature and 77 K. Note the enhanced reduction of the substrate current generation at low temperature for short-channel devices                                                                                                                                                   |

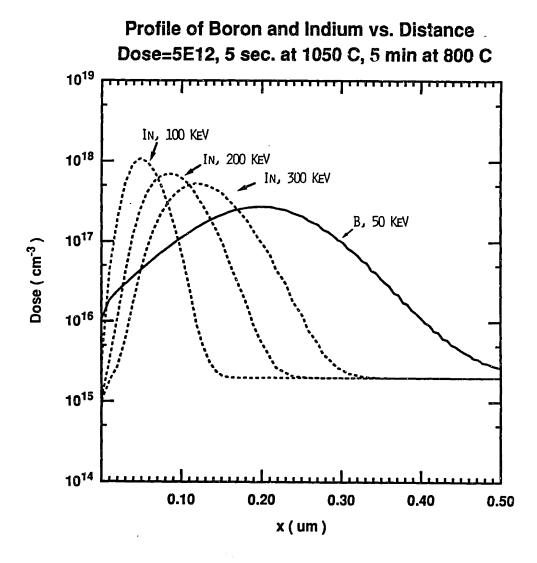

| 7.1 Concentration of Indium implanted at three different energies and boron at 50 KeV, as simulated by SUPREM                                                                                                                                                                                                                                                                            |

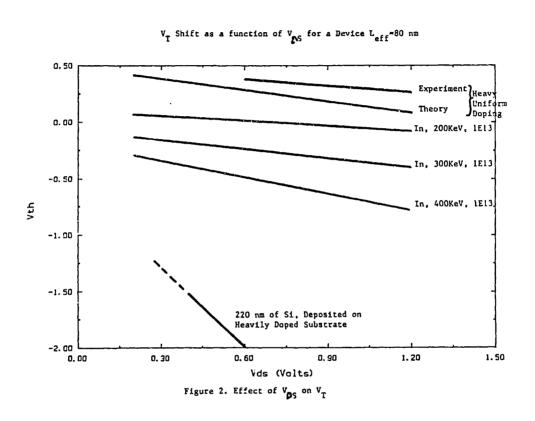

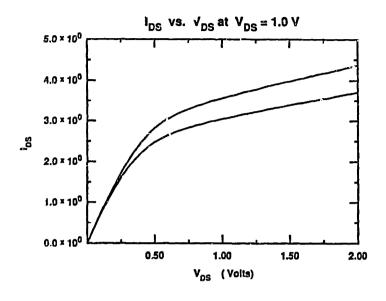

| 7.2 Reduction in $V_T$ as function of $V_{DS}$ for different values of implant energy 106                                                                                                                                                                                                                                                                                                |

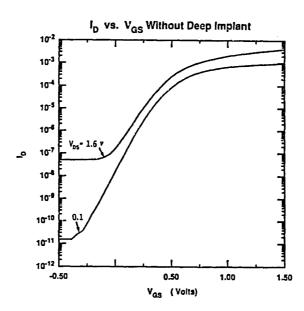

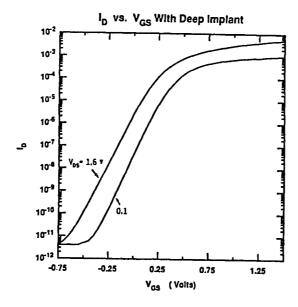

| 7.3 (a): Subthreshold conduction for a submicron MOSFET without the deep implant. (b): Subthreshold conduction for a submicron MOSFET with the deep implant 107                                                                                                                                                                                                                          |

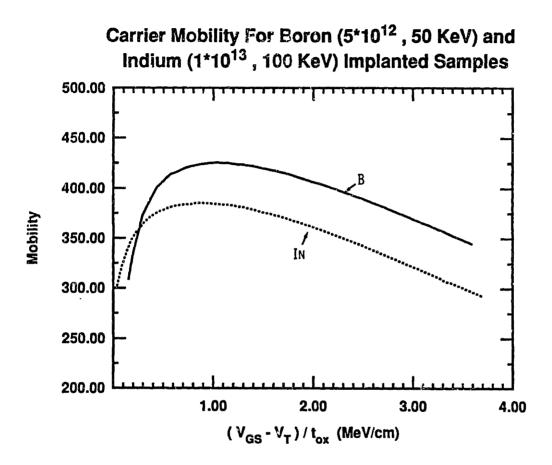

| 7.4 Mobility in a boron doped channel and an Indium doped channel ( with twice the dose and much shallower)                                                                                                                                                                                                                                                                              |

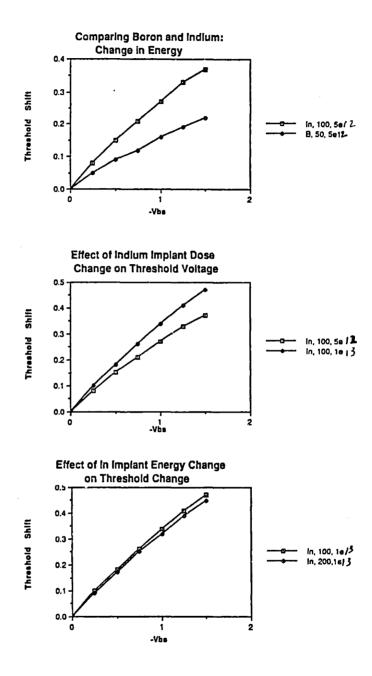

| 7.5 (a) Comparision of Inium and boron doped samples (Table 7.1) in terms of body effect, (b) Effect of dose on body effect, and (c) Effect of implant energy on body effect ( $t_{ox} = 5.3nm$ )                                                                                                                                                                                        |

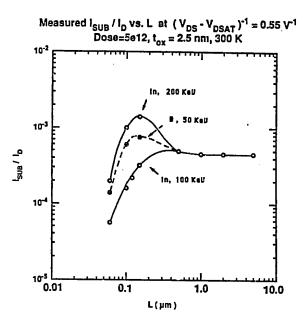

| 7.6 Plots of $log(I_{SUB}/I_D)$ vs. channel length at $(V_{DS}-V_{DSAT})^{-1}=0.55\ V^{-1}$ for different values of implant energies. Note the strong dependence of substrate current generation on implant energy for submicron devices. (a) is without the deep boron implant, and (b) is with the deep implant                                                                        |

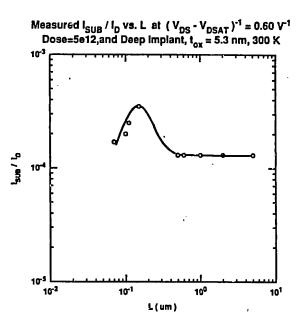

| 7.7 The drain and the corresponding substrate current for two short channel devices (L=0.1 and 0.15 $\mu m$ ), at $V_{GS}=1.2$ V. Note the reduction in the substrate current, despite the increase in $I_D$                                                                                                                                                                             |

## List of Tables

| 2.1 General Scaling Laws                  | • | : 29 |

|-------------------------------------------|---|------|

| 3.1 Improvements Obtained in Process      | • | . 48 |

| 7.1 Comparision of In and B doped Devices |   | 110  |

# List of Figures

| 2.1 MOSFET cross section                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2 (a) MOS capacitor cross section. (b) MOS capacitor band diagram 19                                                                                                                                             |

| 2.3 Total charge induced as a function of $\psi_S$                                                                                                                                                                 |

| 2.4 Cross section of a short channel MOSFET, showing the the charge shared, $\Delta Q_B$ 33                                                                                                                        |

| 3.1 An x-ray mask: A thin polyimide memberane stretched on a vesple ring 41                                                                                                                                        |

| 3.2 SEM micrograph of a (110) Si wafer in which wells were etched                                                                                                                                                  |

| 3.3 Steps involved in fabrication of x-ray mask                                                                                                                                                                    |

| 3.4 A 0.12 $\mu m$ wide line obtained by x-ray exposure                                                                                                                                                            |

| 3.5 Movement of dies (relative to the center of x-ray mask), as measured by the stepper.                                                                                                                           |

| 3.6 A 0.15 $\mu m$ device produced by our process. This device has the highest $g_m$ reported to date, despite its relatively high $R_{SD}$                                                                        |

| 4.1 Carrier velocity in region of high carrier gradient as calculated by drift-diffusion and Hyrodynamic equations [Baccarani and Wordeman]                                                                        |

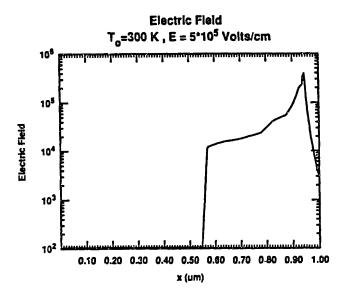

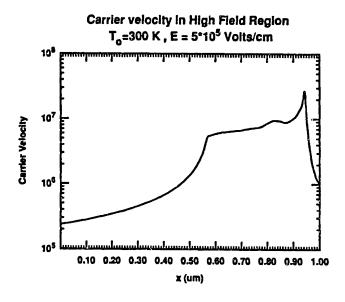

| 4.2 Electric field profile used to study non-stationary effect caused by rapid variations in electric field                                                                                                        |

| 4.3 (a) Carrier velocity in a region of sharp electric field discontinuity (Solid line is exact and dashed line is using effective $D$ ) (b) Carrier temperature in a region of sharp electric field discontinuity |

| 4.4 (a) Carrier velocity in a region of sharp electric field discontinuity for different mobil-                                                                                                                    |

| tinuity for different mobilities                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

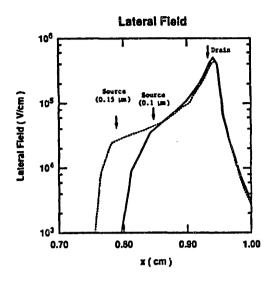

| 5.1 (a) Lateral field for a 0.5 $\mu m$ device for $V_{DS}=2.0$ V. (b) Carrier velocity for a 0.5 $\mu m$ device for $V_{DS}=2.0$ V                                                                                                                                                                                                                                |

| 5.2 (a) Lateral fields for a 0.1 $\mu m$ and 0.15 $\mu m$ device for $V_{DS}=2.0$ V. (b) Carrier velocities for a 0.1 $\mu m$ and 0.15 $\mu m$ device for $V_{DS}=2.0$ V                                                                                                                                                                                           |

| 5.3 (a) Channel doping used in observation of velocity overshoot. (b) Threshold voltage vs. channel length for uniform and nonuniform substrate doping, as simulated by a two dimensional device simulator. The surface doping for the nonuniform case is $2 \times 10^{16}$ cm <sup>-3</sup> . Experimental results for the nonuniform doping case are also shown |

| 5.5 Charactristics of a 90-nm-channel length device at (a)300 K and (b) 77 K 79                                                                                                                                                                                                                                                                                    |

| 5.6 (a) Measured transconductances of devices vs channel lengths at 300 K and 77 K. (b) Calculated average velocities at 300 K and 77 K                                                                                                                                                                                                                            |

| 6.1 Drain region of a MOSFET as modeled by Ko, showing effect of $x_j$                                                                                                                                                                                                                                                                                             |

| 6.2 (a) Drain and substrate current at room temperature for two long channel MOSFETs. (b) Drain and substrate current at room temperature for two two short channel MOSFETs under identical bias as in (a)                                                                                                                                                         |

| 6.3 Plots of $log(I_{SUB}/I_D)$ vs. $(V_{DS}-V_{DSAT})^{-1}$ at room temperature for devices with channel lengths from 0.06 $\mu m$ to 5 $\mu m$ . The arrows trace the "evolution" of the plots as channel length is decreased                                                                                                                                    |

| 6.4 Plots of $E_m$ , the maximum field in the cahannel vs. $(V_{DS} - V_{DSAT})^{-1}$ at room temperature for devices with channel lengths from 0.1 $\mu m$ to 5 $\mu m$ (As calculated by MINIMOS)                                                                                                                                                                |

| 6.5 The maximum carrier temperature in the channel at $V_{DS} = 2.0 \text{ V}$ and $V_{GS} = 1.5 \text{ V}$ , at room temperature for devices with channel lengths from 0.08 $\mu m$ to 5 $\mu m$ with and without velocity overshoot                                                                                                                              |

| 6.6 (a) $I_D$ and $I_{SUB}$ vs. $V_{DS}$ at $(V_{GS}-V_T)=0.5V$ for a long channel device, L= $2.5\mu m$ ( $V_T=0.19~V$ , at 300 K and $V_T=0.46~V$ , at 77 K), at room temperature (solid line) and                                                                                                                                                               |

| at 77 K (dashed line). (b) $I_D$ and $I_{SUB}$ vs. $V_{DS}$ at $(V_{GS}-V_T)=0.5V$ for a short-channel device, L= $0.14\mu m$ ( $V_T=0.07~V$ , at 300 K and $V_T=0.33~V$ , at 77 K ) 99                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.7 Plots of $log(I_{SUB}/I_D)$ vs. $(V_{DS} - V_{DSAT})^{-1}$ for $0.14\mu m < L < 5\mu m$ , at room temperature and 77 K. Note the enhanced reduction of the substrate current generation at low temperature for short-channel devices                                                                         |

| 7.1 Concentration of Indium implanted at three different energies and boron at 50 KeV, as simulated by SUPREM                                                                                                                                                                                                    |

| 7.2 Reduction in $V_T$ as function of $V_{DS}$ for different values of implant energy 106                                                                                                                                                                                                                        |

| 7.3 (a): Subthreshold conduction for a submicron MOSFET without the deep implant. (b): Subthreshold conduction for a submicron MOSFET with the deep implant 107                                                                                                                                                  |

| 7.4 Mobility in a boron doped channel and an Indium doped channel ( with twice the dose and much shallower)                                                                                                                                                                                                      |

| 7.5 (a) Comparision of Inium and boron doped samples (Table 7.1) in terms of body effect, (b) Effect of dose on body effect, and (c) Effect of implant energy on body effect ( $t_{ox} = 5.3nm$ )                                                                                                                |

| 7.6 Plots of $log(I_{SUB}/I_D)$ vs. channel length at $(V_{DS}-V_{DSAT})^{-1}=0.55~V^{-1}$ for different values of implant energies. Note the strong dependence of substrate current generation on implant energy for submicron devices. (a) is without the deep boron implant, and (b) is with the deep implant |

| 7.7 The drain and the corresponding substrate current for two short channel devices (L=0.1 and 0.15 $\mu m$ ), at $V_{GS}=1.2$ V. Note the reduction in the substrate current, despite the increase in $I_D$                                                                                                     |

## List of Tables

| 2.1 General Scaling Laws                | •  | • | • | • | • | • | • | • | • | • | • | ٠ | • | • | • | • | • | • | . : | 29 |

|-----------------------------------------|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|----|

| 3.1 Improvements Obtained in Process .  |    |   | • |   |   | • | • | • |   |   |   |   |   |   | • |   |   |   | . 4 | 48 |

| 7.1 Comparision of In and B doped Devic | es |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 1.  | 10 |

### Chapter 1

### Introduction

Probably the most widely used electronic component is the silicon metal-oxide field effect transistor (MOSFET): It is the basic building block of logic and memory circuits in most computers and digital systems.

It is possible to form two dimensional (and one dimensional) electronic systems using the inversion layer of a MOSFET, and to control the carrier density in the 2-dimensional system over many orders of magnitude. As a result, the Si MOSFET has become one of the basic tools used in the study of electronic transport effects in so-called 2-dimensional electron gas systems, prticulary at cryogenic temperatures.

Since the invention of the integrated circuit, there has been an steady effort to increase the speed, density, and number of devices per chip. As technology has advanced, the smallest dimension in a device has been reduced exponentially with time. As the smallest device dimensions are reduced below 1  $\mu m$ , straight forward device scaling seems questionable: The major concerns are device behavior as dimensions are reduced, and yield and manufacturability of the system containing small devices. A few years ago, 1  $\mu m$  was touted to be the limit for the smallest practical device di-

mension. Now use of 0.1  $\mu m$  channel length devices not only seems to be possible, but inevitable in the near future.

Development of well-behaved short channel MOSFETs is essensial for scaling. Smaller devices are faster, and systems containing them are denser and faster. For practical applications, small MOSFETs should have a clear saturation region of operation (low output conductance), and it must be possible to turn them off sharply below threshold (high subthreshold slope). To achieve this, accurate modeling, device design, and processing are necessary.

As the device dimensions are reduced into the submicron range, in addition to traditionally studied short channel effects (effects caused by the drain and source junction control of the channel charge in the MOSFET), a number of new physical phenomena take place. Under these conditions, some of the assumptions used in modeling the longer channel devices break down. The origin of this discrepency is that in small devices, the carrier relaxation lengths and the distances over which the electric field and carrier density change, become comparable to the device length. In other words, the distances over which the carriers feel the strong electric field, and adjust to it, are close to the device length, i.e. the carriers are not in stationary balance with the electric field over a significant part of the channel. The effects caused by lack of equilibrium between the high electric field and the carrier properties are called non-stationary effects.

This thesis is a study of such non-stationary effects. The basic tool used in this work is the deep-submicron channel length Si MOSFETs. The short channel MOS-

FET is an ideal device for the study of such phenomena. It has a region of very high electric field (channel) and an injector of cold carriers (source). Many transportrelated variables can be monitored over a wide lattice and carrier temperature, electric field strength, carrier density, and, most importantly, length scales. To maximize the amount of the non-stationary effects, one has to increase the relaxation lengths. Therefore, carrier scattering in the channel of the MOSFET has been minimized. Among the non-stationary effects, probably the most prominent is velocity overshoot. This phenomenon has been oberved previously at 4.2 K [Chou, 1985]. The major goal here was to observe it phenomenon at higher temperatures. Therefore, short channel MOS-FETs with high mobility had to be fabricated as the first major part of the work. Once high mobility MOSFETs were obtained, velocity overshoot at room temperature was readily observed. A more interesting (and probably more important) effect observed, is reduction in hot electron effects. As there is less interaction between the carriers and the lattice (because of the reduced carrier temperature) such a reduction was expected. As the channel length was reduced into the deep-submicron range, a reduction in the impact ionization-induced substrate current was observed. It seems that velocity overshoot and reduction in hot electron effects are two closely related phenomena. Both these effects not only prove the existence of non-stationary transport, which occurs over short times and/or distances, and highlight the need for inclusion of a more complete transport model in device simulators, used for modeling short channel devices.

As it turns out, many of the non-stationary effects discussed above manifest them-

selves in the device performance, in devices with L $\approx$  0.1  $\mu m$ . Therefore, it is important to observe these effects in devices which are well behaved. Thus, throughout this work, the effort has been made to minimize parasitic short channel effects.

Besides this introduction and conclusion, this thesis contains six main chapters. Chapter two is a brief review of MOS device physics. The goal has been to emphasize the limitations and problems of commonly used device models. Chapter three is on device fabrication. The process used in this thesis was already developed. Modifications were made to obtain major improvements in device behavior and yield. Chapter four is a review of non-stationary transport in Si. The emphasis is on a hydrodynamic carrier transport model. The goal has been to gain physical insight into the mechanisms reponsible for non-equilibrium transport. Chapter five presents the results on observation of velocity overshoot in Si at room temperature and 77 K. Chapter six is on hot electron effects and the reduction of such effects in deep submicron devices. Chapter seven is on the use of indium as an alternative species to achieve high mobility and threshold. With indium it is possible to observe all the intersting non-stationary effects in short channel MOSFETs, without the presence of unwanted short channel effects.

### Chapter 2

## MOSFET Device Physics

This chapter discusses the fundamentals of MOSFET operation. The basic MOS capacitor, the gradual channel approximation and operation of a MOSFET are presented. Next, issues relating to scaling, mobility, short channel effects, and velocity saturation are presented. Emphasis is placed on limitations of the simple MOSFET theory.

#### 2.1 MOSFET Structure

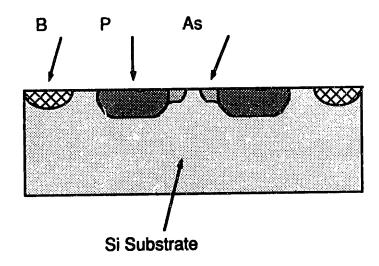

The basic MOS transistor is shown in Fig. 1. The source and drain are heavily doped regions, and the channel is doped with opposite polarity. A gate controls the carrier density on the surface. For the appropriate gate bias, the surface becomes inverted, i.e. it is populated by the same kind of carriers as majority carriers in the source and drain. Thus a conductive path between source and drain is formed, and its conductivity can be modulated by the gate.

Source and drain extend into the z direction, normal to the plane of Fig.2.1. A two dimensional electron gas is formed in the y-z plane. When modeling the MOSFET device operation, the variations along the z-axis are ignored. To be accurate, the full two dimensional Poission equation must be solved (in x-y plane):

$$\nabla^2 \psi = \frac{d^2 \psi}{d^2 x} + \frac{d^2 \psi}{d^2 y} = -\frac{q}{\epsilon s_i} (N - n + p)$$

(2.1.1)

Figure 2.1: MOSFET cross section

where  $\psi$  is the electrostatic potential. Solving the full two dimensional equation implies that the charges in the channel contribute to both lateral and normal electric field. These changes are controlled both laterally (through source and drain bias) and vertically (through gate induced electric field). In long channel devices, it can be shown that most of the charge in the channel is controlled by the gate.

$$\frac{d^2\psi}{d^2x} >> \frac{d^2\psi}{d^2y} \tag{2.1.2}$$

Under this approximation:

$$\frac{d^2\psi}{d^2x} = \frac{-q}{\epsilon_{Si}}(N-n+p) \tag{2.1.3}$$

is solved, and variations along y are ignored. It is assumed that the gate induced vertical electric field is much greater than the lateral field and the latter is ignored when calculating the charge in the channel. Lateral variation in the electric field is then accounted for by a simple resistive voltage drop along the device and the flow of the  $I_{SD}$ . This formulation is widely used and is called the gradual channel approximation (GCA). Within the context of GCA, the lateral field does not induce any charges in the channel. Therefore, two dimensional analytical solutions to the Poission's equation are not required.

#### 2.1.2 MOS Capacitor Structure

Within GCA, first the charge density induced in the inversion layer through the gate bias is obtained. This is the same as the one dimensional MOS capacitor. Fig. 2.2 shows the cross section of the MOS capacitor and the corresponding band diagram. Equation (2.1.3) must be solved.

Introducing the Fermi potential in the semiconductor bulk,  $\psi_F$  (and the thermal voltage  $\phi_t = \frac{kT}{q}$ ) [Sze]:

$$N_D^+ - N_A^- = n - p = N_D - N_A = 2n_i \sinh(\frac{\psi_F}{\phi_t})$$

(2.1.4)

Figure 2.2a: MOS capacitor cross section

Figure 2.2b: MOS capacitor band diagram

then one obtaines (in the presence of the electrostatic potential  $(\psi = \psi(x))$ :

$$n = n_i e^{-\frac{(\psi_F - \psi)}{\phi_i}} \tag{2.1.5a}$$

$$p = p_i e^{\frac{(\psi_F - \psi)}{\phi_i}} \tag{2.1.5b}$$

The differential equation for the carrier density in the MOS capacitor becomes:

$$\frac{d^2\psi}{d^2x} = \frac{2qn_i}{\epsilon_{Si}} \left(\sinh(-\frac{\psi_F}{\phi_t}) - \sinh(\frac{(\psi_F - \psi)}{\phi_t})\right) \tag{2.1.6}$$

This differntial equation is solved subject to the following boundary conditions:

$$\psi(x=0) = \psi_S \tag{2.1.7a}$$

$$\psi(x = Large) = 0 \tag{2.1.7b}$$

The first states that the surface potential is determined by the gate bias (the relation will be determined later), and the second boundary condition is just a statement of the charge neutrallity in the bulk.

Integrating 2.1.6 from x = Large to x away from the interface, the electric field becomes:

$$E(\psi(x)) = -\frac{d\psi}{dx} = \pm \left(\frac{2qn_i}{\epsilon_{Si}}\right)^{1/2} \left[ (N_A - N_D)\psi + n_o\phi_t(e^{-\frac{\psi}{\phi_t}} - 1) + p_o\phi_t(e^{\frac{\psi}{\phi_t}} - 1) \right]^{1/2} (2.1.8)$$

where  $n_o$  and  $p_0$  are the equilibrium values of electron and hole density in the silicon. Knowing the electric field as a function of the potential in the semiconductor, the total induced charge per unit area,  $Q_C$ , can be found using:

$$Q_C = \epsilon_{Si} E_{Surface} = \epsilon_{Si} E(\psi = \psi_{Surface})$$

(2.1.9)

The result is then:

$$Q_C = \pm (2qn_i\epsilon_{Si})^{1/2} [(N_A - N_D)\psi_S + n_o\phi_t(e^{-\frac{\psi_S}{\phi_t}} - 1) + p_o\phi_t(e^{\frac{\psi_S}{\phi_t}} - 1)]^{1/2}$$

(2.1.10)

where the sign of  $Q_C$  agrees with the sign of  $\psi_S$ . In Fig. 3, the total charge induced in the semiconductor as a function of  $\psi_S$  is plotted.

Equation (2.1.10) describes all the regions of operation of a MOS structure: For p-type silicon, if  $\psi_S$  is negative, the second term in the bracket dominates, and the majority holes are present (accumulation). If  $\psi_s$  is small and negative, a depletion layer is formed. For large negative  $\psi_S$ , the minority electron density dominates, and inversion occurs. All that remaines, is to relate the gate bias to  $\psi_S$ . The field in the oxide is:

$$E_{ox} = \frac{\epsilon_{Si}}{\epsilon_{ox}} E_S \tag{2.1.11}$$

The voltage drop in the oxide is:

$$\Delta V_{ox} = \frac{\epsilon_{Si} t_{ox}}{\epsilon_{ox}} E_S \tag{2.1.12}$$

Then:

$$V_G = \psi_s + \Delta V_{ox} \tag{2.1.13}$$

This equation can be solved for  $\psi_S$  for a given  $V_G$ , and the total charge in the semiconductor can be found.

The above equation can be solved exatly. It can be seen that, in inversion, the total charge has two parts: First is that of the depletion region and second is that of a very narrow sheet of high density on the surface. This has prompted the introduction of delta-depletion approximation. That is inversion sheet is modeled by an infinitely thin charge sheet. In this model strong inversion occurs for  $\psi_S = 2\psi_F + \Delta\psi = \phi_B$ , where  $\Delta\psi$  is of the order of 3-6  $\phi_T$  [Tsividis]. The extra  $\Delta\psi$  is due to the fact that the surface, in strong inversion, gets pinned to  $\phi_B$  and not  $2\psi_F$  as many authors have claimed. Total inversion charge density is:  $Q_I = C_{ox}(V_{GS} - V_T)$  where the threshold voltage is:

$$V_T = V_{FB} + \phi_B + \gamma(\sqrt{\phi_B} - \sqrt{\phi_B + V_{BS}})$$

(2.1.14)

Figure 2.3: Total charge induced as a function of  $\psi_S$

where  $\gamma = \sqrt{\frac{2\epsilon_{Si}qN_A}{C_{ox}}}$  is the body effect,  $V_{FB} = \phi_{MS} + \phi_B + \frac{Q_T}{C_{ox}}$  is the flat band voltage,  $\phi_{MS}$  is the work function,  $Q_T$  is the total charges on the semiconductor surface and in the oxide (mobile and fixed), and  $V_{BS}$  is the substrate bias (with respect to the inversion layer). The depletion charge, when in inversion, is given by  $Q_{depl} = -qN_AW_{depl}$ , where the depletion region width is:

$$W_{depl} = \sqrt{\frac{2\epsilon_{Si}}{qN_A}\phi_B} \tag{2.1.15}$$

#### 2.1.2 MOSFET Operation

In this section, a simplified theory of the p-channel MOS transistor is presented. The effects due to small geometry and variations in the mobility are ignored. The approximations used in GCA are emphasized.

The total current in MOS transistor is made up of drift and diffusion parts:

$$dI_D = dI_{drift} + dI_{diff} (2.1.16)$$

For the drift current at a distance dx below the surface, at location (x, y):

$$dI_{drift} = q\mu n(x, y) dx \frac{\partial \psi(x, y)}{\partial y}$$

(2.1.17a)

and the diffusion component is:

$$dI_{diff} = -wDdx \frac{\partial n(x,y)}{\partial y}$$

(2.1.17b)

Now since  $n(x,y) \propto e^{\psi(x,y)}$ , it can be shown that [Tsividis]:

$$I_D = -\frac{W}{L} \int_{V_{SB}}^{V_{DB}} \mu Q_I dV$$

(2.1.18)

Where  $Q_I$  is the mobile channel charge. This is an exact expression and can be used in all regions of operation. If the lateral field is much smaller than the normal field (GCA), then

the free charge obtained from calculations of one dimensional MOS structure can be used. One can use either the charge obtained through the charge sheet model (i.e.  $Q_C$  in (2.1.10) or use the more exact charge obtained from the exact solotion of Poission's equation in one dimension (Pao-Sah Model). Here, the charge sheet model will be presented.

In charge sheet model the mobile charge density  $Q_I(y)$  is:

$$Q_I(y) = -C_{OX}(V_{GB} - V_{FB} - \phi_B - V_{CB} + \frac{Q_B'}{C_{OX}})$$

(2.1.19)

where  $Q'_B$  is:

$$Q_B' = -\gamma C_{ox} \sqrt{\phi_B + V_{CB}} \tag{2.1.20}$$

and  $\gamma$  is the body effect, given before. Carrying out the above integration, for the drain current in the linear region [Tsividis]:

$$I_{DS} = \frac{W}{L} \mu C_{ox} [(V_{GS} - V_{FB} - \phi_B) V_{DS} - \frac{V^2_{DS}}{2} - \frac{2}{3} \gamma ((\phi_B + V_{SB} + V_{DS})^{3/2} - (\phi_B + V_{SB})^{3/2})]$$

(2.1.21)

This expression for current can be simplified to:

$$I_{DS} = \frac{W}{L} \mu C_{ox} [(V_{GB} - VT)V_{DS} - 0.5(1 + \delta)V^{2}_{DS}]$$

(2.1.22)

where  $\delta$  is related to the gamma. The phenemenon of current saturation and pinch-off in the channel are predicted to occur when the free charge in the channel goes to zero.

$$Q_I = 0 (2.1.23)$$

then the saturation voltage is:

$$V_{DSAT} = V_{GS} - V_T (2.1.24)$$

The current in the saturation region becomes:

$$I_{DS} = \frac{W}{L} \mu C_{ox} \frac{(V_{GS} - V_T)^2}{1 + \delta}$$

(2.1.25)

The fact that the mobile charge goes to zero, implies infinite electric field at the pinch-off point. Two dimensional solutions show that the charge density in the channel is never zero and electric field does not become large. At the pinch off point diffusion becomes an important mechanism for transport [Taylor]. After this point current saturation occures and the drift becomes the dominant form of the curent. But the GCA model does not include explicitly current saturation and a mechanism for transfer of curent from the drift mode to the diffusion. As the channel length is reduced and the lateral electric field (and its gradient across the channel) increase, it is expected that these problems with the GCA and the charge sheet model will be agravated.

#### 2.2 Mobility in Inversion layers

Electron mobility in inversion layers is one of the most fundamental parameters in MOS device physics, and must be known for accurate device modeling and design. There is also interest in carrier mobility as an indicator of accuracy of the quantum mechanical models of the two dimensional system at the  $Si/SiO_2$  interface.

In bulk Si, at low temperature (T < 100 K), the mobility is limited by the ionized impurity scattering, and the mobility behavior can be very well explained by the Brook-Herring model (At low carrier densities mobilities close to  $10^5 \text{ cm}^2/V.s$  have been obtained) [Long]. At higher temperature and low carrier densities (below  $10^{16}$ ) the bulk mobility is limited by the accoustic phonon scattering. At higher impurity scattering, the ionized impurity scattering again sets in and reduces the mobility.

Mobility behavior in the silicon inversion layer is considerably more complicated. This is due to the two-dimensional nature of the electron gas and the presence of a normal field that confines the carriers next to the surface. Three scattering mechanisms are recognized

as the main causes of mobility degradation in inversion layers: First is the acoustic phonon scattering which is the dominant scattering mechanism for T > 100 K and at low carrier densities. Coulumb scattering due to ionized impurity scattering, fixed oxide charges, and interface state charges is the second mechanism which is dominant at low temperature (T < 100 K), where the phonon density is low). At room temperature, Coulomb scattering is important for lightly inverted surfaces and low normal fields in the inversion layer. At high inversion levels the contribution of the Coulomb scattering is reduced due to screening of the impurities and charge centers. At very high donor densities,  $(> 10^{17})$  impurity scattering becomes important again. The third important carrier scattering mechanism is that of surface roughness scattering. This type of scattering is important under strong inversion.

In silicon inversion layers, mobility  $\mu_{eff}$  is determined from the drain conductance  $g_D = \frac{I_{DS}}{V_{DS}}$ :

$$\mu_{eff} = \frac{L}{W} \frac{g_D}{Q_I(V_{GS})} |_{V_D \to 0}$$

(2.2.1)

where  $Q_I$  can be determined experimentally:

$$Q_I(V_{GS}) = q \int_{-\infty}^{V_{GS}} C_{GC}(V_G) dV_G$$

(2.2.2)

and  $C_{GC}$  id the gate to channel capacitance.

At room temperature, it is found that the mobility is a stronge function of the normal field. According to [Sun and Plummer], as the substrate doping level is increased, the maximum carrier mobility (mobility near the threshold) decreases. This is not a result of impurity scattering, but rather a result of the increase in the effective normal field necessary for inversion. Thus it is found that:

$$\mu_e \propto (E_{eff})^{-\alpha} \tag{2.2.3}$$

where  $E_{eff}$  is the effective (normal) electric field and  $\alpha$  is an empirically determined constant:  $\alpha \approx 0.2 - 0.3$  at low normal fields in which the phonon scattering dominates  $(E_{norm} < 0.5 \ MeV/cm)$  and  $\alpha = 1$  at high normal fields where the surface roughness scattering dominates  $(E_{norm} > 0.5 \ MeV/cm)$ . This relation seems to be universal, and holds over a wide range of impurity densities. At low carrier concentrations at room temperture, it is found that the universal relation breaks down (probably due to lack of screening).

Effective field in an inversion layer can be written as:

$$E_{eff} = \frac{1}{\epsilon_{SI}} \left[ \frac{1}{2} Q_I + Q_B \right] \tag{2.2.4}$$

This is the average field felt by the carriers in the inversion layer.  $Q_B$  is given by:

$$Q_B = (2q\epsilon_{SI}N_A\phi_B)^{1/2} \tag{2.2.5}$$

and  $Q_I$  is given by (2.2.2). As the substrate doping is increased, the threshold increases, and the increased normal field (caused by increased  $Q_B$ ) at the threshold reduces the carrier mobility. Thus according to this model, in order to increase the carrier mobility, the normal field at the threshold must be decreased. This can be achieved by lowering the substrate doping. Decreasing the substrate doping causes increase in short channel effects in sub-micron channel length devices. In this work a nonuniform substrate doping was used: the channel doping was kept low to minimize the impurity scattering, while just below the surface, the doping was kept as high as possible to reduce the short channel effects.

It has to be emphasized that systematic measurements of mobility in samples in which effect of normal field and impurity scattering were separated, have not been performed.

#### 2.3 Scaling

As the device size is scaled down, one major aim has been to come up with a set of design rules following which the scaled down devices would operate similar to large devices. Different scaling rules have been proposed: One holds the electric field strength constant as the device is scaled down (constant field scaling). Another set of rules aims for device operation with the constant voltage supply (constant voltage scaling). Another set of rules attempts to operate the scaled device under reduced voltages and higher fields (quasiconstant voltage scaling). Each one of these rules imposes a different set of constraints on the scaling of lengths and doping levels, and results in different trade-offs between speed, power, and power-delay product.

The generalized scaling theory was developed by [Baccarani, 1984]. For a given device geometry, the field configuration within device is given by a solution of the Poisson's and te current continuity equations:

$$\frac{\partial^2 \psi}{\partial x^2} + \frac{\partial^2 \psi}{\partial y^2} + \frac{\partial^2 \psi}{\partial z^2} = \frac{q}{\epsilon_{Si}} (p - n + N_D - N_A)$$

(2.3.1)

$$\nabla \cdot \vec{J} = 0 \tag{2.3.2}$$

If the spatial dimensions are scaled by  $1/\lambda$  and the voltages are scaled by  $1/\kappa$  (i.e. the electric field is scaled by  $\kappa/\lambda$ ), and defining the scaled variables:

$$(x', y', z') = (x, y, z)/\lambda$$

(2.3.3a)

$$\psi' = \psi/\kappa \tag{2.3.3b}$$

$$(p', n', N_D', N_A') = (p, n, N_D, N_A)\lambda^2/\kappa$$

(2.3.3c)

Then the following differential equation is satisfied by the scaled quantities:

$$\frac{\partial^2 \psi'}{\partial x'^2} + \frac{\partial^2 \psi'}{\partial y'^2} + \frac{\partial^2 \psi'}{\partial z'^2} = \frac{q}{\epsilon_{Si}} (p' - n' + N'_D - N'_A)$$

(2.3.4)

#### General Scaling Laws

| Linear Dimensions:      | $(W, L, t_{ox}, x_j)$   | $1/\lambda$          |

|-------------------------|-------------------------|----------------------|

| Biases:                 | $V_{GS}, V_{DS}, V_{T}$ | $1/\kappa$           |

| Impurity Concentration  | $N_A, N_D$              | $\lambda^2/\kappa$   |

| Current:                | $I_D$                   | $\lambda/\kappa^2$   |

| Electric Field:         | $oldsymbol{E}$          | $\lambda/\kappa$     |

| Transistor Transit Time | $t_{oldsymbol{d}}$      | $\kappa/\lambda^2$   |

| Power Delay Product:    | $I_D V_D t_D$           | $1/\lambda \kappa^2$ |

Table 2.1

This is identical to equation (2.3.1). If the boundary conditions are scaled too, then the two electric field solutions have identical shape, but are different only in intensity. It must be emphasized that only Poisson equation has been scaled down: The influence of the current continuity equation on the potential distribution has been ignored. This assumption is fine under the subthreshold condition, where the electron concentration is negligible. Under strong inversion, the carrier density in the channel is exponentially dependent on  $\psi_S$ , and it no longer scales by  $\lambda^2/\kappa$ . But if a charge sheet model is assumed (infinitely thin inversion layer), scaling still applies.

Table 2.1 summarizes the scaling factors within the generalized scaling theory. Some of the assertions in terms of speed or power performance of scaling models are questionable. But there is no doubt that scaling improves the packing density and overall speed. In practice, when scaling devices into the deep submicron range, the scaling rules are not followed exactly. The goal is to maximize current drive, mobility, turnoff speed, and minimize output conductance. Some of these goals are contradictory, and depending on the device application, different approaches are taken.

The scaling theory has a number of limitations. The most significant of these is that short channel effects, and turn-off characteristics degradation are ignored. As the device is scaled down, its turnoff characteristics (sub-threshold slopes at different  $V_{DS}$ ) not only

do not improve, but they worsen. It is no longer possible to scale the threshold (i.e. it is not possible to scale the built-in potentials).

Among other problems with scaling models are the effect of the finite inversion layer thickness. As the gate oxide thickness is reduced below 10 nm, its thickness becomes comparable to that of the inversion layer thickness. Finite inversion layer thickness, reduces the effective gate drive (from  $C_{ox}$ ), i.e. the effective gate-channel capacitance is oxide capacitance in series with the bulk and the inversion layer capacitance [Sodini 1982]:

$$C_{GC}(V_{GS}) = \frac{\partial Q_I}{\partial V_{GS}} = \frac{C_{ox}C_{inv}}{C_{ox} + C_{inv} + C_B}$$

(2.3.5)

where  $C_B = \frac{\partial Q_B}{\partial \psi_S}$  is the bulk capacitance and  $C_{inv} = \frac{\partial Q_{inv}}{\partial \psi_S}$  is the inversion layer capacitance. The apparant reduction in the gate drive, is most severe close to the threshold, and causes reduction of  $I_D$ . This might look as if the mobility is degraded in the thin oxide device [Han], but if the  $C_{GC}$  is measured properly, no degradation is observed [Liang].

In scaled devices there is mobility degradation due to increase in the substrate doping and the resultant increase in the normal field under which the device operates. This effect is not included in a straight forward scaling model. As devices are scaled down they operate under larger lateral fields too. This causes velocity saturation.

In scaled devices, the parasitic resistances per device increase. The amount of degradation caused by the parasitics becomes more important as the devices operate under larger current densities.

Despite all these problems, scaling has provided general guidelines for design and understanding of small device, and works very well in the  $L>0.5~\mu m$  range.

#### 2.4 Short Channel Effects

As the MOSFET channel length is scaled down into the deep submicron range, un-

wanted effects associated with the drain control of the channel and the two dimensional structure of the MOSFET, become more prominent. Among these are reduction of the threshold as the channel length is reduced, the increased output conductance, reduction of the subthreshold swing (slope), reduction in body effect coefficient, and dependence of threshold voltage on  $V_{DS}$  (drain induced barrier lowering or DIBL). These effects are closely related, are caused by sharing of the space charge layer of the drain-bulk junction and the channel depletion charge at the drain side of the channel. When this common charge becomes a significant part of the channel charge, then the drain voltage influences the channel properties. The charge sharing model, used in modeling of short channel devices is presented next. There are a number of other effects that take place mainly in the short channel devices (hot-electron effects and velocity saturation) and have a different origin. They are explained later.

### 2.4.1 Charge Sharing Model

This model concerns itself with the effect of drain and source depletion layer on the threshold of a short channel device. This is a very simple conceptual model and it is not possible to justify all its steps.

Consider the short channel MOSFET in Fig. 2.4. When calculating the threshold in a long channel device, it is assumed that all the charges in the inversion layer and the depletion layer have their image on the gate electrode, i.e. this is essentially a one dimensional problem. In other words, the gate bias must be large enough to support all the charges in the channel. In a short channel device, a significant fraction of the field lines from the channel charges terminate on the drain. Thus, the extra charge on the gate (at a given gate bias), must terminate on the extra inversion charges in the channel, i.e. more

$I_D$  and lower  $V_T$ . In a long channel device the threshold voltage is:

$$V_T = V_{FB} + \phi_B - \frac{Q_B}{C_{ox}} \tag{2.4.1}$$

If the channel is short, the fraction of the channel whose field lines terminate on the drain, has to be subtraced from the total depletion charge in the threshold formula  $(Q_BL)$  (Figure 2.4):

$$V_T = V_{FB} + \phi_B - \frac{Q_B L - \Delta Q_B}{L C_{ox}} \tag{2.4.2}$$

Thus the reduction in the threshold voltage due to charge sharing is:

$$\Delta V_T = \frac{\Delta Q_B}{LC_{or}} \tag{2.4.3}$$

For a  $n^+$  junction of radius  $r_j$ , and space charge layer thickness  $l_S$  at  $V_{DS} = 0$ , using simple geometrical argument:

$$\Delta V_T = \gamma \frac{r_j}{L} (\sqrt{1 + \frac{2l_S}{r_j}} - 1) \sqrt{V_{SB} + \phi_B}$$

(2.4.4)

For a deep junction, a Taylor expansion of the above formula can be obtained:

$$\Delta V_T = \frac{q N_A W_{max}}{C_{ox}} \frac{l_S}{L} \tag{2.4.5}$$

This expression states (as expected) that the charge shared is proportional to the product of space charge layer thickness and the substrate doping:

$$\Delta Q_B \propto N_A \times l_S \tag{2.4.6}$$

The fraction of the charge shared between channel and drain junction is:

$$\frac{\Delta Q_B}{Q_B} \propto \frac{l_s}{L} \propto \frac{1}{L} \sqrt{\frac{1}{N_A}} \tag{2.4.7}$$

Figure 2.4: Cross section of a short channel MOSFET, showing the the charge shared,  $\Delta Q_B$

Expression (2.4.7) shows why increasing the substrate doping reduces the short channel effects. Increase in substrate doping increases the net amount of the charge shared, but reduces the fraction of the charge shared between  $n^+$  junctions and the channel.

Putting a heavily doped substrate just below the surface would also reduce the short channel effect (while keeping the threshold constant): The heavy  $p^+$  doping just below the surface, reduces the depletion layer width just below the surface. Then the charge shared is the product of a small  $l_S \propto \sqrt{1/N_A^+}$  and a light surface doping  $\propto N_A$ , and the charge shared is reduced (Figure 7.2, Chapter 7).

If there is finite bias on the drain and source,  $\Delta V_T$  can be approximated (for small  $V_{DS}$ ) as:

$$\Delta V_T = \frac{q N_A W_{max}}{C_{ax}} \left(\frac{l_S + l_D}{2L}\right) \tag{2.4.8}$$

where  $l_S$  and  $l_D$  are the space charge layer thicknesses at finite source and drain biases:

$$l_D = \sqrt{\frac{2\epsilon}{qN_A}} \sqrt{\phi_B + V_{DB}} \tag{2.4.9}$$

For small  $V_{DB}$  (compared to  $2\psi_F$ ), threshold shift is:

$$\Delta V_T = \alpha_1 \frac{\epsilon_{Si}}{\epsilon_{ox}} \frac{t_{ox}}{L} [(\phi_B + V_{SB}) + \alpha_2 V_{DS}]$$

(2.4.10)

This relation predictes a linear variation of  $\Delta V_T$ . Although this was derived for small  $V_{DB}$ , measurements and two dimensional simulation shows that this relation holds for large values of  $V_{DB}$  also (Figure 7.2).  $\alpha_1$  and  $\alpha_2$  are constants that depend on the process and channel length. According to this relation, reduction in  $t_{ox}$  would reduce the short channel effects.

The charge sharing model is an intuitive tool for understanding short channel effects. It does not address issues raised by the breakdown of the gradual channel approximation. When designing short channel MOSFETs, one must use two dimensional simulators for accurate predication and models.

## 2.5 Velocity Saturation

As the magnitude of the lateral electric field applied to the semiconductor increases, the electrons begin to gain energy. To balance the energy gain from the field, there is an increase in the rate of energy loss to the lattice. The primary loss mechanism at high fields, is optical phonon emission. At very high fields, because of the increase in the phonon emission rate, velocity saturates. The high field transport, and saturation velocity in the steady state, are governed primarily by the interaction of the electrons and phonons, and are independent of impurity scattering and the details of low field mobility.

The saturation velocity  $v_s$  is given as:

$$v_s = \sqrt{\frac{3\hbar\omega_o}{4m}\tanh\frac{\hbar\omega_o}{2kT_o}} \tag{2.5.1}$$

where  $h\omega_o$  is the energy of optical phonon emission, and  $T_o$  is the lattice temperature. When used in device modeling, it is useful to obtain a relationship between mobility and electric field that includes the velocity saturation term also. One such relationship is:

$$\mu(E) = \frac{\mu_o}{[1 + (\frac{E}{E_C})^{\beta}]^{1/\beta}}$$

(2.5.2)

where  $E_C$  is the critical field for the velocity saturation,  $v_s$ :

$$E_C = \frac{v_s}{\mu_o} \tag{2.5.3}$$

For silicon,  $\beta$  values between 1 and 2 have been used.

## 2.5.1 MOSFET with Velocity Saturation

In this section a simple theory of MOSFET under the effect of strong lateral field and velocity saturation is presented. This model is useful in explaining some of the effects seen in short channel MOSFETs. The mobility model used is as follows:

$$v = \frac{\mu_{eff}E}{1 + E/E_c} \qquad E < E_c$$

$$= v_{sat} \qquad E > E_c$$

(2.5.4)

where E is the lateral field and  $E_c = 2v_{SAT}/\mu_{eff}$  is the critical field for velocity saturation.  $\mu_{eff}$  is the effective carrier mobility:

$$\mu_{eff} = \frac{\mu_o}{1 + a(V_{GS} - V_T)} \tag{2.5.5}$$

where a is an experimentally determined constant. Furthermore in this model it is assumed that the drift dominates the total current, and the total number of the carriers in the channel is given by  $C_{ox}(V_{GS} - V_T)$ . In the linear region, the current at any point along the channel is the product of the carrier velocity, v(x), and density:

$$I_D = I(x) = WC_{ox}(V_{GS} - V_T - V(x))v(x)$$

(2.5.6)

Expressing v(x) in terms of  $E(x) = -\frac{dV(x)}{dx}$ , and integrating from source to drain, one obtaines:

$$I_D = \frac{W\mu_{eff}C_{ox}(V_{GS} - V_T - V_{DS}/2)}{L(1 + V_{DS}/E_cL)}V_{DS}$$

(2.5.7)

this is valid for operation in the saturation region. Saturation of current is at the point where carriers are moving with the saturation velocity, i.e.  $E = E_c$  at the drain side. At the saturation point:

$$I_D = W v_{SAT} C_{ox} (V_{GS} - V_T - V_{DSAT})$$

(2.5.8)

where  $v_{SAT}$  is the drain saturation velocity. Solving for  $V_{DSAT}$  by equation Eq. (2.5.8) and Eq. (2.5.7), one obtaines:

$$V_{DSAT} = \frac{E_c L (V_{GS} - V_T)}{E_c L + (V_G - V_T)}$$

(2.5.9)

As one scales the channel length, it takes less drain bias for the critical field to get to  $E_c$ , and thus  $V_{DSAT}$  is reduced from its first order theory. This simple model will later be used in chapters on velocity overshoot and hot electron effects.

# Chapter 3

# **Fabrication**

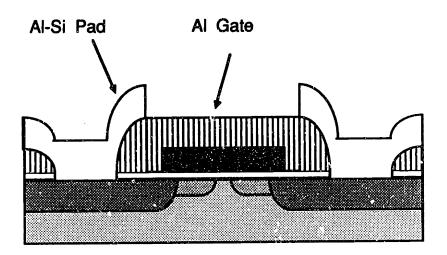

This chapter reviews the techniques used in the fabrication of deep submicron MOS-FET. The basic process was developed by [Chou, 1986]. Some improvements in his process have been made.

#### 3.1: Introduction

As the device dimensions are reduced and the density of devices is increased, a number of new fabrication obstacles are encountered. It is no longer possible to use techniques used in fabrication of deep long channels and apply them to fabrication of submicron devices. The foremost among them is the issue of lithography. Because of the limits of optical lithography it is not possible to reliably put down linewidths below 0.5  $\mu m$  using commercially available G-line or H-line optical steppers (Using high NA oil immersion lenses, Kausta et al have achieved 0.13  $\mu m$  linewidth, but this was a research demonstration). This is not the only the limitation of optical systems: the variations in the linewidths defined with optical lithography become unacceptable in the submicron range. That is why one has to resort to shorter wavelength lithographic tools e.g. X-ray or electron beam.

Lithography is not the only technological issue faced in fabricating of short channel devices: Because of scaling of all device dimensions, e.g. the junctions, oxide thickness and

the contact areas, etching and patterning tolerances of most fabrication steps decrease. More controlable, uniform, and selective fabrication steps have to be developed. Probably the biggest challenge in utilization of deep submicron MOS devices will be the reduction of mismatch among devices and uniformity across wafer. As the dimensions are reduced the devices operate at higher speeds and current densities. It is extremely important (and very difficult because of shallower junctions) to reduce parasitic resistances and capacitances. Small changes in parasitics will cause unacceptable variations in performance.

At MIT we did not have access to e-beam lithogrophy, and there was a x-ray exposure system available. A process based on use of this system to fabricate short channel devices was developed here by Chou. Since the details of his process were reported earlier, the details will be only briefly repeated here, along with the modifications made in the current thesis work. First the fabrication of x-ray mask would be reported, and then the details of fabrication steps are presented. The results will be compared with those obtained earlier.

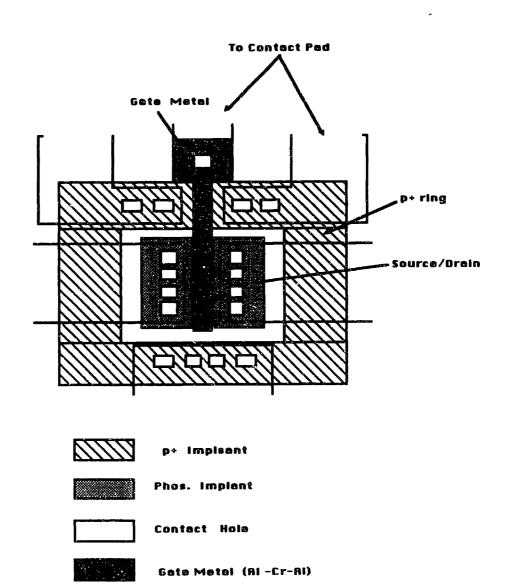

# 3.2 Fabrication of X-ray Mask

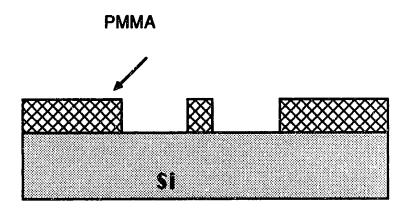

To fabricate short channel MOSFET's, narrow linewidths must be defined. The conventional patterning tool for small linewidths has been either electron-beam lithography or x-ray lithography. Previous work in the Submicron Structures Lab (SSL) at MIT has made use of x-ray lithography. The x-ray mask membrane has been organic (polyimide). Thus, there was significant distortion across the mask. As a result one is not able to align the mask to a previous layer. This excludes use of the mask for self-aligened structures (This problem would go away if one used inorganic masks, a project currently being pursued in the SSL). As a result, the x-ray mask must be used as the first layer and all the subsequent layers must be aligned to it. Since we are fabricating short channel MOSFET's, x-ray will be used to define source and drain regions in x-ray resist, the PMMA. The pattern

in PMMA will later be used as a mask against ion implantation, during the formation of source and drain regions.

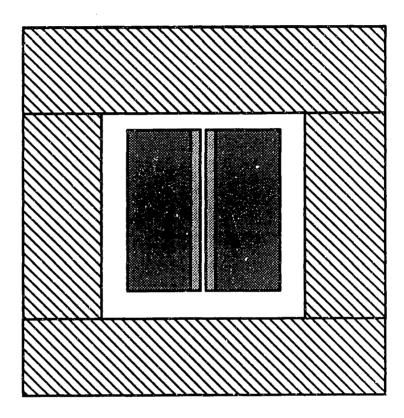

X-ray masks memebranes used are thin polyimide ( $\approx 1 \mu m$  thick) stretched on a vespel ring, as shown in Fig. 3.1. Coarse patterns are defined on the back of the mask by means of optical lithography. Fine features are defined in gold on the front of the mask by means of shadowing to a mesa step formed in polyimide. A good part of fabrication of the x-ray mask involves forming vertical sidewall mesas on Polyimide for the susequent shadowing.

X-ray masks are fabricated as follows: (110) Si wafers ( with flat along (111)) are oxidized in dry  $O_2$  ( $t_{ox}=450~A$ ). This oxide is later used as a mask for formation of mesas. On two corners of the wafer, sets of alignment mark, each rotated  $0.5^{\circ}$  with respect to the other, are placed along with rectangles. The goal here is to find a set of alignment marks which correspond to well that are optimally aligned to the crystallographic axis. Oxide is etched below this pattern. Resist is striped. Using anisotropic etching  $(KOH: H_2O: Isopropylalchohal\ 3:8:2$  by volume at  $80^{\circ}C$ ) Si is etched (0.2  $\mu m$  for about 1 minute). Etch rate is about 100 times faster on (110) plane (bottom of the wells) as compared to the (111) planes (sides of the wells). If we are very closely aliegned to the (111) plane, very smoth well walls are obtained (Figure 3.2).

Also, along the intersection of (111) planes and (110) planes the etch rate is different and as a result striations appear on the bottom of the square wells. These lines make an angle of 35.3° with the (111) plane. Therefore, one has to find the rectangle in which the striations on the bottom of well make an angle of 35.3° with the wall of the well. The wall of that well is along (111) and the corresponding set of alignment marks are exactly parallel to the (111) plane. Close examinations of the walls that are off alignment by even 2°, indicates that any steps in these walls are less than 10 nm.

Figure 3.1: An x-ray mask: A thin polyimide memberane stretched on a vesple ring

# Anisotropic Etching of Si

Figure 3.2 SEM micrograph of a (110) Si wafer in which wells were etched. The side wall to the left is (111) plane. Note the extremely smooth sidewall that results from anisotropic etching.

After finding the right alignment mark (the one that is aligned to the (111) plane), the mesa pattern is defined by optical projection lithography, and etched into oxide all over the wafer. Next, silicon is etched in the same anisothropic etch as before for about  $0.25 \ \mu m$  (Figure 3.3a). Then oxide is stripped everywhere and about 1  $\mu m$  of Polyimide (Dupont, type PI-2555) is spun on . After curing at 80°C for 30 minutes and a 150°C to 250°C ramp in about 3 hours, it is cured at 400° for 30 minutes (Figure 3.3b). About 10 nm of chromium (for adhesion) and 150 nm of gold is e-beam evaporated. Next the coarse pattern (on the back of x-ray mask) is defined in photoresist (all features of the mask, except the submicron lines). Gold is patterned in an ion miller (Wet etch although easier causes severe undercutting and loss of critical dimension) (Figure 3.3c). Then, a espel ring (about 1 inch in diameter) is attached and silicon is etched from the back in  $HF: HNO_3$ , 97: 3. If there is too much bubling, the amount of  $HNO_3$  can be reduced further. After the etch, the thin membrane is left streched on the ring. Then the fine line gold absorber is produced by angle evaporation on mesa side walls at 4° to the desired thickness (Figure 3.3d).

In most of our work, 150, 200 1nd 250 nm absorber lines were used. Previously the excess gold was ion milled from the back surface. It was found that there is no need for this since the very thin layer of gold on back is transparent to x-ray. Moreover, ion milling causes excess heating of the mask (and breakage). As a last step, 50 nm of Al is evaporated on the back of the mask to help in forming contact between the mask and the wafer during the x-ray exposure. The mask is used to expose about 0.2  $\mu m$  of PMMA on device wafers.

#### 3.2.2 X-ray Exposure

The x-ray mask is used to carry out x-ray exposure. The x-ray source is the  $C_k$  line of a graphite target ( $\lambda$  =4.5 nm). The mask was held intimately into contact with the

d- MOUNT VESPEL RING ETCH SI SHADOW EVAPORATE AU

Figure 3.3: Steps involved in fabrication of x-ray mask

substrate. The substrate is a lightly doped p-type ( $\rho = 10\text{-}20~\Omega - mm$ ), coated with 220 nm of PMMA. The distance between the source and the mask is about 10.5 cm, and for our low power source (300 Watt), exposure takes about 12-18 hours. After exposure the samples were developed in isopropyl alchhol-MIBK solution (ratio of 60-40 by volume). A typical line obtained by the x-ray exposure is presented in Fig. 4.4.

## 3.2 Device Fabrication

The pattern obtained by x-ray lithography is used as a mask for the source and drain implantation. Arsenic, with an energy of 30 KeV and a dose of  $7 \times 10^{15}$  per  $cm^2$  is used for  $n^+$  source and drain. The 200 nm PMMA thickness is more than enough to stop the As, whose range is R=31 nm and straggle is  $\Delta R=9$  nm. To stop 99.999% of the As, the thickness of PMMA must be greater than  $R+4.3\Delta R=70$  nm.