ALEPH 95-94 DATACQ 95-01 U. Becker et al. 28.7.1995

## The Hitchhiker's Guide to the Level1 Universe

U. Becker, B. Rensch, J. Sommer, S. Werner Institut für Hochenergiephysik, Universität Heidelberg, Germany

## LEVEL1 ONLINE MANUAL

2nd edition July 1995

# Contents

| 1 | DA                     | Q in a  | Nutshell                    | 6  |

|---|------------------------|---------|-----------------------------|----|

|   | 1.1                    | The F   | inite State Machine         | 6  |

|   | 1.2                    | Startin | ng a Run                    | 7  |

|   | 1.3                    | The R   | Readout                     | 7  |

|   | 1.4                    | The M   | Monitoring                  | 8  |

|   | 1.5                    | The R   | Run Quality                 | 8  |

| 2 | $\mathbf{A}\mathbf{X}$ | AONL    | and FIC                     | 9  |

|   | 2.1                    | AXAC    | ONL                         | 9  |

|   | 2.2                    | FIC     |                             | 10 |

| 3 | X1                     | MIST:   | The Level1 Data Base Editor | 12 |

|   |                        | 3.0.1   | Link Trigtype               | 13 |

|   |                        | 3.0.2   | Edit Resources              | 14 |

|   |                        | 3.0.3   | Work on Hardware            | 15 |

|   |                        | 3.0.4   | Define Trigger Bits         | 15 |

|   |                        | 3.0.5   | Test TrigType               | 16 |

|   |                        | 3.0.6   | Trigger Help/Doc            | 16 |

|   |                        | 3.0.7   | Accommodation               | 16 |

|   |                        | 3.0.8   | Write Monitor_Info to FIC   | 18 |

|   |                        | 3.0.9   | Start Monitor on FIC        | 18 |

|   |                        | 3.0.10  | List DBmods                 | 18 |

|   | 3.1                    |         | to do What with X1MIST      | 18 |

|   |      | 3.1.1    | Dis- or Enable a Trigger                            | 18 |

|---|------|----------|-----------------------------------------------------|----|

|   |      | 3.1.2    | Set Downscale Factors and Random Trigger Parameters | 19 |

|   |      | 3.1.3    | Set Thresholds                                      | 19 |

|   |      | 3.1.4    | Disable an ADC, TDC or TSS from Readout             | 20 |

|   |      | 3.1.5    | Change the Timing                                   | 20 |

|   |      | 3.1.6    | Change the Trigger Logic                            | 21 |

| 4 | Peri | manen    | t Tasks on the VAX                                  | 23 |

|   | 4.1  | X1DA     | Q                                                   | 23 |

|   | 4.2  |          | )N                                                  |    |

|   | 4.3  | X1VEI    | R                                                   | 24 |

|   | 4.4  | X1AN     | L                                                   | 24 |

|   | 4.5  |          | ССН                                                 |    |

|   | 4.6  | Update   | e Error Messages                                    | 24 |

| 5 | Util | ities or | n the VAX                                           | 25 |

|   | 5.1  |          | B                                                   |    |

|   | 5.2  |          | ERT                                                 | 26 |

|   | 5.3  |          | D                                                   | 26 |

|   | 5.4  |          | D                                                   | 26 |

|   | 5.5  |          | R                                                   | 27 |

|   | 5.6  |          | OG                                                  | 27 |

|   | 5.7  | ErrHel   | p                                                   | 28 |

|   | 5.8  | CIA .    | -<br>                                               | 29 |

|   | 5.9  | PRESE    | ENTER                                               | 29 |

|   | 5.10 | HEDT     |                                                     | 29 |

|   | 5.11 | X1PRI    | ES                                                  | 29 |

|   |      |          | ART                                                 | 30 |

|   |      |          | EREF                                                | 30 |

|   | E 11 | VICAI    | I D                                                 | 20 |

| 5.17 |                                                                                                                    | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | X1RUNQ                                                                                                             | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 5.17.1 Update the Run Quality Code                                                                                 | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.18 | X1TRGD                                                                                                             | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.19 | X1NEWS                                                                                                             | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.20 | XPRINT                                                                                                             | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.21 | PSPRINT                                                                                                            | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.22 | All_UPDATE                                                                                                         | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.23 | FBDB                                                                                                               | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.24 | SCHEDB                                                                                                             | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

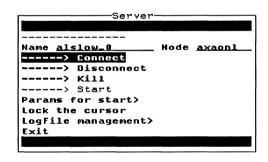

| 5.25 | SERV 3                                                                                                             | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Per  | manent Tasks on the FIC 3                                                                                          | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6.1  | XSETUP                                                                                                             | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.2  |                                                                                                                    | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.3  |                                                                                                                    | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.4  | X1PROD                                                                                                             | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.5  | X1FORM                                                                                                             | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.6  | X1WTCH                                                                                                             | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.7  | XCBCHAIN                                                                                                           | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Util | lities on the FIC 4                                                                                                | <b>2</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7.1  | DISPLAY                                                                                                            | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.2  | RTEST                                                                                                              | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | What to do after a Power Cut                                                                                       | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.3  | what to do after a rower Out                                                                                       | ı                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | uble Shooting 4                                                                                                    | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Tro  | uble Shooting    4      General hints    4                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 5.20<br>5.21<br>5.22<br>5.23<br>5.24<br>5.25<br>Per<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>Uti<br>7.1 | 5.20 XPRINT       3         5.21 PSPRINT       3         5.22 All_UPDATE       3         5.23 FBDB       3         5.24 SCHEDB       3         5.25 SERV       3         Permanent Tasks on the FIC         6.1 XSETUP       3         6.2 XRODBA       3         6.3 XHWTEST       3         6.4 X1PROD       3         6.5 X1FORM       3         6.6 X1WTCH       3         6.7 XCBCHAIN       4         Utilities on the FIC       4         7.1 DISPLAY       4 |

|              |     | 8.2.2   | Using RTEST                                  | 47         |

|--------------|-----|---------|----------------------------------------------|------------|

|              | 8.3 | Fastbu  | as Errors                                    | 47         |

|              |     | 8.3.1   | Fastbus not operational                      | 47         |

|              |     | 8.3.2   | XHWTEST                                      | 48         |

|              |     | 8.3.3   | High Voltage                                 | <b>4</b> 9 |

|              | 8.4 | Missin  | g or Junk Trigger                            | 49         |

|              |     | 8.4.1   | Errors in the Trigger Verification           | 49         |

|              |     | 8.4.2   | Timeout or Maximum Rate Exceeded             | 50         |

|              |     | 8.4.3   | Inefficiencies                               | 50         |

|              | 8.5 | Where   | e to Get Information if Something Went Wrong | 51         |

|              | 8.6 | OS9 fo  | or Pedestrians                               | 52         |

|              | 8.7 | Spare   | Modules                                      | 52         |

| 9            | Mis | cellane | eous                                         | 53         |

|              | 9.1 | Teleph  | none Numbers                                 | 53         |

|              | 9.2 | Useful  | Manuals                                      | 53         |

|              | 9.3 | Trigger | r Banks                                      | 53         |

| $\mathbf{A}$ | The | Direc   | tory Structure on the FIC                    | 54         |

| В            | The | Direc   | tory Structure on the VAX                    | 55         |

| $\mathbf{C}$ | The | X1 G    | lobal Section                                | 57         |

|              |     |         |                                              |            |

| D            | SOF | R Bank  |                                              | <b>58</b>  |

|              | D.1 | X1CB    |                                              | 58         |

|              | D.2 | X1DA    |                                              | 5,8        |

|              | D.3 | X1TH    |                                              | 59         |

|              | D.4 | X1TT    |                                              | 60         |

|              | D.5 | XTBN    | T                                            | 61         |

|              | D.6 | XTMS    | 3                                            | 62         |

|              | D.7 | XTTL    |                                              | 62         |

| $\mathbf{E}$ | Readout Banks              | <b>64</b> |

|--------------|----------------------------|-----------|

|              | E.1 X1DI                   | 64        |

|              | E.2 X1ER                   | 64        |

|              | E.3 X1HI                   | 65        |

|              | E.4 X1RG                   | 65        |

|              | E.5 X1TD                   | 66        |

| $\mathbf{F}$ | EOR Banks                  | 67        |

|              | F.1 X1SM                   | 67        |

|              | F.2 X1SV                   | 67        |

| $\mathbf{G}$ | XTTL                       | 68        |

|              | G.1 Signal Names           | 68        |

|              | G.2 XTTL Rules             | 68        |

| Н            | Xlv1_X1DAQ.hlp             | 70        |

| Ι            | Xlv1_X1MON.hlp             | 73        |

| J            | Xlv1_X1VER.hlp             | 75        |

| K            | Xlv1_X1ANL.hlp             | 77        |

| L            | Help for Level1 Histograms | 79        |

# Chapter 1

# DAQ in a Nutshell

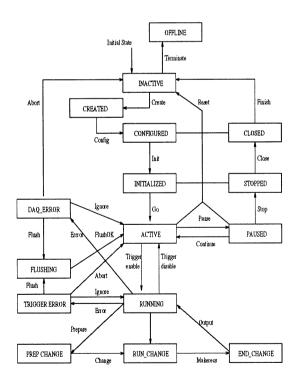

## 1.1 The Finite State Machine

The ALEPH DAQ with all its different subdetectors and subdetector tasks ( $\approx 350$ ) is a highly complex system which needs much effort to be handled during data taking. To control the status of each task, one has adopted a "Finite State Machine" (FSM) protocol (see figure 1.1) controlled by the DAQ Run Controller. The different states

Figure 1.1: The Finite State Machine Diagram

(boxes in figure 1.1) of the FSM reflect at every instant the state of the whole DAQ

system. Transitions between different states are only allowed along predefined paths (arrows in figure 1.1). The interface which translates the shift operator commands and which steers the readout system is called the DAQ Run Controller. The DAQ Run Controller creates the Subdetector Run Controllers on the VAX, and a control task on the readout processors (FICs). The Level1 Run Controller is called X1DAQ (X1SUPT in the mainstream), the Level1 control task on the FIC is called VDAQ\_CONT. The control task finally creates, depending on the Run Contol Table, the producer, consumer and reformatter tasks required on the particular FIC. Commands given by the operator to the DAQ Run Controller instruct the program to bring all subsidiary tasks into a certain state. This is called a transition. When all subtasks have reached successfully the desired state, the DAQ Run Controller itself executes this transition and the FSM reaches the next state.

## 1.2 Starting a Run

Lets have a closer look on what is happening during the start of a run with special emphasis on the Level1 trigger: Starting a run is under the control of the DAQ Run Controller. It gives the command to all subdetector Run Controllers to change their state in the FSM diagram. In the first step, the global data base of the trigger, defining the parameters of the system, is prepared and downloaded into the X1 Global Section (see appendix C). From here the DAQ Run Controller selects the trigger type (e.g. CALLRUN, TEST\_RUN, RUN\_DFLT ...) and Level3 receives the thresholds and calibration constants. How this data base is managed and how you can change the settings of the trigger is described in more detail in section 3. Then all data modules necessary on the FIC have to be prepared and sent down to the FIC. Now the system is set up, and some simple tests are performed and the start of run record (SOR), containing and archiving all information of the trigger setting of this specific run, is written. When everything was successful, the trigger has nothing left to do before going into the state ACTIVE.

## 1.3 The Readout

Each bunch crossing starts a trigger cycle unless the detector is busy. The trigger signals are distributed by the Main Trigger Supervisor (MTS) via the Fan In/Out (FIO) tree. Each readout processor in ALEPH has an associated trigger signal receiver (TSR) which sends SD specific signals to its electronics and handles the trigger protocol with the MTS. If the signals arriving from a particular SD at the Level1 hardware have forced a Level1 yes, the Level1 TSR will inform the MTS via a dedicated cable connection of its decision, and the MTS will start the Level2 cycle. In addition, the MTS receives the trigger mask on two cables from the TPR. If this cycle, too, results in a positive trigger decision, the readout will be started.

On the Level1 FIC the producer task X1PROD now starts to collect all relevant trigger

information from the hardware and writes it into the memory of the FVSBI. The next step belongs to the reformatter task X1FORM which reads from the event buffer, creates the BOS banks (see appendix E) and puts the event into the format expected by the offline software. Finally, the consumer task informs the next level of the readout tree that the event is ready. The administration of the memory is done by a Buffer Manager; it allocates the requested space, notifies the consumer task X1FORM if there is a new event, and frees the memory from events already seen by the consumer. After all pieces of an event are collected in the Main Aleph Event Builder (MAEB), they are sent to the online VAX (AXADAQ). Here the LEVEL3 trigger decides whether the event will be accepted or not; accepted events are finally written to disk.

## 1.4 The Monitoring

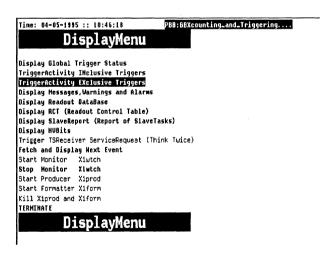

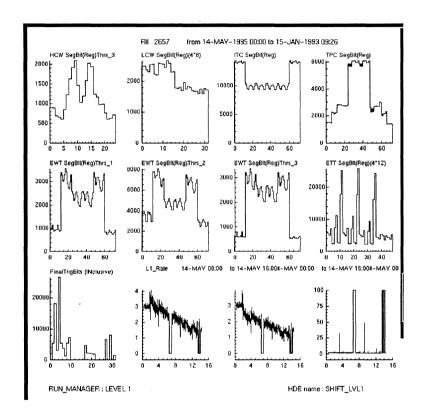

A copy of the event is sent, via the so called spy channel, to AXADAQ where it is available for monitoring tasks. Some events are shown on the event display, an important monitoring tool. Level has provided three monitoring tasks: XT1MON, XT1VER and XT1ANL, which check the data coming from the Level1 trigger. While XT1VER checks whether the trigger logic works correctly, XT1MON provides the histograms for the PRESENTER where they can be investigated (for XT1MON and XT1VER see also below, PRESENTER and event display are desribed in detail in the SD Coordinator Manual and the Data Manager Manual). XT1ANL checks the histograms of the ITC, TPC, LCW, ECW and HCW segment bits from the registers (see below). The error messages and information provided by the trigger tasks can be derived by X1ERR, which is described further down in the text. XT1MON and XT1VER also deliver some statistics and run summaries at the end of each run. The control task X1WTCH on the FIC also performs a lot of monitoring and informs the Run Controller X1SUPT about all errors. Besides that, it delivers all kind of information to the DISPLAY task which allows you to follow up the trigger activities online. For details how to use DISPLAY see below.

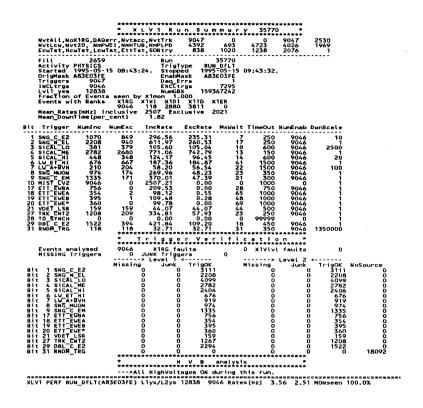

## 1.5 The Run Quality

When the disks receiving the ALEPH data are full, the events are sent to FALCON which copies them onto tape and processes the data with JULIA. The processed data (POTs) are now used for the Run Quality checks. In this step, the Level1 trigger software produces some statistics and prepares the data files necessary for the determination of the thresholds in the trigger hardware. How to derive the threshold is described in the sections X1CALB and THRFIT. The Run Quality also produces a printout with statistics, reports of problems and other information. You can get it using X1RUNQ (See section 5.17). Note, that the downgrading of a run is **NOT** done by the Run Quality but has to be done by every SD coordinator by hand with the help of the CIA tool.

# Chapter 2

## **AXAONL** and FIC

## 2.1 AXAONL

AXAONL is the name of the Aleph Online Cluster which consists of two AXP servers (AXAONL and AXADAQ) and several stations. To log on, use preferably the AXALV1 and –if you don't have your own account– the userid TRIGGER; ask for the current password in time. Several trigger tasks running on the Online Cluster are described below. It is very useful, even mandatory, to have the following line in your AXAONL login.com:

\$ @Disk\$USER:[TRIGGER]X1symbols

The following commands are then defined in X1SYMBOLS:

Cmds List Commands X1mist XLV1 Database Editor Print RunQ output for XLV1 X1rung Scan Logfiles X1supt, X1mon, X1ver X1err X1prb XLV1 General Problem Loggerr X1alert Permanent Display of X1prb messages X1calb Calculate Effective Thresholds X1xsum Print a short RunSummary/Rates ThrFit Test Linearity of Thresholds Poor man's Presenter for XLV1 Histograms X1pres X1chart Poor man's Presenter for XLV1 TimeCharts X1RGd Display X1RG bank from ONLINE data X1TDd Display X1TD bank from ONLINE data

X1trgd Print/Update Trigger-definitions Post News for communication in XLV1-group X1news Permanent Display of ALEPH status Aldisp CIA Report RunQuality problems Hedt Edit Histogram Database (X1mon, X1ver) HsaveRef Generate Reference Histos for X1mon, X1ver Pres Start the Presenter ErrLog Extract Messages sent to ErrorLogger List HelpInfo for ErrorLogger Messages ErrHelp Coord Scan/Update Coordinators Schedb Scheduler DataBase Print TEXT\_File double\_sided to LWACR\$TEXT\_132 **X**print **PSprint** Print POST\_File double\_sided to LWACR\$POST

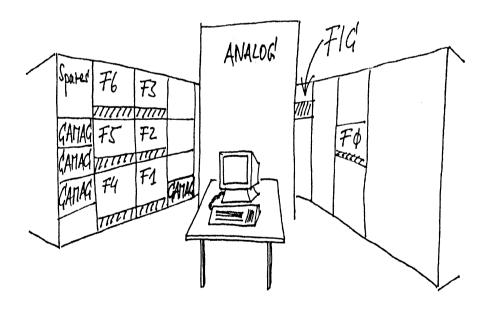

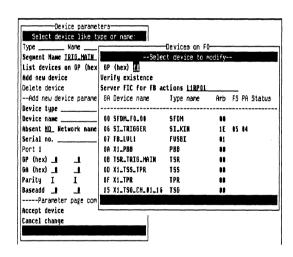

## 2.2 FIC

Since 1994 all Fastbus readout processors are replaced by VME based 68040 processors, called FIC (Fast Intelligent! Controller). Each FIC is connected to a Fastbus crate via an interface, the FVSBI. The trigger FIC is named L1RP01 and is placed at the far right hand side in the barrack C2 in the HCAL VME maincrate (figure 2.1). It is labelled 'L1RP01'. If you want to log on, you first have to connect to the Online

Figure 2.1: The C2 barrack

cluster. If you are in the control room use the Falco terminal in the trigger corner. At the prompt *Local*> type *c axalv1*, then logon as *TRIGGER*.

Now type telnet l1rp01 and wait for the prompt Enter username: Write level1 aleph where level1 is the username and aleph is the password. (Using the password manager instead, gives you write access to the area outside /os9/usr/level1. Be bloody careful!) This Falco terminal is normally used to monitor the trigger via the DISPLAY task. Type display to start it after logging on to the FIC. How to handle DISPLAY is described in section 7.1.

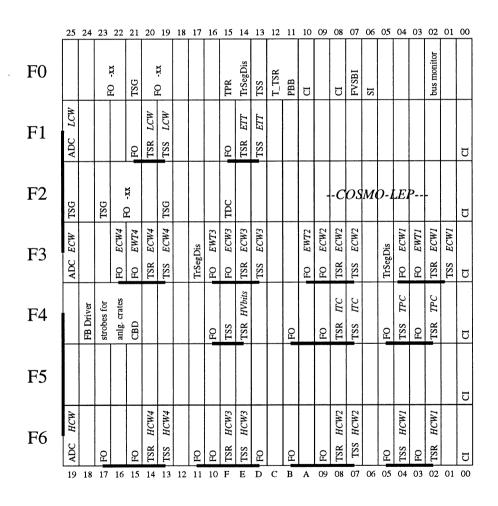

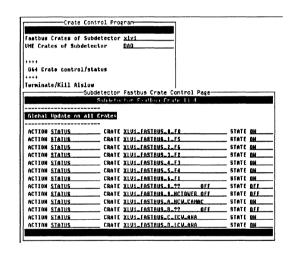

All important tasks running on the FIC are started or at least prepared at boot time when \( \langle os 9 \setminus boot \setminus l1rp01\_start \) is called automatically. \( l1rp01\_start \) calls \( \langle os 9 \setminus lvel1 \setminus vme / scripts \setminus level1\_start \) which loads all required Level1 tasks in the module directory and creates the Run Control Table from \( \langle os 9 \setminus boot \setminus data / l1rp\_table.txt \). If changes in the boot procedure are necessary, they have to be made in \( l1rp01\_start \). An overview of the modules in the Fastbus crates is given in fig 2.2. Note that the F0 crates contains two CIs (Cluster Interconnect), one for the branch F1 to F3, the second for the branch F4 to F6.

Figure 2.2: The modules in the Fastbus crates

# Chapter 3

# X1MIST: The Level1 Data Base Editor

See [Trigger.Mist]x1mist.mms for the resources.

X1MIST is a powerful tool to manage the Level1 data base. This task allows you to change <sup>1</sup> the trigger settings and to test the hardware without much effort. See also the section 5.23 on the Fastbus data base. It is absolutely necessary for you as the Level1 coordinator to be familiar with this task.

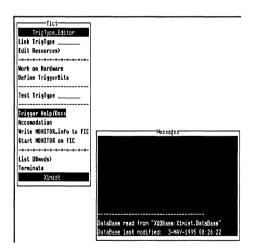

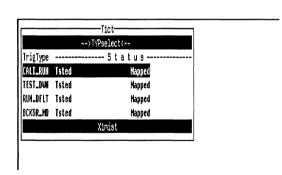

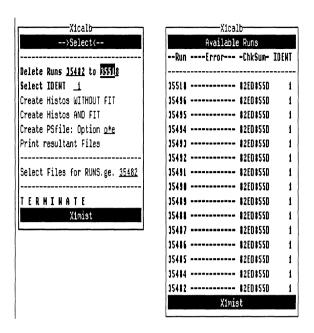

To run X1MIST type x1mist. It may take a while until you can take any action in the UPI menu which should appear on your screen (figure 3.1).

Figure 3.1: X1MIST Main Menu

If a highlighted line is visible, you can start. Use the cursor keys to move up and down in the menu. Commands which can be executed are indicated in bold letters. Place

<sup>&</sup>lt;sup>1</sup>X1MIST may crash when writing to the DB. This may be due to some unknown BOS timing (BOS checks the time left of a process). Logout, Logout, Retry.

the cursor on the appropriate line and press the return key. Some commands require parameters (indicated by a '\_\_\_\_\_\_\_\_'). If you don't know what to fill in, hit again the return key, and the program usually will show you a list of possible choices. To go up one level press 'F12'.

## 3.0.1 Link Trigtype

Here you can compile different trigger types out of the given hardware facilities (their use is defined under Edit Resources). You have to follow some conventions which are described in trigger help/docs under the keyword Mist. As a beginner you will use this facility only to inform yourself how the Trigger is set up. To get information, follow these instructions: go up to the line link TrigType and press enter (figure 3.2). Choose e.g. RUN\_DFLT with the cursor keys. Press enter again. Now you see a long list of trigger hardware components which are linked to already defined options (figure 3.3). Choose the one on which you need information and press enter once more. Now all the necessary information about this component and how it is used in this special trigger type appears on the screen.

Figure 3.2: Trigger Type Menu

| T1ct-                                     |                              |

|-------------------------------------------|------------------------------|

| >Link Trig                                | Type<                        |

| Created: 12-JAN-1994 Mod                  |                              |

| UnMap from Global_Section                 |                              |

| Delete this Definition                    |                              |

| Cancel Changes                            |                              |

| Test/Save/Map this Definit                | ion                          |

| Suspend Linking(Save unche                | cked)                        |

|                                           |                              |

| Title> Default Iriglype fo                |                              |

| Write SOR for this TrigType               | e 1 (8=No, 1=Yes)            |

| > System                                  |                              |

| RUN_DELT X1_TPR                           | F000000F 101                 |

| ====>USF X1_TSS_TPR                       | F000000D 102<br>F4000015 104 |

| STANDARD X1_CBD<br>====>USE X1_TSR_HVBITS |                              |

| > T D C                                   | 740000E 105                  |

| SIANDARD XI_TDC_1                         | F200000F 201                 |

| > T S G                                   | F200000F 201                 |

| 0108-88U X1_TSG_CH_01_08                  | F0000015 311                 |

| DONT_USE X1_TSG_CH_09_16                  |                              |

| 1724-88U X1_TSG_CH_17_24                  |                              |

| 2532-88U X1_TSG_CH_25_32                  |                              |

| 3340-8BU X1_TSG_CH_33_40                  |                              |

| DONT_USE X1_TSG_CH_41_48                  |                              |

| 4956-8BU X1_TSG_CH_49_56                  |                              |

| DONT_USE X1_TSG_CH_57_64                  |                              |

| > P L U                                   |                              |

| STDO8-0 XI_PLUI_SECO                      | FE000008 411                 |

| STDO8-1 X1-PLU1-SEC1                      | FE000008 412                 |

| STD07-0 X1_PLU2_SECO                      | FE000007 413                 |

| STD07-1 X1_PLU2_SEC1                      | FE800007 414                 |

| STD18-0 X1_PLU3_SECO                      | FE000012 415                 |

| STD18-1 X1_PLU3_SEC1                      | FE000012 416                 |

| STD17-0 X1_PLU4_SECO                      | FE000011 417                 |

| STD17-1 X1_PLU4_SEC1                      | FE000011 418                 |

| Status: Tated                             | Mapped                       |

Figure 3.3: Hardware Components

To see all possible (defined) options, clear the line in front of the component and press enter. If you have, by accident, overwritten something, don't hesitate to use the *cancel changes* command. Note that  $save/update\ this\ Definition\ takes$  quite some time.

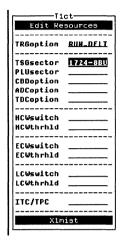

#### 3.0.2 Edit Resources

Here you can define the components out of which a trigger type is to be composed (figure 3.4). You may also receive information about a trigger type from here (figure 3.5 and 3.6). The procedure is quite similar to that described above. If you have to

Figure 3.4: The Resources Menu

Figure 3.5: The Trigger Options

Figure 3.6: The Enable Mask

change the setting of the trigger (e.g. dis- or enable a trigger, change a downscaler, the timing, the PLU setting etc.), here is the right place to do it. For a detailed description how to perform the most common changes, see below. If you have, by accident, overwritten something, don't hesitate to use the *cancel changes* command.

#### 3.0.3 Work on Hardware

Here one has the possibility to check the trigger hardware (figure 3.7).

#### You shouldn't do this during data taking!

(In fact you will get a warning if the DAQ is running.) To perform tests on a particular module, place the cursor on the corresponding line and hit enter. If the module has been identified, a menu will be displayed, giving you access to all the internal registers and functions. Another, though less comfortable, way to play around with the hardware is at your disposal by running the task RTEST on the FIC.

#### Note:

Since X1MIST receives the information about the hardware from the Fastbus data base, all modules have to be declared there (see section 5.23).

|                 |      |       | c t    |           |       |      |

|-----------------|------|-------|--------|-----------|-------|------|

|                 |      | dWare | Resour |           |       |      |

| PortName        | DevT | Sub   | MyId   | FB_addr   | FB_id | Avai |

| X1_TPR          | TPR  | SYS   | 101    | F000000F  | 68BC  |      |

| X1_TSS_TPR      | TSS  | SYS   | 102    | FOUOUUOD  | 6888  |      |

| X1_FBD          | FBD  | SYS   | 103    | F4000018  | 6841  |      |

| X1_CBD          | CBD  | SYS   | 104    | F4000015  | 68B9  |      |

| X1_TSR_HUBITS   | TSR  | SYS   | 105    | F400000E  | 68BA  |      |

| X1_PBB          | PBB  | SYS   | 106    | F000000B  | 6903  |      |

| X1_TDC_1        | TDC  | SYS   | 201    | F200000F  | 1035  |      |

| X1_TSG_CH_01_08 | TSG  | SYS   | 311    | F0000015  | 68DE  |      |

| X1_T80_CH_09_16 | TSO  | SYS   | 312    | F0000015  | 68DE  |      |

| X1_T80_CH_17_24 | TSG  | SYS   | 313    | F2000019  | 68DE  |      |

| X1_TSG_CH_25_32 | TSG  | SYS   | 314    | F2000019  | 68DE  |      |

| X1_TSG_CH_33_40 | TSG  | SYS   | 315    | F2000617  | 68DE  |      |

| X1_TSG_CH_41_48 | TSG  | SYS   | 316    | F2000017  | 68DE  |      |

| X1_T80_CH_49_56 | TSG  | SYS   | 317    | F2000013  | 68DE  |      |

| X1_T80_CH_57_64 | T86  | 848   | 318    | F2000013  | 68DE  |      |

| X1_TSG_CH_65_72 | TSG  | SYS   | 319    | FFFFFFF   | FFFF  |      |

| X1_TSG_CH_73_80 | TSG  | SYS   | 320    | FFFFFFF   | FFFF  |      |

| X1_PLU1_SEC0    | PLU  | SYS   | 411    | FE000008  | DEAD  |      |

| X1_PLU1_SEC1    | PLU  | SYS   | 412    | FE000008  | DEAD  |      |

| X1_PLU2_8EC0    | PLU  | SYS   | 413    | FE000007  | DEAD  |      |

| XI_PLU2_SEC1    | PLU  | SYS   | 414    | FE0000087 | DEAD  |      |

| X1_PLU3_SEC0    | PLU  | SYS   | 415    | FE000012  | DEAD  |      |

| X1_PLUJ_SEC1    | PLU  | SYS   | 416    | FE000012  | DEAD  |      |

| X1_PLU4_SEC0    | PLU  | SYS   | 417    | FE000011  | DEAD  |      |

| XI_PLU4_SECI    | PLU  | 878   | 418    | FE000011  | DEAD  |      |

| X1_PLU5_SECO    | PLU  | SYS   | 419    | FFFFFFF   | FFFF  |      |

| X1_PLU5_SEC1    | PLU  | SYS   | 420    | FFFFFFF   | FFFF  |      |

| X1_PLU6_SEC0    | PLU  | SYS   | 421    | FFFFFFF   | FFFF  |      |

| X1_PLU6_SEC1    | PLU  | SYS   | 422    | FFFFFFF   | FFFF  |      |

| X1_ADC_HCW      | ADC  | HCW   | 502    | F6000019  | 1045  |      |

| X1_TSR_HCW1     | TSR  | HCW   | 511    | F6000002  | 68BA  |      |

| X1_TSS_HCW1     | TSS  | HCW   | 521    | F6000004  | 68BB  |      |

Figure 3.7: Work on Hardware Menu

## 3.0.4 Define Trigger Bits

Edit XTBN gives a short description of the trigger bits (figure 3.8). You can find here the information which subdetector is used for which trigger bit. It is also used to autodisable a trigger in X1SUPT if the corresponding SD is not in the partition. In  $Edit \ XTTL$  the recipe is given how to derive the trigger decision in software (see section 4.3 and appendix G) (figure 3.9). If you want to exchange two lines enter M (move) in the right column of the line to be moved and F (following) in the right column of the line after which the new line should appear.  $Edit \ XTMS$  defines the masks used in  $Edit \ XTTL$ .

| Edit Bank XTBN                                         |      |       |      |    |

|--------------------------------------------------------|------|-------|------|----|

| No Mnemonic On Description                             | Dete | ctors | used |    |

| RUDI-ISI 1 Random Test Trigger (PIU-level)             |      |       |      |    |

| 1 SN6_C_E2 1 Sng Charged FIMag & ITC_RPZ(/IPC) EVI2    | ECAL | IIC   |      |    |

| 2 SMG_M_EL 1 Single Neutral Energy Barrel EVI3         |      |       |      |    |

| 3 SiCAL_LO 1 SiCAL UL SngArm ThresUlou 9.              | SCAL |       | =    | Ξ  |

| 4 SiCAL_HE 1 SiCAL High*Low coinc Thrs#H.L 24. *12.    | SCAL |       |      |    |

| 5 BiCAL_HI 1 SiCAL UN SngArm Thrs=UHig 36.             | SCAL |       | =    | Ξ  |

| 6 LV_ET_HI 1 LCV Total Energy (High Threshold) ETLV2   |      |       |      |    |

| 7 LV_A+BUH 1 LCV_A_high.or.B_high & Anti-Spark FTLV3   | LCAL | EIOI  |      |    |

| 8 SHG_MUON 1 Single Muon (>No TPC update() HUT1        |      |       |      |    |

| 9 SHG_C_FM 1 Single Charged FIMag (NoTPC) FWT1         |      |       |      |    |

| 18 MIST_102 1 12us after lius (12no to Busu TimeOut)   |      |       |      |    |

| I FCW_TEST 1 FCW Two Neutral Clusters lowest Thresh    |      |       |      |    |

| [2                                                     |      |       |      | Ξ  |

| 13 SiCAL_HX 1 SiCAL (UH*LV+H+H) Coincidence SubSet _ME | SCAL | =     | _    | _  |

| 14 BCAL_TRG 1 Single Arm BCAL (18 GeV in 1/4 modules)  |      |       |      |    |

| 15 FINCHESE 1 BCAL_TRB+SNB_C_EZ (TaggedTwoPhoton)      |      |       |      |    |

| 16 TAG_ZGAM 1 SNO_C_EZ+(SICAL_HI+LV_A+BUH)+ITC_BE_ZTRK |      |       |      |    |

| 17 ETT_EVBA i Total Energy ECU Barrel ETEVI            |      |       |      |    |

| is ETT_EWEA i Intal Energy ECV Endcap_A ETEW2          | ECAL | ETOT  |      |    |

| 19 FIT_FWFB 1 Intal Energy FCV Endcap_B FTFW2          | ECAL | EIOI  | =    | Ξ  |

| 20 FIT_FWF# 1 Intal Fnerow FCV EndCanA*FndCanB FTEW1   | ECAL | ETOT  |      | _  |

| 21 UDET_ISR 1 MiniMertex LaserShot (External)          |      |       |      |    |

| ZZ BM_RL_MU 1 Beam Related Muon HCW [A*[B (4DP) o. Hod |      |       |      |    |

| 23 IPC_LASR 1 IPC LaserShot (External)                 |      |       |      |    |

| 24 HUT_TEST 1 Single Meutral energy 3. Threshold       | HCAL | _     | _    | _  |

| 25 ZW_Trigg 1 SNG_C_EM. and. SNG_MUON                  | HCAL | ECAL  | IIC. | _  |

| 26 TRK_CHT1 1 IT_TrkCnt>2 Lv2=TP_TI>2                  | HC   | IPC_  |      | _  |

| 27 TRK_CNT2 1 TTC_828 1v2=Lv1.and.(TPTI+TPTO)>0        | IIC  | TPC   | LULZ | _  |

| 28 IS_SYNCH 1 On if TS_Hodule HOT synchron to beam     |      |       |      | _  |

| 29 DRI_C_F2 1 SNG_C_F2 and two ITC tracks (TPC update) |      |       | IPC  | LU |

| 16 4                                                   |      |       |      | _  |

|                                                        |      |       |      |    |

| 31 BMDM_TRG 1 DownScaled 68X-Trigger (External:PBB)    |      |       |      |    |

|              | Tiet                             |     |

|--------------|----------------------------------|-----|

|              | Edit Bank XITL                   |     |

| Lv1 Mnemonic | Operation                        | M F |

| N PR01       | PLU1 MR08 H01E                   |     |

| 1 PR02       | PROI DIO2 HIST                   |     |

| 1 PR03       |                                  |     |

| 1 PR04       | PRO3 DIO3 HIST                   |     |

| 1 PR05       | PR03 DI01 HIST                   |     |

| 1 PR06       | PLU2 HR04 H00F                   |     |

| 1 PR07       | PR06 DI01 HIST                   |     |

| 1 PR08       | PR05 OR PR07                     |     |

| 1 PR09       | PLUI MRIJ HOSI                   |     |

| 1 PRIC       | PLU1 MR14 M001                   |     |

| 1 PR23       | PLU4 MR02 M001                   |     |

| 1 PR24       | EVT2 AND ITCT HADI HIST AND PRIA |     |

| 1 PR25       | HVT3 AND ITCT MAD1 MIST          |     |

| 1 PR26       | EVT1 AND ITCI MADI MIST          |     |

| 1 PR27       | LCU AND HOUF MADI MISI           |     |

| 1 PR28       | PLU4 MR14 H003 MA01 MISI         |     |

| 1 PR29       |                                  |     |

| 1 PR38       | PR28 OR PR29                     |     |

| 1 PR31       | PR01 DI02 HIST                   |     |

| 1 PR48       | PR03 DI0Z HIST                   |     |

| 1 PR41       | PR06 DI02 MIST                   |     |

| 1 PR42       | PR40 OR PR41                     |     |

| 1 PR43       |                                  |     |

| 1 PR44       | IPCI AND EVIZ MADI MISI          |     |

| 4            |                                  |     |

| 1 RHDH_ISI   | M001                             | _   |

| 1 SHG_C_E2   | PR24                             |     |

| 1 SHG_N_EL   | <u>FVI1</u>                      |     |

| 1 Sical_LO   | PLU4 HR14 H083 H801 HISI         |     |

| 1 SICAL_ME   | PLU4 MR10 M001 MA01 MIST         |     |

| 1 Sical_HI   | PLU4 MR1Z HU03 MA01 MISI         |     |

| 1 LV_EI_HI   | ETLW MRU4 MUUB MAUJ MISI         | _   |

|              | Ximist                           |     |

Figure 3.8: Description of the Trigger Bits Figure 3.9: Software Trigger Decision

#### 3.0.5 Test TrigType

Having chosen the desired trigger type, you can now do what X1SUPT (X1DAQ) does while preparing a run: call XHWTEST, XSETUP... You will get a warning if you try so while the DAQ is active, because this might be destructive — in those cases the task will anyway refuse to follow your orders because the DAQ is not in a state allowing these tasks to take over. The results of the tasks will appear on your screen. In Test TrgType you have also the opportunity to review the trigger type and make some printouts of the actual trigger type, the corresponding timing (see figure 3.10) and PLU setting.

## 3.0.6 Trigger Help/Doc

To retrieve information, type the keyword, press enter and select List DOCuments with above KeyWord(s), then list. To leave the file which now pops up, type 'Ctrl Z'.

#### 3.0.7 Accommodation

This is the one and only place to rename the FIC: with FIC\_processor you may define a new name and also declare the names of the tasks and their timeouts. Furthermore, the printer and the X1MIST scratch file are defined with Printer, Scrfile as well as the high voltage bits under HVBits Definitions (see figure 3.11). With X1moni Options one can set thresholds for error messages due to trigger timeout or exceeding maximum

| Timing for TrigTyp | e: RUN_DFLT | ě     | s of 16-M | AY-1995 | 10:00:04 | 35  |          |   |

|--------------------|-------------|-------|-----------|---------|----------|-----|----------|---|

| TSGgroup StrtName  | SignlNam    | Delay | Length    | Jitter  | FBmodule | Lin | Lou Suse | • |

| 1724-8BU LVL1_STA  | HCW_ANA     | 2500  | 200       | 25      | F2000019 | 6   | 7 Gate   |   |

| 1724-8BU LVL1_STA  | HCW_ADC     | 2550  | 50        | 0       | F2000019 | 5   | 5 EndM   |   |

| 2532-08U LVL1_STA  | LCW_ANA     | 4400  | 200       | 25      | F2000019 | 10  | 13 Gate  |   |

| 2532-8BU LVL1_STA  | ECW_ANA     | 4400  | 200       | 25      | F2000019 | 10  | 11 Gate  |   |

| 2532-8BU LVL1_STA  | ECW_ADC     | 4650  | 50        | 0       | F2000019 | 9   | 9 EndM   |   |

| 2532-8BU LVL1_STA  | LCW_ADC     | 4650  | 50        | 0       | F2000019 | 12  | 12 EndM  |   |

| 3340-8BU LVL1_STA  | INV_LV5W    | 4800  | 2000      | 25      | F2000017 | 4   | 5 Gate   |   |

| 3340-0BU LVL1_STA  | ITC_TSR     | 4900  | 2000      | 25      | F2000017 | 6   | 7 Gate   |   |

| 1724-8BU LVL1_STA  | LCW_TSR     | 4950  | 3276750   | 25      | F2000019 | 1   | 4 Gate   |   |

| 1724-8BU LVL1_STA  | HCW_TSR     | 4950  | 3276750   | 25      | F2000019 | 1   | 2 Gate   |   |

| 1724-00U LVL1_STA  | ECW_TSR     | 4950  | 3276750   | 25      | F2000019 | 1   | 3 Gate   |   |

| 3340-8BU LVL1_STA  | PLU_STR1    | 5250  | 100       | 25      | F2000017 | 1   | 2 Gate   |   |

| 3340-8BU LVL1_STA  | PLU_STR2    | 5250  | 100       | 25      | F2000017 | 1   | 3 Gate   |   |

| 0108-88U LVL1_STA  | LVL1_EN     | 5700  | 200       | 25      | F0000015 | 1   | 2 Gate   |   |

| 0108-8BU LVL1_STA  | LVL1_STR    | 6300  | 200       | 75      | F0000015 | 1   | 4 Gate   |   |

| 2532-8BU LVL1_STA  | TDC_STOP    | 7800  | 3000      | 25      | F2000019 | 14  | 15 Gate  |   |

| 4956-8BU LVL2_STA  | TPC_TSR     | 200   | 1000      | 25      | F2000013 | 1   | 2 Gate   |   |

| 4956-8BU LVL2_STA  | TPC_PLU     | 400   | 100       | 25      | F2000013 | 3   | 4 Gate   |   |

| 0108-8BU LVL2_STA  | LVL2_EN     | 900   | 200       | 25      | F0000015 | 5   | 6 Gate   |   |

| 0108-8BU LVL2_STA  | LVL2_STR    | 1600  | 200       | 75      | F0000015 | 5   | 8 Gate   |   |

| 2532-8BU LVLX_CLR  | TSR_RES     | 0     | 200       | 0       | F2000019 | 16  | 16 Gate  |   |

Figure 3.10: The Timing Signals

rate (see figure 3.12); these thresholds are used and compared to the actual values during the run by X1WTCH running on the FIC. X1veri Options allows you to switch

| T1ct    |          |                            |    |  |  |  |  |  |  |  |

|---------|----------|----------------------------|----|--|--|--|--|--|--|--|

|         | >HVBits< |                            |    |  |  |  |  |  |  |  |

| >Set    | Use      | ed=2 for TriggerLowVoltage | ı  |  |  |  |  |  |  |  |

|         |          |                            | ı  |  |  |  |  |  |  |  |

| Bit Use |          | Explanation                | ı  |  |  |  |  |  |  |  |

|         | Ω        | ECAL EndCap_A              | ı  |  |  |  |  |  |  |  |

|         | 1        | ECAL_EndCap_B              | ı  |  |  |  |  |  |  |  |

|         | 1        | FCAL Barrel                | ı  |  |  |  |  |  |  |  |

|         | 1        | LCAL                       | ı  |  |  |  |  |  |  |  |

|         | 1        | IPC df/dX                  | ı  |  |  |  |  |  |  |  |

|         | 1        | IIC                        | ı  |  |  |  |  |  |  |  |

|         | 1        | SAHBA                      | 1  |  |  |  |  |  |  |  |

|         | 1        | HCAL EndCap_B              | ١. |  |  |  |  |  |  |  |

|         | •        | HUAL ENGUADER              | П  |  |  |  |  |  |  |  |

|         | Ť        | SICAL                      | П  |  |  |  |  |  |  |  |

|         | 1        | BCAL                       | H  |  |  |  |  |  |  |  |

|         | 1        | UDET 100%                  | ı  |  |  |  |  |  |  |  |

|         | 2        | TriggerAnalog              | Н  |  |  |  |  |  |  |  |

|         | 2        | IriggerCAMAC               | Ш  |  |  |  |  |  |  |  |

|         | î        | TPC HU.                    | Н  |  |  |  |  |  |  |  |

|         | ī        | UDET Not-Off               | ĮĮ |  |  |  |  |  |  |  |

|         | ñ        | Unused                     | Н  |  |  |  |  |  |  |  |

|         | ō        | Unused                     | 11 |  |  |  |  |  |  |  |

|         | Ā        | UnUsed                     | :  |  |  |  |  |  |  |  |

|         | <u> </u> | UnUsed                     | 1  |  |  |  |  |  |  |  |

|         | ī        | UDET 902                   | l  |  |  |  |  |  |  |  |

|         | ī        | IO-sunchronize             | ı  |  |  |  |  |  |  |  |

|         | <u> </u> | LepBeam_Pickup             | ı  |  |  |  |  |  |  |  |

|         | <u> </u> | UnUsed                     | ı  |  |  |  |  |  |  |  |

|         | •        | UnUsed                     | ı  |  |  |  |  |  |  |  |

|         | <u> </u> | UnUsed                     | ı  |  |  |  |  |  |  |  |

|         | <u> </u> | Unlised                    | 1  |  |  |  |  |  |  |  |

| 28      | O        | UnUsed                     | 1  |  |  |  |  |  |  |  |

| 29      | Ω        | UnUsed                     | ı  |  |  |  |  |  |  |  |

| 30      | .Q.      | UnUsed                     | ı  |  |  |  |  |  |  |  |

|         |          | X1mist ->                  | ı  |  |  |  |  |  |  |  |

|         |          |                            | 1  |  |  |  |  |  |  |  |

| Tict      |                |                    |               |  |  |  |  |  |

|-----------|----------------|--------------------|---------------|--|--|--|--|--|

|           | >TRGwat        | tchdog<            |               |  |  |  |  |  |

|           | all Rates by   |                    |               |  |  |  |  |  |

| ===>Scale | all TimeOuts   | by <u>100</u> /100 |               |  |  |  |  |  |

| 1         |                |                    |               |  |  |  |  |  |

|           | TimeOut[s] Mx] |                    |               |  |  |  |  |  |

| RNDM_TST  | 2000           | 20000              | 20000         |  |  |  |  |  |

| SNG_C_E2  | 250            | _6000              | 6000          |  |  |  |  |  |

| SNG_N_EL  | 250            | 6000               | 6000          |  |  |  |  |  |

| SiCAL_LO  | 600            | 18000              | 18000         |  |  |  |  |  |

| SICAL_HE  | 150            | 12000              | 12000         |  |  |  |  |  |

| SICAL_HI  | 600            | 18000              | 18000         |  |  |  |  |  |

| LW_ET_HI  | _1500          | 3000               | 3000          |  |  |  |  |  |

| LW_A+BVH  | _1500          | 3000               | 3000          |  |  |  |  |  |

| SNG-MUON  | 350            | _3000              | 3000          |  |  |  |  |  |

| SNG_C_EM  | 300            | 3000               | _3000         |  |  |  |  |  |

| MIST_LV2  | _1000          | 30000              | 0             |  |  |  |  |  |

| ECW_TEST  | 99999          | 99999              | 99999         |  |  |  |  |  |

|           | _2000          | 3                  | 3             |  |  |  |  |  |

| SiCAL_MX  | _2000          | 12000              | 0             |  |  |  |  |  |

| BCAL_TRO  | _1000          | 99999              | 300           |  |  |  |  |  |

| FINCHtst  | _2000          | 500                | 300           |  |  |  |  |  |

| TAG_2GAM  | _1000          | _2000              | _1000         |  |  |  |  |  |

| ETT_EWBA  | 750            | 6000               | _3000         |  |  |  |  |  |

| ETT_EWEA  | 1000           | 6000               | _6000         |  |  |  |  |  |

| ETT_EVEB  | _1000          | _6000              | <u>_60.00</u> |  |  |  |  |  |

| ETT_EWE*  | _1000          | 6000               | _6000         |  |  |  |  |  |

| VDET_LSR  | 500            | 300                | 300           |  |  |  |  |  |

| BM_RL_MU  | 99999          | 20000              | 20000         |  |  |  |  |  |

| TPC_LASR  | _1000          | 500                | 500           |  |  |  |  |  |

| HWT_TEST  | 99999          | 20000              | 20000         |  |  |  |  |  |

| Z0_Trigg  | 100            | 30000              | 30000         |  |  |  |  |  |

| TRK_CNT1  | 250            | _6000              | <u>_6000</u>  |  |  |  |  |  |

| TRK_CNT2  | 250            | _6000              | <u>6000</u>   |  |  |  |  |  |

| TO_SYNCH  | 99999          | 99999              | 0             |  |  |  |  |  |

| DBL_C_E2  | 450            | 3000               | 500           |  |  |  |  |  |

|           | X1r            | nist.              | - >           |  |  |  |  |  |

Figure 3.11: The HV Bits  $\mathbf{F}$

Figure 3.12: The Timeout Thresholds

off the TDC check, usually done in X1VER. The calibration constants for the Level3 tasks are set with Calib\_Constants. Use X1supt Options to set the parameters for the calibration task X1CALB to dis- or enable the 'Autotrigger' which, if set, disables automatically all triggers whose defining detector components are switched off; this avoids unnecessary timeout warnings.

If you have changed something here, do not forget to Write MONITOR\_Info to FIC

afterwards. (This is done automatically by X1SUPT during startup, the watchdog X1WTCH on the FIC checks every five minutes for a new data module.)

#### 3.0.8 Write Monitor\_Info to FIC

see Accommodation

#### 3.0.9 Start Monitor on FIC

Usually X1SUPT takes care that the monitor task X1WTCH is running; if this is not the case and if it fails to launch the task, a warning will be sent to the error logger.

#### 3.0.10 List DBmods

Lists the time when modifications have been made. Here you can give or deny access to X1MIST: Only registered users are allowed to use X1MIST.

## 3.1 How to do What with X1MIST

There may come the time when it is necessary to change the trigger settings, so make yourself familiar with the procedures in time:

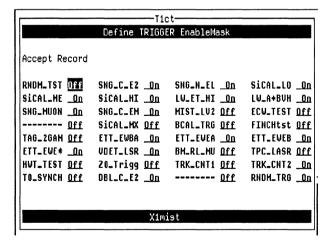

## 3.1.1 Dis- or Enable a Trigger

Level1 is using internally a selective readout. The basic information (TSR, PLU, TPR, PBB) is read on every event, while the ADCs, TDCs and TSSs are only read for some triggers. Especially the TSS are read only on random triggers.

To change the trigger mask select: Edit Resources, TRGoption, TrigType (most probably RUN\_DFLT) and Define Trigger Enable Mask (see figures 3.5 and 3.6) and go to the appropriate trigger, press the dot '.' on the numerical keypad and select ON or OFF. Choose Accept Record - Return and Save/Update this Definition. After a change of the trigger enable mask, take care that the mask is also changed in a\_eor\$src:runchk\_constants.inc. Otherwise this will produce error messages in the aleph run summary. Ask your friendly software manager.

The submasks for the selective readout of the TSSs, ADC and TDC can be changed after selecting the corresponding line *Define* ... Readout Mask from the menu shown in figure 3.5. However, the TSS should only be read out on random triggers.

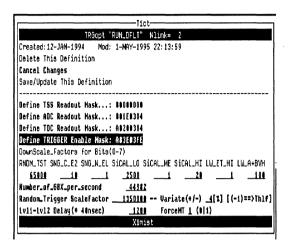

## 3.1.2 Set Downscale Factors and Random Trigger Parameters

Same as above but stop at the menu shown in figure 3.5. Go to the appropriate downscaler (above the eight downscale values you can see the corresponding trigger) and write the desired value on the line - press Return, then Save/Update this Definition. The random trigger, which is usually taken each  $2\,700\,000$  GBX (30 sec)  $-1\,350\,000$  GBX in 4-bunch mode -, may be randomized using the option variate(+/-), e.g.  $variate \pm 2\%$  will choose the random triggers uniformly from a GBX interval with mean  $2\,700\,000$  (1 350 000) and width +/- 54 000 (27 000).

To meet a request of the DAQ, a random trigger scheme where the time difference between two subsequent triggers is exponentially distributed is possible:

This feature is invoked by setting variate = -1; the mean trigger rate is given by the ratio:  $Number\_of\_GBX\_per\_second/Random\_TriggerScalefactor$  (see figure 3.5).

#### 3.1.3 Set Thresholds

When you have determined the effective thresholds with X1CALB (see section 5.14) and their (hopefully) linear dependence with the DAC counts (see section 5.15), you might want to set certain thresholds to new values. Choose the *HCW-,ECW-* or *LCWthrhld* in *Edit Resources* (figure 3.13). Choose which DAC values you want to change, overwrite

|              | THRset "TH3_DFLT" Nlink= 1             |              |  |  |  |

|--------------|----------------------------------------|--------------|--|--|--|

| Created: 12- | JAN-1994 Mod:24-MAY-1994 10:31:52      |              |  |  |  |

| Delete This  | Definition                             |              |  |  |  |

| Cancel Char  | iqes                                   |              |  |  |  |

| Save/Update  | This Definition                        |              |  |  |  |

| SetThr: Fro  | mCha _1 ToCha 10 DAC_Value0            |              |  |  |  |

|              |                                        |              |  |  |  |

|              | > ThresHold <                          | TSR_Mask-    |  |  |  |

| EndA odd     | 55 55 55 55 55 55 55 55 55 55          | 000000000000 |  |  |  |

|              | 55 55 55 55 55 55 55 55 55 55 55       |              |  |  |  |

| Barr odd     | 29 29 29 29 29 29 29 29 29 29 29 29 29 | 000000000000 |  |  |  |

| Barr even    | 29 29 29 29 29 29 29 29 29 29 29 29 29 |              |  |  |  |

|              | 55 55 55 55 55 55 55 55 55 55          | 000000000000 |  |  |  |

|              | 55 55 55 55 55 55 55 55 55 55 55 55 55 |              |  |  |  |

|              | EA EB BA TI                            |              |  |  |  |

|              | 60 60 15 15                            | 0000         |  |  |  |

|              | 60 61 15 15                            |              |  |  |  |

| 64611        |                                        |              |  |  |  |

| ECWthreshold |                                        |              |  |  |  |

Figure 3.13: Trigger Thresholds

the value (one by one or use SetThr: FromCha 1 ToCha 80 DAC\_Value 0 instead; Return, Save/Update this Definition.

Note: If it is really necessary to set bits in the TSR mask – in order not to loose in trigger efficiency because of a module malfunction –, you should know that this mask is not known to the verification (X1VER) and will lead to error messages like 'junk trigger', guaranteed.

## 3.1.4 Disable an ADC, TDC or TSS from Readout

If an ADC, TDC or TSS hardware error occurs in XHWTEST during the CONFIG step and prevents ALEPH from running, it might be necessary to disable the component from the readout (if there is not enough time to investigate and fix the problem.) Note that all other trigger components are absolutely essential for data taking and must not be disabled!

Select: Link Trigtype, Run\_Dflt and the component you want to disable (figure 3.3). Write Dont\_use in the corresponding line, press Return and select Save/Update this Definition (be patient, very slow).

Do not forget to enable the component again when the problem is fixed. Clear the line of the component and choose, after pressing 'Return', the appropriate run mode from the popped up menu.

#### 3.1.5 Change the Timing

If you have good reasons to believe that the trigger timing has to be adjusted, choose the appropriate TSG in *Edit Resources* and change the programming of the TSG by overwriting the setting (figure 3.14).

|                               | T1             | ct         |          |            |  |  |

|-------------------------------|----------------|------------|----------|------------|--|--|

| TSGdef "1                     | 724-8BU"       | Nlink=     | 3        |            |  |  |

| Created: 12-JAN-1994          | Mod:2          | 0-APR-1995 | 11:30:40 |            |  |  |

| Delete This Definiti          | on             |            |          |            |  |  |

| Cancel Changes                |                |            |          |            |  |  |

| Check/Save This Defi          | <u>ni</u> tion |            |          |            |  |  |

| Display TimingSequen          | ce             |            |          |            |  |  |

| Common ResetSignal??          | ISR_RES        | _ (Blank i | f None)  |            |  |  |

| Cha StrtNam GateNa            | m Cycles       | EndmNam    | Clk[ns]  | Parameter  |  |  |

|                               |                |            |          |            |  |  |

| 1 LUL1_STA                    | 97             | I_01_TSR   | 50       | 710        |  |  |

| 2 I_01_ISR HCW_ISR            | <u>65535</u>   |            | 50       | 730        |  |  |

| 3 I_01_TSR ECW_TSR            | 65535          |            | 50       | <u>730</u> |  |  |

| 4 I_01_ISR LCW_ISR            | <u>65535</u>   |            | 50       | 730        |  |  |

| 5 LULI_STA                    | 63             | HCW_ADC    | 50       | 710        |  |  |

| 6 LULI_STA                    | 60             | I_01_HCW   | 50       | 710        |  |  |

| 7 I_01_HCW HCW_ANA            | 4              |            | 50       | 735        |  |  |

| 8                             | 1              |            | 50       | 1020       |  |  |

| Valid StrtNam are: I and      |                |            |          |            |  |  |

| BX LVL1_STA LVL2_STA LVLX_CLR |                |            |          |            |  |  |

| All INTERN                    | AL signa       | ls must st | art "I_" |            |  |  |

| <u> </u>                      |                |            |          |            |  |  |

Figure 3.14: The TSG 1724-8BU Signals

This example shows the "daisy chain" of some signals:

The starting signal is LVL1\_STA (issued by the PBB/TSR), its endmarker is generated after 97 clock cycles (each clock cycle lasts 50 ns). This endmarker is used as an

internal signal named  $I\_01\_TSR$  which produces the gates  $HCW\_TSR$ ,  $ECW\_TSR$  and  $LCW\_TSR$  each at a length of 65535 cycles. — This large number is necessary in order to hold the signals on the TSR during the level1 and level2 cycle. Note that this TSG receives a hard reset:  $TSR\_RES$  (see the line:  $Common\ ResetSignal$ ??) —

In addition, the LVL1\_STA signal generates after 63 cycles the endmarker HCW\_ADC which is used to gate (length: 1 cycle) the HCW ADC. Finally, after 60 cycles the gate (length: 4 cycles) for the HCW analog crate is produced via the internal signal I\_01\_HCW.

Choosing Display TimingSequence from the menu displays the signals, their delays, lengths and jitter (figure 3.15). Note that the switching to the internal signals I....

| T1ct                |          |      |  |       |         |        |

|---------------------|----------|------|--|-------|---------|--------|

| TSGsignals expanded |          |      |  |       |         |        |

| StrtName            | Sign1Ham | Suse |  | Delay | Length  | Jitter |

| LVL1_STA            | HCW_ANA  | Gate |  | 2500  | 200     | 25     |

| LVL1_STA            | HCW_ADC  | EndM |  | 2550  | 50      | 0      |

| LVL1_STA            | LCW_TSR  | Gate |  | 4950  | 3276750 | 25     |

| LVL1_STA            | HCW_TSR  | Gate |  | 4950  | 3276750 | 25     |

| LVL1_STA            | ECW_TSR  | Gate |  | 4950  | 3276750 | 25     |

|                     |          |      |  |       |         |        |

|                     |          |      |  |       | ,       |        |

|                     |          |      |  |       |         |        |

|                     |          |      |  |       |         |        |

|                     |          |      |  |       |         |        |

|                     |          |      |  |       |         |        |

|                     |          |      |  |       |         |        |

|                     |          |      |  |       |         |        |

| X1mist              |          |      |  |       |         |        |

|                     |          |      |  |       |         |        |

Figure 3.15: The Timing Sequence

takes 2 cycles.

The most common case is to change the delay of signal A by changing the number of cycles of the signal whose endmarker starts A. Take care that no other signals are affected. You must not use different clock periods within a group of eight channels! A printout of the whole trigger timing can be made in *Test Trigtype*. The main timing signals are measured with a TDC and checked by X1VER. You may also survey these TDC values online with X1TDD (see below).

## 3.1.6 Change the Trigger Logic

If you want to build a new or change an old trigger: Do the neccessary cabling in C2, then choose the affected PLUs in *Edit Resources* and do the programming (then *Compile* and *Save/Update this Definition*) (figure 3.16). Valid output signals (see

Figure 3.16: PLU Setting

column Output in figure 3.16) are:  $TRIG\_xx$  or an internal signal  $I\_...$  or NC for "not connected". The internal signals may cross the boundaries of a single sector e.g. the output signal 'I\_SGCE2A' (see figure 3.16) is defined in sector STD07-1 but it is used in a different sector. After a change it is wise to check with  $Test\ TrigType$  whether the whole set of definitions is consistent. **Note:**

Some PLUs are strobed (*LV1STROBE*, *LV2STROBE*), i.e. their input is looked at (and the output is evaluated) when the strobe signal is present; their hardware switch must be on "cnt" (continuous). The others are operated on the overlap ("ovp") mode: their input is looked at continuously. The corresponding hardware switch and the mode parameter must be on "ovp". The *mode* parameter in the PLU setting menu (figure 3.16) has no effect, it is there as a reminder.

Maybe you have to change the bank XTTL (for verification) and XTBN. It may also be wise to adjust the setting of the maximum rate and timeout in X1MONI options under ACCOMODATION. A description how to change XTTL can be found in appendix G.

#### Note:

The run has to be started from INACTIVE (execute RESET, PREPARE) to load the new setting into the global section. Write down in the Shift and Trigger logbooks which runs are affected by your changes and add a comment in X1PRB, where all your changes to the X1MIST data base are logged automatically.

# Chapter 4

# Permanent Tasks on the VAX

## 4.1 X1DAQ

See [Trigger.Mist]x1daq.mms for the resources.

X1DAQ runs as the Run Controller X1SUPT in the DAQ during data taking. It performs the transitions between the states of the FSM tree, reports errors and allows to change certain settings of the trigger also from the DAQ console (SABOTAGE option in the X1SUPT menu). Furthermore, X1DAQ writes the Start Of Run Record (SOR, see appendix D) and prepares a special SOR for X1VER and X1MON. Its error messages and explanation can be found in [trigger.doc]xlv1\_x1daq.hlp or can be extracted by ERRHELP (see also appendix H). The logfile is written to a\_s\$log:xt1supt\_0.log.

## 4.2 X1MON

See [Trigger.Ver]x1mon.mms for the resources.

X1MON (called XT1MON in the mainstream) monitors the running of the Level1 trigger and reports all the faults and changes of the system, e.g. it monitors the trigger mask, the low voltages of the trigger crates, the trigger rates etc. Last but not least it provides the histograms for the presenter. Its error messages and explanation can be found in [trigger.ver]xlv1\_x1mon.hlp or can be extracted by ERRHELP. The error messages of X1MON can be found in appendix I, the logfile is written to a\_s\$log:xt1mon\_0.log. The helpfile for the presenter histograms on the Level1 shiftpage is placed in [trigger.doc]xt1mon\_0.hlp and a\_pres\$help:xt1mon\_0.hlp (see appendix I).

#### 4.3 X1VER

See [Trigger.Ver]x1ver.mms for the resources.

The verification task X1VER (XT1VER in the mainstream) serves the monitoring of the trigger, too. Its main purpose is to check whether the trigger logic is working correctly. The logic is simulated in software using the XTTL bank in the start of run record (see appendices D.7 and G and figure 3.9). The result is compared with the hardware decision. X1VER's error messages and explanation can be found in [trigger.doc]xlv1\_x1ver.hlp. The logfile of X1VER is written to a\_s\$log:xt1ver\_0.log.

## 4.4 X1ANL

See [Trigger.Ver]x1anl.mms for the resources.

The task X1ANL (XT1ANL in the mainstream) looks at the histograms produced by X1MON for the ITC, TPC, LCW, ECW and HCW segment bits from the registers (TSRs). It looks for large deviations from the mean value, asymmetries in the distributions and other unpleasant features and reports them to ERRLOG and to X1PRB. The logfile is written to a\_s\$log:xt1anl\_0.log.

## 4.5 X1WTCH

See [Trigger.doc]x1wtch.mms for the resources.

This permanent task performs an automatic logging of the LEP and run status and writes the information to the problem logger under the tag X1WATCH (see section 5.1). In addition X1WTCH cleans the directory [Trigger.Eordata]. All automatic routine checks should be added into this task. Note: There exists also a 'X1WTCH' task running on the FIC (see section 6.6) which, however, has nothing to do with this one, running on the VAX.

## 4.6 Update Error Messages

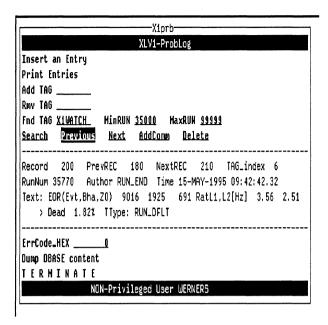

If you want to change or update the error helpfiles of X1MON, X1VER, X1DAQ you first have to edit the appropriate file ([trigger.doc]xlv1\_\*\*\*.hlp). Now copy the new version on a\_err\$dat:x1\*\*\*.hlp (\*\*\* stands for MON,VER or DAQ) with: mms/d=[Trigger.doc]x1help or @[Trigger]all\_update.