# The Front-End Electronics for LHCb calorimeters

C.Beigbeder, R.Bernier, D.Breton, T.Cacéres, O.Callot, P.Cros, B.Delcourt, A.Hrisoho, B.Jeanmarie, J.Lefrancois, V.Tocut, K.Truong, I.Videau

Laboratoire de l'Accélérateur Linéaire BP 34 – 91898 Orsay Cedex - France

#### 1. ABSTRACT

The electronics for the electromagnetic andhadronic calorimeters of LHCb is under design. The 32 channel-9U front-end board offers the complete front-end and readout electronics for every channel including original shaping, 12bit-40MHz ADC, digital filtering and latency for level 0 and level 1 triggers. The clipped PM input signal is integrated during 25ns, but also delayed then subtracted to itself 25ns later which allows performant pile up independence. This board also includes the first processing levels of the L0 calorimeter trigger.

A 16 channel-6U prototype board has been designed and used at CERN in test beam in 1999.

#### 2. INTRODUCTION

The electromagnetic and hadronic calorimeters currently designed for LHCb are lead-scintillator sandwiches employing the "Shashlick" technology. The output of the plastic fibers is equipped with phototubes. The readout system will have to deal with 6000 channels for the Ecal and 1500 for the Hcal.

#### 3. **REQUIREMENTS**

The main requirement for LHCb electronics is the pile-up rejection. Indeed, to ensure a satisfactory independance of successive sampling, the residue of a signal 25 nsec after the sampling time is required to be less than 1%. This implies to shape the PM signal. Shaped data has to be sampled at 40MHz on 12 bits then to undergo digital filtering for rejecting LF noise and to be transcoded within LUTs into energy over 8 bits for trigger data and 12 bits for readout data. The latter has to be buffered during the L0 latency, to be derandomized and then rebuffered for the level 1 latency. After the level 1 trigger, an extended zero suppression has to be performed before sending the formatted event to the DAQ.

There are also trigger elements sitting in the front-end crate. The first stages concern the search for local maxima inside groups of 512 channels, with a validation by the Preshower and Pad Chamber data.

#### 4. FRONT-END OVERVIEW

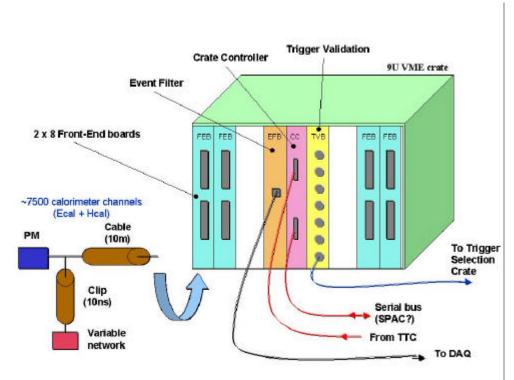

Fig 1 describes the Front-End crate and its main interconnections. The PM signals are connected to the Front-End board through 10 meters of coaxial cables. There are 16 FEBs in the crate, each receiving 32 signals. The output of these boards are connected to the custom backplane, sending signals using LVDS levels to the Event Filter. This board is in charge of performing the advanced zero suppression and the event formatting after level 1. Data is then sent to the DAQ through optical links. The Crate Controller is in charge of driving the serial link which is used for loading the hardware and of distributing the TTC signals.

From its 32 signals, and using also neighboring cells, each FEB computes, in pipeline mode, the maximum of the 32 sums over every 2x2 cell area. This maximum is sent to the Trigger Validation Board, which validates the candidate with the Preshower and the Pad Chamber (ECAL) or adds the ECAL information (HCAL), and then sends the result to the final Selection Crate over long distance links, for the final Level 0 decision.

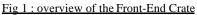

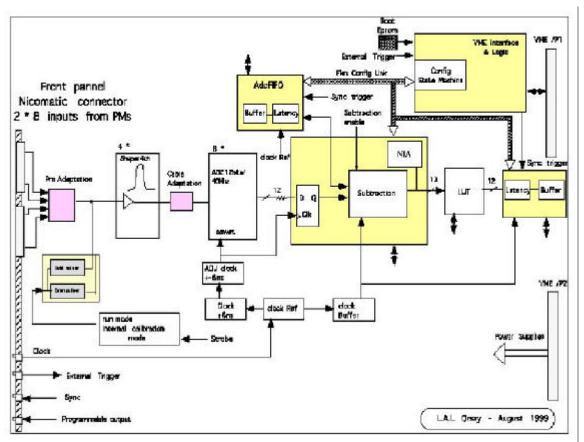

Fig 2 : block diagram of the Front-End board

### 5. THE FRONT-END BOARD

Fig 2 shows the block diagram of the 32 channel Front-End board. This is a 9U board using VME mechanics but without the VME bus. This one will be replaced by a serial bus which has still to be defined.

The main data path inside the board starts with the four 8-channel coaxial input connectors. Then signals goes into the cable compensation, a pole zero network compensating for a 10%-20nsec signal tail, before entering the analog chip. After a 12bit ADC conversion, data undergoes a subtraction of the smallest of the two previous samples. This subtraction is intended to reduce the high bandwidth noise of the integrator, and the two samples are used to decrease the probability that a signal is present in the sample which is subtracted. Then data is converted into energy within two LUTs, one for the trigger which outputs 8 bit words, the other for the readout data which outputs 12 bit words in a pseudo floating format. The latter data is then sent to the L0 latency pipeline, L0 derandomizer and L1 latency buffer. After L1 trigger, it is sent across the backplane using LVDS levels towards the Event Formatter.

At the right top of the board, trigger data is first added in squares of 4 cells while preserving the original granularity, then compared looking for the local maximum on the board. The latter is sent with its address (total of 13 bits) using LVDS levels towards the Trigger Validation Board.

Beside those data paths, some utility functions have been implemented. To correct for variable time delay in PM, one can adjust the sampling time of every ADC on the board thanks to programmable delay chips with a precision of 1 ns. A functional analog calibration has also been implemented to allow checking of the complete readout chain. This has already been useful during the test beam operations.

#### 6. THE FRONT-END ELEMENTS

The purpose of those elements is to shape the PM pulses in less than 25ns to avoid electronics pile-up. The characteristics aimed for are the following :

- At the input : the PM maximum current is 20mA over 25 ohms.

- At the output : the ADC input dynamic range is 1V under 250 ohms.

- The residue after 25ns should be smaller than 1%.

- The sampling area should cover +- 2nsec with a 1% precision.

- The RMS noise should be < 1 ADC count (250uV).</li>

- Because of the shaping and limited integration time, the fluctuation on the useful number of photoelectrons is increased compared to the case of a full integration. This increase should remain smaller than a factor 1.414.

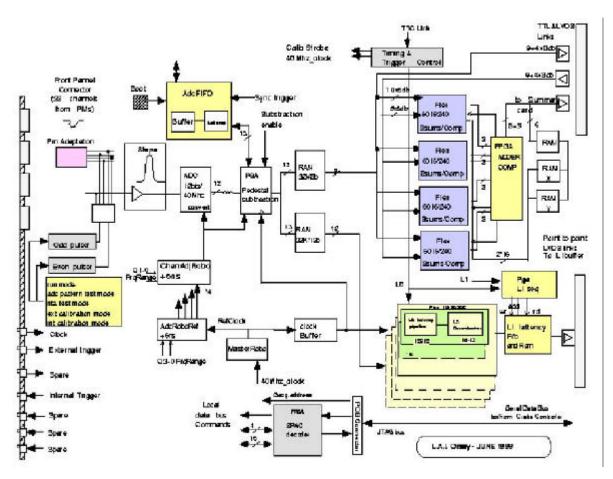

#### Fig 3 : PM output pulse

To fulfil the above requirements, two problems have to be solved. The first one concerns the PM signal. If one looks at Fig 3, which shows an idealized PM signal, the PM output current has a fast rise time but a slow decay that goes over at least the two consecutive samples at 40 MHz. It thus needs to be pulled to zero after 10ns to ensure the zero pile-up requirement. The remaining area is on the order of 60% of the original one.

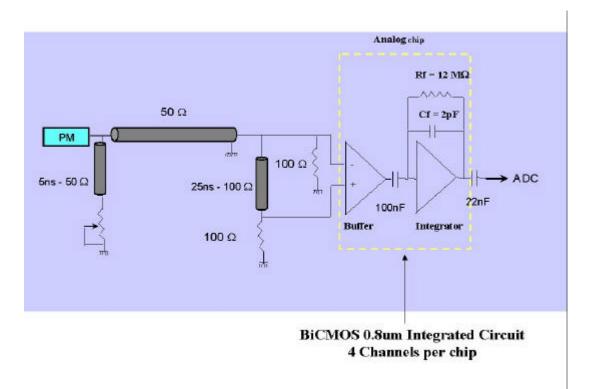

### Fig 4 : Front-End Electronics

To realize this cut on the signal, the clipping circuit on the left of Fig 4 will be used. It consists in a short 1 meter cable located at the output of the PM base. It sends part of the signal towards a variable network which will send back a inverted part of the signal. As both the source and reflected signals are negative exponentials, their superposition leads to zero, as shown on fig 5.

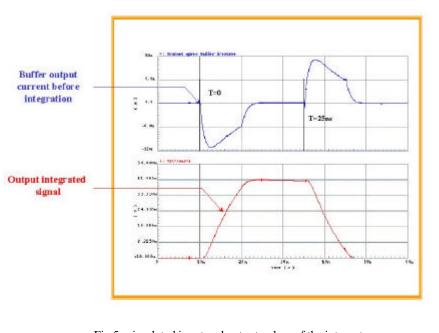

### Fig 5 : simulated input and output pulses of the integrator

Now that the input signal has been shaped, we have to measure the energy deposited in the calorimeter. The corresponding information is the area of the PM signal. The best way to measure it without deteriorating too much the statistic fluctuation is to integrate this signal in a capacitor (Cf). The difficulty then becomes to empty this capacitor. Two ways are possible :

- Use a switch mounted in parallel but this system induces a dead time when the capacitor is being emptied, what implies the use of two integrators in parallel and a multiplexor. But due to the inevitable injection of charge from the switches, pedestals are generated which can be the sources of drifts at the 0.1% level.

- Subtract in a linear way the signal to itself thanks to a specific configuration.

The latter is the chosen solution. The configuration appears in the middle of Fig 4. The input signal of the analog chip is diverted, delayed by 25ns, then subtracted to itself thanks to the differential buffer. The latter has also in charge the division of the input current to adapt it to the small value of Cf.

Between the buffer and the integrator, there is an external AC coupling that allows to separate the DC levels. The integrator has a fast risetime and offers a satisfactory plateau at the top of the signal (see bottom plot of Fig 5).

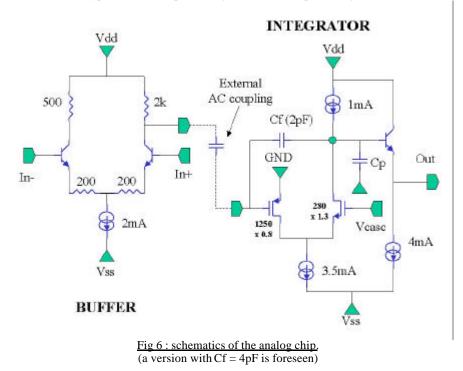

Fig 6 shows the schematics of the analog chip. The 2K resistor at the output of the buffer is used for replacing a 1mA current source that would never match exactly the half of the emitter source current and produce more noise with the same power supplies than the resistor. Obviously, the buffer provides essentially a current output as the input impedance of the integrator is small (200 ohms) compared to the 2K of the resistor.

The integrator schematics is based on a cascode amplifier. Its open loop gain is high (60dB), it's fast as there is no Miller effect on the input PMOS, and it produces very low noise. On the other hand, there is a need for an emitter follower at the output not to degrade the gain by the charge impedance. In our case, as the charge is only 350 ohms, another follower has been mounted on the board using discrete elements. The decay time of the integrator is linked to the 2K resistor which leads to a nominal value of 4us.

The 350 ohm charge is composed of 250 ohms which is the ADC input impedance and a serial 100 ohm resistor. The latter prevents the ADC saturation at 1V from affecting the integrator. The resulting effect is a division of the signal by a factor 1.4.

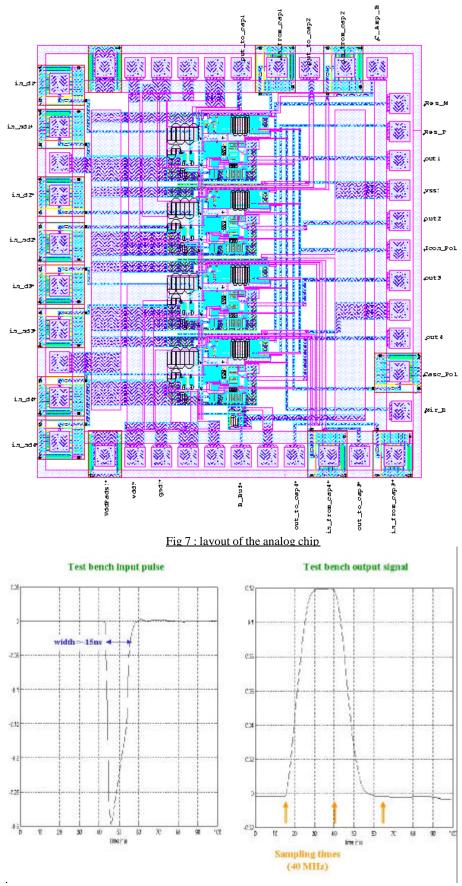

Fig 7 shows the layout of the current version of the analog chip. Up to now, three versions have been submitted in only 6 months. The main difficulty that appeared was a resistor in the gate access to the input PMOS of the integrator. This was due to a bad polysilicon design and introduced noise and instability in the chip response. This problem was fixed and the chips received in the summer of 1999 were fully operational. When mounted on test bench at LAL, the chip offered the results shown in Fig 8.

Fig 8 : real signals on test bench

On this plot (Fig 8), the input pulse derives from a generator and is clipped as the real PM signal. The output signal shows a nice flat top in concordance with the simulations. The global preliminary results from this test bench are given in Fig 9.

| Simulation Results :                         |                             | Current Test Bench Results : |                                                 |

|----------------------------------------------|-----------------------------|------------------------------|-------------------------------------------------|

| Dynamic Range :                              | 1.4V                        | <=>                          | > 1.4V                                          |

| Non Linearity :                              | 0.5%                        | <=>                          | $\leq 1\%$ over the whole dynamic range         |

| Residue after 25 ns :                        | <0.5%                       | $\langle = \rangle$          | <1% (undershoot ~3%)                            |

| RMS Noise after<br>subtraction               | 1 ADC Channel<br>(ie 250uV) | <=>                          | 1.2 ADC Channels<br>(ie 300uV)                  |

| Power Consumption                            | : 40mW / Channel            | <=>                          | 38mW / Channel                                  |

| Open-Loop Gain :                             | ~60dB                       | <=>                          | ~ <b>6</b> 0dB                                  |

| gm (Input PMOS) = 34mA / V                   |                             | gm (Input PMOS) = 18mA / V   |                                                 |

| Fall Time :                                  | 3us                         | <=>                          | 2us                                             |

| Rise Time :                                  | 1.2ns                       | <=>                          | 5ns                                             |

|                                              |                             | with a 8pi                   | F parasitic capacitance at the integrator input |

| Input Impedance :                            | 90Ω                         | <=>                          | 270Ω                                            |

| Deterioration of statistic fluctuation < 1.4 |                             | <=>                          | <1.2                                            |

### Fig 9 : first results from the test bench

These results show a good adequation between simulation and real circuit, except for the gm of the input transistor. This is due to simulation models and also explains the mismatches in the rise time and the input impedance of the integrator.

## 7. THE PROTOTYPE FRONT-END BOARD

The prototype FEB shown on Fig 10 is a 16 channel board which has been designed for the test beam of 1999. It comprises the same readout chain excepting the L1 buffer. Moreover, some extra functionalities as the spying of the raw data at the output of the ADCs have been implemented. This allows to crosscheck offline the subtracted data with their source.

Another interesting purpose of this board is the configuration state machine implemented in the VME interfaceAltera. It allows to configure all the other FPGAs on the board in an interactive way, permitting to debug the board easily (even far from home through ftp) and also to modify the functionnality of the FPGAs for test purposes.

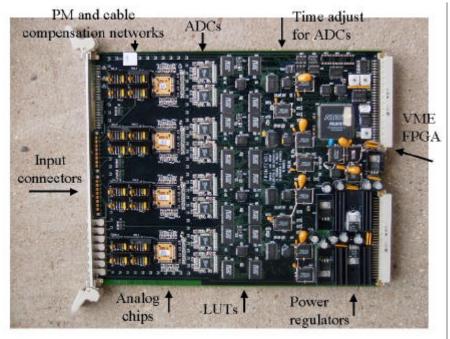

Fig 10 : prototype of the Front-End board

Fig 11 offers a picture of the board. On the left side, one can see the  $2 \times 8$  channel input connectors, followed by the PM and cable compensation networks and the delay lines. The four 4 channel analog chips are followed by half the ADCs and the LUTs. All the big FPGAs (10K50 and 6K16) are on the other side of the board, together with the other half of the ADCs.

Fig 11 : top layer of the prototype FEB

## 8. THE TEST BEAM ENVIRONMENT

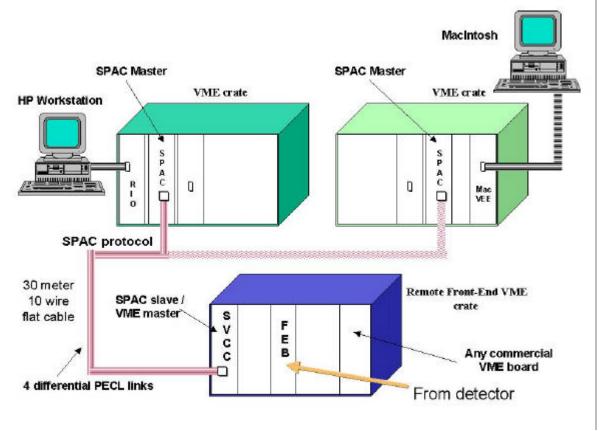

This board was installed on test beam in the setup shown in Fig 12.

One can remark here that two VME master crates can alternatively be connected to the remote electronics. This is intended for debugging and monitoring purposes. Indeed, when electronics is installed at CERN for test beam, local DAQ still needs to be debugged. The MacIntosh interactive test software, which also provides data acquisition, and the possibilities of live insertion of the SPAC bus thus allow to start the debugging phase of the hardware while permitting crosscheck of the readout data with the one read by the standard DAQ.

## 9. TEST BEAM RESULTS

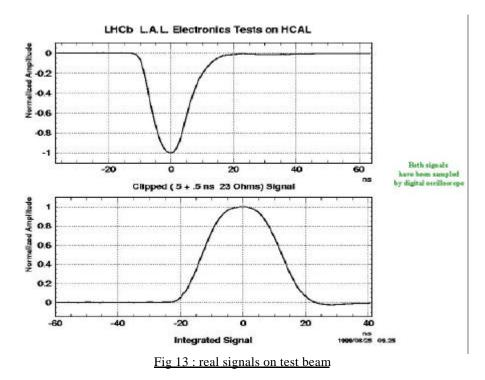

The first measurements made on test beam were related to the signal coming from the PMs. It is plotted on top of Fig 13.

One can remark that the width of the signal is larger than on test bench. This was due to an underestimate of the risetime of the PM and of the light output from the scintillator and the wavelengthshifting fiber in the test bench simulation. Nevertheless, the shape at the output of the integrator (bottom plot) looks adequate with a flat top within 1% for +-2nsec.

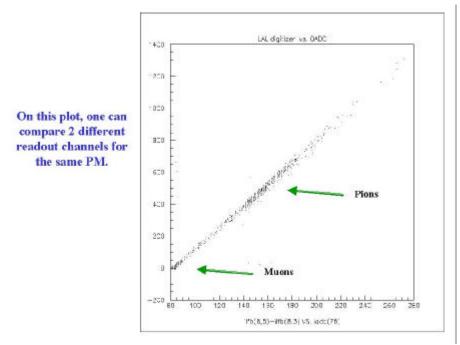

The following step was to compare the new 40MHz electronics with the CAMAC LeCroy one. Data was thus taken on the same channel through the two different paths. The comparison is plotted on Fig 14.

Fig 14 : new electronics vs LeCroy ADCs

Fluctuations from a strict correlation are caused by noise of the 40MHZ and Lecroy ADC and by the deterioration of statistical fluctuation from the fast electronics (see Fig 9).

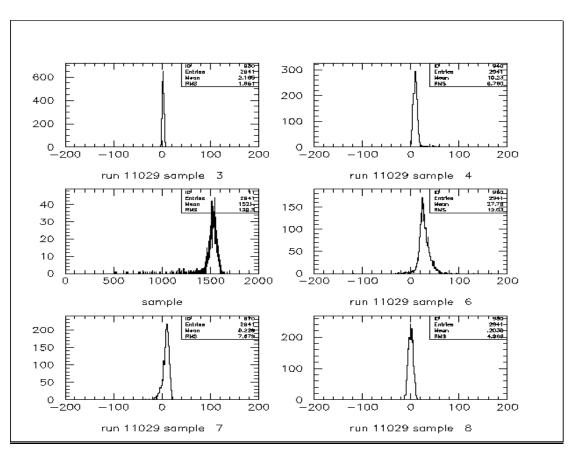

Fig 15 presents the results of an ECal run. 6 samples are plotted successively. The signal is centered on the sample 5 (third one). On the sample 3, one can observe the noise distribution. This corresponds to a RMS of 1.86 ADC count.

Fig 15 : 6 samples from an Ecal run

On the samples 6 and 7 appears the result from the subtraction of the smallest of the two previous samples. On sample 8, we're back to the baseline. The effects on samplings other than the main one are typically at or below the 1-2% level.

## 10. NEXT STEPS OF THE DEVELOPMENT

The previous measurements made on test beam prove the consistency of the electronics which has been designed. We are currently concentrating on the various noise sources to reduce the total noise on the board under 1.5 ADCC.

- The next steps of the developments for this electronics are the following :

- Concerning the Front-End Board :

- A new version of the analog chip aiming at a reduced noise

- Implementation of the trigger part of the board

- Study of the L1 buffering hardware

- Extension to a 9U/32 channel board

- Study of the fastbackplane using LVDS signals

- Study of the Event Filter (which provides advanced zero suppression and event formatting)

- Study of the Crate Controller (which includes serial access bus and TTC)

- Study of the Trigger Validation Board (which prepares the candidates for the L0 trigger Main Selection Crate)

## 11. REFERENCES

For completing the information given in this paper, one could have a fruitful look to the following notes :

- J.Christiansen, "Requirements to the L0 front-end electronics", LHCb technical note, July 30th 1999

- C.Beigbeder et al., "A Joint Proposal for the Level 0 Calorimetric Triggers", LHCb 99-017, June 7th 1999

- D.Breton et al., "SPAC : Serial Protocol for the Atlas Calorimeter ", www.lal.in2p3.fr/technique/se/spac