Thesis RAL-TH-2001-007

# Radiation Effects in Electronics for the CMS Tracking Detector

J R Fulcher

Thesis-2001-Fulcher

CERN LIBRARIES, GENEVA

July 2001

# 23/6655

CM-P00040988

#### © Council for the Central Laboratory of the Research Councils 2001

Enquiries about copyright, reproduction and requests for additional copies of this report should be addressed to:

The Central Laboratory of the Research Councils Library and Information Services Rutherford Appleton Laboratory Chilton Didcot Oxfordshire OX11 0QX

Tel: 01235 445384 Fax: 01235 446403

E-mail library@rl.ac.uk

ISSN 1362-0215

Neither the Council nor the Laboratory accept any responsibility for loss or damage arising from the use of information contained in any of their reports or in any communication about their tests or investigations.

# Radiation Effects in Electronics for the CMS Tracking Detector

Jonathan Richard Fulcher

A thesis submitted for the degree of Doctor of Philosophy of the University of London and Membership of the Diploma of Imperial College

January 2001

Imperial College London

## **Abstract**

This thesis presents a study into the CMS tracker analogue front-end amplifier readout chip (APV), which during the period of the study was fabricated in three different VLSI technologies. The early versions were fabricated in a total dose radiation hardened Harris 1.2 µm process. Later it was transferred to a DMILL 0.8 µm process and the latest version is in a 0.25 µm technology. Part of this thesis describes a test system which was designed to thoroughly test APV chips on the silicon wafer and produce a comprehensive data set for each chip to enable confident selection of good chips. The main study is on the effects that large dose radiation environments can cause in the individual parts of the chip. With the chips fabricated in different technologies it was possible to make some comparisons of the magnitude of the effects between the Harris and the 0.25µm technologies, but most of the work was aimed towards understanding the effects within the 0.25 µm technology. Single Event Upset (SEU) was the main consideration behind the experimental and simulation work. The study had two main goals: the first was to investigate how SEU would affect the operation of the CMS detector in the expected high radiation environment of the Large Hadron Collider (LHC). The second goal was to look at SEU from a more academic viewpoint, enabling a full understanding of how it is caused and what factors affect its magnitude. Simulations were performed in order to reconstruct the conditions brought about by highly ionising particles striking certain parts of the sensitive circuits, along with careful consideration of the mechanisms behind the effect such as: ionised charge collection within the semiconductor parts of the chip, how this charge deposition affects the circuit and how the effects manifest themselves within larger devices. A good set of results was collected from specially designed experiments, from which a confirmation of the theoretical effect was produced.

# Acknowledgements

During the three years which I have spent in the High Energy Physics group at Imperial College, I have received much appreciated help and guidance in all aspects of my work. I wish to thank Mark Raymond for his unrelenting support, tolerance and especially sense of humour, not to mention all his hard work building the electronics for all the experiments. I would also like to thank Geoff Hall for his guidance throughout and PPARC and Rutherford Appleton Laboratory for funding my research over the three years.

Thanks to Federico Faccio and Mika Huhtinen for their work on SEU prediction in CMS, Irving Din Doyal for his contribution to the transistor measurements, Etam Noah for his contribution to transistor and APV irradiation, charge collection simulation and work on SEGR, and also to Lih-King Lim for his contribution to the APV test data analysis.

Thanks go to Greg, Barry, Jan, Etam, Emlyn and Rob for the great atmosphere at work and occasional moments of inspiration over a coffee or down the local. I would also like to thank my best friends: Maria, Rupert and Paul for supporting me and keeping me sane during the writing of my thesis. Thanks also to everyone in the clan, you are all great friends. I would like to dedicate this thesis to my mum, dad and three sisters without any of whom this would never have been possible. Also love goes to both of my grandmothers for staying with us long enough to see me through my education.

It has been a great three years and a real pleasure to be a part of such a lively and exciting group. Finally I would like to thank Peter Dornan for allowing me to work with the group.

# **Contents**

| Abstract                                                                                                         |         |

|------------------------------------------------------------------------------------------------------------------|---------|

| Acknowledgements                                                                                                 |         |

| Contents                                                                                                         | ····· 7 |

| List of Figures                                                                                                  |         |

| List of Tables                                                                                                   |         |

| Introduction                                                                                                     |         |

| The Road to Electronics in High Energy Physics                                                                   |         |

| Chapter 1 The LHC & CMS                                                                                          |         |

| 1.1 The LHC Radiation Environment                                                                                |         |

| 1.2 The CMS Experiment                                                                                           |         |

| 1.2.1 The Tracking System                                                                                        | 28      |

| 1.2.2 The Front End System                                                                                       |         |

| 1.3 The APV readout chip                                                                                         | 30      |

| 1.4 MOSFET Transistors                                                                                           |         |

| 1.4.1 MOSFET operation                                                                                           |         |

| 1.5 Conclusions                                                                                                  |         |

|                                                                                                                  |         |

| Chapter 2 Testing The APV Chip                                                                                   |         |

| 2.1 Motivations                                                                                                  |         |

| 2.2 Development of The System                                                                                    | 44      |

| 2.3 Equipment and Test Criteria                                                                                  |         |

| 2.3.1 APV6 and APVM Equipment                                                                                    |         |

| 2.3.2 Recent Modifications                                                                                       |         |

| 2.3.4 Test Criteria                                                                                              |         |

| 2.4 Test Data Storage and Retrieval                                                                              | 52      |

| 2.4.1 Example APV6 Data Sheet                                                                                    |         |

| 2.4.2 Example APV6 Wafer Map                                                                                     |         |

| 2.4.3 Availability of data on the web                                                                            | 55      |

| 2.5 Yields                                                                                                       | 56      |

| 2.5.1 APV6 Yields                                                                                                |         |

| 2.5.2 APVM Yields                                                                                                |         |

|                                                                                                                  |         |

| 2.6 Analysis of Test Data                                                                                        |         |

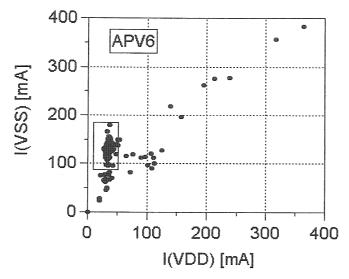

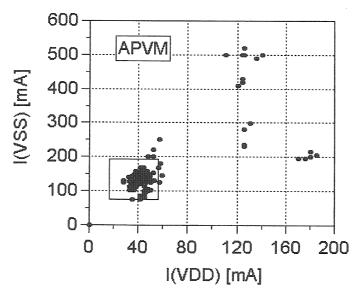

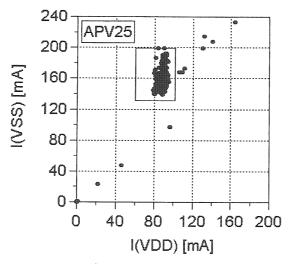

| 2.6.2 Scatter Plots in Current Space                                                                             |         |

| 2.6.3 APV6 Pipeline Noise and its Correlation with Currents                                                      | 63      |

| 2.6.4 Gain and its Correlation with Currents                                                                     |         |

| 2.6.5 Correlation Between Current and Test Failures in APV6/M 2.6.6 Uniqueness of APV25 Pedestal Characteristics |         |

|                                                                                                                  |         |

| 2.7 Conclusions                                                                                                  | 70      |

| Chapter 3 Radiation Effects on Microelectronics and the APV  | 72  |

|--------------------------------------------------------------|-----|

| 3.1 Ionizing Radiation and Energy Deposition in Silicon      | 73  |

| 3.1.1 Ionization                                             | 73  |

| 3.1.2 Bremsstrahlung                                         |     |

| 3.1.3 Rutherford Scattering                                  |     |

| 3.1.4 Inelastic nuclear interactions                         |     |

| 3.1.5 Stopping powers                                        | 74  |

| 3.2 Total dose radiation damage                              |     |

| 3.2.1 Bulk Damage                                            |     |

| 3.2.2 Ionizing radiation effects                             |     |

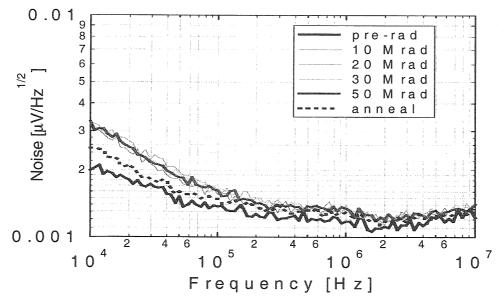

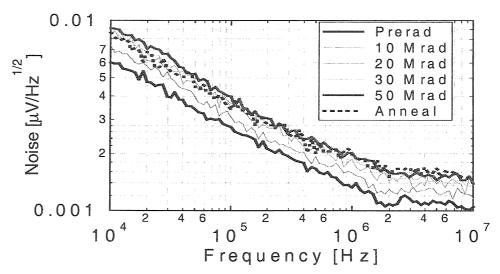

| 3.2.3 Effects on noise                                       | 81  |

| 3.3 Single Event Effects                                     |     |

| 3.3.1 Single Event Latchup                                   |     |

| 3.3.2 Single Event Gate Rupture                              |     |

| 3.3.3 Single Event Upset                                     |     |

| 3.4 Making Experimental Measurements                         |     |

| 3.4.1 Individual upset rate measurements                     |     |

| 3.4.2 Use of heavy ions to scan LET                          |     |

| 3.4.3 The shape of the cross-section curve                   | 88  |

| 3.4.4 Possible Causes of the Cross-section Curve Shape       |     |

| 3.5 Single Event Upset in the APV                            |     |

| 3.5.1 Sensitive circuits in the APV                          |     |

| 3.5.2 Simulations of SEU in APV25 circuits                   |     |

| 3.5.3 Simulating SEU in the APV25                            |     |

| 3.6 Modelling the Heavy Ion Upset Cross-Section in the APV25 | 97  |

| 3.6.1 Total Sensitive Area of APV25                          |     |

| 3.6.2 Converting to Threshold LET                            |     |

|                                                              |     |

| 3.7 Modelling the CMS Environment                            |     |

| 3.8 Conclusions                                              | 105 |

| Chapter 4 Radiation Testing Results                          | 106 |

| 4.1 Total Dose Studies of APV Test Transistors               | 106 |

| 4.1.1 Measurement of Transfer Characteristics                |     |

| 4.1.2 Noise Measurements                                     |     |

| 4.1.3 Harris Devices                                         | 108 |

| 4.1.4 0.25µm Devices                                         |     |

| 4.1.5 Harris Irradiation Results                             |     |

| 4.1.6 Results of 0.25µm Irradiations                         |     |

| 4.1.7 Comparison between Harris and 0.25µm Technologies      |     |

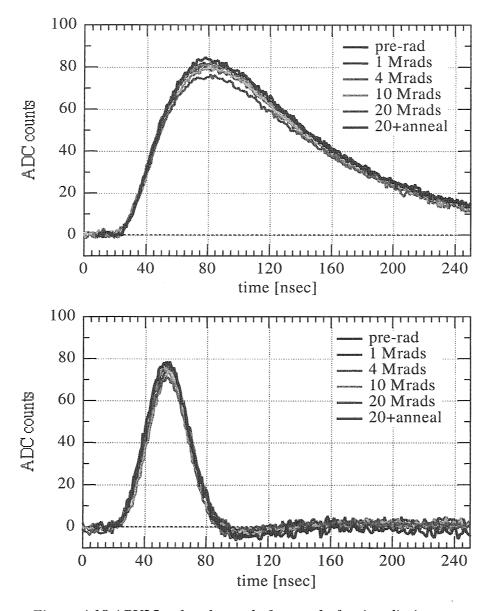

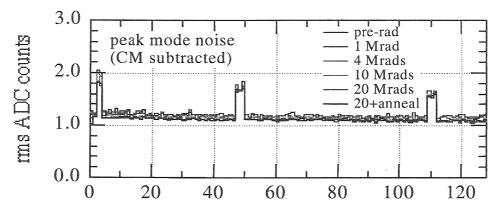

| 4.1.8 APV25 X-ray Irradiation Results                        |     |

| 4.1.9 Gate Rupture in the APV6 and APV25                     |     |

| 4.2 Single Event Upset Testing                               |     |

| 4.2.1 Hardware                                               |     |

| 4.2.2 Masking APV sections                                   |     |

| 4.2.3 Software                                               |     |

| 4.2.5 Measuring errors in the APV                            |     |

|                                                              |     |

| 4.3 APV6 SEU Results                                         |     |

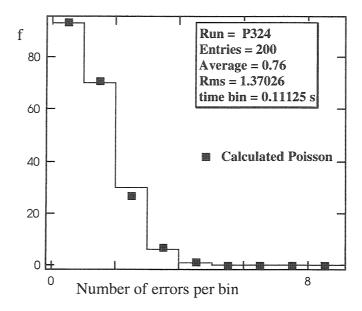

| 4.3.1 Error distribution                                     |     |

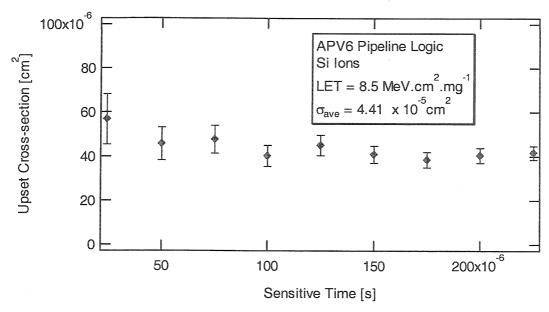

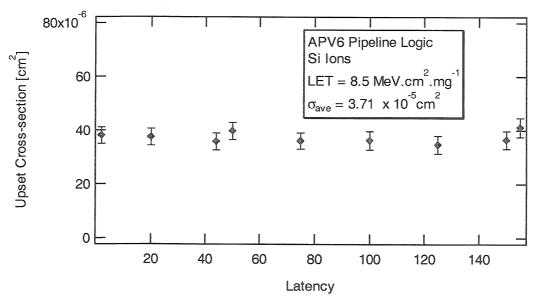

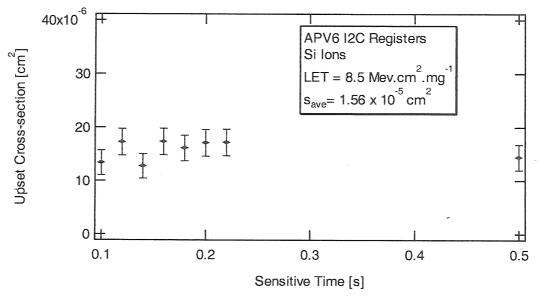

| 4.3.2 Pipeline cross-section                                 |     |

| 4.3.4 Discussion and future measurements                     | 135 |

| 4.4 APV25 SEU Cross-sections                   |     |

|------------------------------------------------|-----|

| 4.4.1 Effective LET                            | 137 |

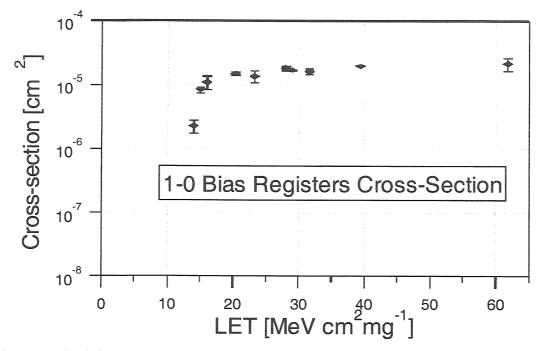

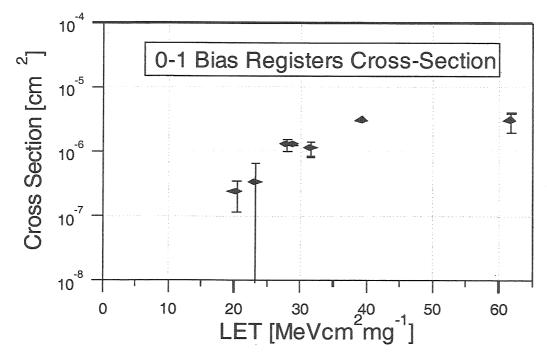

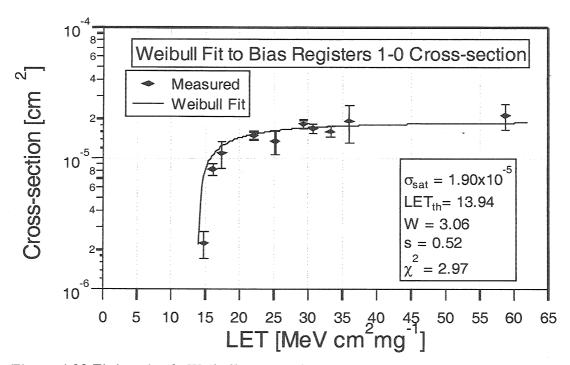

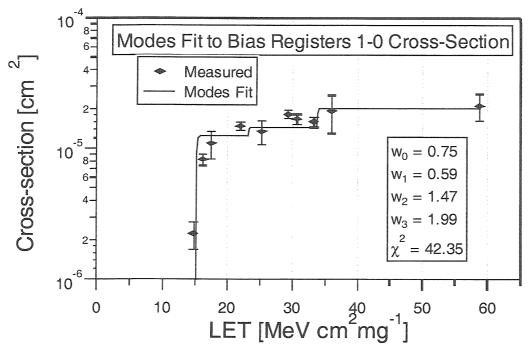

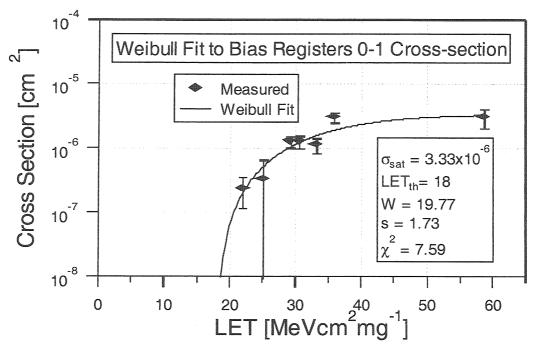

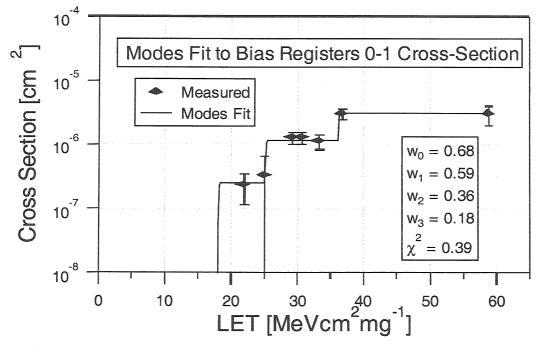

| 4.4.2 Bias Registers                           |     |

| 4.4.3 Fitting Theoretical Curves to Data       |     |

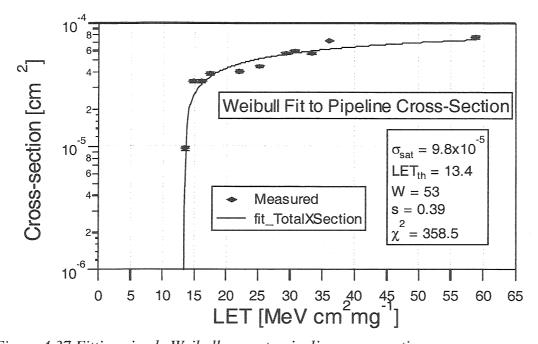

| 4.4.4 Pipeline                                 | 144 |

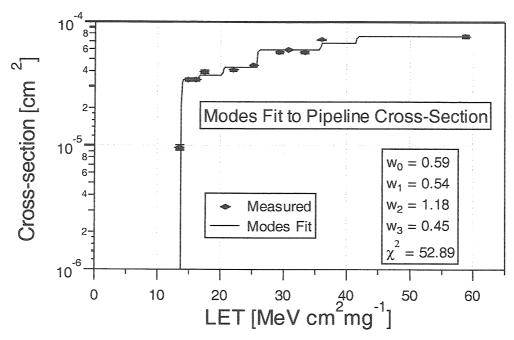

| 4.4.5 A Closer Look at the Modes               | 145 |

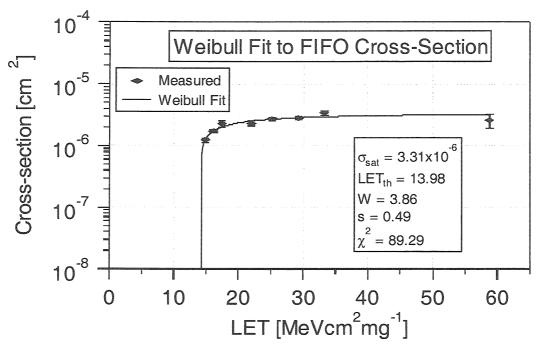

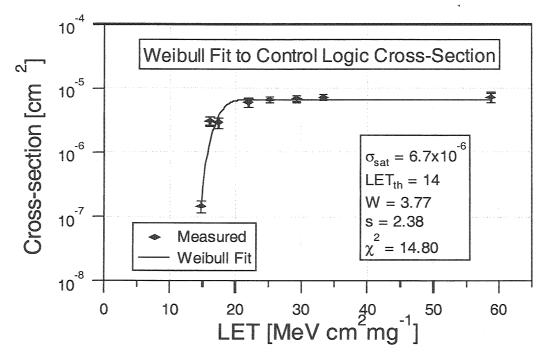

| 4.4.6 FIFO and Control Logic                   |     |

| 4.5 Upset Rate Predictions for the CMS Tracker | 149 |

| 4.6 Conclusions                                | 150 |

| Chapter 5 Summary and Conclusions              | 152 |

| 5.1 Wafer Testing                              | 152 |

| 5.2 Radiation Effects                          | 153 |

| References                                     | 155 |

# **List of Figures**

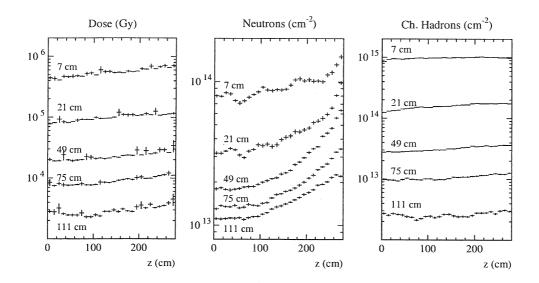

| Figure 1.1 Radiation levels at selected radii in the CMS Tracker region. All values correspond to an                 |      |

|----------------------------------------------------------------------------------------------------------------------|------|

| integrated luminosity of $5x10^5$ pb <sup>-1</sup> . The error bars indicate only the statistics of the simulations. | The  |

| neutron fluences include only the part of the spectrum above 100 keV.                                                | 26   |

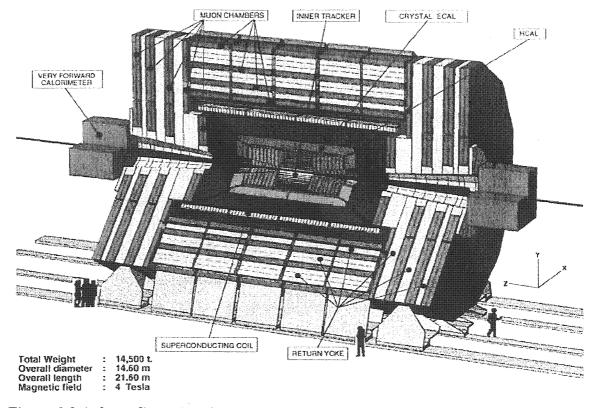

| Figure 1.2 A three-dimensional view of the CMS detector.                                                             |      |

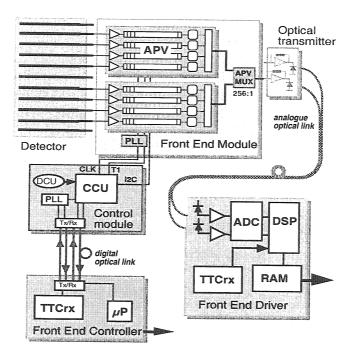

| Figure 1.3 Diagram of the front-end readout                                                                          | 29   |

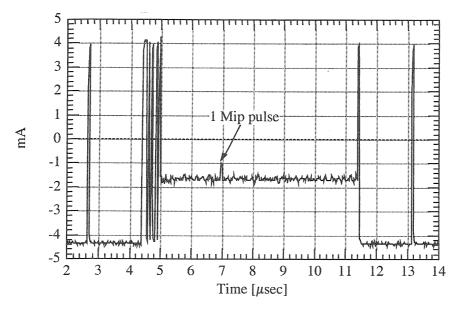

| Figure 1.4 Example data frame from APV25, a signal of 1 mip can be seen                                              |      |

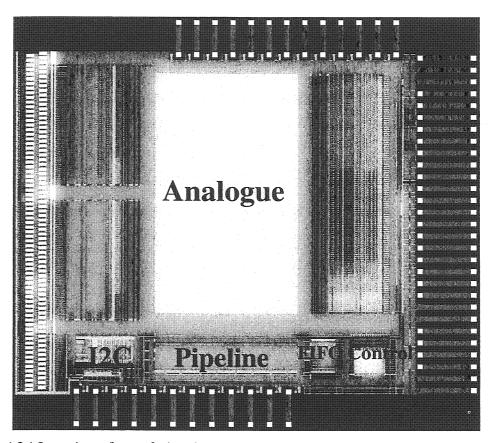

| Figure 1.5 APV25-S1 the latest version of the APV                                                                    |      |

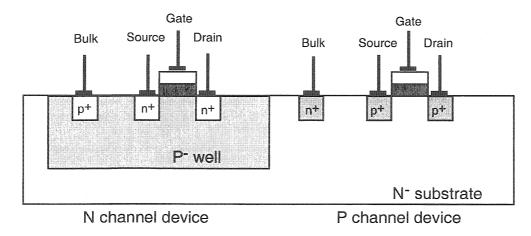

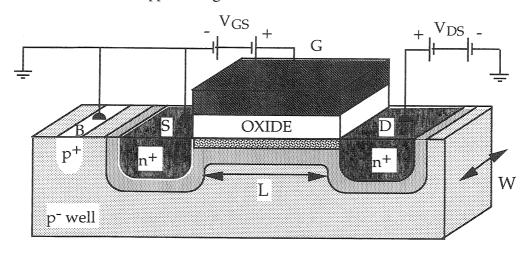

| Figure 1.6 Cross-section through an ideal NMOS and PMOS transistor.                                                  |      |

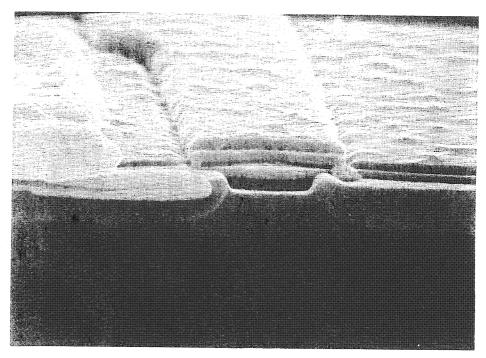

| Figure 1.7 Scanning electron microscope photograph of the cross section of an NMOS transistor                        |      |

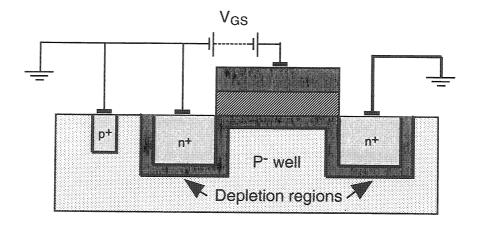

| Figure 1.8 NMOS transistor under initial bias conditions.                                                            |      |

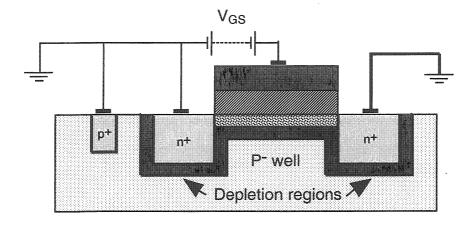

| Figure 1.9 NMOS transistor during inversion.                                                                         | 36   |

| Figure 1.10 An n-type transistor biased in strong inversion.                                                         |      |

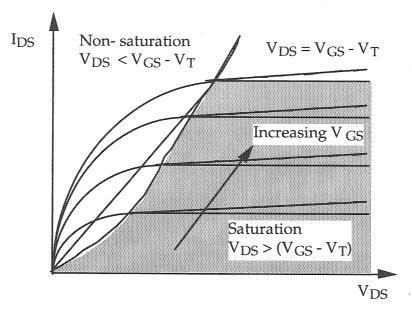

| Figure 1.11 Operation of a transistor in the saturation region. The constant plateau represents $\lambda=0$ , risi   | ing  |

| plateau represents λ>0.                                                                                              |      |

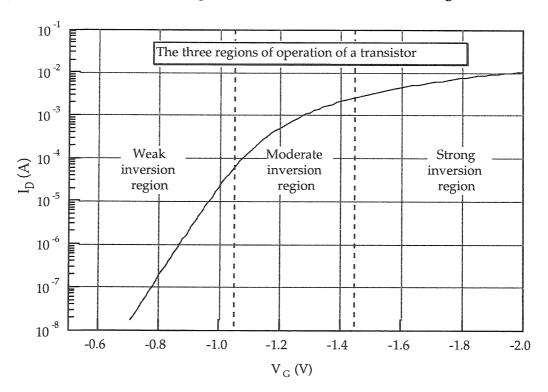

| Figure 1.12 The three regions of operation on an MOS transistor. Data is from a 2000 $\mu$ m $\times$ 1.4 $\mu$ m    |      |

| PMOS Harris transistor, measured as described in chapter 4.                                                          | 39   |

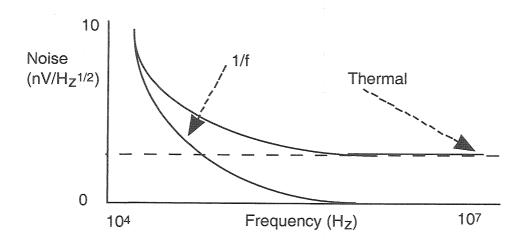

| Figure 1.13 General noise spectrum for an MOS transistor.                                                            | 42   |

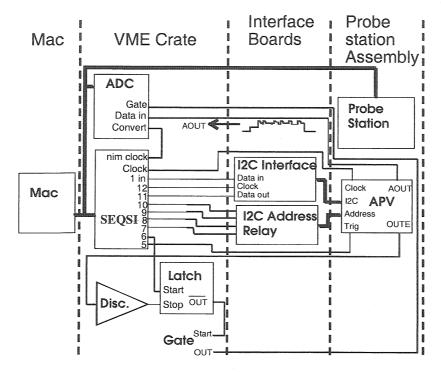

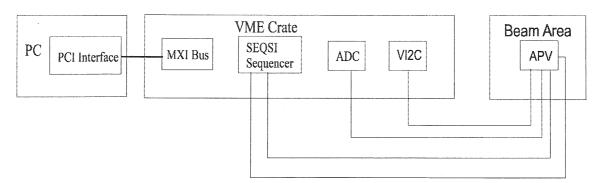

| Figure 2.1 Schematic of the probe-station test setup.                                                                | 46   |

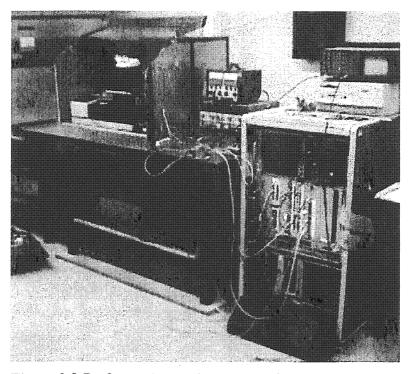

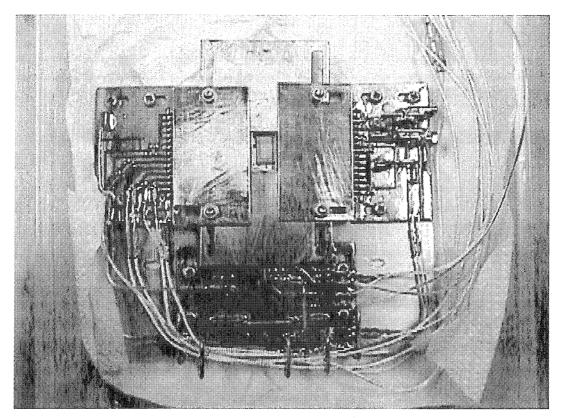

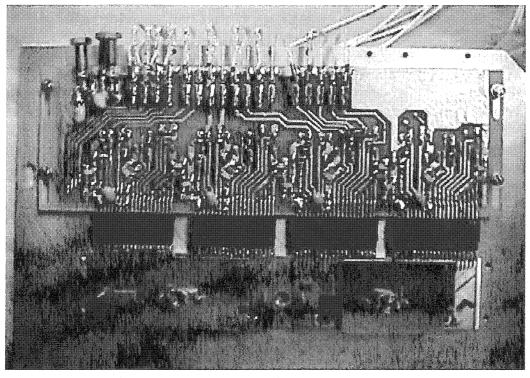

| Figure 2.2 Probe station and VME interface.                                                                          | 46   |

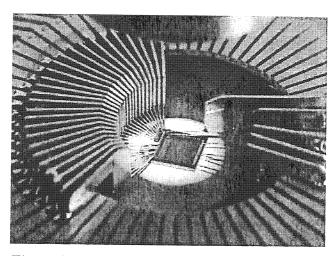

| Figure 2.3 Probe card interfacing an APV25.                                                                          |      |

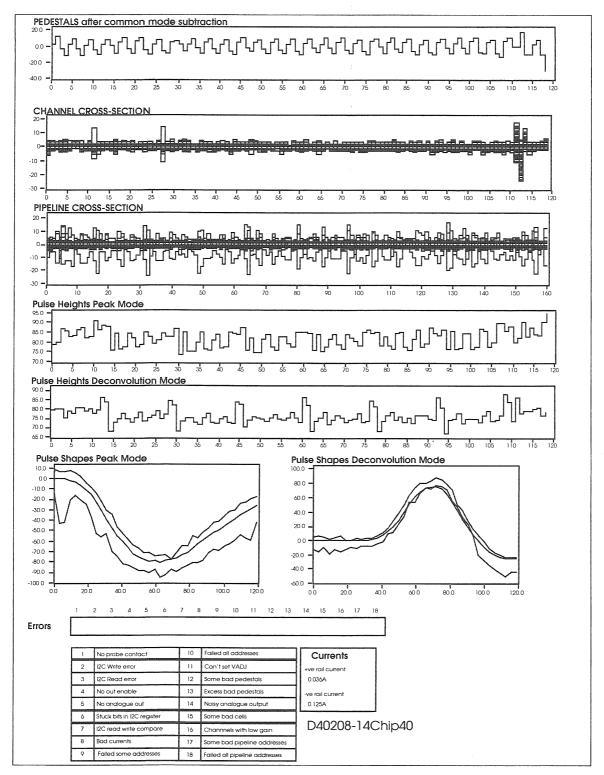

| Figure 2.4 Data sheet from chip 40, wafer 14 from the first APV6 run.                                                |      |

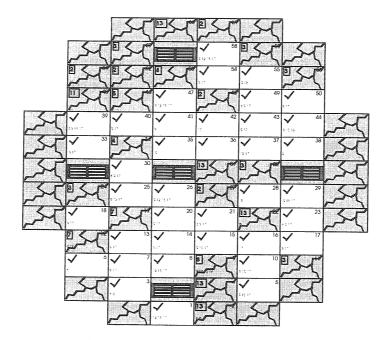

| Figure 2.5 Map of wafer 14 from APV6 run D40208A. Note incomplete sites at edge of wafer are nev                     |      |

| probed, also the 5 sites which contain transistor test structures.                                                   |      |

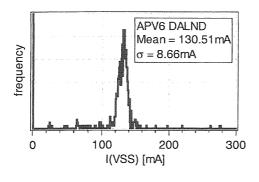

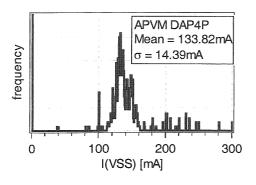

| Figure 2.6 Current distributions for APV6.                                                                           | 60   |

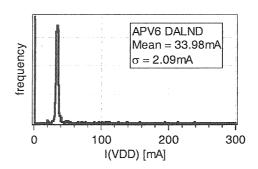

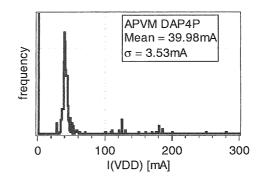

| Figure 2.7 Current distributions for APVM DAP4P.                                                                     | 60   |

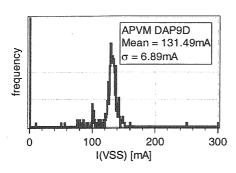

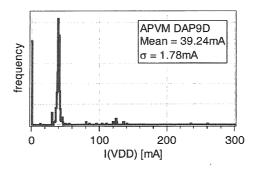

| Figure 2.8 Current distributions for APVM DAP9D                                                                      |      |

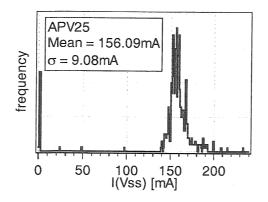

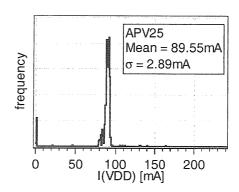

| Figure 2.9 Current distributions for APV25.                                                                          |      |

| Figure 2.10 I(VDD) vs I(VSS) for APV6                                                                                | 62   |

| Figure 2.11 I(VDD) vs I(VSS) for APVM.                                                                               |      |

| Figure 2.12 I(VDD) vs I(VSS) for APV25                                                                               |      |

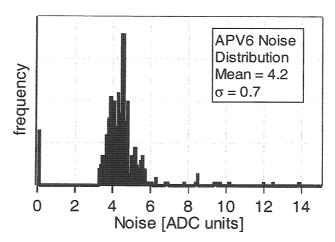

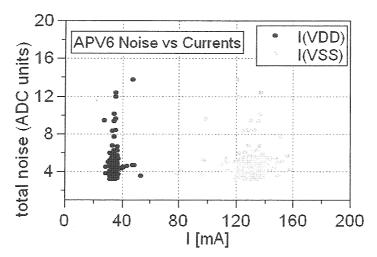

| Figure 2.13 Distribution of average channel noise from all APV6 chips.                                               |      |

| Figure 2.14 Noise vs Current for APV6.                                                                               |      |

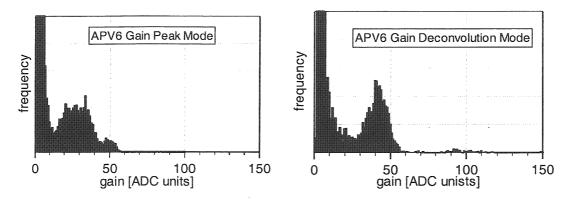

| Figure 2.15 APV6 gain distribution in peak and deconvolution mode                                                    |      |

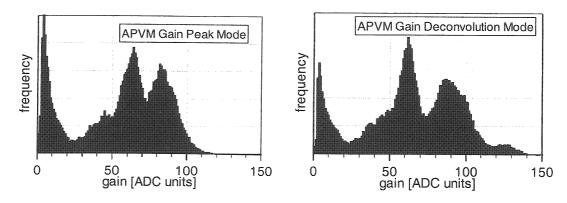

| Figure 2.16 APVM gain distribution in peak and deconvolution mode.                                                   |      |

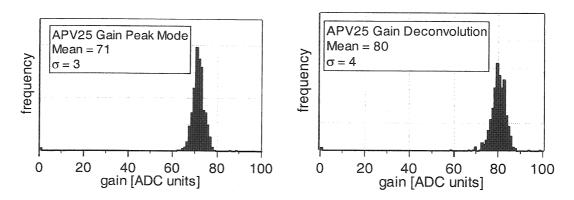

| Figure 2.17 APV25 gain distribution in peak and deconvolution mode                                                   |      |

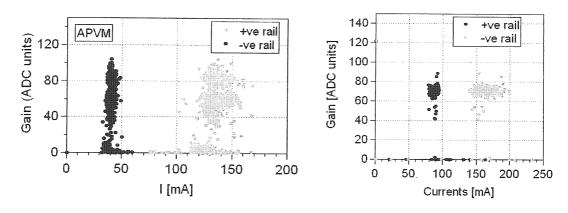

| Figure 2.18 Gain vs Current for APVM and APV25.                                                                      |      |

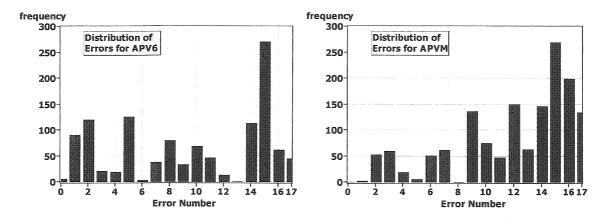

| Figure 2.19 Distribution of Errors for APV6 and APVM.                                                                |      |

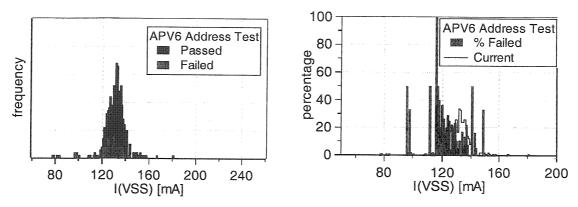

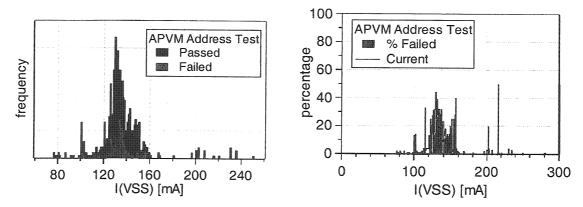

| Figure 2.20 Current and failure percentage distributions of APV6 chips that passed and failed I <sup>2</sup> C add   | ress |

|                                                                                                                      | 67   |

| Figure 2.21 Current and failure percentage distributions of APVM chips that passed and failed I <sup>2</sup> C       |      |

| address test.                                                                                                        | 67   |

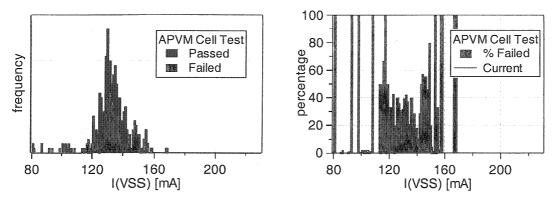

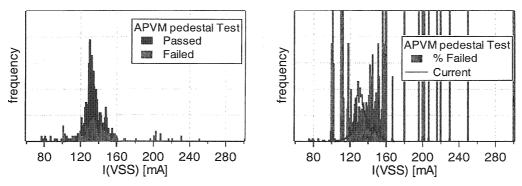

| Figure 2.22 Current and failure distributions of APVM chips that passed and failed pipeline cell test                | 68   |

| Figure 2.23 Current and failure distributions of APV6 chips that passed and failed pedestal test                     |      |

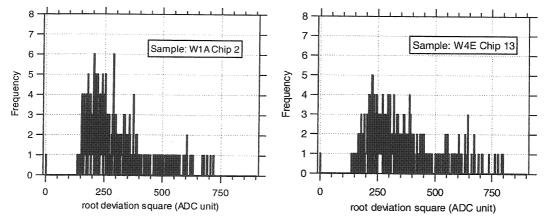

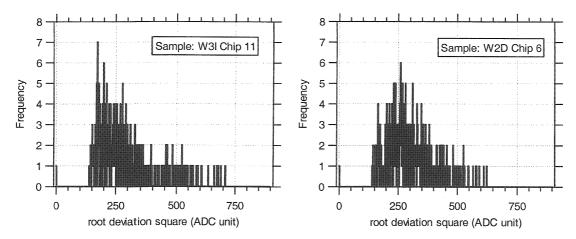

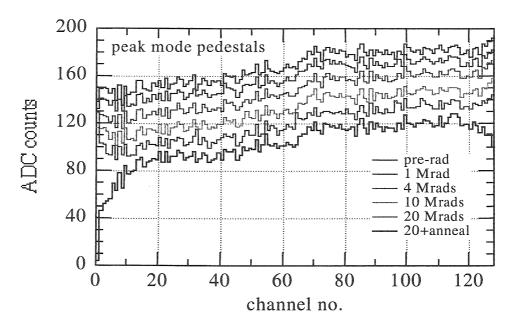

| Figure 2.24 Distribution of $\delta$ for two sample chips                                                            |      |

| Figure 2.25 Distribution of δ for two sample chips.                                                                  | 70   |

| Figure 3.1 Example measurements of the stopping powers of the proton, K-meson, pion electron and                     |      |

| muon                                                                                                                 | 75   |

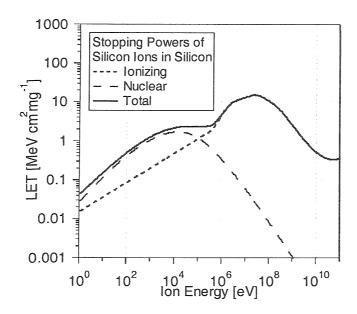

| Figure 3.2 Energy loss of silicon in silicon as a function of the kinetic energy.                                    | 76   |

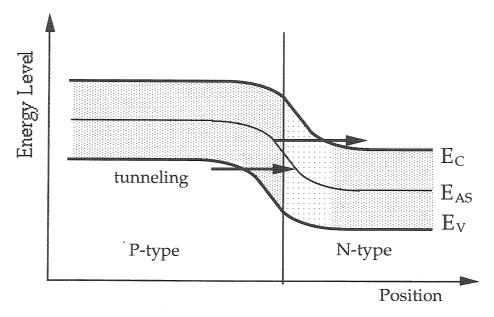

| Figure 3.3 An effect of energy levels in the band gap of a p-n junction.                                             | 77   |

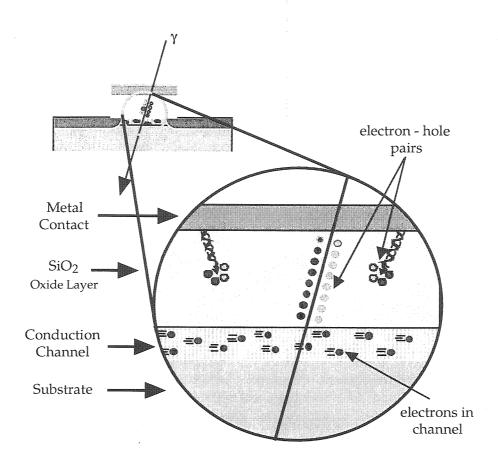

| Figure 3.4 Electron hole pair production.                                                                            |      |

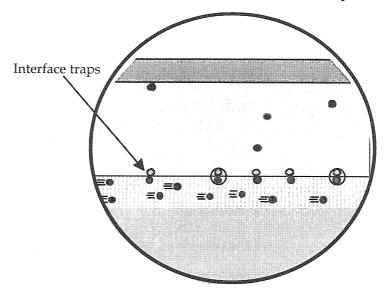

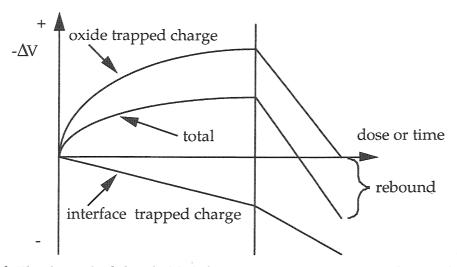

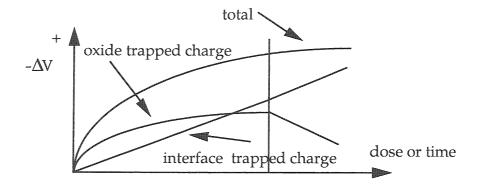

| Figure 3.5 Trapped charge in the oxide and charge traps at the interface.                                            |      |

| Figure 3.6. The theoretical threshold shifts in an NMOS transistor before and after irradiation.                     |      |

| Figure 3.7 The theoretical threshold shifts in a PMOS transistor before and after irradiation                        |      |

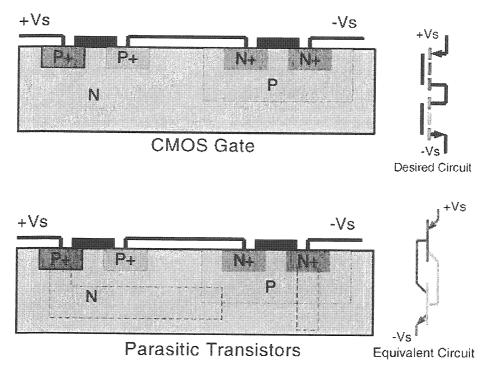

| Figure 3.8 Two parasitic transistors in positive feedback loop that can give rise to SEI                             | 02   |

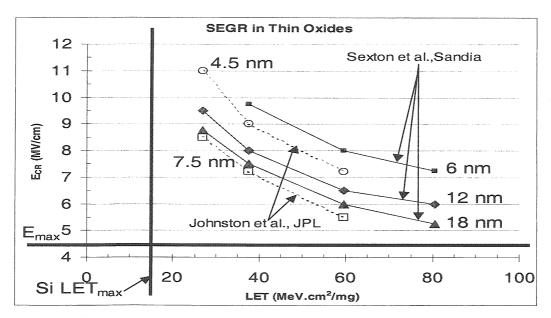

| Figure 3.9 Critical electrical field as a function of particle LET. The horizontal bold solid line indica                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .tes   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| the electric field across the oxides in an APV25 operated under normal conditions. The vertical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | l bold |

| solid line indicates the maximum LET expected in the CMS tracker.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 84     |

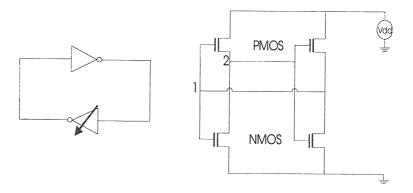

| Figure 3.10 Schematic representation of a memory cell composed of two cross coupled inverters, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

| circuit description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

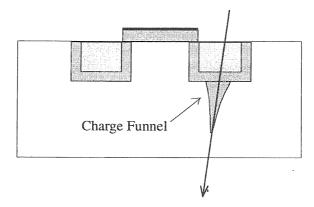

| Figure 3.11 Interaction of an ion in an implant depletion region.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| Figure 3.12 Illustration of collected current pulse shape.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

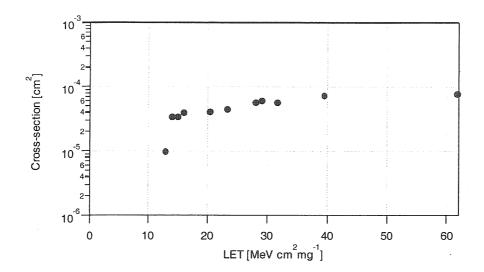

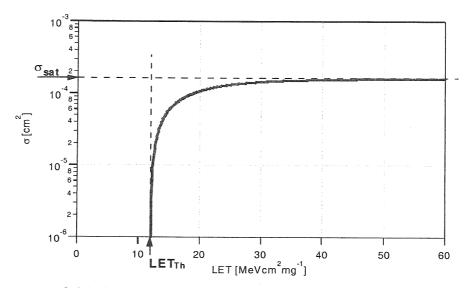

| Figure 3.13 A typical set of experimental measurements of SEU cross-section vs LET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

| Figure 3.14 The Weibull fit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 89     |

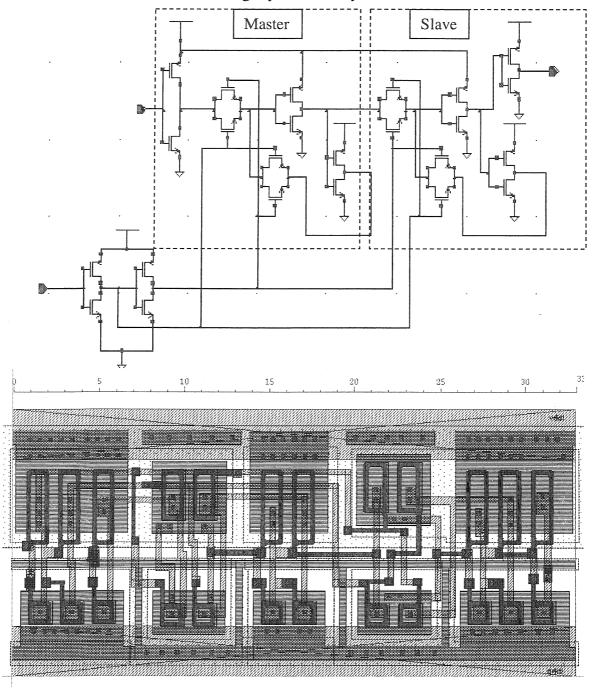

| Figure 3.15 DFF Schematic and layout diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 91     |

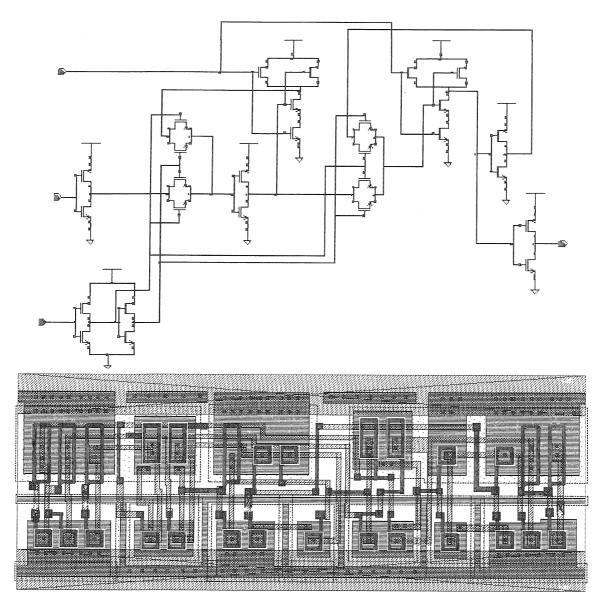

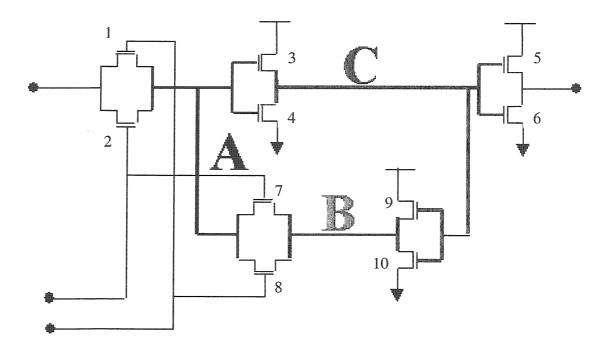

| Figure 3.16 DFF-Reset schematic and layout diagram.  Figure 3.17 schematic of DFF slave.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 92     |

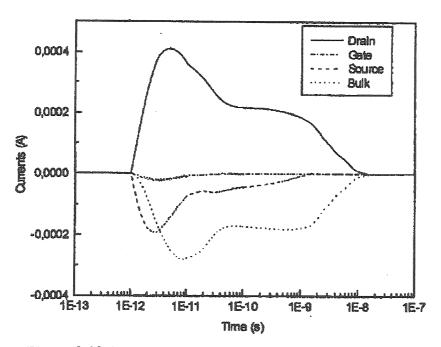

| Figure 3.17 Schematic of DFF stave.  Figure 3.18 Currents of the on NMOS transistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

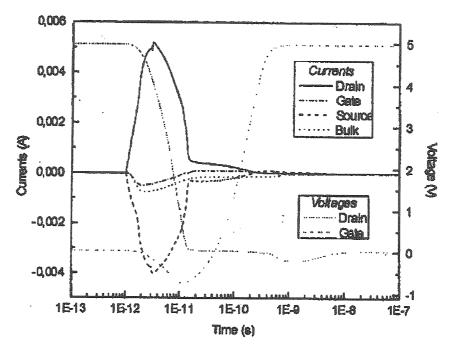

| Figure 3.19 Currents and voltages during a charge injection greater than critical.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

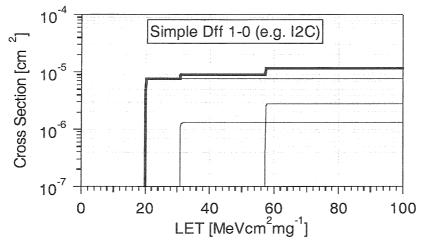

| Figure 3.20 Theoretical cross-sections for 1-0 transitions in a simple DFF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

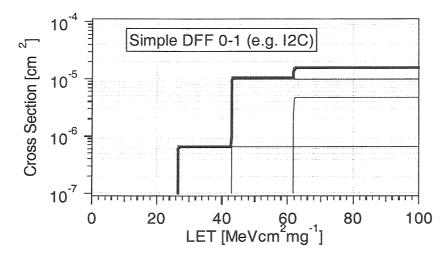

| Figure 3.21 Theoretical cross-sections for 0-1 transitions in a simple DFF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

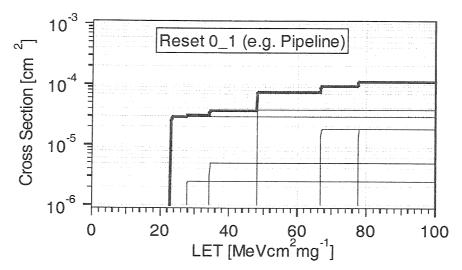

| Figure 3.22 Theoretical cross-section for pipeline logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |

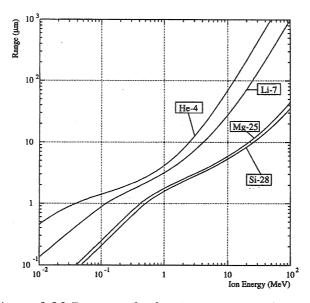

| Figure 3.23 Ranges of a few ion types in silicon.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

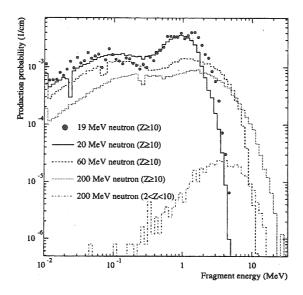

| Figure 3.24 Fragment energy spectra from n-Si scattering at energies above 20MeV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

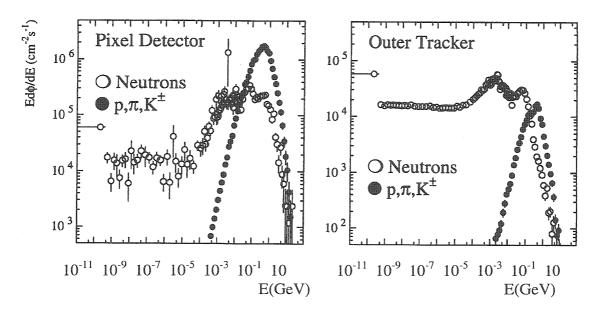

| Figure 3.25 Energy spectra of neutrons and charged hadrons in the inner and outer tracker.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

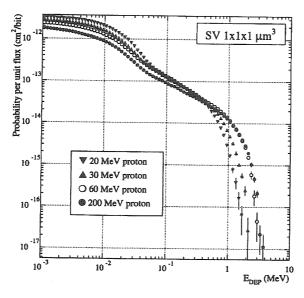

| Figure 3.26 Energy deposition probabilities for protons of different energies. The curve shows the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10 .   |

| probability to have, within the SV an ionizing deposition greater or equal to the indicated $E_{\text{DEP}}$ v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | value. |

| The state of the s |        |

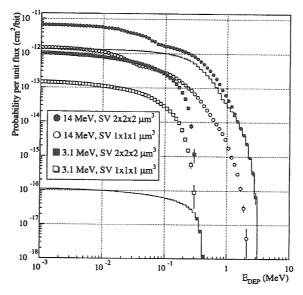

| Figure 3.27 Energy deposition probabilities for 3.1 MeV and 14 MeV neutrons with two different SV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| sizes. The solid lines show the contribution of $(n,\alpha)$ reactions for the $2x2x2\mu m^3$ cases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

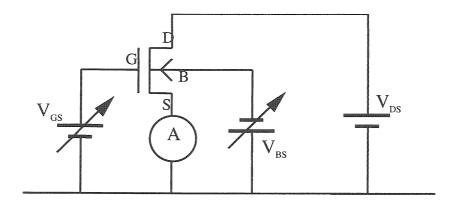

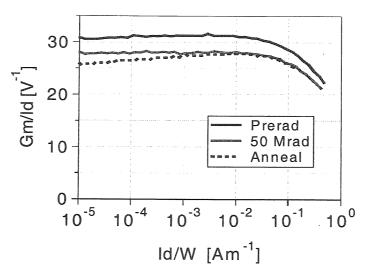

| Figure 4.1 Circuit diagram for transistor test setup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |

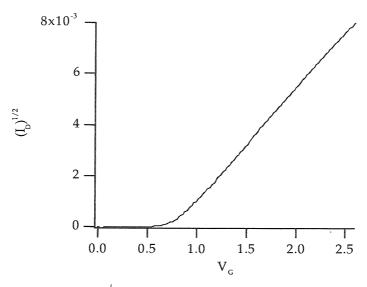

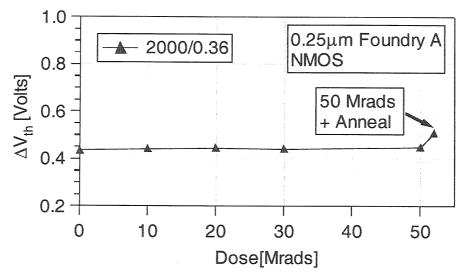

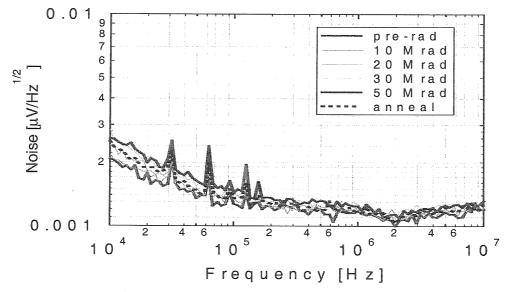

| Figure 4.2 $\sqrt{I_{DS}}$ v. $V_{GS}$ for an NMOS transistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 107    |

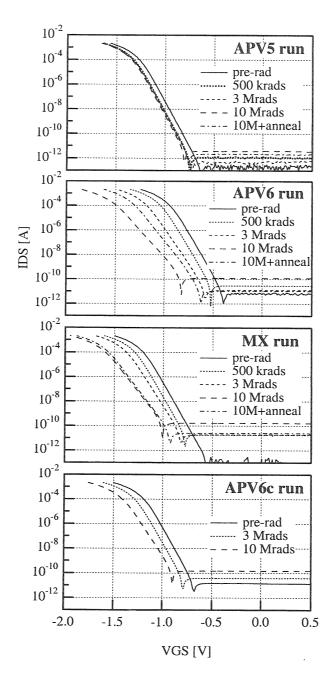

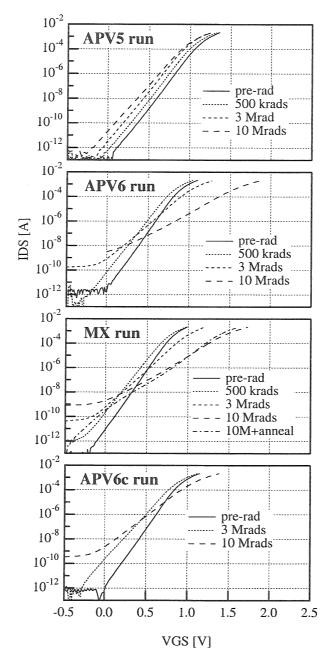

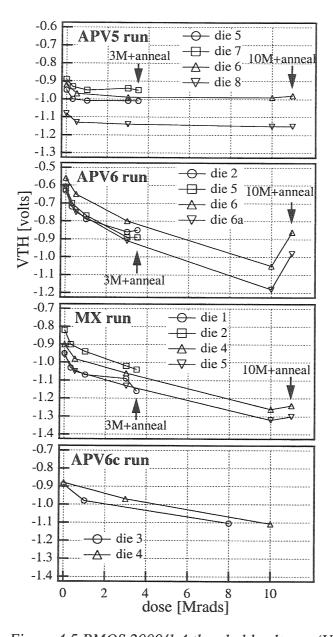

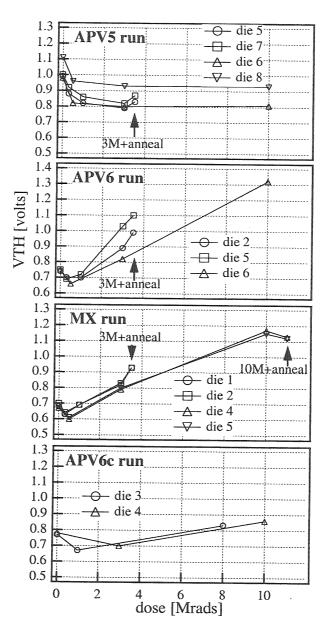

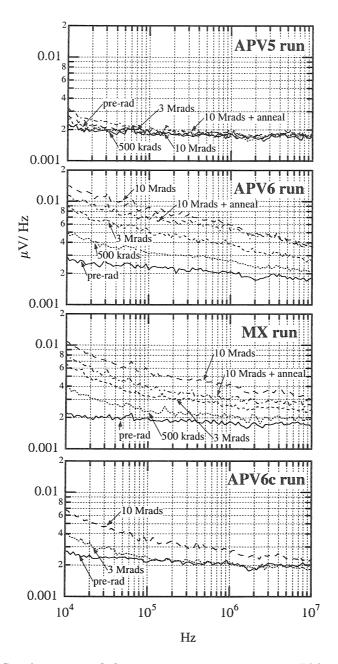

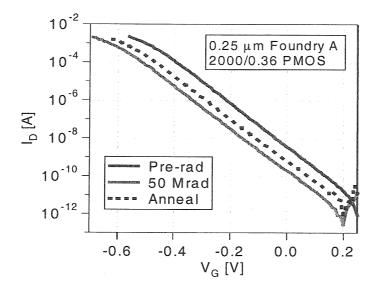

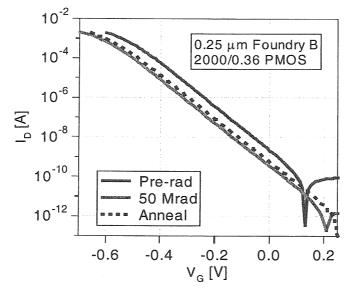

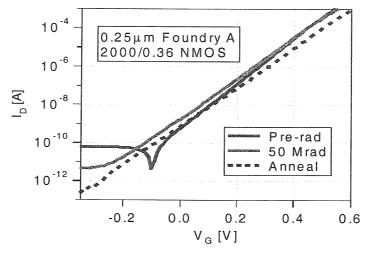

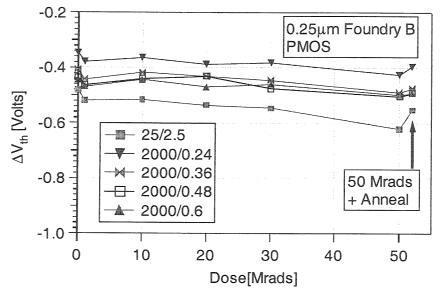

| Figure 4.3 PMOS 2000/1.4 I <sub>DS</sub> vs. V <sub>GS</sub> characteristics up to 10 Mrads and after annealing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |