# 5008082 208082

# Etude des transistors MOS avancés sur Silicium sur Isolant (SOI): bruit, dégradation en environnement radiatif et applications

#### Federico Faccio

Novembre 1997

CERN LIBRARIES, GENEVA

CM-P00041377

#### **THESE**

présentée par

#### Federico FACCIO

# pour obtenir le grade de **DOCTEUR** de l'INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

(Arrêté ministériel du 30 mars 1992)

Spécialité: PHYSIQUE DES COMPOSANTS A SEMICONDUCTEURS dans le cadre de la formation OPTIQUE, OPTO-ELECTRONIQUE ET MICRO-ONDES

\_\_\_\_\_

#### Etude des transistors MOS avancés sur Silicium sur Isolant (SOI): bruit, dégradation en environnement radiatif et applications

-----

Date de soutenance: 5 Novembre 1997

#### Composition du jury:

TOUBOUL André Professeur, Université Bordeaux 1 Président LERAY Jean-Luc Docteur d'Etat, CEA Rapporteur Professeur, UCL FLANDRE Denis Rapporteur PACCAGNELLA Alessandro Professeur, Università di Padova Rapporteur CRISTOLOVEANU Sorin Directeur de Recherche, CNRS Directeur de Thèse ANGHINOLFI Francis Ingénieur, CERN Resp. de Thèse CERN

Thèse préparée au sein du groupe de microélectronique du **CERN**

(Laboratoire Européen pour la Physique des Particules)

A mamma Rosanna e papà Mario

libero di trovare il mio cammino, mi avete aiutato a percorrerlo Monsieur Sorin Cristoloveanu a accepté de diriger cette étude. C'est en grande partie à sa confiance que cette thèse doit son existence. Son esprit ouvert, son envergure scientifique et sa créativité sont des qualités que j'ai pu apprécier tout au long de mes travaux, et qui m'ont aidé à les finaliser.

Monsieur Francis Anghinolfi a assuré le suivi de mon activité au CERN. Je le remercie pour sa très grande disponibilité, sa rigueur, et le soutien qu'il m'a témoigné pendant ces années. Il a mérité le prix Nobel pour la patience pour avoir inlassablement corrigé mes fautes de français. J'ai beaucoup appris en travaillant avec lui.

Monsieur Jean-Luc Leray, Monsieur Denis Flandre et Monsieur Alessandro Paccagnella m'ont fait l'honneur d'être rapporteurs de ce travail. Je les remercie pour leur disponibilité et pour toutes leurs observations et commentaires, qui ont contribué à l'amélioration de ce manuscrit. Je remercie Monsieur André Touboul, qui a présidé le jury de thèse, pour sa disponibilité et pour l'intérêt qu'il a porté à mon travail.

Je tiens à remercier Monsieur Gérard Borel, Monsieur Jean Rédolfi et toute l'équipe de Thomson TCS pour leur collaboration au long de cette étude.

Grâce au soutien que j'ai reçu au sein du groupe de Microélectronique du CERN, mon travail de recherche a pu aboutir à une thèse. Je remercie pour cela Monsieur Mike Letheren, chef du groupe, et Monsieur Pierre Jarron, chef de la section "analogique" où j'ai eu l'occasion d'apprendre tout ce que je sais sur la microélectronique. Je suis particulièrement reconnaissant à Monsieur Erik Heijne pour l'attention qu'il a toujours porté à ma formation et pour m'avoir encouragé à entreprendre ce travail de thèse. Merci à Jean-Claude Santiard pour son aide, particulièrement indispensable lors du montage du système de mesure de bruit. I also want to thank Paul Aspell for his collaboration in the framework of the RD9 project, together with all the other members of the MIC group for their support and friendship during the past 6 years.

Un pensiero riconoscente è rivolto all'ingegner Franco Bonaudi ed al Dottor Sergio Fubini, la cui gentilezza ed entusiasmo scientifico sono per me un modello, nonchè all'Associazione per lo Sviluppo Scientifico e Tecnologico del Piemonte (ASP) per avere reso possibile l'inizio della mia avventura al CERN.

Molto più povero sarebbe stato il mio lavoro senza le discussioni con Giuseppe Rossi, Marco "Topoliño" Fornasari e Massimo Bianchi, studenti al CERN e preziosi colleghi. Grazie per i dibattiti animati "sulla vera origine della gobba", sempre stimolanti e ricchi, ma anche per terrina campagnola, gnocchi, e spaghetti a go-go. Grazie per avere condiviso entusiasmo ed abbattimento nel corso della nostra ricerca, e per la vostra preziosa amicizia. Grazie alla neodottoressa Cinzia Da Vià ed a Giovanni Anelli, impegnati al mio stesso tempo nella scrittura della tesi, per le fruttuose discussioni, il loro sostegno e la loro amicizia. Grazie a Cristina Soave per avere condiviso due splendidi anni di ricerca e di vita.

Grazie a Rosanna, Mario, nonna Elena, Cesare e Barbara per la loro presenza costante ed affettuosa nei momenti felici ed in quelli difficili.

Merci à Heidi Ellefsplass pour m'avoir accompagné, avec beaucoup d'écoute et une patience sans mesure, pendant la rédaction du manuscrit. Merci, Heidi, pour m'avoir entouré de chaleur, de sérénité, de vie.

### Table des matières

| Introduction                                                                                       | p. 9         |

|----------------------------------------------------------------------------------------------------|--------------|

| Chapitre 1: Environnement radiatif dans les expérience<br>Physique des Hautes Énergies (HEP<br>LHC | ) du         |

| 1.1 Les expériences de physique du LHC                                                             |              |

| 1.2 L'environnement radiatif à ATLAS et CMS                                                        | -            |

| 1.2.1 Central tracker                                                                              |              |

| 1.2.2 Calorimètres                                                                                 | p. 18        |

| 1.2.3 Détecteur à muons                                                                            | p. 19        |

| 1.3 Synthèse                                                                                       | <del>-</del> |

|                                                                                                    | p. 20        |

|                                                                                                    |              |

| Chapitre 2: Effets des rayonnements sur les transistors et méthodologies de durcissement           | MOS p. 21    |

| 2.1 Dose intégrée                                                                                  | _            |

| 2.1.1 Centres de défault dans l'oxyde de silicium et à l'interfac                                  |              |

| Si-SiO <sub>2</sub>                                                                                |              |

| 2.1.2 Formation de la charge piègée dans l'oxyde et à l'interfa                                    |              |

| 2.1.3 Conséquences sur les transistors MOS                                                         | 1            |

| Déplacement de la tension de seuil                                                                 |              |

| Diminution de la mobilité                                                                          |              |

| Augmentation du bruit                                                                              | p. 25        |

| Courants de fuite                                                                                  | p. 26        |

| 2.2 Phénomènes non récurrents (Single Event Phenomena: SEP)                                        |              |

| 2.2.1 Effets des ions lourds                                                                       | p. 29        |

| 2.2.2 Effets des protons                                                                           | p. 30        |

| 2.2.3 Aléa logique (Single Event Upset, SEU)                                                       | p. 31        |

| 2.2.4 Verrouillage maintenu (Single Event Latchup, SEL)                                            | p. 32        |

| 2.2.5 Single Event Snapback (SES)                                                                  |              |

| 2.2.6 Claquage de grille (Single Event Gate Rupture, SEGR)                                         | p. 33        |

| 2.2.7 Destruction par échauffement excessif (SEBO)                                                 | -            |

| 2.3 Méthodologies de durcissement                                                                  |              |

| 2.3.1 Durcissement technologique                                                                   | p. 34        |

| Durcissement à la dose intégrée                                                                    | p. 34        |

| Durcissement aux effets transitoires                                                               |              |

| 2.3.2 Durcissement électrique (conception de circuits)                                             | •            |

| 2.3.3 Durcissement des systèmes                                                                    | n 10         |

| 2.4      | Synthèse                                                                                                                                                       | p. 41                                                             |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Chapitre | 3: Techniques d'évaluation du durcissement à la dose intégrée                                                                                                  |                                                                   |

| 3.1      | Conditions de test                                                                                                                                             | <ul><li>p. 43</li><li>p. 45</li></ul>                             |

| 3.2      | Méthodes standard de test de qualification                                                                                                                     | p. 49<br>p. 49                                                    |

| 3.3      | Techniques d'évaluation des dégradations                                                                                                                       | p. 52                                                             |

| 3.4      | Synthèse                                                                                                                                                       | p. 56                                                             |

| Chapitre | 4: Les technologies SOI                                                                                                                                        | p. 58                                                             |

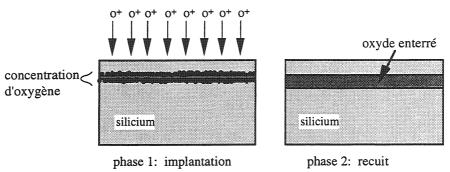

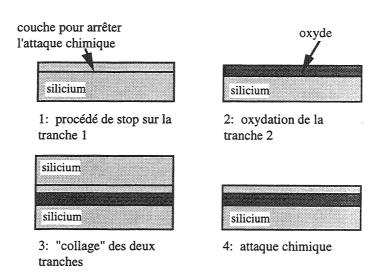

| 4.1      | L'oxyde enterré                                                                                                                                                | <ul><li>p. 58</li><li>p. 59</li><li>p. 60</li><li>p. 62</li></ul> |

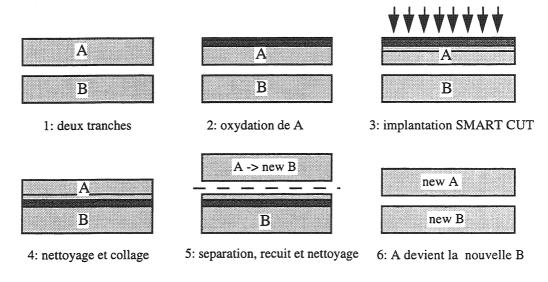

| 4.2      | SOI partiellement, moyennement et totalement déserté                                                                                                           | <ul><li>p. 65</li><li>p. 65</li><li>p. 70</li><li>p. 70</li></ul> |

| 4.3      | Tenue aux radiations des technologies SOI.  4.3.1 Dose intégrée  Oxyde de grille  Oxydes latéraux et de champs  Oxyde enterré  4.3.2 Phénomènes non récurrents | p. 73<br>p. 73<br>p. 73<br>p. 73<br>p. 75<br>p. 76                |

| 4.4      | 4.3.3 Résumé comparatif                                                                                                                                        | <ul><li>p. 78</li><li>p. 79</li></ul>                             |

| Chapitre | 5: Caractérisation statique des transistors en HSOI3-<br>HD et leur tenue à la dose intégrée |       |

|----------|----------------------------------------------------------------------------------------------|-------|

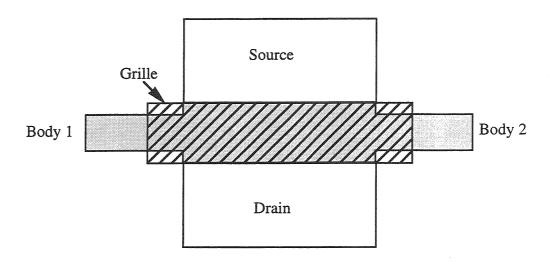

| 5.1      | HSOI3-HD.                                                                                    | p. 80 |

|          | 5.1.1 Epaisseur du film                                                                      | p. 81 |

|          | 5.1.2 Contacts de body                                                                       |       |

|          | 5.1.3 Paramètres statiques                                                                   | p. 83 |

| 5.2      | Conditions de test                                                                           | p. 84 |

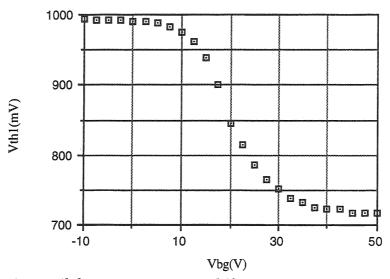

| 5.3      | Variation de la tension seuil avec l'irradiation                                             | p. 85 |

|          | 5.3.1 Transistor principal                                                                   |       |

|          | 5.3.2 Transistor de face arrière                                                             | p. 87 |

| 5.4      | Transconductance et mobilité                                                                 | p. 89 |

| 5.5      | Courant de fuite                                                                             | p. 91 |

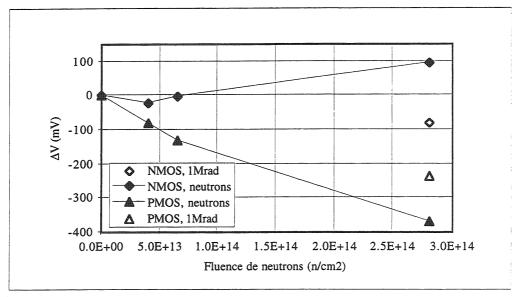

| 5.6      | Irradiations avec sources autres que le <sup>60</sup> Co                                     | p. 92 |

|          | 5.6.1 Irradiations avec une source de neutrons                                               |       |

|          | 5.6.2 Irradiations avec une source de protons                                                |       |

| 5.7      | Synthèse                                                                                     | p. 96 |

|          |                                                                                              |       |

|          |                                                                                              |       |

| Chapitre | 6: Le bruit                                                                                  | p. 98 |

|          | Conditions expérimentales de mesure                                                          |       |

|          | 6.1.1 Taille des transistors mesurés                                                         |       |

|          | 6.1.2 Polarisation pendant la mesure                                                         | _     |

|          | 6.1.3 Le système de mesure                                                                   |       |

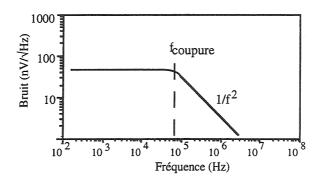

| 6.2      | Le spectre de bruit des transistors MOS                                                      | p.100 |

| 6.3      | Le bruit 1/f                                                                                 | p.102 |

| 6.4      | Le bruit blanc                                                                               | p.106 |

|          | Le bruit de génération-recombinaison                                                         | ~     |

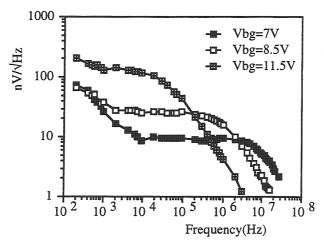

|          | La contribution additionnelle dans le spectre de bruit                                       | _     |

| 0.0      | 6.6.1 Modèle de l'origine de la composante additionnelle de bruit                            |       |

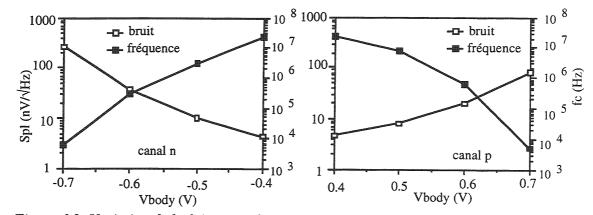

|          | 6.6.2 Confirmations expérimentales du modèle                                                 |       |

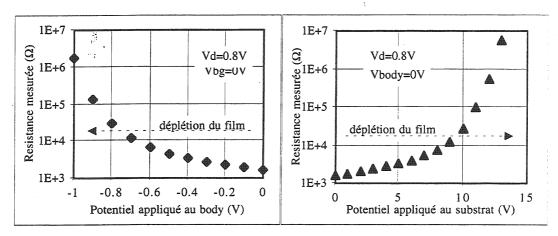

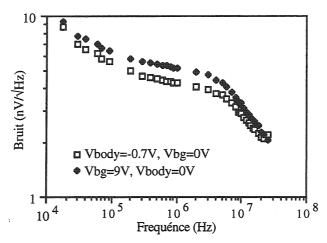

|          | Corrélation entre R <sub>mes</sub> et la bosse de bruit                                      |       |

|          | Egalité du bruit au plateau (S <sub>pl</sub> ) référé au <i>body</i>                         |       |

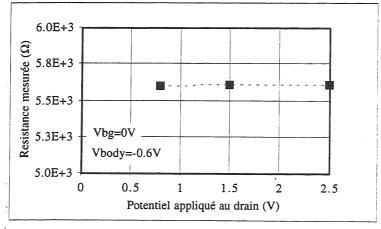

|          | Résultats en régime ohmique de fonctionnement                                                | p.118 |

|          | Vérification quantitative du modèle: estimation de la résistance                             | P     |

|          | et de la capacité RC                                                                         | p.119 |

|          | Efficacité du filtre RC                                                                      | p.120 |

|          |                                                                                              | p.122 |

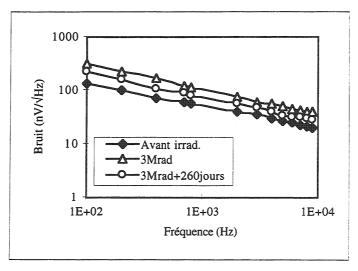

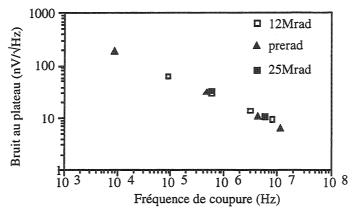

|          | Evolution avec l'irradiation                                                                 | p.123 |

|          | 6.6.3 Considérations sur la composante additionnelle de bruit                                | p.124 |

| 6.7      | Synthèse                                                                                     | p.125 |

| analogique-numérique (HADC11) (HADC11)                                                                        | p.126                                     |

|---------------------------------------------------------------------------------------------------------------|-------------------------------------------|

|                                                                                                               | -                                         |

|                                                                                                               | p.126<br>p.126                            |

|                                                                                                               | p.128                                     |

|                                                                                                               | p.129                                     |

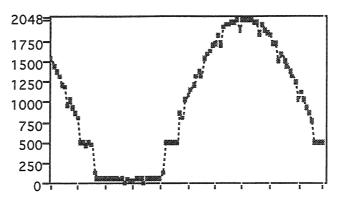

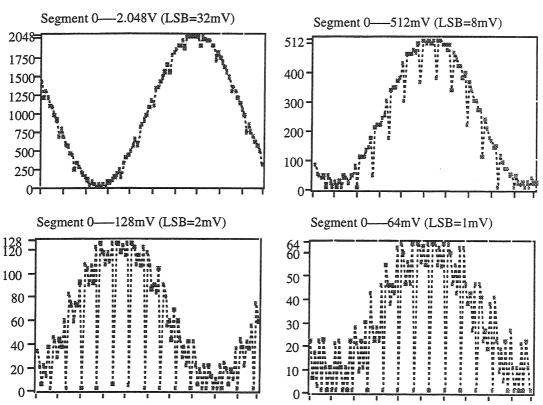

| 7.3 Résultats sur le convertisseur HADC11                                                                     | p.131                                     |

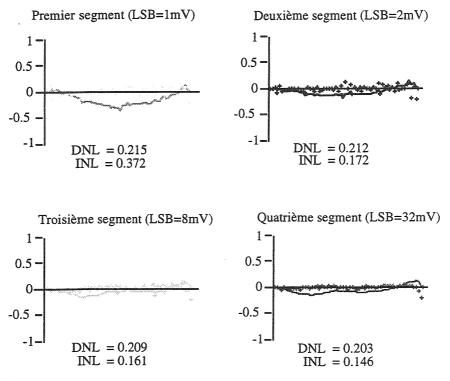

| 7.3.1 Résultats avant irradiation                                                                             | p.132                                     |

|                                                                                                               | p.132                                     |

|                                                                                                               | p.132                                     |

|                                                                                                               | p.133<br>p.134                            |

| •                                                                                                             | •                                         |

| 7.4 Synthèse                                                                                                  | p.137                                     |

|                                                                                                               |                                           |

|                                                                                                               |                                           |

| Conclusion                                                                                                    | p.139                                     |

|                                                                                                               | 1                                         |

| Difficultie prophigues                                                                                        | 141                                       |

| Références Bibliographiques                                                                                   | p.141                                     |

|                                                                                                               |                                           |

| Annexe 1: Interaction des rayonnements avec la                                                                | 1 ~ ~                                     |

| matière                                                                                                       | -                                         |

|                                                                                                               | p.155                                     |

| Effets de déplacement                                                                                         | -                                         |

| Références Bibliographiques                                                                                   | p.157                                     |

|                                                                                                               |                                           |

|                                                                                                               |                                           |

|                                                                                                               |                                           |

| Annere 2. Effets des revenuents sur les tronsisters                                                           |                                           |

| Annexe 2: Effets des rayonnements sur les transistors bipolaires                                              | p.158                                     |

| bipolaires                                                                                                    | p.158                                     |

| <b>bipolaires</b> A2.1 Dose intégrée                                                                          | p.158                                     |

| bipolaires  A2.1 Dose intégrée  Conséquences sur les transistors bipolaires.                                  | -                                         |

| bipolaires  A2.1 Dose intégrée  Conséquences sur les transistors bipolaires  Transistors NPN                  | p.158<br>p.158                            |

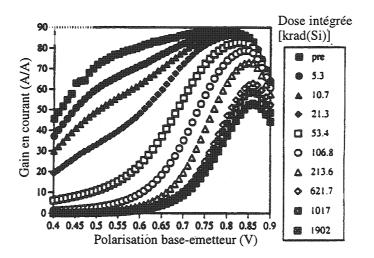

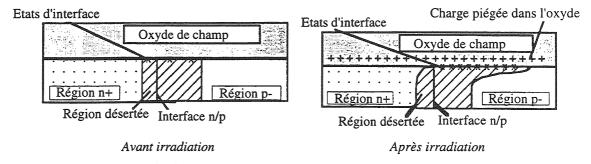

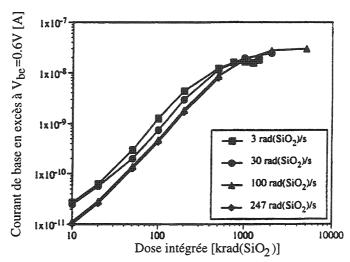

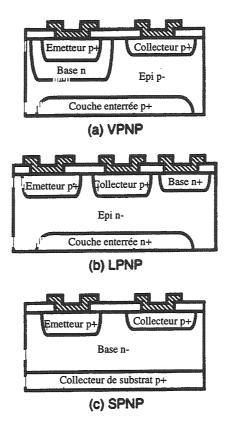

| bipolaires  A2.1 Dose intégrée  Conséquences sur les transistors bipolaires  Transistors NPN  Transistors PNP | p.158<br>p.158<br>p.159                   |

| bipolaires  A2.1 Dose intégrée                                                                                | p.158<br>p.158<br>p.159<br>p.160          |

| bipolaires  A2.1 Dose intégrée                                                                                | p.158<br>p.158<br>p.159<br>p.160<br>p.162 |

| Annexe | 3:   | Approximation de $\Delta Log(I)$ dans la méthode de la pente en inversion faible | o.165 |

|--------|------|----------------------------------------------------------------------------------|-------|

|        |      |                                                                                  |       |

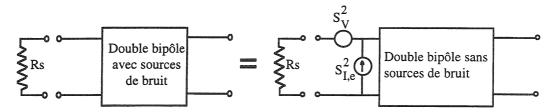

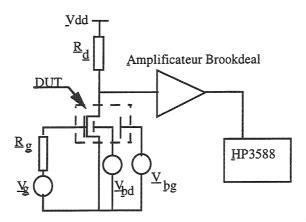

| Annexe | 4:   | Le système de mesure du bruit p                                                  | ).166 |

|        |      | Mesure en régime de saturation p  Mesure en régime ohmique p                     |       |

| Re     | éfér | ences Bibliographiques p                                                         | ).169 |

#### Introduction

Le CERN, laboratoire européen pour la physique des particules, travaille depuis plusieurs années pour préparer la construction du plus puissant accélérateur de particules du monde: le LHC (*Large Hadron Collider*). L'un des défis technologiques de ce projet concerne la survie aux radiations de l'électronique intégrée en proximité des détecteurs de particules. L'environnement radiatif des expériences sera déterminé par les collisions des faisceaux de particules, les détecteurs les plus près du point de collision étant les plus exposés. Dans ces régions, des niveaux de dose intégrée supérieurs d'un facteur 10 à 100 à ceux typiques des applications spatiales pourront être atteints après 10 ans de fonctionnement du LHC. La dose intégrée sera accompagnée par une fluence de neutrons de l'ordre de 10<sup>14</sup> neutrons/cm<sup>2</sup>. Dans un tel environnement, l'utilisation de technologies durcies pourra résoudre le problème de la survie de l'électronique.

Plusieurs technologies microélectroniques tolérantes ou durcies aux effets des radiations ont été développées en Europe et aux Etats Unis pour des applications militaires et pour l'espace. La plupart de ces technologies, notamment celles qui sont plus efficacement durcies, ont été longtemps réservées aux composants militaires; elles sont devenues plus largement disponibles seulement ces dernières années. Ainsi, l'accès à HSOI3-HD, une technologie CMOS durcie produite par le fabricant français Thomson TCS, a été ouvert pour des applications commerciales au début des années 90. Cette filière sur silicium sur isolant (SOI), de par ses caractéristiques de tenue aux effets des rayonnements, présentait un intérêt considérable pour la fabrication de circuits intégrés destinés aux expériences du LHC. Pour cette raison, à la fin de 1990, un projet de recherche et développement a été lancé au CERN. Ce projet, appelé RD9, avait comme but l'évaluation de la performance analogique et du durcissement de la technologie HSOI3-HD en vue des applications dans le LHC. La caractérisation analogique devait comprendre l'étude du bruit, paramètre fondamental dans le choix d'une technologie pour l'électronique de front-end qui doit amplifier les signaux délivrés par les détecteurs.

Le projet de recherche a été structuré en plusieurs phases. Dans la première phase, l'évolution des caractéristiques statiques des transistors avec l'irradiation devait être mesurée et analysée. La deuxième phase était centrée sur l'étude du spectre de bruit des transistors avant et après irradiation. Finalement, des circuits mixtes analogiques-numériques devaient être intégrés dans la technologie. L'architecture de ces circuits devait être typique de l'électronique appliquée à la physique des particules.

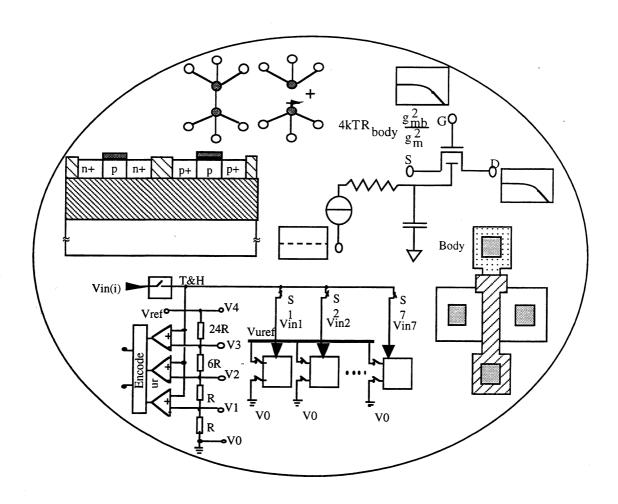

L'étude présentée dans ce mémoire a été effectuée dans le cadre du projet de recherche RD9, et a suivi les trois phases qui le composent. Par conséquent, nous nous sommes intéressés d'abord à la technologie, et donc à la physique des dispositifs et aux effets fondamentaux des rayonnements sur les transistors, et ensuite à la conception des circuit intégrés. L'éventail des thèmes abordés lors de cette étude étant assez vaste

(effets des rayonnements, technologies SOI, analyse du bruit, conception de circuits), ce mémoire a été organisé en 7 chapitres.

Le chapitre 1 décrit l'environnement radiatif des expériences de physique du LHC, avec les hauts niveaux de dose intégrée et de fluence de neutrons prévus, qui ont motivé cette étude.

Le chapitre 2 propose une familiarisation avec les effets des rayonnements sur les transistors MOS, dont la compréhension est indispensable pour l'analyse des résultats des mesures. A partir des effets fondamentaux, des méthodologies de durcissement à plusieurs niveaux (technologique, électrique et systèmes) sont proposées.

La complexité des effets des rayonnements implique la nécessité d'effectuer les test d'irradiations dans des conditions contrôlées. Les conditions de test, codifiées par deux méthodes standard, sont discutées dans le chapitre 3. Ce chapitre décrit aussi les techniques de caractérisation des dégradations des transistors qui ont été utilisées dans notre étude.

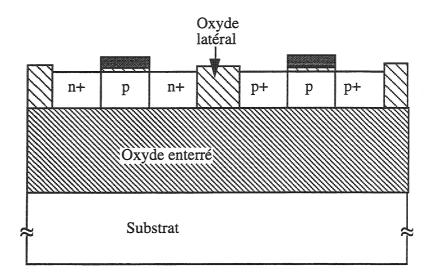

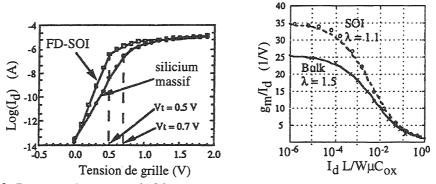

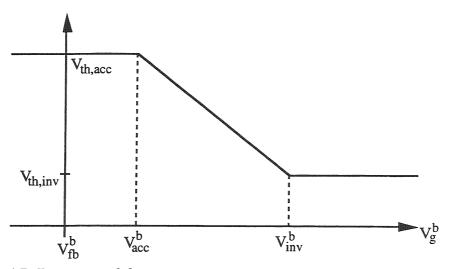

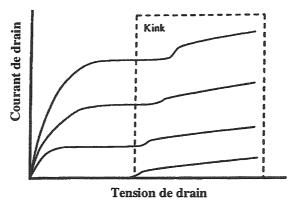

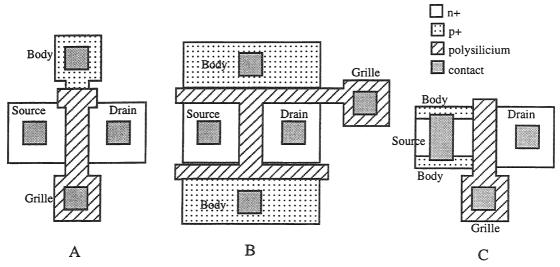

Les technologies sur silicium sur isolant (SOI) sont présentées dans le chapitre 4, qui donne les équations fondamentales du fonctionnement des transistors SOI. La performance électrique supérieure des transistors sur film totalement déserté par rapport aux transistors sur silicium massif, qui en fait de très bons candidats pour les applications à basse puissance ou basse tension, est mise en évidence. Un paragraphe est dédié à la tenue aux radiations des technologies SOI, et montre leurs avantages par rapport aux technologies sur silicium massif pour ce qui concerne les phénomènes non récurrents, particulièrement le latch-up.

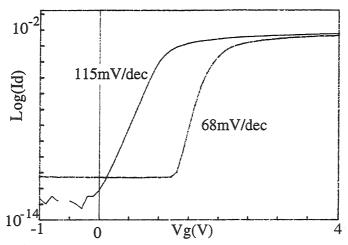

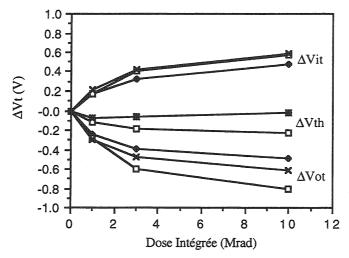

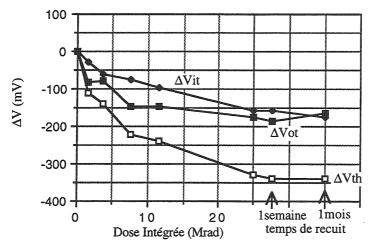

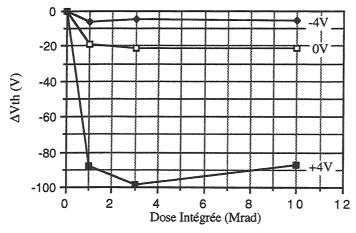

Le chapitre 5 montre les résultats de la caractérisation statique des transistors en HSOI3-HD. Une description sommaire de la technologie est donnée avant d'analyser les résultats des irradiations avec une source de rayons  $\gamma$  ( $^{60}$ Co). Des mesures effectuées après les irradiations avec une source de neutrons ou de protons sont aussi présentées. Ces mesures ont confirmé que dans cette technologie CMOS les dégradations provoquées par les rayonnements sont dominés par les effets d'ionisation.

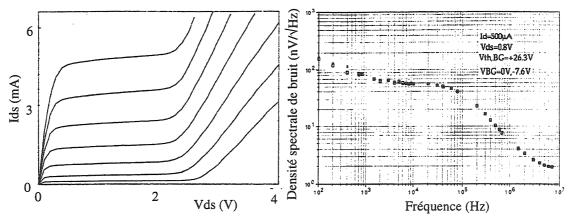

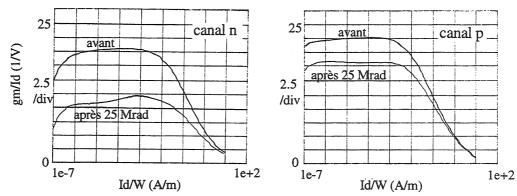

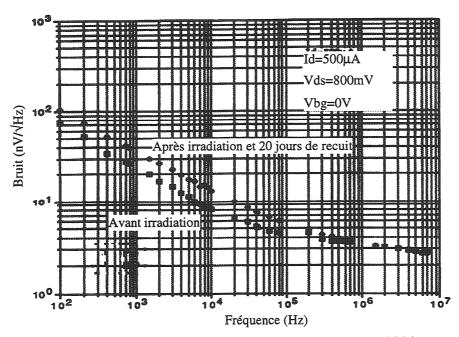

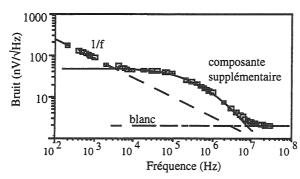

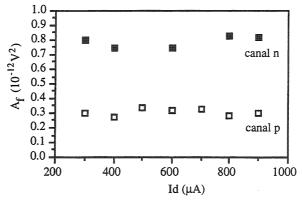

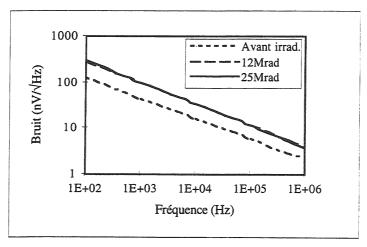

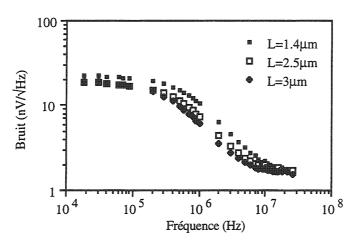

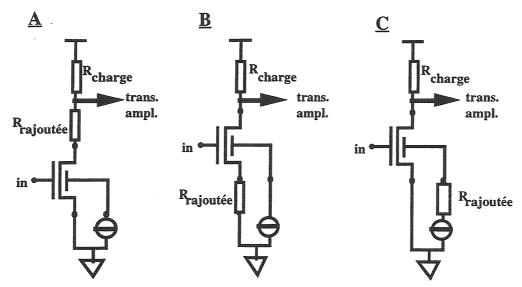

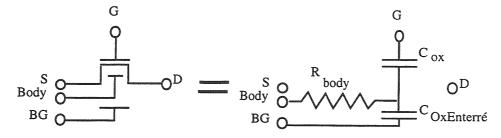

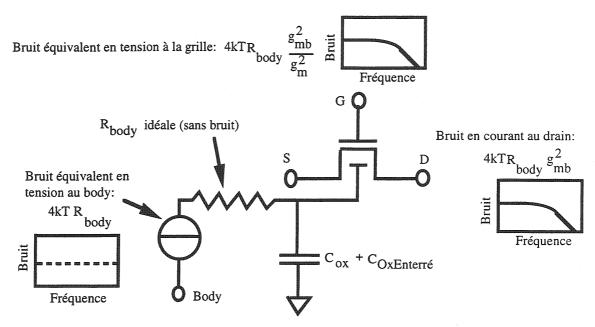

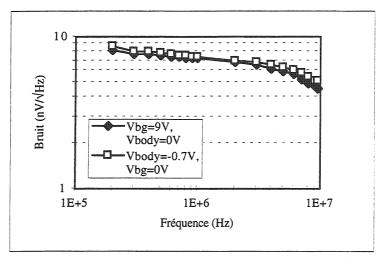

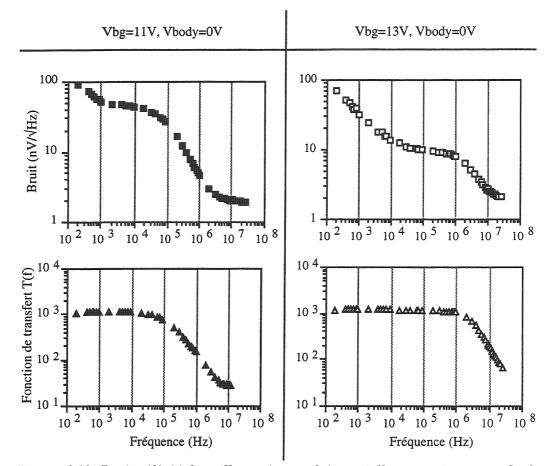

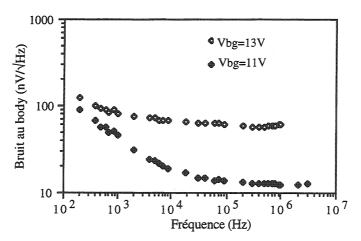

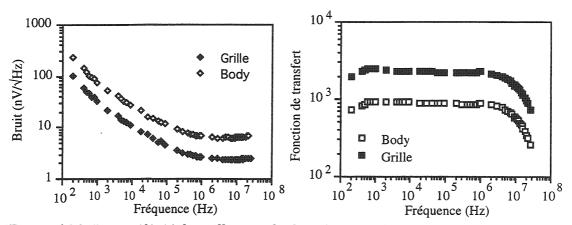

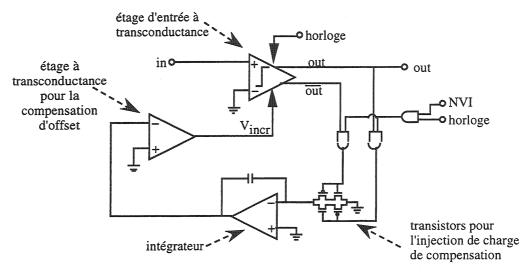

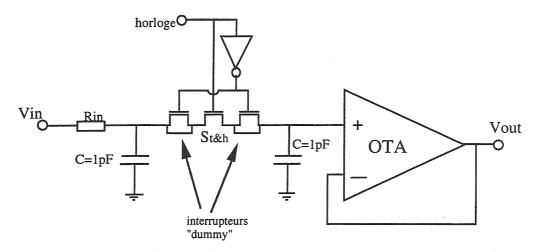

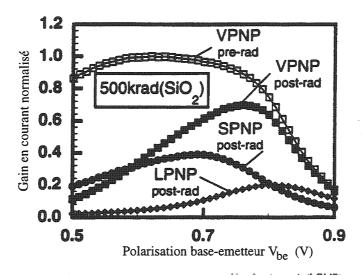

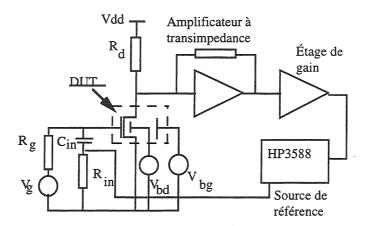

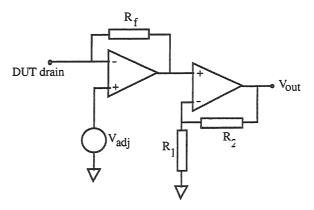

Le chapitre 6 contient une étude approfondie du bruit des transistors SOI dans la technologie HSOI3-HD. Nous avons observé trois sources de bruit dans le spectre, mesuré dans l'intervalle de fréquence 100 Hz–20 MHz. La composante additionnelle, qui se présente comme une "bosse" dans le spectre, se superpose aux contributions du bruit 1/f et du bruit blanc. Nous proposons un modèle pour l'origine de cette composante additionnelle et présentons une série d'observations expérimentales qui le confirment. L'évolution du bruit avec les irradiations est analysée pour les trois sources de bruit.

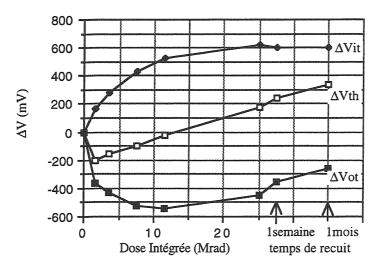

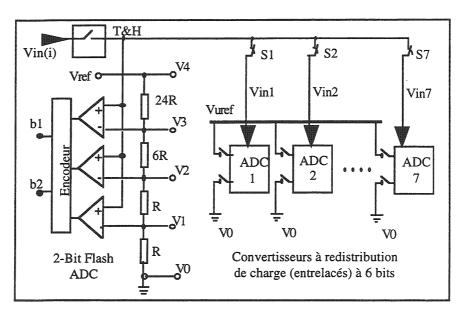

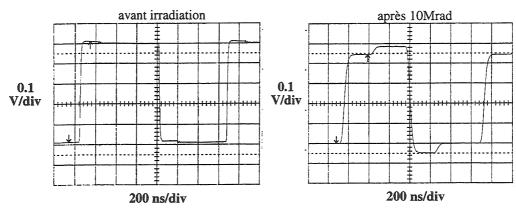

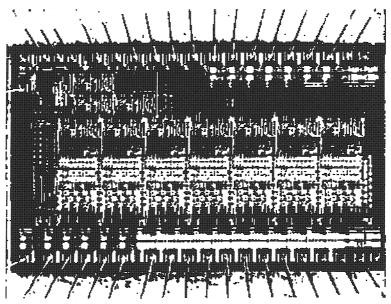

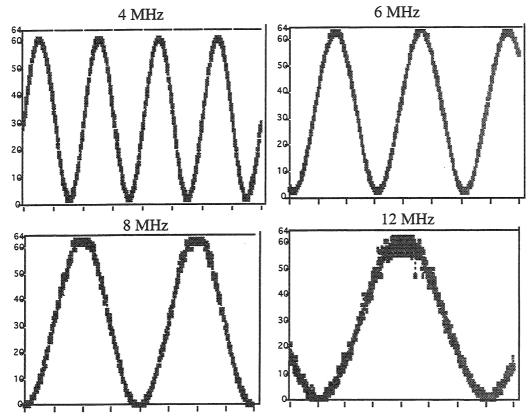

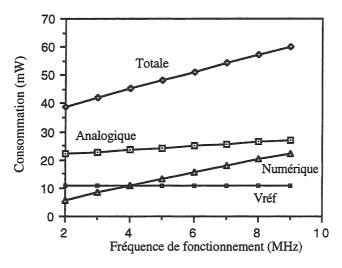

La dernière étape de l'étude concerne la conception de circuits en technologie HSOI3-HD: nous avons développé un convertisseur analogique-numérique capable de réaliser une conversion non linéaire de 11 bits de dynamique à une fréquence

d'échantillonnage de 5 MHz. Le chapitre 7 présente l'architecture du circuit, sa performance conforme aux spécifications et les résultats d'irradiation jusqu'à une dose intégrée de 10 et 20 Mrad.

#### Chapitre 1

#### Environnement radiatif dans les expériences de Physique des Hautes Énergies (HEP) du LHC

Le projet du grand collisionneur de hadrons LHC (*Large Hadron Collider*), qui sera le plus grand et le plus puissant accélérateur de particules du monde, a été approuvé par le Conseil du CERN en Décembre 1994. Les accélérateurs déjà existants sur le site du CERN seront utilisés en injecteurs pour le LHC: le Synchrotron à Protons (PS) accélérera les protons à 28 GeV, puis le Super Synchrotron à Protons (SPS) portera leur énergie à 450 GeV. Injectés dans les deux chambres à vide du LHC, les deux faisceaux de protons seront ultérieurement accélérés en directions opposées dans un anneau de 27 km de circonférence pour atteindre l'énergie de 7 TeV. Les collisions entre protons, avec une luminosité de 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>, seront produites au centre des immenses expériences de physique, où l'ensemble des interactions entre particules sera étudié. Le même collisionneur pourra également être utilisé pour produire des collisions entre ions de plomb à une énergie de 1148 TeV (dans le centre de masse) avec une luminosité de 10<sup>27</sup> cm<sup>-2</sup>s<sup>-1</sup>.

#### 1.1 Les expériences de physique du LHC

Quatre expériences de physique sont à ce jour prévues dans le LHC: ALICE, ATLAS, CMS et LHC-B.

ALICE [1] est une expérience conçue pour l'étude des collisions entre ions lourds (Pb-Pb). Elle ne nécessite pas une luminosité très élevée: sur 4000 collisions par seconde, il y a une grande probabilité d'avoir plus de 10 collisions dont le produit est intéressant pour l'étude physique visée. Chacune de ces collisions produit environ 10000 particules chargées à l'intérieur du détecteur, ce qui implique la nécessité d'un système de reconstruction des traces très sophistiqué. Pour cette raison, le point de collision en ALICE sera entouré de plusieurs couches de détecteurs à pixel en silicium, détecteurs à dérive en silicium, détecteurs à "strip" en silicium, détecteurs à gaz (MSGC, Micro Strips Gas Chambers) et chambres à fil. A cause de la faible luminosité, ces détecteurs et l'électronique associée ne seront pas soumis à de fortes doses ou fluences de particules. Les simulations détaillées de l'environnement radiatif n'ont pas encore à ce jour été effectuées, mais le niveau de dose intégrée devrait être en tout cas inférieur aux 200 krad.

Le but de LHC-B est l'étude de la physique des particules qui contiennent le quark beauty (B). La luminosité nécessaire pour produire 10<sup>5</sup> collisions intéressantes par année est de 10<sup>32</sup> cm<sup>-2</sup>s<sup>-1</sup>, ce qui implique 10<sup>7</sup> collisions inélastiques p-p par seconde [2]. Les détecteurs seront positionnés, selon le projet, à 1 cm du point d'interaction et

probablement endommagés par l'irradiation produite. Ils devront probablement être remplacés régulièrement après chaque année d'opération. L'électronique sera installée plus loin du point de collision, et les niveaux de dose intégrée et de fluence de particules permettront le fonctionnement à long terme de composants tolérants aux effets des rayonnements.

ATLAS [3] et CMS [4] sont deux expériences general-purpose pour étudier les collisions p-p. Leur but principal est l'observation de la particule appelée "Higgs", dont la masse n'est pas connue avec certitude. Pour pouvoir étudier cette particule, une grande luminosité est nécessaire à cause de la difficulté statistique de la produire et d'en assurer une détection efficace. À la luminosité prévue de  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>, 20 collisions inélastiques p-p auront lieu au centre de ces deux expériences chaque 25 ns, ce qui signifie environ  $10^9$  collisions par seconde. Malgré cette impressionnante fréquence des collisions, on prévoit que seulement 10-400 Higgs seront clairement visibles par année (le nombre exact dépend de la masse de cette particule).

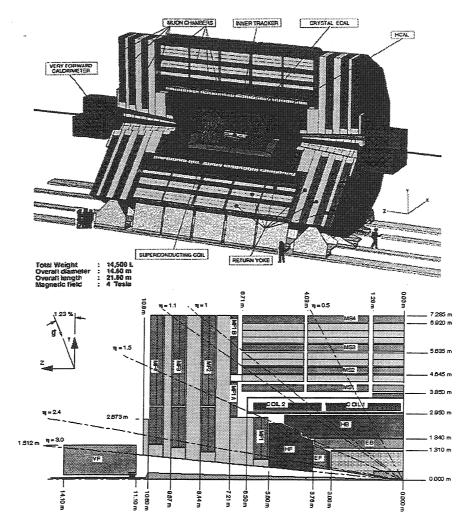

Les expériences ATLAS et CMS, énormes systèmes d'un poids respectif d'environ 7000 et 14000 tonnes, seront composées de plusieurs détecteurs spécialisés à une tache spécifique pour la reconstruction de la physique de la collision. Leur structure prévoit une partie très proche au point de collision (*central tracker*) pour reconstruire la trajectoire des particules, une partie pour la mesure de leur énergie (calorimètres électromagnétique et hadronique) et une partie pour la détection des muons (détecteur à muons). Tous les détecteurs se trouveront dans un fort champ magnétique de 2 à 4 T, nécessaire pour l'identification de l'énergie et de la charge des particules. La Figure 1.1 montre deux vues de l'expérience CMS.

Le débit de 10<sup>9</sup> collisions par seconde, qui se traduit en un pareil débit de signaux délivrés par les détecteurs, doit être fortement réduit (d'un facteur 10<sup>7</sup>) pour l'analyse des données: le débit maximum pour l'analyse off-line sera de 100 Hz. Par conséquent, une partie importante des circuits électroniques qui réalisent les fonctions d'amplification, mise en forme, stockage et traitement des données devront être positionnés près des détecteurs correspondants. La communication entre circuits situés en positions différentes dans l'expérience constituera la base pour le système de trigger, responsable du choix des données à enregistrer pour l'analyse off-line.

À cause du haut débit des collisions, la dose intégrée et la fluence de particules dans ATLAS et CMS seront beaucoup plus importantes que dans les autres deux expériences. La survie aux radiations des détecteurs et de l'électronique les plus proches au point de collision pose par conséquent problèmes, et dans certaines régions les plus internes des expériences une électronique durcie devra nécessairement être utilisée. Pour cette raison, seul l'environnement radiatif de ATLAS et CMS sera décrit dans le prochain paragraphe.

Figure 1.1: Deux vues de CMS (Compact Muon Solenoid) [4]. Dans les acronymes qui indiquent les différentes parties de l'expérience, la lettre B (Barrel) caractérise les détecteurs en symétrie radiale tandis que la lettre F (Forward) indique les détecteurs qui se trouvent à haute pseudorapidité.  $IB="Barrel\ Inner\ Detector"$  (tracker central),  $IF="Forward\ Inner\ Detector"$ ;  $EB="Barrel\ Electromagnetic\ Calorimeter"$  (calorimètre électromagnétique),  $EF="Forward\ Electromagnetic\ Calorimeter"$ ;  $HB="Barrel\ Hadronic\ Calorimeter"$  (calorimètre hadronique),  $HF="Forward\ Hadron\ Calorimeter"$ ;  $MS="Barrel\ Muon\ Station"$  (chambres à muon),  $MF="Forward\ Muon\ Station"$ ;  $VF="Very\ Forward\ Calorimeter"$  (calorimètre qui devrait être installé à pseudorapidité très élevée,  $\eta>3$ ). Dans la figure, "Superconductive Coil" est l'aimant supraconducteur qui produira le champ magnétique.

#### 1.2 L'environnement radiatif à ATLAS et CMS

L'environnement radiatif des expériences à LHC est dominé par la production de particules énergétiques secondaires au point de collision p-p. Les détecteurs et l'électronique associée devront être en mesure de fonctionner à long terme (10 années) dans cet environnement, d'où la nécessité de prévoir avec certitude le niveau de dose

intégrée et la fluence de particules (hadrons chargés, photons et neutrons) dans chaque partie des expériences. Dans ce but, un grand travail a été effectué pour développer et perfectionner des outils de simulation: à ce jour, grâce à des programmes de simulations tels que DTUJET [5], FLUKA [6] et GCALOR [7], l'environnement radiatif est bien connu.

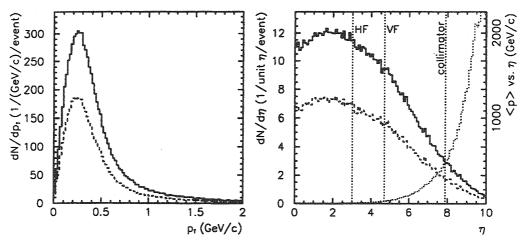

La plupart des particules secondaires produites dans la collision, surtout les plus énergétiques, ont une direction proche de celle des faisceaux de protons. La distribution angulaire des particules secondaires n'est pas exprimée en fonction de l'angle  $\theta$  entre la direction de la particule secondaire et le faisceau de protons mais en fonction de la pseudorapidité  $\eta$ . La relation entre la pseudorapidité et l'angle  $\theta$  est [8]:

$$\eta = -\ln\left(\tan\frac{\theta}{2}\right) \tag{1.1}$$

La distribution des particules en énergie est normalement exprimée en fonction de l'impulsion p ou de sa projection en direction orthogonale au faisceau (p<sub>T</sub>):

$$E \approx p = \frac{p_T}{\sin \theta} \tag{1.2}$$

Avec ces notations, la distribution angulaire et en énergie des particules secondaires produites par une collision p-p en CMS est montrée en Figure 1.2.

Figure 1.2: Distribution énergétique (à gauche) et angulaire (à droite) des particules secondaires produites par une collision p-p. La ligne continue indique toutes les particules, la ligne hachurée les particules chargées. Dans la figure de droite, la ligne pointillée représente l'impulsion (qui est liée à l'énergie à travers l'équation (1.2)) en fonction de la pseudorapidité, et montre que les particules plus énergétiques sont émises presque en parallèle aux faisceaux de protons ( $\eta$ >6 signifie  $\theta$ <0.28 radians) [4].

#### 1.2.1 Central tracker

Le but de cette partie centrale de l'expérience est la reconstruction des trajectoires des particules produites dans les collisions p-p. À cause de sa proximité au point de collision, le flux de particules dans le central tracker sera très élevé et pour pouvoir

accomplir sa tâche il doit être conçu avec une haute granularité (ce qui signifie que les éléments détecteurs sont très petits et nombreux), une haute résolution spatiale et temporelle et avec des matériaux légers. Cette dernière exigence naît du besoin d'avoir une faible probabilité de conversion d'énergie en photons et un faible bremsstrahlung des électrons.

Les détecteurs choisis seront pour la plupart en silicium (pixels et *microstrips*), mais aussi à gaz (MSGC et TRT, *Transition Radiation Tracker*). Pour ce qui concerne l'électronique associée, les exigences de basse puissance, haute densité et complexité peuvent être satisfaites seulement par des technologies microélectroniques sur silicium. La plupart des circuits de *front-end* (circuits mixtes analogiques-numériques) intégrés à l'intérieur du *tracker*, qui réaliseront une lecture analogique ou binaire des signaux délivrés par les détecteurs, auront une taille de 70 à 100 mm² et seront intégrées en technologie bipolaire, CMOS ou BiCMOS.

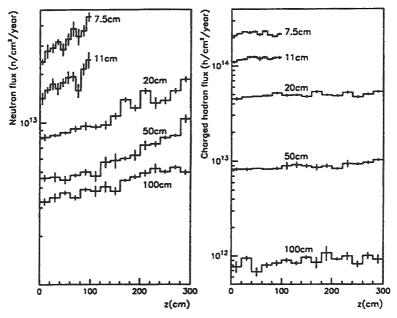

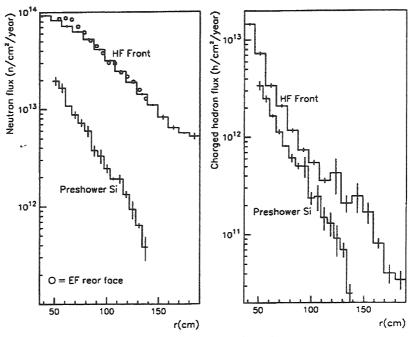

Figure 1.3: Flux (par année) de neutrons et de hadrons chargés à différentes distances radiales du point de collision dans le "central tracker" de CMS. Les neutrons proviennent des interactions des particules chargées dans les calorimètres et dans le collimateur des faisceaux de protons qui se trouve à très haute pseudorapidité: pour cette raison le flux de neutrons est plus important dans la région "forward" (haute pseudorapidité, z élevé dans la figure). Le flux de hadrons chargés diminue approximativement avec le carré de la distance (r), mais le flux des particules les moins énergétiques (dont l'effet sur les détecteurs et l'électronique est plus important car elles peuvent déposer plus d'énergie) diminue avec la distance à cause du fort champ magnétique de 2 à 4 T [4].

Cette partie de l'expérience sera exposée au flux de particules provenant du point de collision et aux neutrons produits par l'interaction de ces particules dans les calorimètres. Le flux de neutrons est fortement dépendant du matériau qui compose le

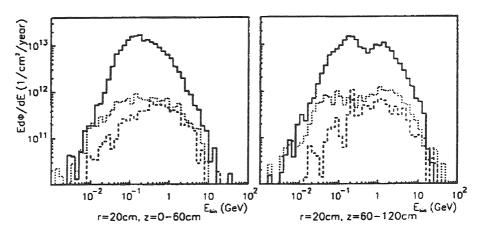

calorimètre électromagnétique (ECAL) et des caractéristiques des modérateurs, et cela en intensité et en spectre énergétique. Les résultats des simulations concernant le flux de neutrons et hadrons chargés dans CMS sont résumés en Figure 1.3. Le flux de hadrons chargés est dominé par les pions ( $\pi$ ) avec une énergie entre 10 MeV et 10 GeV, comme montré en Figure 1.4 pour une distance radiale de 20 cm.

Figure 1.4: Composition énergétique du spectre des particules secondaires chargées dans le "central tracker" de CMS, à une distance radiale de 20 cm [4]. La ligne continue indique le flux de pions ( $\pi^{\pm}$ ), qui est le dominant; les lignes pointillée et hachurée représentent, respectivement, les protons (avec leurs antiparticules, les antiprotons,  $\overline{p}$ ) et les kaons ( $K^{\pm}$ ).

L'électronique intégrée est sensible surtout à l'énergie de ionisation déposée par les particules chargées et les photons. Pour cette raison, il est utile d'exprimer en dose intégrée l'environnement radiatif. Le tableau I.1 résume, à distance radiale croissante du point de collision, le type de détecteur installé dans chaque expérience et le niveau prévu de dose intégrée par année [2].

Tableau I.1: Dose intégrée par année à l'intérieur du "central tracker" pour ATLAS et CMS. Le type de détecteur qui sera installé dans les deux expériences est aussi indiqué. La dose intégrée ne change pas en s'éloignant en direction z (voir les coordonnés en Figure 1.1) jusqu'à l'extremité du détecteur [4].

| R (cm) | Type de détecteur<br>ATLAS | CMS       | Dose intégrée<br>(rad/année) |

|--------|----------------------------|-----------|------------------------------|

| 7.5    | Si pixels                  |           | 9•10 <sup>6</sup>            |

| 11     |                            | Si pixels | 6·10 <sup>6</sup>            |

| 20     | GaAs/Si strips             | Si strips | 2.7•106                      |

| 30     | Si strips                  | Si strips | 1.5•10 <sup>6</sup>          |

| 50     | TRT                        | MSGC      | 5.5·10 <sup>5</sup>          |

| 100    | TRT                        | MSGC      | 8·10 <sup>4</sup>            |

#### 1.2.2 Calorimètres

On peut distinguer deux types fondamentaux de calorimètres: les calorimètres électromagnétiques (ECAL) qui se trouvent le plus près du point de collision, tout de suite après le *tracker*, et les calorimètres hadroniques (HCAL) (voir Figure 1.1).

ECAL utilise, selon l'expérience considérée, des détecteurs à argon liquide (LAr) ou des détecteurs en cristaux scintillateurs (PbWO<sub>4</sub>). Dans le projet de CMS, un détecteur en silicium appelé *preshower* est prévu avant la partie en cristaux scintillateurs. Si le détecteur à argon liquide est insensible aux effets des radiations, les cristaux en PbWO<sub>4</sub> perdent leur efficacité optique, donc le signal délivré diminue avec l'irradiation. Un dopage avec du nobium (Nb) semble donner à ces cristaux un meilleur durcissement.

HCAL est constitué par des briques d'un matériau plastique scintillateur, dont la lumière émise est transférée en longueur d'onde par des fibres WLS (Wave Length Shifting fibers). L'irradiation cause une diminution de la quantité de lumière produite, mais le choix du matériau plastique peut permettre un fonctionnement efficace pendant 10 années dans l'environnement radiatif prévu. Dans ATLAS, pour la partie forward qui est la plus exposée aux radiations, des couches de détecteurs en LAr seront utilisées en alternance avec des couches en matériaux absorbeurs.

L'électronique associée aux détecteurs pour les calorimètres, comparée à celle nécessaire pour le tracker, est moins exigeante en puissance et densité. Les signaux des cristaux scintillateurs seront amplifiés par des photodétecteurs (APD, silicon Avalanche PhotoDiode), tandis que des circuits amplificateurs en technologie silicium ou arséniure de gallium (GaAs) seront utilisés pour les détecteurs LAr. Dans les deux cas, les signaux, une fois amplifiés, seront stockés dans l'attente du trigger et convertis en signaux numériques par des circuits intégrés en silicium ou par des microsystèmes spécifiquement développés.

Il y a une différence considérable de flux de particules dans les calorimètres selon leur position dans l'expérience. Les détecteurs *forward* seront exposés au flux de particules plus élevé. Ce flux, toujours dominé par les neutrons, pourra atteindre le niveau de  $10^{14}$  cm<sup>-2</sup> par année à une distance radiale de 50 cm. Les neutrons dominent car les matériaux des calorimètres produisent beaucoup de neutrons quand ils sont traversés par des hadrons rapides. Le flux de neutrons et de hadrons chargés pour CMS est montré en Figure 1.5 pour le calorimètre hadronique et pour le *preshower* du calorimètre électromagnetique. La dose intégrée suit la même géométrie, les détecteurs "forward" étant les plus exposés, et décroît fortement à l'intérieur du calorimètre lorsque l'on s'éloigne du maximum des cascades de particules (électromagnétiques ou hadroniques), comme montré pour le flux de hadrons chargés en HCAL en Figure 1.5. Dans les régions les plus exposées une dose de 300 krad par année peut être atteinte, mais la plus grande partie du calorimètre, celle qui couvre les faibles pseudorapidités en

symétrie cylindrique autour du point de collision (barrel), reçoit entre 0.1 et 10 krad par année.

Figure 1.5: Flux de neutrons et de hadrons chargés dans le détecteur "preshower" et dans la région "forward" du calorimètre hadronique de CMS (du coté le plus proche du point de collision, indiqué "front"). Dans la figure de gauche, les cercles indiquent le flux dans la partie extérieure du calorimètre électromagnétique, en présence d'un matériau modérateur entre les parties hadronique et électromagnétique [4].

#### 1.2.3 Détecteur à muons

Le détecteur à muons est la partie qui se trouve le plus à l'extérieur dans les expériences, et son but est la détection des muons qui est essentielle pour fabriquer les triggers de lecture nécessaires aux autres détecteurs et pour compléter le bilan énergétique des collisions. Ce détecteur est constitué par des chambres à muons de plusieurs types: les RPC (Resistive Plate Chambers) et TGC (Thin Gap Chambers) assurent le trigger de base, tandis que les MDT (Monitored Drift Tubes) et les CSC (Cathode Strip Chambers) servent à la détection de précision des muons. L'électronique associée est composée d'une partie analogique pour l'amplification des signaux et d'un convertisseur analogique-numérique (convertisseur flash ou systèmes de conversion TDC, "Time-to Digital", selon l'architecture choisie).

L'environnement radiatif dans cette région éloignée du point de collision est caractérisé par un flux de  $10^{11}$ - $10^{12}$  neutrons pas année et par une dose intégrée de 10 krad par année, cela dans les parties les plus exposées (forward). Pour ce qui concerne l'électronique, l'utilisation d'une technologie microélectronique tolérante aux effets des radiations est suffisante, sans devoir utiliser des composants spécialement durcis.

#### 1.3 Synthèse

Dans ce chapitre, les quatre expériences de physique du LHC, le nouveau projet pour un accélérateur de particules du CERN, ont été présentées. A cause de la grande énergie des particules accélérées et du haut débit des collisions, l'environnement radiatif des quatre expériences posera des problèmes à la survie des détecteurs de particules et de l'électronique associée. Cet environnement radiatif sera dominé par les hadrons produits par l'interaction des faisceaux accélérés (principalement pions, mais aussi protons et kaons) et par les neutrons produits par l'interaction des hadrons dans les matériaux composants les détecteurs.

L'environnement radiatif des expériences ATLAS et CMS, qui est assez similaire, peut être décrit séparément pour la partie centrale, les calorimètres et les détecteurs à muons. La partie centrale de l'expérience, appelé *central tracker* et visant à la reconstruction des trajectoires des particules, sera exposée au flux de particules provenant du point de collision et aux neutrons produits par l'interaction de ces particules dans les calorimètres. La dose intégrée annuelle pourra varier entre 80 krad (à 1 m du point de collision) et 9 Mrad (à 7.5 cm), tandis que la fluence de neutrons pourra atteindre dans les 10 années de fonctionnement de la machine les 5•10<sup>14</sup> neutrons/cm<sup>2</sup> (à 7.5 cm).

Pour ce qui concerne les calorimètres électromagnétique (ECAL) et hadronique (HCAL), une différence considérable de flux existe selon leur position dans l'expérience, les détecteurs *forward* étant exposés aux flux les plus importants. Ces flux seront dominés par les neutrons, car les matériaux des calorimètres produisent beaucoup de neutrons quand ils sont traversés par des hadrons rapides. Un flux de  $10^{14}$  neutrons/cm<sup>2</sup> par année pourra être atteint dans les régions les plus exposées. La dose intégrée pourra aussi varier considérablement, entre 0.1 krad et 300 krad par année.

Les détecteurs à muons, qui se trouvent très éloignés du point de collision, seront exposés à des fluences de  $10^{11}$ - $10^{12}$  neutrons/cm<sup>2</sup> et à une dose intégrée annuelle inférieure à 0.5 krad.

Les détecteurs de particules et l'électronique intégrée devront être capables de survivre pendant 10 ans à cet environnement. La qualification des composants électroniques et le choix des technologies en vue de leur utilisation dans cet environnement, occuperont un rôle fondamental dans la construction des expériences. Pour cela faire, il est nécessaire de connaître les effets des rayonnements sur les dispositifs et les méthodologies de test à appliquer. Les effets sur les transistors MOS et bipolaires seront traités, respectivement, au chapitre 2 et à l'Annexe II, tandis que le chapitre 3 illustrera les méthodologies de test.

#### Chapitre 2

# Effets des rayonnements sur les transistors MOS et méthodologies de durcissement

Les transistors MOS sont des dispositifs dans lesquels la conduction se passe à l'interface silicium—oxyde de silicium. Le substrat en silicium est en général assez dopé pour ne pas ressentir les effets de déplacement (voir annexe 1) jusqu'à des flux intégrés de l'ordre de quelques  $10^{15} {\rm cm}^{-2}$ . Ces effets peuvent donc être ignorés dans l'examen des conséquences de l'exposition à des rayonnements des technologies MOS, et ne seront par conséquent pas considérés dans ce chapitre. Les effets non récurrents (Single Event Phenomena: SEP) et de dose intégrée sont au contraire très importants dans les transistors MOS et seront traités dans ce qui suit.

#### 2.1 Dose intégrée

La description complète des effets de la dose totale déposée dans les structures MOS est bien au delà des buts de ce travail, surtout pour ce qui concerne l'étude au niveau microscopique des défauts introduits ou activés par les radiations ionisantes. Quelques publications sur ce sujet se trouvent dans les références [2–35].

#### 2.1.1 Centres de défaut dans l'oxyde de silicium et à l'interface Si-SiO2

Pour mieux comprendre l'effet de la dose totale dans les transistors MOS, il est utile d'introduire brièvement la nature de quelques défauts normalement présents dans l'oxyde de silicium et à l'interface Si-SiO<sub>2</sub>. Ces défauts introduisent des états énergetiques localisés dans la bande interdite et agissent comme des centres de piégeage pour les porteurs (électrons dans la bande de conduction, trous dans la bande de valence).

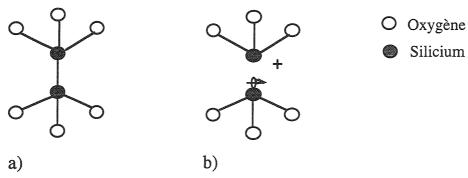

Dans l'oxyde de silicium, le centre de défaut le plus connu est le centre de type E'. Ce centre a un précurseur qui n'est pas actif en condition normale, mais qui est activé par le rayonnement sous forme de centre de piègeage pour charges positives. Le précurseur est déjà présent dans l'oxyde avant l'irradiation, et est illustré dans sa variété la plus répandue en Figure 2.1. Il constitue l'origine physique des pièges dans l'oxyde (oxide traps en anglais).

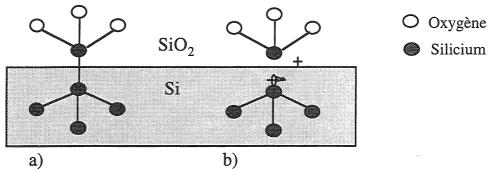

L'interface  $Si-SiO_2$  est un lieu de transition entre un matériau cristallin (Si) et un matériau amorphe ( $SiO_2$ , l'oxyde thermique de grille du transistor). La brusque transition entre les deux matériaux et l'interruption de la structure cristalline du silicium donnent lieu à des défauts, qui se situent à l'interface ou à quelques angströms de

l'interface, dont le plus répandu est le centre P<sub>b</sub>. L'état d'interface actif est illustré en Figure 2.2, avec son précurseur.

Figure 2.1: Le centre E' dans les deux états: a) précurseur, b) état actif.

Figure 2.2: Le centre P<sub>b</sub> dans les deux états: a) précurseur, b) actif.

Les états d'interface, au contraire des E' qui correspondent toujours à niveaux énergétiques donneurs (chargés toujours positivement), peuvent être donneurs, accepteurs ou neutres. Leur charge nette peut donc être positive ou négative selon leur position par rapport au niveau de Fermi. Les défauts  $P_b$  sont responsables des pièges à l'interface (interface traps en anglais).

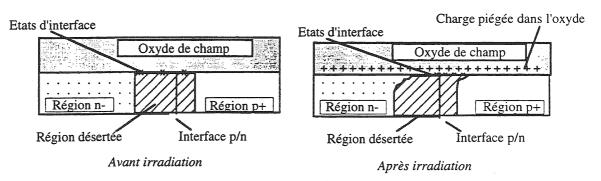

#### 2.1.2 Formation de la charge piégée dans l'oxyde et à l'interface

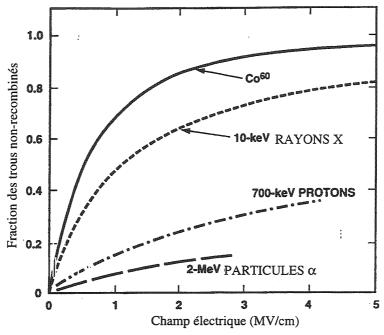

Lors de leur passage dans la structure MOS, les radiations ionisantes produisent sur leur chemin des paires électron-trou. Une partie de ces paires se recombine, mais le champ électrique normalement appliqué au dispositif dissocie le reste. Le pourcentage de charges non recombinées est fonction du type de rayonnement, du matériau et de l'intensité du champs électrique. Après formation, et sous l'effet du champ électrique, électrons et trous se déplacent dans l'oxyde en directions opposées. Les électrons ont une mobilité beaucoup plus élevée que les trous, et quittent l'oxyde en quelques picosecondes, les trous se trouvant encore presque au point de génération. La migration des trous dans l'oxyde est expliquée avec le modèle du transport par sauts des polarons, et leur vitesse augmente avec le champ appliqué et la température.

Dans leur migration vers l'interface, les trous trouvent des centres de défauts neutres, de type E'. Une fraction variable des trous produits par ionisation est piégée dans ces défauts, et donne naissance à une charge fixe positive (Qot). Cette charge subit un lent processus de neutralisation avec deux mécanismes de récombinaison: avec des des électrons venant du substrat de silicium par effet tunnel et avec des électrons de la bande de valence de l'oxyde qui ont été excités thermiquement. La distribution spatiale et énergétique des pièges a une grande influence sur l'efficacité absolue et relative des deux processus.

On observe aussi une accumulation à l'interface de pièges induits par les rayonnements. Une corrélation entre cette accumulation et le nombre de centres précurseurs de type  $P_b$  a été trouvée dans l'expérience, mais le mécanisme de formation des défauts à l'interface n'est à ce jour pas encore tout à fait compris. Les deux modèles dominants sont le WML (Winokur-McLean) [20, 21] et le (HT)<sup>2</sup> (Hole Trapping/Hydrogen Transport) [22, 23]. Au contraire des défauts dans l'oxyde, les défauts à l'interface ne subissent pas une neutralisation à température ambiante.

Il est important de remarquer que la polarisation du dispositif pendant l'exposition aux rayonnements détermine la cinétique de la formation des défauts et du piégeage.

#### 2.1.3 Conséquences sur les transistors MOS

Le comportement d'un MOSFET vis-à-vis de la dose totale est lié à la quantité et à la cinétique de piégeage et dépiégeage des charges aux interfaces Si-SiO<sub>2</sub>. Les effets principaux sur les caractéristiques électriques du transistor sont les suivants:

- -le déplacement de la tension de seuil du transistor

- -la diminution de la mobilité des porteurs dans le canal, et par conséquent de la transconductance

- -l'augmentation du bruit du transistor

- -l'augmentation des courants de fuite.

Les trois premiers effets sont liés aux phénomènes qui se produisent dans l'oxyde de grille du transistor sous l'effet de l'irradiation.

#### Déplacement de la tension de seuil

Le déplacement de la tension de seuil est une conséquence du piégeage de charge qui a lieu dans l'oxyde et dans les états d'interface. La charge piégée dans l'oxyde est toujours constituée par des trous: il s'agit donc de charge positive. L'effet de cette charge est différent pour les transistors NMOS ou PMOS: elle diminue le seuil du NMOS et augmente (en valeur absolue) le seuil du PMOS. Pour ce qui concerne les défauts à l'interface, leur état de charge est dépendant de leur niveau énergétique

relativement au niveau de Fermi à l'interface: ils sont chargés négativement dans le NMOS (piégeage d'électrons) et positivement dans le PMOS (piégeage de trous). La conséquence est une augmentation de la tension de seuil (en valeur absolue) pour les NMOS comme pour les PMOS.

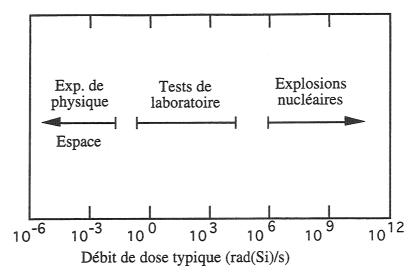

La dynamique du piégeage est différente pour la charge dans l'oxyde et dans les états d'interface, ce qui implique que le déplacement du seuil dépend de la durée et du débit de dose de l'irradiation. Cela pose le problème de définir des procédures de mesure en laboratoire qui puissent donner avec confiance des prévisions du comportement des dispositifs dans l'environnement radiatif réel (espace, accélerateurs de particules) où le débit de dose est très faible. Ce problème sera examiné en détail dans la suite.

En général, la formation des états d'interface a une dynamique plus lente que le piégeage des trous dans l'oxyde. Dans les mesures d'irradiation courantes (débit de dose supérieur à 1 rad/sec), elle continue dans le temps qui suit l'exposition. Tous les phénomènes qui caractérisent l'évolution des paramètres du transistor après l'exposition se regroupent sous le terme anglais de *annealing* (recuit).

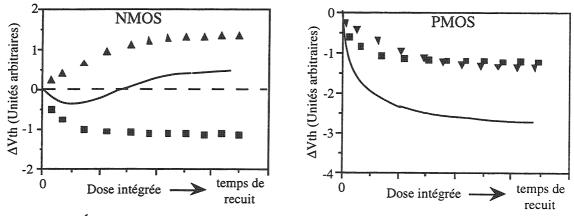

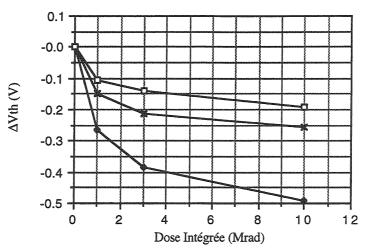

Dans la Figure 2.3, l'évolution typique du seuil des transistors NMOS et PMOS est montrée, et les contributions relatives des charges piégées dans l'oxyde et à l'interface sont illustrées. On distingue l'évolution en fonction de la dose intégrée et du temps de recuit, le débit de dose étant typique des irradiations en laboratiore. Dans le cas du PMOS, le seuil continue à augmenter en valeur absolue avec l'irradiation et l'annealing. Le seuil du NMOS subit le phénomène appelé en anglais rebound. Le piégeage de trous, plus rapide, provoque une diminution du seuil au début de l'exposition. L'effet du piégeage dans les états d'interface se montre seulement plus tard et tend à augmenter le seuil. Le déplacement du seuil, après avoir été négatif, devient positif. A dose intégrée élevée il y a un effet de saturation des charges piégées dans l'oxyde, et les états d'interface dominent l'évolution du seuil.

Figure 2.3: Évolution typique de la tension de seuil  $V_{th}$  (ligne continue) des transistors NMOS et PMOS avec la dose intégrée et le temps d'annealing (recuit). Les contributions relatives des charges piégées dans l'oxyde (carrés) et à l'interface (triangles) ont été séparées. Les unités pour  $\Delta V_{th}$ , la dose intégrée et le temps de recuit sont arbitraires car elles dépendent fortement de la technologie.

La polarisation de la grille des transistors NMOS et PMOS a une influence importante dans la dynamique de formation ou d'activation des défauts. Il a été démontré qu'il existe une corrélation entre la migration de trous (ou plus généralement de porteurs de charge positive) dans l'oxyde et la formation d'états de défauts à l'interface. Dans les transistors NMOS, la polarisation positive appliquée à la grille favorise la migration des charges positives vers l'interface où elles peuvent contribuer à la création de défauts à l'interface. La tension positive appliquée sur la grille du transistor NMOS pour le rendre conducteur est par conséquent une sorte de "pire cas" sous irradiation. A l'inverse, pour le PMOS la tension négative appliquée sur la grille pour le rendre conducteur a pour effet de réduire la formation des défauts à l'interface sous irradiation.

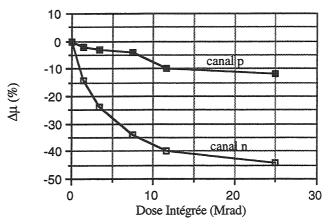

#### Diminution de la mobilité

La formation des pièges à l'interface est responsable de la diminution de la mobilité des porteurs dans le canal de conduction. Pour les mêmes raisons que celles énoncées plus haut dans le cas de la tension de seuil, la dégradation de mobilité est plus forte pour le NMOS (polarisé positivement) que pour le PMOS (polarisé négativement). La transconductance, directement liée à la mobilité, diminue aussi avec l'exposition aux rayonnements. Cette dégradation provoque une diminution de la vitesse dans les circuits numériques et est particulièrement indésirable dans les circuits analogiques, dont les performances dynamiques et de bruit sont souvent déterminés par la transconductance.

#### Augmentation du bruit

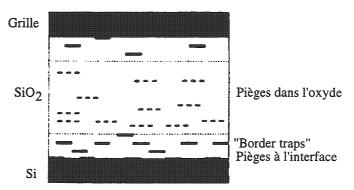

Le bruit des transistors est un paramètre important principalement pour les applications analogiques. La plupart des applications étant numériques, il n'y a pas eu beaucoup d'attention accordée au bruit des technologies durcies et à son évolution avec l'exposition aux rayonnements. Le groupe le plus actif dans ce domaine est sans doute celui de *Sandia National Laboratories*, au Nouveau Mexique. Les travaux de recherche de ce groupe ont été focalisés sur l'étude du bruit 1/f, plutôt à basse fréquence, et à la corrélation de ce bruit avec quelques types de pièges créés par l'irradiation. A la suite de ces travaux, une nouvelle catégorie de pièges, nommée "border traps" par Fleetwood [24–27], a été introduite. La localisation spatiale de ces pièges est illustrée en Figure 2.4.

Figure 2.4: Diagramme schématique [24] de la localisation spatiale des défauts dans les structures MOS. Les "border traps" sont localisée dans les premiers  $\approx 3$  nm de l'oxyde, et peuvent rapidement échanger leur charge avec le silicium (ou la grille).

Il s'agit de défauts dans l'oxyde, donc de type E', qui se trouvent à proximité de l'interface et de toute façon assez près pour pouvoir échanger des porteurs avec le canal. Ils sont responsable du bruit 1/f et peuvent être partagés en états rapides (temps de commutation entre  $10^{-6}$  s et 1 s) et états lents (temps de commutation supérieur à 1 s).

Nous avons vu que un des effets des rayonnements est d'activer les états précurseurs des défauts E'. Par conséquent, l'irradiation augmente le bruit 1/f des transistors MOS. Les expériences ont montré une bonne corrélation entre l'augmentation du bruit et le piégeage dans l'oxyde, confirmant la théorie. Ce résultat suggère que les techniques de durcissement technologique développées pour réduire le piégeage des trous dans l'oxyde suite aux rayonnements peuvent être utilisées pour diminuer le bruit 1/f des transistors MOS. Plus spécifiquement, la réduction des vacances d'oxygène dans l'oxyde peut réduire de façon importante le bruit 1/f des transistors MOS, ce qui est utile même dans les applications non durcies.

#### Courants de fuite

Même si le durcissement "naturel" des oxydes de grille commerciaux augmente suite à la réduction des épaisseurs d'oxyde (oxydes ultra-minces) [28, 29], les oxydes latéraux et de champ restent souvent très sensibles aux effets des rayonnements. Une dose relativement faible (de l'ordre de 10 krad dans la plupart des technologies commerciales) peut induire suffisamment de charge dans l'oxyde latéral pour provoquer le non fonctionnement du circuit intégré.

Les oxydes latéraux et de champ sont beaucoup plus épais que les oxydes de grille, typiquement de l'ordre de 200-1000 nm [30]. Au contraire des oxydes thermiques de grille, ils sont généralement produits avec une large variété de techniques de déposition et leur caractéristiques de piégeage ne sont pas contrôlées, pouvant donc être très différentes de celles des oxydes thermiques [31, 32].

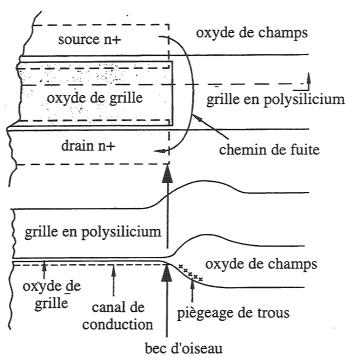

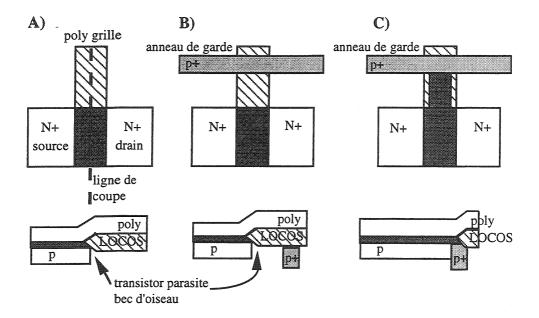

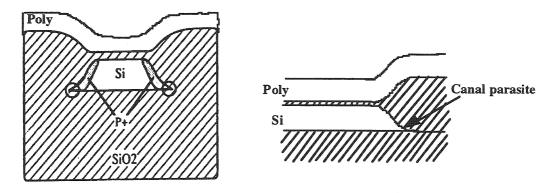

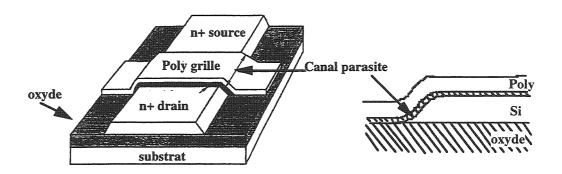

Les oxydes latéraux peuvent être responsables, sous irradiation, de courants de fuite source-drain à travers l'activation d'une structure latérale parasite, telle que le transistor en forme de "bec d'oiseau" (*bird's beak*) lié à la transistion LOCOS-oxyde mince de grille. On peut le modéliser comme un transistor parasite d'oxyde épais [33] en parallèle avec le transistor principal et partageant sa grille avec lui. Sa structure classique est montrée en Figure 2.5.

Figure 2.5: Le transistor parasite dû à l'oxyde latéral [1]. Le chemin de fuite est causé par la charge positive piégée dans la zone de transition entre oxyde épais et oxyde de grille.

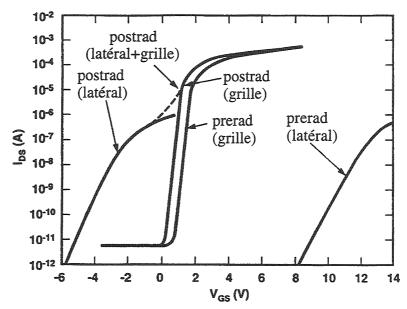

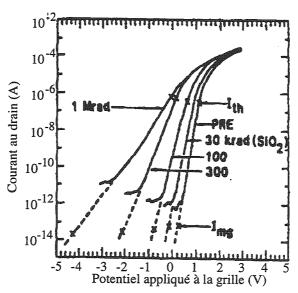

Seuls les transistors à canal n sont sensibles aux courants de fuite. En fait, les trous piégés dans l'oxyde latéral suite à l'irradiation tendent à diminuer le seuil du transistor latéral parasite (sur substrat de type p). Si l'accumulation de charge dans l'oxyde latéral est suffisante, il peut y avoir formation du canal de conduction du transistor parasite [34] et par conséquent le transistor ne peut plus être commuté en position "off". Cette situation est illustrée en Figure 2.6 où, même à une tension de grille nulle, un courant source-drain est présent. Cela accroît largement la consommation statique du circuit intégré et peut aussi, dans les cas extrêmes, empêcher son fonctionnement.

Les oxydes de champ sont topologiquement, voir physiquement, différents des oxydes latéraux. Ce sont des isolants fondamentalement épais, et leur rôle est de séparer les lignes d'interconnections (poly, métal) de la surface du silicium. La sensibilité à l'irradiation provient, pour les structures à oxyde épais sur substrat de type p, de la possibilité d'inversion en surface du silicium, permettant des chemins de fuite induits entre les sources ou les drains de transistors adjacents ou entre caissons [35]. La situation peut être aggravée lorsqu'une ligne d'interconnexion existe au-dessus de ce chemin de fuite potentiel, car elle agit alors comme une grille virtuelle et peut provoquer

ou augmenter le courant de fuite. La conséquence de ce courant est l'augmentation de la consommation statique, parfois la perte de fonctionnalité du circuit intégré.

Figure 2.6: Courbe I–V du transistor principal (de grille) et du transistor latéral parasite [1]. Le courant de fuite du transistor principal est engendré, après irradiation, par le déplacement du seuil du transistor parasite. Les charges piégées dans l'oxyde épais latéral sont responsables de ce déplacement.

## 2.2 Phénomènes non récurrents (Single Event Phenomena: SEP)

On utilise le nom de phénomènes non récurrents pour comprendre les effets istantanés induits par les ions lourds ou les protons de haute énergie. Les SEP sont soit destructeurs, soit réversibles, provoquant une défaillance fonctionnelle temporaire ou définitive du composant. Les SEP se produisent de manière non récurrente dans le temps et l'espace en fonction de la fluence des ions, au contraire des effets de la dose totale dont les dommages sont cumulés et provoquent une dégradation progressive.

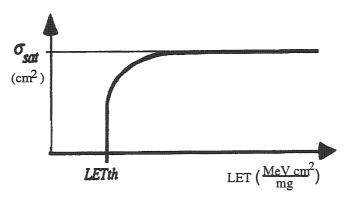

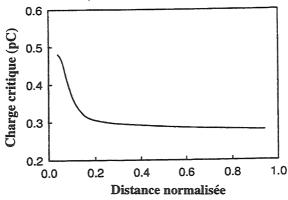

La sensibilité des transistors aux SEP est caractérisée par leur section efficace en fonction du transfert linéaire d'énergie (Linear Energy Transfer: LET). Le LET est l'énergie transférée moyenne ( $\Delta E_t$ ) per unité de longueur de trace ( $\Delta x$ ) normalisée à la densité  $\rho$  du matériel: LET= $\Delta E_t/(\rho \cdot \Delta x)$ . La section efficace  $\sigma$  exprime le nombre d'événements (SEP) par unité de fluence, et une courbe  $\sigma$ = $\sigma$ (LET) typique pour un circuit intégré est montrée en Figure 2.7.

Figure 2.7: Section efficace de SEP en fonction du LET des ions.

Le LET<sub>th</sub> (seuil, LET threshold) est le LET minimum créant un effet singulier au niveau du point le plus sensible dans le composant: seules les particules avec LET supérieur peuvent produire des SEP. Les composants ayant un LET<sub>th</sub> inférieur à 10–20 MeVcm<sup>2</sup>/mg sont considérés sensibles. La valeur asymptotique de  $\sigma$  lorsque le LET augmente,  $\sigma_{sat}$ , exprime la surface totale sensible aux SEP du composant. Les composants avec  $\sigma_{sat}$  entre  $10^{-3}$  et  $10^{-1}$  cm<sup>2</sup> sont considérés comme sensibles aux aléas logiques (changement de l'état logique d'un élement de mémoire).

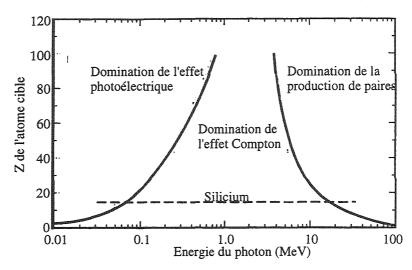

#### 2.2.1 Effets des ions lourds

Les ions lourds transfèrent leur énergie à la matière surtout par ionisation et par collisions nucléaires élastiques. Au début du parcours de l'ion dans la matière, l'ionisation constitue le mode principal de transfer d'énergie, ce qui provoque un progressif ralentissement de l'ion. Ensuite, le ralentissement et l'arrêt sont dues à des collisions nucléaires, qui produisent des déplacements des atomes de la cible et créent des défauts de structure. Lorsqu'un ion traverse une zone désertée, la haute concentration de paires électron-trou, suite à la ionisation, forme un plasma très dense qui déforme la zone de déplétion originelle dans un volume cylindrique qui suit la trajectoire de l'ion. Cela constitue une région appelée "funnel", qui s'étend dans le substrat (ou dans le caisson). La charge présente dans la cette région peut être collectée rapidement à l'électrode sous l'effet du champ électrique.

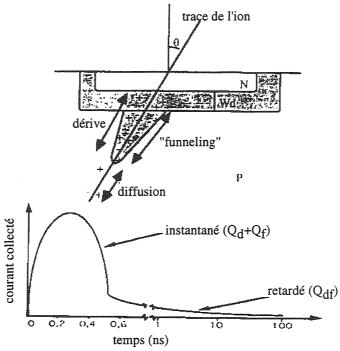

Le courant induit possède deux composantes, l'une instantanée et l'autre retardée. La composante instantanée des charges collectées comporte un courant de dérive  $(Q_d)$  et une aspiration de charges (courant de "funneling",  $Q_f$ ) et a une durée de l'ordre de quelques centaines de picosecondes [36]. La composante retardée, qui est un courant de diffusion  $(Q_{df})$ , peut durer plusieurs centaines de nanosecondes. La zone de funnel et les composantes du courant collecté sont illustrées en Figure 2.8 [37].

Si la zone diffusée dans le substrat de silicium (de type n+ ou p+) traversée par l'ion est un point de mémoire, le courant collecté localement dans cette zone peut changer son état logique (aléa logique, Single Event Upset: SEU). Si au contraire la zone désertée traversée se trouve entre substrat et caisson, ce courant peut amorcer un thyristor parasite (verrouillage maintenu, Single Event Latchup: SEL).

Figure 2.8: Formation d'une zone de "funnel" au passage d'un ion lourd à travers la région désertée d'une jonction, et impulsion de courant qui en résulte [1]. Dans l'impulsion, on distingue le courant instantané qui est dû à la collection des charges par dérive  $(Q_d)$  et funneling  $(Q_f)$ , et le courant retardé de diffusion  $(Q_{df})$ .

Les ions lourds peuvent aussi provoquer une défaillance dans un transistor bipolaire parasite (destruction par échauffement excessif, Single Event Burnout: SEBO), ou encore induire un claquage dans l'oxyde de grille (claquage de grille, Single Event Gate Rupture: SEGR).

#### 2.2.2 Effets des protons

Les protons de haute énergie peuvent également amorcer des SEP. Leur action est plus complexe que celle des ions lourds, et peut être partagée en deux phénomènes différents. Dans le premier, les protons produisent des SEP de la même manière que les ions lourds. En raison du faible LET des protons, inférieur à 1 MeVcm²/mg, leur apport direct dans les SEP est faible ou négligeable pour la plupart des composants, étant donné que seul un petit nombre d'entre eux possède un LET seuil inférieur à 1 MeVcm²/mg.

En ce qui concerne le second mécanisme, les protons interagissent avec les atomes du composant pour créer des ions secondaires possédant des LET beaucoup plus élevés que celui du proton incident (jusqu'à 8–10 MeVcm²/mg pour les composants à base de silicium). Les atomes du composant impliqués dans la réaction sont en majorité ceux du

matériel semiconducteur, mais il peut également s'agir d'atomes de lignes de métallisation, qui sont parfois beaucoup plus lourds. Ce second mécanisme peut être déclenché même par les neutrons.

#### 2.2.3 Aléa logique (Single Event Upset, SEU)

C'est une modification soudaine et réversible de l'état logique d'un point mémoire élémentaire, induite par les charges générées le long de la trace d'un ion lourd (ou d'un ion secondaire produit par le passage d'un proton à haute enérgie) dans le volume d'un composant électronique. Ces charges sont collectées aux électrodes du composant, et leurs effet au niveau du circuit dépend de la sensibilité du noeud touché.

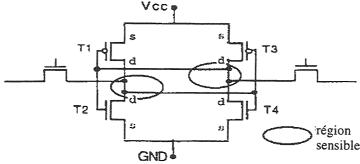

À titre d'exemple, nous examinerons le cas des SRAM à base de deux inverseurs CMOS. Le courant qui suit le passage de l'ion coule toujours de la région dopée n à la région dopée p: le drain d'un transistor n peut donc changer d'état logique seulement s'il se trouve à l'état logique 1. Inversement le drain d'un transistor p est sensible s'il se trouve à l'état logique 0. Pour cette raison, les noeuds les plus sensibles d'un point mémoire SRAM sont les drains des transistors MOS dans l'état bloqué, comme illustré en Figure 2.9. Si du courant est injecté dans le drain à cause du passage d'un ion lourd, la tension de grille connectée peut s'en trouver changée et causer le basculement de l'état logique d'un point mémoire [38].

Le passage d'un ion lourd dans le drain de T1 et T2 ne produit pas obligatoirement un aléa logique. Les charges déposées peuvent en fait suivre deux chemins: traverser le transistor sous tension (supposons T1) et aller vers l'alimentation ou passer sur la grille de T3 et T4. Seulement si ce second processus est plus rapide, et si la charge déposée est suffisante, un SEU peut avoir lieu. Dans les technologies sur substrat p, qui sont les plus répandues, le drain du transistor n est plus sensible à l'aléa logique que le drain du transistor p. Ce dernier se trouve dans le caisson n, dont la jonction avec le substrat est une région désertée qui contribue à la collection des charges au passage de l'ion. La moitié environ des charges de ionisation dans le caisson ne migrent pas au drain p+ et ne contribuent pas à changer son état logique. Au contraire, pour un drain n+, toutes les charges de ionisation peuvent être recueillies au drain.

Figure 2.9: Les noeuds les plus sensibles d'un point mémoire SRAM élémentaire sont les drains des transistors dans l'état bloqué [2].

#### 2.2.4 Verrouillage maintenu (Single Event Latchup, SEL)

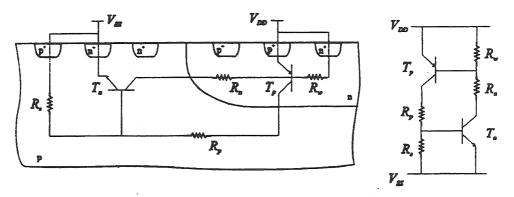

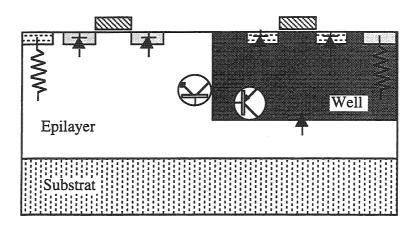

Le verrouillage maintenu est provoqué par l'activation d'un thyristor parasite, qui est intrinsèque dans la structure CMOS sur substrat massif. Cela est montré en Figure 2.10. Le thyristor parasite est représenté par deux transistors bipolaires constitués par les jonctions entre substrat, caisson (well), source et drain. Ces jonctions sont normalement polarisés en inverse.

Un événement tel qu'un courant d'avalanche, un photocourant, une surtension (qui peuvent être provoqués par un ion lourd) peut instantanément augmenter la tension entre base et émetteur des transistors bipolaires  $T_n$  ou  $T_p$  et les mettre en conduction. Un courant très élevé peut s'écouler, dépendant du gain en courant des deux transistors et seulement limité par les résistances  $R_n$  et  $R_p$ . Si le gain en courant de la boucle formée par les deux transistors  $T_n$  et  $T_p$  est supérieur à l'unité, ce courant se maintient après la fin de la perturbation qui l'a causé. Ce courant peut détruire le circuit, à moins que l'alimentation ne soit rapidement coupée (dans un délai inférieur à quelques centaines de microsecondes, selon le type de composant).

Figure 2.10: Schéma d'une structure CMOS sur silicium massif, avec caisson de type n. Les éléments parasites responsables du verrouillage sont mis en évidence, et le circuit électrique équivalent est représenté.

#### 2.2.5 Single Event Snapback (SES)

Le snapback est un mécanisme rétroactif de courant qui peut avoir lieu dans les composants MOS à canal n fonctionnant dans des conditions d'intensité de courant élevée. Dans ce cas, le transistor bipolaire NPN parasite peut être déclenché par un mécanisme d'avalanche se produisant à la jonction drain. Cette avalanche induite dans la zone désertée du drain par l'ion lourd provoque l'injection de trous dans la région du substrat p en dessous de la grille, qui agit comme courant de base du transistor NPN parasite et provoque l'injection d'électrons par la source (émetteur) vers le drain (collecteur). L'augmentation de courant qui en résulte renforce le mécanisme d'avalanche et ferme la boucle [39]. On peut bloquer les SES en coupant l'alimentation.

#### 2.2.6 Claquage de grille (Single Event Gate Rupture, SEGR)

Le claquage de grille peut survenir dans des cas où il existe un champ électrique élevé [40], lors des opérations d'écriture ou d'effacement dans une SRAM non volatile, une EEPROM ou dans des composants MOSFET de puissance [41, 42]. Le claquage est provoqué par le tube de plasma transitoire généré le long de la trace de l'ion dans l'oxyde de grille, avec passage de courant important. Si la densité de courant est suffisamment élevée, celle-ci peut provoquer un claquage thermique et la destruction locale de l'oxyde.

## 2.2.7 Destruction par échauffement excessif (Single Event Burn Out, SEBO)

On peut observer cet effet dans les composants MOSFET de puissance à canal n avec une polarisation appliquée importante et un champ électrique interne élevé [43]. Il est lié à la présence d'un transistor bipolaire parasite qui peut s'activer suite au passage d'un ion lourd qui crée un courant transitoire. Se ce transistor parasite conduit suffisamment, la puissance dissipée localement peut faire fondre le composant.

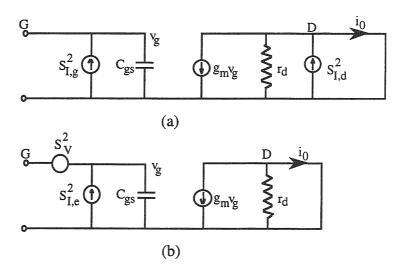

#### 2.3 Méthodologies de durcissement