# Performance of a Double-Sided Silicon Microstrip Detector with a Wide-Pitch N-side Readout using a Field-Plate and a Multi P-stop Structure

Y. SAITOH, T. AKAMINE, M. INOUE, J. YAMANAKA, N. ECHIGO, S. MIYAHARA, M. KAMIYA, H. IKEDA, T. MATSUDA, A. BOZEK, J. HABA, S. KOIKE, H. OZAKI, M. TANAKA, H. IWASAKI, Y. HIGASHI, T. TSUBOYAMA, Y. YAMADA, E. BANAS, Z. NATKANIEC, H. PALKA, M. ROZANSKA, K. RYBICKI, S. OKUNO, H. TAJIMA, H. AIHARA, C. FUKUNAGA, T. HIROSE, Y. ASANO, S. MORI, Y. TUJITA, H. MIYATA, K. MIYANO, M. HAZUMI, T. HARA, T. KAWASAKI, Y. NAGASHIMA and K. SENYO

SW9704

Submitted to the IEEE Nuclear Science Symposium, November 3-9, 1996, Anaheim, California, U.S.A.

# National Laboratory for High Energy Physics, 1996

## KEK Reports are available from:

Technical Information & Library National Laboratory for High Energy Physics 1-1 Oho, Tsukuba-shi Ibaraki-ken, 305 JAPAN

Phone: 0298-64-5136

Telex: 3652-534 (Domestic) (0)3652-534 (International)

(0)3652-534 Fax: 0298-64-4604 Cable: KEK OHO

E-mail: Library@kekvax.kek.jp (Internet Address)

Internet: http://www.kek.jp

# Performance of a Double-Sided Silicon Microstrip Detector with a Wide-Pitch N-side Readout using a Field-Plate and a Multi P-stop structure

Y. Saitoh, T. Akamine, M. Inoue, J. Yamanaka, N. Echigo, S. Miyahara and M. Kamiya Seiko Instruments Inc., Matsudo, Chiba 271, Japan

H. Ikeda, T. Matsuda, A. Bozek, J. Haba, S. Koike, H. Ozaki, M. Tanaka, H. Iwasaki Y. Higashi, T. Tsuboyama and Y. Yamada KEK, National Laboratory for High Energy Physics

E. Banas, Z. Natkaniec, H. Palka, M. Rozanska and K. Rybicki Cracow Institute of Nuclear Physics

#### S. Okuno

Department of Industrial Engineering and Management, Kanagawa University

H. Tajima and H. Aihara

Department of Physics, University of Tokyo

C. Fukunaga and T. Hirose Physics Department, Tokyo Metropolitan University

Y. Asano, S. Mori and Y. Tujita Institute of Applied Physics, Tsukuba University

> H. Miyata and K. Miyano Physics Department, Niigata University

M. Hazumi, T. Hara, T. Kawasaki, Y. Nagashima and K. Senyo Physics Department, Osaka University

#### Abstract

The previous double-sided silicon microstrip detector (DSSDs) prototype with integrated coupling capacitors formed by oxide-nitride-oxide (ONO) dielectric film showed band-to-band tunneling (BBT) current at the field-plate structure for the N<sup>+</sup> strip, which represented a limitation of the biasing configuration. We report improved characteristics of the modified field-plate structure and the wide-pitch n-side readout using a multi p-stop structure combined thereon.

#### I. INTRODUCTION

A silicon vertex detector (SVD) for the KEK B-factory experiment (BELLE collaboration) [1], consisting of detector units assembled by the FCB (Flip-chip bonding) method [2] and arranged in a superlayer structure [1], is planned to be constructed. The double-sided silicon microstrip detectors (DSSDs) to be used in the detector units will have an ONO (oxide-nitride-oxide) dielectric film as an integrated coupling capacitor in the silicon microstrip detectors. In order to implement higher unit capacitance together with higher reliability and lower defect density, we previously have proposed processing techniques for a DSSD with an ONO

capacitor which have achieved the specifications for a HEP application in terms of strip yield, leakage current, bias resistors and inter-strip isolation [3, 4]. While the ONO dielectric film together with the field-plate structure for the N<sup>+</sup> strip at the n-side (ohmic-side of the DSSD) provided only very low voltage for forming sufficient inter-strip resistance, the BBT effect was able to increase the leakage current [4]. We report improved characteristics of the modified "moderate field-plate" structure in this study.

Along with the field-plate structure, a wide-pitch n-side readout with a multi floating p-stop structure (separating the p-stop implantation in a few parts) was eventually employed as the DSSD in the BELLE experiment [5, 6]. An alternative design of the ohmic-side structure, i.e. a common p-stop (p-barrier) design, has a capability to attract carriers over a distance of 100 µm or more [7], because the floating p-stop is automatically biased by a punch (reach)-through effect [8] to generate a local drift field for electrons. We did not choose the common p-stop design, in order to fabricate a compact structure for the readout electrode, and hence, reduce strip capacitance, and to make the detector immune from excess noise [9] as well as any soft-avalanche breakdowns between the readout N+ strips and the P+ floating implants (p-stops).

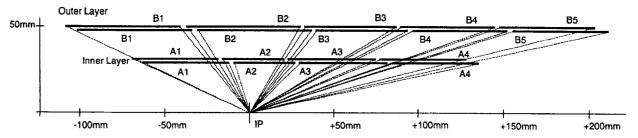

Fig. 1 Schematic cross-sectional view of the SVD.

In order to avoid an increase of the effective size of the N<sup>+</sup> strip electrode and excess noise, a field-plate structure, which forms the local depletion region, has been employed. On the other hand, in order to maintain the charge collection efficiency for inclined tracks, a wide-pitch readout of the multi p-stop structure has been employed at the same time. The p-stops provide a lateral electric field in-between the readout electrode to gather carriers to the readout electrode. We report some of the signal performances of the DSSDs described above.

#### II. DSSD SPECIFICATIONS

In the KEK B-factory experiment, the dimensions of the 9 kinds of DSSDs, which make up the SVD, must be varied for the sake of a specific mechanical constraints as well as the physical requirements [1]. Fig. 1 shows a schematic cross-

Table 1 Common design geometry and process parameters.

| Si Substrate: n-type, <100>, 4 inches, $300 \pm 15 \mu m$      |                          |  |  |  |  |  |

|----------------------------------------------------------------|--------------------------|--|--|--|--|--|

| Resistivity                                                    | 4 - 8 kΩcm               |  |  |  |  |  |

| Design parameters: (for inner detectors)                       |                          |  |  |  |  |  |

| Detector size (sensitive area)                                 | 31.95 x (Table 2) mm     |  |  |  |  |  |

| P-side:                                                        |                          |  |  |  |  |  |

| Strip width (diffusion)                                        | 5 μm                     |  |  |  |  |  |

| Strip pitch (diffusion)                                        | 25 μm                    |  |  |  |  |  |

| Strip pitch (readout)                                          | 50 μm                    |  |  |  |  |  |

| Number of strips (diffusion)                                   | 640 x 2                  |  |  |  |  |  |

| Slant angle                                                    | 20 m radian              |  |  |  |  |  |

| N-side:                                                        |                          |  |  |  |  |  |

| Strip width (diffusion)                                        | 5 μm                     |  |  |  |  |  |

| Readout electrode width                                        | 14 μm                    |  |  |  |  |  |

| (this forms the field plate stru                               | cture)                   |  |  |  |  |  |

| Strip pitch (diffusion)                                        | (varied in Table 2)      |  |  |  |  |  |

| Strip pitch (readout)                                          | 50 μm                    |  |  |  |  |  |

| Number of strips                                               | (varied in Table 2)      |  |  |  |  |  |

| Process target parameters:                                     |                          |  |  |  |  |  |

| ONO capacitor:                                                 |                          |  |  |  |  |  |

| Top oxide thickness around 40 to 50 Å                          |                          |  |  |  |  |  |

| Intermediate Si <sub>3</sub> N <sub>4</sub> thickness          | $1500 \pm 200 \text{ Å}$ |  |  |  |  |  |

| Bottom oxide thickness                                         | $420 \pm 20 \text{ Å}$   |  |  |  |  |  |

| Bias resistor (both sides):                                    |                          |  |  |  |  |  |

| Poly-Si sheet resistivity                                      | 100 kΩ/□                 |  |  |  |  |  |

| (this composes 20 M $\Omega$ resistivity of the bias resistor) |                          |  |  |  |  |  |

| Inter metal dielectric film (n-side):                          | •                        |  |  |  |  |  |

| Polyimide (3 layer) thickness                                  | 5 μm                     |  |  |  |  |  |

| Bump electrode height (both sides)                             | •                        |  |  |  |  |  |

|                                                                |                          |  |  |  |  |  |

sectional view of the SVD. Four different kinds of DSSDs (A1 to A4) form the inner layer of the SVD, which consists of two inner detector units arranged in a superlayer structure with the p-sides placed face to face, a 2 mm gap in-between them and a 6 mm offset lengthwise. The remaining five kinds of DSSDs (B1 to B5) form the outer layer of the SVD, which consists of two outer detector units arranged in a superlayer structure similar to the inner layer.

The common design geometry and target process parameters for the DSSDs are given in Table 1. The possible dimensional variations for the n-side are given in Table 2.

Table 2 Dimensional variations for the n-side.

|        | Pitch and number of strips | Sensitive area size                  |  |  |

|--------|----------------------------|--------------------------------------|--|--|

| Inner: |                            |                                      |  |  |

| A1     | 90 μm x 576                | 51.75 mm                             |  |  |

| A2     | 50 μm x 704                | 35.75 mm                             |  |  |

| A3     | 90 μm x 128                |                                      |  |  |

|        | + 180 µm x 224             | 51.75 mm                             |  |  |

| A4     | 180 μm x 288               | 51.66 mm                             |  |  |

| Outer: |                            |                                      |  |  |

| B1     | 226 μm x 298               | 67.122 mm                            |  |  |

| B2     | 113 μm x 596               | 67.235 mm                            |  |  |

| B3     | 226 μm x 240               | 54.014 mm                            |  |  |

| B4, B  | 5 (same as B3, readout p   | (same as B3, readout pad coordinates |  |  |

|        |                            | are different)                       |  |  |

#### III. PROTOTYPE FABRICATION

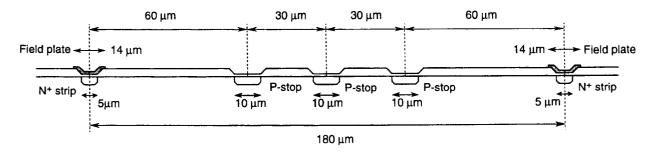

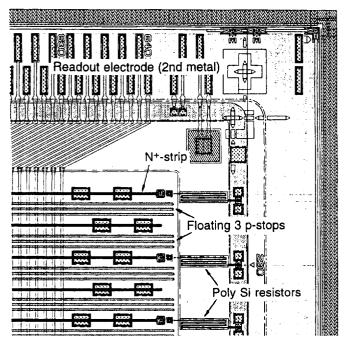

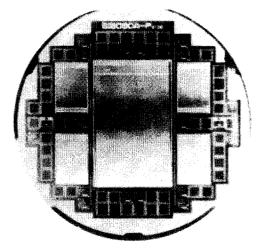

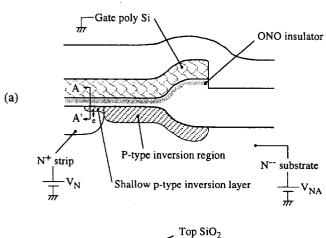

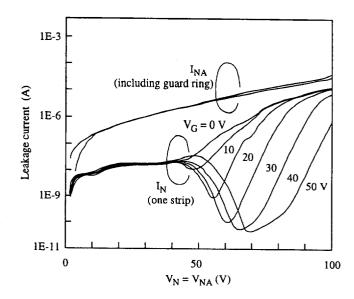

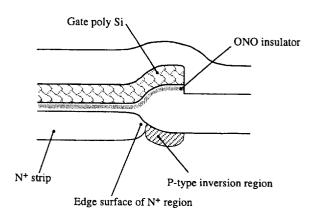

Based on the previous analysis [5, 6] and the above constraint, we chose nine different structures to be examined as possible candidates of the wide-pitch (except for the 50  $\mu$ m-pitch) detector, which are listed in Table 3. A schematic cross-sectional view of the proposed ohmic-side structure (e.g. type A4) is shown in Fig. 2, a view of the pattern design is shown in Fig. 3. Those structures were fabricated by the above mentioned processing techniques, and arranged in test patterns (four small detectors) around a real size detector (one big detector) which is almost equivalent to the A4 type. The modified "moderate field-plate" structure is applied to all the detectors on the N<sup>+</sup> strip within this prototype wafer [Photo 1].

Fig. 2 Schematic cross-sectional view of the proposed ohmic-side structure (e.g. type A4).

Table 3 Varied dimensions for the test patterns.

| Readout | Number   | Location                        |

|---------|----------|---------------------------------|

| pitch   | of p-sto | ops (fixed 10 μm width)         |

| 90 μm   | non      |                                 |

|         | 1        | at 45 μm                        |

| 113 µm  | 1        | at 56.5 μm                      |

|         | 2        | at 41.5, and 71.5 μm            |

| 180 µm  | 2        | at 75, and 195 μm               |

|         | 3        | at 60, 90, and 120 μm (Fig. 2)  |

|         | 4        | at 45, 75, 195, and 135 µm      |

| 226 µm  | 4        | at 68, 98, 128, and 158 µm      |

|         | 5        | at 53, 83, 113, 143, and 173 µm |

Fig. 3 A view of the n-side design of the detector.

Photo 1 Fabricated detector and test elements on a 4" wafer.

### IV. PERFORMANCE AND DISCUSSION

#### A. Modified "moderate field-plate" structure

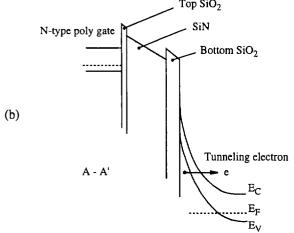

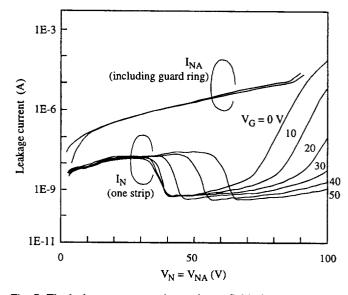

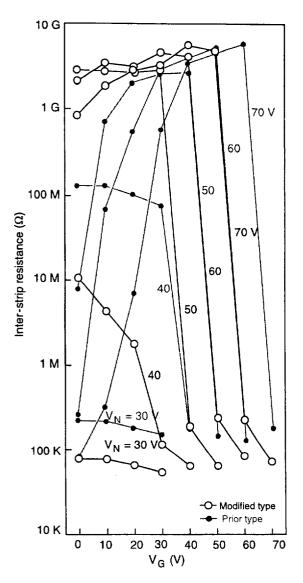

As we reported previously [4], the higher electric field of the ONO insulator appears not only to lower the voltage (around 15 V) in order to form sufficient inter-strip resistance, but also to form an inversion layer encroaching onto the surface of the edge of the N+ region [see Fig. 4 (a)]. Fig. 4 (b) shows a cut out (A - A') of the supposed energy-band diagram of Fig. 4 (a). Since the band was strongly bent by the high electric field, the tunneling electrons are flowing from the shallow p-type inversion layer to the N+ region. The electrons from the shallow p-type inversion layer are provided through the outer p-type inversion layer which touches a full-depleted region of the substrate. Although this current (Field plate assisted BBT current; FBT current) is not expected to have enough energy to cause the microdischarge phenomenon [11], it can still increase leakage current to represent a limitation of the biasing configuration (Fig. 5). The modified "moderate field-plate" structure (Fig. 6) has been examined. The moderate field-plate structure showed acceptable I-V characteristics (Fig. 7) as a function of the field-plate biasing while maintaining enough inter-strip resistance (Fig. 8; within 50 µm-pitch of the N+ strips), in which less reduction of resistance was

observed in the  $V_G < V_N$  - 40 V region. An ion implantation to form the N<sup>+</sup> region was carried out as being self aligned to the LOCOS (which is employed as a thick oxide within an inter-strip [4]) edge in the same manner as the p-side, the surface of the edge of the N<sup>+</sup> region was not strongly affected by the electric field due to the thick oxide above it. On the other hand, an inversion voltage in a MOS structure, which has a highly doped N<sup>+</sup> type poly-Si gate on an N<sup>--</sup> substrate shows  $N_D$  (the donor density)-dependence abruptly along with increased insulator thickness with a cross point for each  $N_D$  [12]. It was proven that there was less difference in the inversion voltage for a LOCOS oxide thickness of around 6000 Å compared to a thinner insulator case.

Using SMA<sup>2</sup>SH preamplifier chips [5, 10], the fabricated DSSD with the moderate field-plate structure provided superior charge responses for a collimated IR light even at a bias voltage exceeding a full depleted voltage.

Fig. 4 The pervious field-plate structure (a) and the band bending at the N<sup>+</sup> edge surface (b).

Fig. 5 The leakage current at the pervious field-plate structure.

Fig. 6 The modified "moderate field-plate structure".

Fig. 7 The leakage current at the moderate field-plate structure.

Fig. 8 Inter-strip resistance as a function of the field-plate biasing.

#### B. Wide-Pitch readout with Multi P-stop structure

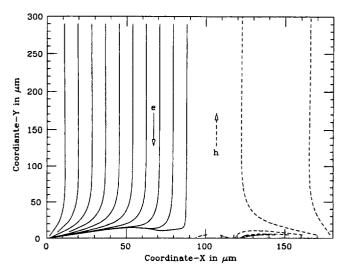

According to the previous analysis of a numerical model [6], the electric field near the ohmic-side with the multi p-stop structure is very delicate. However, we could find that the lateral electric field of the multi p-stop structure is stronger than that without the p-stop structure. The p-stops provide higher capability of transporting electron carriers to the readout electrode. Also from the point of view of carrier flow lines, numerical analysis [6] showed us that electrons are perfectly transported to the electrode as long as the multi pstop structure is well organized, while some carriers may be kicked back in the wrong direction when the arrangement of the p-stops is not appropriate. Fig. 9 shows the carrier flow for a 180 µm-pitch ohmic-side structure with three p-stops, where we find that electrons are perfectly transported to the read out electrode, while a majority of holes are trapped by the p-stop. We can understand here that the floating P+ implants on the ohmic-side provide a trail (potential minimum) for

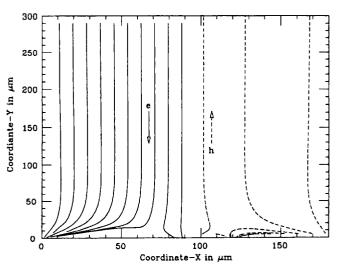

electrons, while it is at the same time a barrier (potential maximum) for holes. By removing a center strip out of the three p-stops, we can see that the trail for the electron carriers is intercepted by a potential blockade, and, hence, some carriers are kicked back to a wrong direction (Fig. 10). We eventually chose to set the distance between the p-stops to 30  $\mu$ m. For larger distances, we easily found malfunctions as shown in Fig. 10.

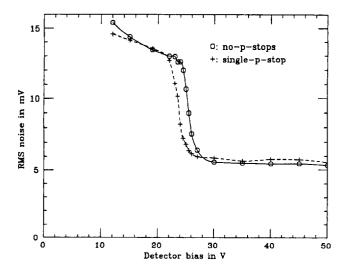

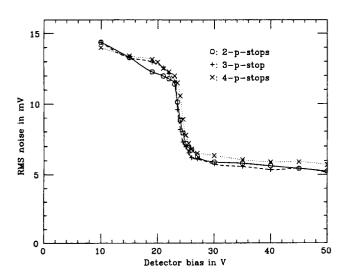

Fig. 11 shows rms noise from a 64-channel SMA<sup>2</sup>SH preamplifier [5], which is wire-bonded to the 90  $\mu$ m-pitch prototype detector. Shown are two sets of data points, one is for a structure without a p-stop, and the other is with a p-stop. It appears that the p-stop helps channel-separation capability as long as it is the 90  $\mu$ m-pitch structure. For larger pitch detectors with a different configuration of p-stops the details of the p-stop configuration slightly affect the characteristics as shown in Fig. 12. The larger pitch detector gathers larger current per strip, the shot noise contribution appears to be larger for wider pitch detectors.

Fig. 9 Carrier flow lines for a 180 μm-pitch detector with three p-stops.

Fig. 10 Carrier flow lines for a 180  $\mu$ m-pitch detector with two p-stops which are separated by 60  $\mu$ m.

Fig. 11 Channel separation for a 90  $\mu$ m-pitch detector.

Fig. 12 Channel separation for a 180  $\mu$ m-pitch detector.

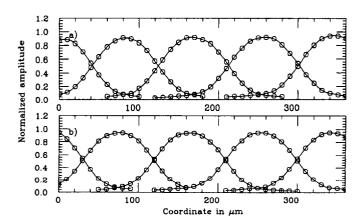

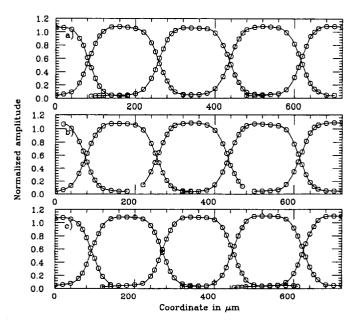

Fig. 13 shows a response of the 90 µm pitch detector structure for an IR pulse of 850 nm shined from the junctionside. The location of the IR spot was adjusted to shine on the part in between the adjacent junction-side strips in such a way that the two junction-side strips yield approximately the same amount of output signals. The sum of these two signals from the junction-side was employed as a denominator to normalize the ohmic-side signals. The spot size of the IR is known to be about 23 µm in diameter, which is still small enough to study the wide-pitch structure in this study. The normalized amplitudes for the 90 µm pitch structure shows similar responses for those configurations with or without a p-stop. It appears the capacitive coupling between adjacent readout strips dominates over the effect of the lateral carrier transport. Fig. 14 shows charge sharing curves for a 180 um pitch detector structure. In Fig. 14 we find that the normalized amplitude at its flat-top becomes larger than in Fig. 13, which arises from the fact that the capacitive coupling between the adjacent readout strip becomes minor and the effect of the carrier transport capability becomes evident. We cannot find any apparent difference between the structures of the two p-stops and the three p-stops. The p-stop structures also work very well for 113 and 226  $\mu m$  pitch structures.

Fig. 13 Charge sharing 90  $\mu$ m-pitch detector a) without and b) with a p-stop.

Fig. 14 Charge sharing for a 180 μm-pitch detector

- a) with two p-stops,

- b) with three p-stops, and

- c) with four p-stops.

Although this study showed good results with any type of p-stop structure, we decided to use an odd number of p-stops in the structure to apply the scheme to a real SVD in order to achieve peak potential between the N<sup>+</sup> strips to guarantee proper carrier deflection. It seems that a longer wave of the IR pulse test would be disturbed by a reflection from the opposite surface of the detector, and a more effective incident angle would be affected by a reflection from the surface of the detector. The justified design principle and procedure for a

wide-pitch detector found in this study will give full play to its ability in a real SVD.

#### V. CONCLUSION

A wide-pitch ohmic-side structure was designed using both a modified field-plate and p-stops. These structures were fabricated in practice with the most convincing technology so far developed including an ONO integrated capacitor, etc. The modified "moderate field-plate" structure showed superior I-V characteristics as a function of the field plate biasing while maintaining enough inter-strip resistance. The prototype detectors showed uniform and perfect charge collection efficiency even for the largest pitch detector of 226  $\mu m$ . The design principle and procedure for a wide-pitch detector were justified in practice.

## VI. ACKNOWLEDGMENTS

We would like to thank all the people of BELLE collaboration for their discussions and encouragement.

#### VII. REFERENCES

- [1] BELLE collaboration, "A Study of CP Violation in B Meson Decays (Technical Design Report)", KEK-Report 95-1, April 1995

- [2] Y. Saitoh et al., "Development of Novel Fabrication Techniques for a Silicon Micro-Vertex Detector Unit using the Flip-Chip Bonding Method", IEEE Trans. on Nucl. Sci., Vol. 40, No. 4, 1192-1196, August 1994

- [3] S. Okuno, H. Ikeda, T. Akamine, Y. Saitoh, K. Kadoi and Y. Kojima, "A Stacked Dielectric Film for a Silicon Microstrip Detector", Nucl. Instr. & Meth. A 361 (1995) 91-96

- [4] Y. Saitoh et al., "Fabrication of a Double-Sided Silicon Microstrip Detector with an ONO Capacitor Dielectric Film", IEEE Trans. on Nucl. Sci., Vol. 43, No. 3, pp. 1123-1129, June 1996

- [5] H. Ikeda et al., "Charge partitioning study of a wide-pitch silicon micro-strip detector with a 64-channel CMOS preamplifier array", Nucl. Instr. & Meth. A 376 (1996) 155-162

- [6] H. Ikeda et al., "Combined use of a field-plate and narrow pbarriers for a wide-pitch ohmic readout of the BELLE doublesided SVD", KEK Preprint 96-128, September 1996

- [7] M. Hazumi et al., "Evaluation of silicon micro strip detectors with large readout pitch", 2nd international symposium on development and application of semiconductor tracking detectors, October 1995, Hiroshima

- [8] J. Ellison et al., "Punch-through currents and floating strip potentials in silicon detectors", IEEE Trans. on Nucl. Sci., NS-36 (1989) 267-271

- [9] J. Alexander et al., "R&D for the CLEO III silicon vertex detector", 2nd international symposium on development and application of semiconductor tracking detectors, October 1995, Hiroshima

- [10] H. Ikeda et al., "Single-channel prototype of a CMOS SVD preamplifier for the B-factory experiment, BELLE", Nucl. Instr. & Meth. A 372 (1996) 125-134

- [11] T. Ohsugi et al., "Microdischarges of AC-coupled silicon strip sensors", Nucl. Instr. & Meth. A 342 (1994) 22-26

- [12] E. H. Nicolson and J. R. Brews, "MOS Physics and Technology", Wiley, New York, 1982