Proceedings of the 31st International Workshop on Vertex Detectors (VERTEX2022) Downloaded from journals.jps.jp by 2001:1458:204:1::102:eb78 on 06/24/24

Proc. 31st Int. Workshop on Vertex Detectors (VERTEX2022) JPS Conf. Proc. 42, 011021 (2024) https://doi.org/10.7566/JPSCP.42.011021

# Improvement in the Design and Performance of the Monopix2 Reticle-Scale DMAPS

Ivan Caicedo<sup>1,\*</sup>, Marlon Barbero<sup>2</sup>, Pierre Barrilon<sup>2</sup>, Christian Bespin<sup>1</sup>, Ivan Berdalovic<sup>4</sup>, Patrick Breugnon<sup>2</sup>, Roberto Cardella<sup>4</sup>, Yavuz Degerli<sup>3</sup>, Jochen Dingfelder<sup>1</sup>, Leyre Flores Sanz de Acedo<sup>4</sup>, Fabrice Guilloux<sup>3</sup>, Amr Habib<sup>2</sup>, Tomasz Hemperek<sup>1</sup>, Toko Hirono<sup>1</sup>, Fabian Hügging<sup>1</sup>, Hans Krüger<sup>1</sup>, Thanushan Kugathasan<sup>4</sup>, Konstantinos Moustakas<sup>1</sup>, Patrick Pangaud<sup>2</sup>, Heinz Pernegger<sup>4</sup>, Francesco Piro<sup>4</sup>, Petra Riedler<sup>4</sup>, Alexandre Rozanov<sup>2</sup>, Piotr Rymaszewski<sup>1</sup>, Lars Schall<sup>1</sup>, Philippe Schwemling<sup>3</sup>, Walter Snoeys<sup>4</sup>, Tianyang Wang<sup>1</sup>, Norbert Wermes<sup>1</sup>, Sinuo Zhang<sup>1</sup>

E-mail: \* caicedo@physik.uni-bonn.de

(Received February 1, 2023)

"LF-Monopix2" and "TJ-Monopix2" are the second generation of "Monopix" Depleted Monolithic Active Pixel Sensor prototypes fabricated in 150 nm and 180 nm CMOS processes, respectively. Both devices implement a fully functional column-drain read-out architecture at a reticle-size scale, but differ on the concept used for pixel design. LF-Monopix2 has each pixel's full front-end and read-out circuitry placed and isolated inside a charge collection node of a size comparable to the pixel area. TJ-Monopix2 separates all electronics from its small collection electrode within the pixel and uses process modifications to enhance its charge collection capabilities. The chips inherited and improved radiation-hard designs tested in their direct predecessors, while also reducing their pixel sizes and increasing their active column lengths to 1.7 centimeters.

An overview of the design and latest test results of unirradiated Monopix2 chips are presented. Their front-end performance was quantified according to their response to injected test pulses or radioactive sources. Moreover, a successfully thinned-down and fully depleted LF-Monopix2 showed a high and uniform in-time detection efficiency on a test beam campaign.

**KEYWORDS:** Semiconductor Detectors, Radiation-Hard CMOS Sensors, Depleted Monolithic Active Pixel Sensors, Radiation Damage.

# 1. Introduction

Multiple particle collider experiments intend to use large areas of semiconductor tracker systems based on radiation-hard pixel detectors with high-rate capability. By integrating sensor and readout electronics in one silicon piece, a monolithic active pixel sensor designed in a commercial CMOS process could reduce the material budget and production complexity of the devices used for that purpose [1]. With an increasing accessibility to CMOS imaging technology, multiple research efforts have been dedicated in the last decade to the development of radiation-hard versions of this concept as an alternative to the standard hybrid pixel approach. These novel detectors, known as "Depleted Monolithic Active Pixel Sensors" (DMAPS), have their radiation tolerance enhanced through technology add-ons and careful design allowing them to be biased with high voltages [2–4] and/or collect charge through drift in a highly resistive silicon substrate [5–7].

<sup>&</sup>lt;sup>1</sup>University of Bonn, Physikalisches Institut, Nußallee 12, 53115 Bonn, Germany

<sup>&</sup>lt;sup>2</sup>Aix Marseille University, CNRS/IN2P3, CPPM, 163 Avenue de Luminy, Marseille, France

<sup>&</sup>lt;sup>3</sup>IRFU CEA-Saclay, Batiment 141, Gif-sur-Yvette Cedex, France

<sup>&</sup>lt;sup>4</sup>CERN, Espl. des Particules 1, 1211 Meyrin, Switzerland

The goal of the "Monopix" DMAPS line [8,9] is the development of radiation-hard monolithic CMOS sensors that (1) integrate all signal processing and digital read-out electronics within each pixel cell and (2) are read-out with a fast synchronous "column-drain" architecture [10, 11]. Two different technologies and pixel layout concepts were chosen to implement these features: "LF-Monopix" uses a 150 nm CMOS process and locates all pixel circuitry within a large charge collection electrode, while "TJ-Monopix" was designed in a 180 nm CMOS process and it has all pixel electronics separated from its small electrode. In these devices, electronics and sensor have been designed to meet the requirements of the outer layers of the ATLAS Inner Tracker (ITk) at the HL-LHC [12]. Hence, the chips are expected to handle an event readout rate of ~ 1 MHz/mm² within a time window of 25 ns, be radiation tolerant up to a Total Ionising Dose (TID) of 80 Mrad and have a detection efficiency > 98.5% after a Non-Ionizing Energy Loss (NIEL) fluence of  $10^{15}$  n<sub>eq</sub>/cm². The first Monopix chips ("LF-Monopix1" and "TJ-Monopix1") were fully functional and intensively measured in order to characterize their performance, identify and fix possible design drawbacks and prove their radiation hardness [13–19].

The second and latest Monopix prototypes ("LF-Monopix2" and "TJ-Monopix2") implement optimized versions of the best performing features tested in their predecessors. The dimensions of both chips are at reticle size scale ( $\geq 2 \, \mathrm{cm}^2$ ) and they have a synchronous read-out operating in a 1.7 cm-long pixel column. Specific details for each design will be given throughout the text, but other features common to both (LF-/TJ-)Monopix2 chips are:

- An injection circuit for characterization, where a negative digital pulse is sent into each pixel to

toggle two reference voltages connected to a capacitor (C<sub>inj</sub>), hence injecting a charge proportional to the voltage difference into the amplifier.

- A local (4-/3-)bit current tuning DAC (TDAC) that can be used to adjust the threshold of the discriminator of each pixel in order to reduce the global threshold dispersion of the front-end.

- Time stamping of every leading (LE) and trailing edge (TE) of the discriminated signal of a pixel with a (6-/7-)bit counter running at a frequency of 40 MHz. The difference between these values is known as Time-Over-Threshold (ToT) and it has a non-linear proportionality with the input charge.

This article presents design features and improvements of the Monopix2 chips, as well as a partial characterization of their performance before irradiation.

## 2. LF-Monopix2

#### 2.1 Description of the chip

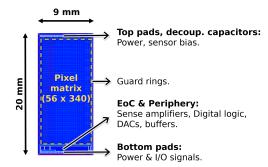

LF-Monopix2 is a DMAPS designed in a 150 nm CMOS process from LFoundry [20]. The device (as depicted in Fig. 1) has a total area of  $1.8\,\mathrm{cm^2}$ , out of which 82% corresponds to an active matrix of  $56\times340$  pixels. The remaining space is occupied by decoupling capacitors, pads, guard rings, end-of-column and periphery logic. It uses a Czochralski-grown p-type silicon substrate with a resisitivity >  $2\,\mathrm{k}\Omega$  · cm as support and sensitive material. After wafer processing (TAIKO backgrinding, plasma etching, accceptor ion implantantion and metallization), it was possible to thin LF-Monopix2 chips down to  $100\,\mu\mathrm{m}$ . These samples could also be depleted through a negative bias voltage applied to their outermost guard ring, while showing a leakage current <  $1\,\mu\mathrm{A/cm^2}$  during operation.

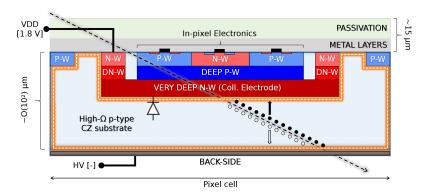

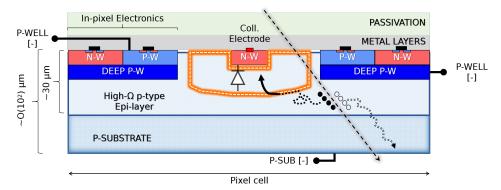

The pixels have a size of  $150 \times 50 \, \mu m^2$ , a value 40% smaller than in the first prototype. Their layout follows the "large collection electrode" approach shown in Fig. 2, where full CMOS-capable electronics are placed and isolated within a high-voltage compatible n-type implant used as charge collection node. This design provides a strong and uniform electric field across the pixel, which results in short drift paths and a high collection efficiency that minimize the probability of charge trapping after irradiation. On the other hand, the junction between the collection node and p-type well isolating in-pixel electronics contributes significantly to the overall detector capacitance ( $C_{det}$ )

Fig. 1. The LF-Monopix2 DMAPS and its chip layout.

**Fig. 2.** Schematic cross-section of the "large collection electrode" pixel design implemented in LF-Monopix. The depletable volume is delimited by white dashed lines.

of  $\sim 250$  fF. A value of this magnitude requires special design efforts to deal with effects like a large equivalent noise charge (ENC), the possibility of switching digital signals coupling to the collection electrode, or a slow rise time during amplification.

The core front-end design of LF-Monopix2 (present in  $\sim 57\%$  of the matrix) uses a combination of charge sensitive amplifier (CSA) and discriminator that was available in its predecessor [21] and proved to be fast (threshold overdrive  $\sim 400\,\mathrm{e^-}$  [15]) and radiation-hard (up to a TID of 100 Mrad and NIEL fluence of  $1\times10^{15}\,\mathrm{n_{eq}/cm^2}$  [13, 19]). The amplifier, labeled "CSA 1", uses an NMOS transistor as input of a single-staged folded cascode structure. Moreover, the discriminator consists of a self-biased amplifier with a CMOS inverter at its output stage. The ENC of this front-end in LF-Monopix2 was measured to be  $\sim 100\,\mathrm{e^-}$  [17], an improvement of 30% with respect to the first prototype thanks to the reduction in  $C_{det}$  associated with the smaller pixel size. Besides, its analog power consumption (measured at default DAC settings) was  $28\,\mu\mathrm{W/pixel}$  ( $\sim 370\,\mathrm{mW/cm^2}$ ).

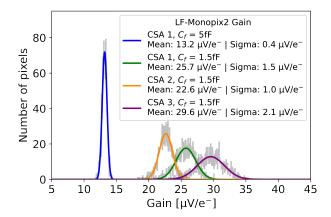

Even though the main front-end was expected to benefit from the reduction of detector capacitance in LF-Monopix2, some additional variations aiming to further improve the gain and time response were also included in a fraction of the chip for testing. The first one, consists in reducing the feedback capacitance ( $C_f$ ) of the front-end with CSA 1 from 5 to 1.5 fF. The second and third one, correspond to two new CSAs with a telescopic cascode structure,  $C_f = 1.5$  fF and fixed (CSA 2) or adjustable (CSA 3) currents flowing into the input transistor.

The untuned threshold dispersion varied between 350 and  $800\,\mathrm{e^-}$  depending on the front-end design. Nevertheless, this value could be successfully tuned down to  $\sim 100\,\mathrm{e^-}$  in all cases by using the 4-bit local TDAC [19].

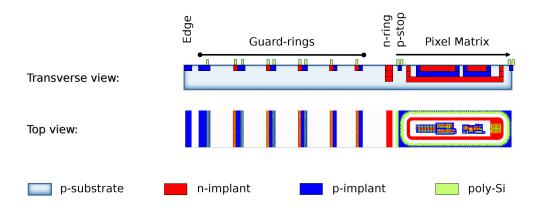

## 2.2 Improvement of the sensor's breakdown voltage

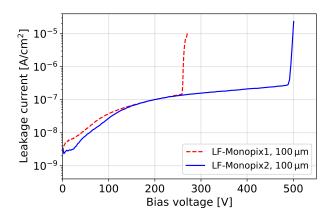

LF-Monopix2 features the guard-ring layout illustrated in Fig. 3. It was inspired by the outcome from comparative measurements of different guard-ring configurations in passive sensor test structures fabricated in the same technology and resistivity as both LF-Monopix chips [22, 23]. These studies indicated that the breakdown voltage of unirradiated sensors can benefit from (1) the use of deep n-type implants in the n-ring, (2) an increase in the distance between the n-ring and the closest guard-ring to the matrix and (3) the use of combined n- and p-type implants for the guard-rings. The latter two modifications were the main changes in the guard-ring design of LF-Monopix2 with respect to that of its predecessor. Their implementation resulted in an increase of the chip's breakdown voltage of  $\sim 200\,\mathrm{V}$ , as shown in Fig. 4 through I-V curves measured in 100  $\mu m$  thick samples. Measurements in multiple devices indicate that the breakdown voltage before irradiation can vary between sensors from 460 to 500 V.

**Fig. 3.** Guard-ring design of LF-Monopix2.

**Fig. 4.** I-V curves of 100 μm thick LF-Monopix1 and LF-Monopix2 devices. The leakage current was divided by the total area of every chip.

## 2.3 Measurement of the injection capacitance

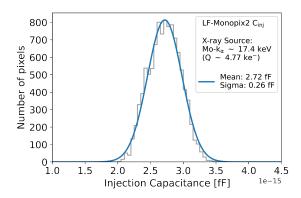

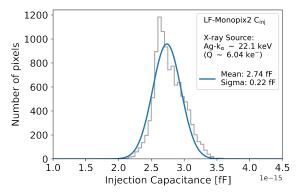

The injection capacitance of LF-Monopix2 was measured in order to use reference pulses to calibrate the ToT response of each pixel to collected charge. In the first place, a scan across the whole range of injection voltage amplitudes was carried out in small steps and the resulting ToT distributions were recorded for each of them. In the second place, the chip was exposed to characteristic fluorescent X-rays from molybdenum and silver targets ionized by a radioactive <sup>241</sup>Am source. A significant fraction of these photons have an energy corresponding to the characteristic  $K_{\alpha}$  transition of an electron to the innermost energy shell of each material:  $K_{\alpha} \sim 17.4 \, \text{keV}$  for Mo and  $K_{\alpha} \sim 22.1 \, \text{keV}$ for Ag. The most intense peak in each pixel's ToT distribution was fitted with a gaussian function, and its mean value was associated with the amount of charge created in silicon by the absorbed  $K_{\alpha}$ X-rays. In the end, this mean ToT value was used to trace-back the voltage that caused the same pixel response in the first measurement, and the ratio between charge created and injected voltage resulted in the capacitance value. The distributions of  $C_{inj}$  values calculated individually for  $\sim 10^4$ pixels are shown in Fig. 5 and 6 for the molybdenum and silver targets, respectively. An average of the measured capacitances results in a  $C_{inj} \sim 2.73$  fF. This value is larger than the  $\sim 2$  fF expected from post-layout simulations during design, but the same discrepancy was observed in LF-Monopix1 [24] and it could be explained by an imprecise modeling of the custom-made capacitor in software.

**Fig. 5.** Injection capacitance measured in LF-Monopix2 with molybdenum's  $K_{\alpha}$  characteristic X-rays as reference.

**Fig. 6.** Injection capacitance measured in LF-Monopix2 with silver's  $K_{\alpha}$  characteristic X-rays as reference.

## 2.4 Measurement and improvement of the gain of the front-ends

A distribution of the gain of each front-end design was measured by calculating the slopes of linear fits to single pixel thresholds at four different global threshold voltages. In order to minimize the influence of the local tuning circuitry on the measured gains, the scans were carried out with all TDAC values set to the unbiased condition of the discriminator. The results for every front-end configuration are shown in Fig. 7. For CSA 1, the use of a feedback capacitance of 5 fF results in a gain of  $(13.2 \pm 0.4) \, \mu V/e^-$ , while a smaller capacitance of 1.5 fF increases this value to  $(25.7 \pm 1.5) \, \mu V/e^-$ . The front-ends with new CSA designs use only a feedback capacitance of 1.5 fF, and their measured gains were  $(22.6 \pm 1.0) \, \mu V/e^-$  for CSA 2 and  $(29.6 \pm 2.1) \, \mu V/e^-$  for CSA 3.

#### 2.5 Test beam results for thin sensors before irradiation

LF-Monopix2 chips with a thickness of 100 µm were biased and read-out while exposed to 5 GeV and 2.5 GeV electron beams at the DESY II [25] and ELSA [26] accelerator facilities, respectively. The detection efficiency and timing performance of the devices were quantified using a EUDET-type

Fig. 7. Gain of the multiple front-end designs implemented in LF-Monopix2.

telescope [27] for particle tracking and a FE-I4 chip [28] as timing reference plane. Each region with a common front-end in the chip was operated at a mean threshold of  $2\,\mathrm{ke^-}$  for a comparison of the detection time between different designs. Furthermore, multiple bias and threshold voltages were set to the largest region of the matrix with a common front-end (CSA 1, with  $C_f = 5\,\mathrm{fF}$ ) to evaluate the efficiencies with respect to those parameters. For all cases, the tuned threshold distributions had a dispersion of  $100\,\mathrm{e^-}$ .

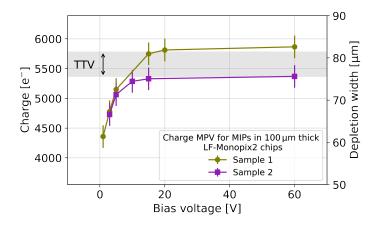

A scan across different bias voltages was used to determine the value at which the sensor reaches full depletion. After a calibration of the individual ToT response of single pixel hits into charge, the overall charge distribution measured in the active region was fitted with a convolution of Landau and Gaussian functions. The most probable values (MPV) extracted for each voltage step were used to estimate the width of the depleted region, under the assumption of a charge per unit length of  $71\,e^-/\mu m$  created by the energy loss of 5 GeV electrons traversing an 85  $\mu m$  thick silicon layer. Fig. 8 shows the most probable signals observed in two different LF-Monopix2 samples with respect to the applied bias voltage. The depletion plateau started at a value between 15 and 20 V, in agreement with the manufacturer's claim of a substrate resistivity larger than  $2\,k\Omega$  · cm. In addition to that, both chips concurred well with one another in their depletion profile before reaching the plateau, as expected from samples diced from the same silicon wafer.

Since approximately 15  $\mu$ m of the chip's total thickness correspond to passivation and metal layers, the maximum depletion width expected in a 100  $\mu$ m thick chip would be close to 85  $\mu$ m. In reality though, the average silicon width in each sensor can be up to 10  $\mu$ m smaller than the thinning target value after backside processing due to additional removal during etching and the total thickness variation (TTV) across the wafer. The full depletion widths were (83.5  $\pm$  2.4)  $\mu$ m for the first sample and (76.4  $\pm$  2.4)  $\mu$ m for the second one, where the uncertainty of each measurement is mainly due to the ToT resolution. These values are still within the TTV range measured in wafers of this thickness after processing ( $\sim$  6  $\mu$ m), and the MPVs recorded were more than three times larger than the chip's minimum operational threshold.

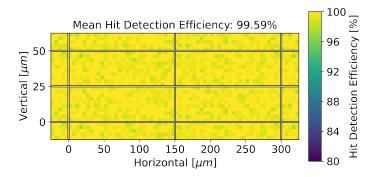

The hit detection efficiency of a fully depleted device was quantified for  $\sim 10^4$  pixels at a threshold of  $(2040 \pm 104)\,\mathrm{e}^-$ . The data were analyzed using the python-based "BTA" software [29] and projected onto the  $2 \times 2$  pixel array shown in Fig. 9. The resulting efficiency is uniform across the whole pixel area, and its mean value of 99.6% is in very good agreement with the one reported for an unirradiated LF-Monopix1 of similar characteristics [17].

The time-walk of a hit pixel corresponds to the time difference between the rising edge of its CSA signal above threshold and the start of charge collection. This quantity was recorded in beam for every hit using the timestamps of the leading edge of the output of the discriminator and the

**Fig. 8.** Most probable charge signals created by the passage of 5 GeV e<sup>-</sup> through 100 μm thick unirradiated LF-Monopix samples as a function of the applied bias voltage. The height of the shaded region in the vertical axis corresponds to the average total thickness variation in backside processed LF-Monopix2 wafers.

**Fig. 9.** Hit detection efficiency map of a 100 μm thick LF-Monopix2 (data from  $\sim 10^4$  pixels projected onto a 2 × 2 pixel array). The chip was exposed to a 5 GeV e<sup>-</sup> beam. Threshold: 2 ke<sup>-</sup>. Bias voltage: 60 V.

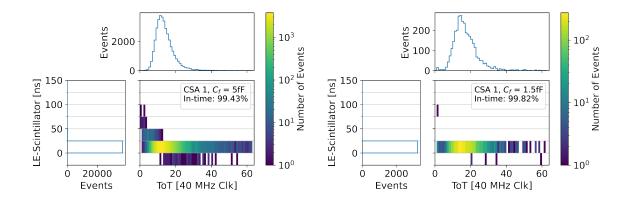

signal of a scintillator used as trigger for all devices. Though the latter was sampled with a resolution of 1.56 ns, the resolution of the measurement was limited by the 40 MHz clock used in the chip. Fig. 10 shows (for two front-ends with CSA 1, but different  $C_f$ ) the dependence of the time-walk of pixels with the largest signal in every recorded event (also known as "seed pixels") with respect to the total ToT. In these distributions, an event was considered to be "in-time" if its time-walk was within the first 25 ns. 99.43% of all efficient events were in-time for the front-end with  $C_f = 5$  fF, representing an improvement of 2% with respect to the value measured in the same front-end in LF-Monopix1. This change can be mainly attributed to the reduction in detector capacitance due to a smaller collection node. For the front-ends with  $C_f = 1.5$  fF, their larger gain reduced the rise time of the CSA signal, and therefore a percentage of more than 99.8% of all events were recorded in-time.

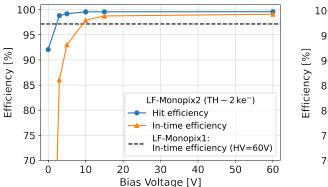

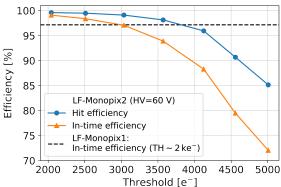

Using the time-walk measurements, it was possible to apply an additional criterion to the selection of efficient events so that only those with seed pixels registered within 25 ns were considered. Hit and in-time detection efficiencies were calculated for the front-end with CSA 1 and  $C_f = 5\,\mathrm{fF}$ , with respect to the bias voltage applied to the sensor (Fig. 11) and its mean threshold (Fig. 12). As a reference for the improvement in LF-Monopix2, the dotted line in the plots corresponds to the mean in-time efficiency of 97.2% measured for the same front-end in an unirradiated LF-Monopix1 chip with similar depletion and a threshold close to  $2\,\mathrm{ke}^-$ .

**Fig. 10.** Time-walk of seed pixel hits recorded in a 100 µm thick LF-Monopix2 with CSA 1 and feedback capacitance of (Left) 5 fF or (Right) 1.5 fF. The projections of both axes include all ToT or time bins. The chip was exposed to a 5 GeV e<sup>-</sup> beam. Threshold: 2 ke<sup>-</sup>. Bias voltage: 60 V.

**Fig. 11.** Hit and in-time detection efficiencies measured with respect to the bias voltage applied to a 100  $\mu$ m thick unirradiated LF-Monopix2. Front-end: CSA 1 with  $C_f = 5$  fF. Threshold: 2 ke $^-$ .

**Fig. 12.** Hit and in-time detection efficiencies measured with respect to the mean threshold of a 100  $\mu$ m thick unirradiated LF-Monopix2. Front-end: CSA 1 with  $C_f = 5$  fF. Bias voltage: 60 V.

For the overall hit detection, an efficiency larger than 98.5% could be reached at (1) a voltage above  $3\,V$  for a  $2\,\mathrm{ke^-}$  threshold, or (2) a threshold below  $\sim 3.3\,\mathrm{ke^-}$  in a fully depleted sensor. Moreover, the in-time efficiency at full depletion was 99.1% for a threshold of  $2\,\mathrm{ke^-}$ . Since almost all events were recorded within  $25\,\mathrm{ns}$  for the front-ends with smaller  $C_f = 1.5\,\mathrm{fF}$ , their in-time efficiency would be practically the same as the hit detection one at the lowest threshold setting: 99.6%. The percentage of in-time events drops faster than the overall detected ones for lower bias voltages, since the number of hits with a smaller input charge (and a signal shaping time larger than  $25\,\mathrm{ns}$ ) increases as the lower end of the distribution gets closer to the threshold. On the other hand, the decrease of in-time efficiency for larger thresholds occurs because, for a given input charge, the time that the CSA signal takes to go above discrimination increases as the threshold voltage does. Based on these measurements and the previous characterization of changes in the front-end and sensor in LF-Monopix1 after X-ray and neutron irradiation [17, 19], LF-Monopix2 is expected to improve the already high radiation-hardness of its predecessor.

# 3. TJ-Monopix2

## 3.1 Description of the chip

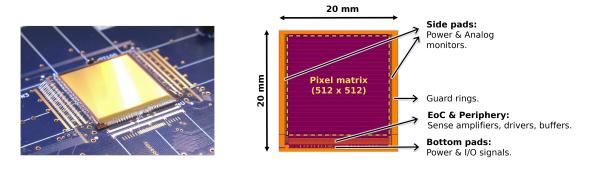

TJ-Monopix2 is a DMAPS fabricated in a modified 180 nm CMOS process from Tower Semi-conductor [30]. Its pixel concept and front-end were derived from the ALPIDE chip [31] and substantially optimized for improved radiation hardness. The device (as depicted in Fig. 13) has a total area of  $4\,\mathrm{cm}^2$ , out of which 72% corresponds to an active matrix of  $512\times512$  pixels. The remaining space is occupied by decoupling capacitors, pads, guard rings, end-of-column and periphery logic. The chip's sensitive volume can be either a high-resistivity ( $\sim 1\,\mathrm{k}\Omega\cdot\mathrm{cm}$ ) p-type epitaxial layer grown on a highly doped p-substrate, or a highly resistive ( $> 3\,\mathrm{k}\Omega\cdot\mathrm{cm}$ ) Czochralski-grown p-substrate.

Fig. 13. The TJ-Monopix2 DMAPS and its chip layout.

The pixels have a size of  $33.04 \times 33.04 \, \mu m^2$ . Their layout follows the "small collection electrode" approach, where a small ( $\sim 2 \times 2 \, \mu m^2$ ) n-type implant at the center of the pixel is used for charge collection while all CMOS electronics are placed at a distance from it and isolated within p-type wells. The main advantage of a small electrode design is its very small detector capacitance ( $C_{det} < 5 \, \mathrm{fF}$ ), which in turn translates into a large and fast voltage input signal. Under those conditions, an open-loop voltage amplifier is preferred to the charge sensitive amplifiers used in other particle detectors, since the original signal-to-noise ratio is large enough to require only a second stage amplification before discrimination, the circuit is very compact and it has a low power consumption of  $\sim 1 \, \mu \mathrm{W/pixel}$  ( $\sim 90 \, \mathrm{mW/cm^2}$ ).

In the standard imaging process (shown in Fig. 14), a p-type epitaxial layer with a resistivity of  $1 \, k\Omega \cdot cm$  can be partially depleted close to the collection node by applying small voltages at both the p-well shielding the pixel electronics and the p-substrate. Charges created in the small depleted region can be collected by drift, but those in the rest of the volume would be relegated to move only by diffusion. This approach is not suitable for high radiation environments, where charges moving slowly by diffusion or those with very long drift paths have a higher probability to be trapped by bulk damage induced defects.

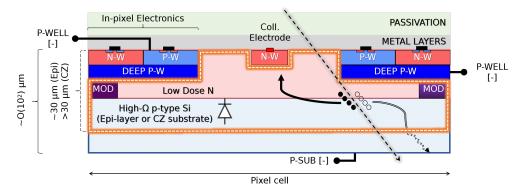

As a first attempt to improve the radiation-hardness of the standard process, a low-dose n-type layer between the p-well and p-type sensitive volume was added to the matrix. The purpose of this modification was to extend the depletion region across the whole pixel area and form a potential minimum towards the electrode that could enhance the collection of distant charges [7]. After a successful proof-of-concept in a small sensor [32], this modification was taken into account for the pixel designs of TJ-Monopix1 [9] and a similar chip with an asynchronous read-out architecture called MALTA [33]. Test beam campaigns in the first versions of both chips showed a significant loss of hit detection efficiency after a NIEL fluence of  $10^{15} \, n_{eq}/cm^2$  [14, 16, 34]. Two main factors

**Fig. 14.** Schematic cross-section of a "small collection electrode" pixel design implemented in the standard imaging process. Only a fraction of the p-type epitaxial layer close to the collection node (similar to the one delimited with white lines) can be depleted.

were identified as the causes of this performance: An inefficient charge collection at the pixel corners and a high limit to the minimum operational threshold (> 450 e<sup>-</sup>) caused by an asymmetric ENC distribution linked to random telegraph signal (RTS) noise.

The observation of detection efficiency patterns correlated to the location of the deep p-well implant in the pixel motivated a set of TCAD simulations that looked at possible improvements in charge collection through additional modifications to the implants [35]. These studies suggested two new possible process variants that would enhance the lateral field towards the collection node at the pixel edges: (1) creating a gap in the n-layer (n-gap) or (2) introducing an additional deep p-well implant below the existing one (extra deep p-well). The two features were included in a second submission of the TJ-Monopix1 chip, which was also produced in both epitaxial- and Czochralski-grown substrates (Fig.15). After neutron irradiation, samples from the new modified versions showed a significant increase in detection efficiency with respect to the original design [18]. Moreover, the improved charge collection also benefited from a larger achievable depletion volume (and hence, charge signal) in the Czochralski substrate. All of these improvements to the small electrode design are also available in the TJ-Monopix2 chips.

**Fig. 15.** Schematic cross-section of one of the "modified small collection electrode" pixel designs implemented in TJ-Monopix. The low dose n-type layer enables a uniform depletion of a p-type epitaxial layer (up to  $\sim 30 \, \mu m$ ) or Czochralski substrate (larger than  $30 \, \mu m$ ). Either deep p-type implants or a gap in the n-layer at the pixel edges (MOD) enhance the lateral component of the electric field. The depletable volume is delimited by white dashed lines.

### 3.2 Improvement of the front-end

As mentioned earlier, the ENC distribution of TJ-Monopix1 showed a long tail towards higher charge values, which was linked to RTS noise caused by charge trapping or release at the gate interface of small transistors in the front-end. This effect limited substantially the minimum operational threshold of the chip at a reasonable noise rate. Since the magnitude of the currents associated with RTS at a gate is inversely proportional to its area, a plausible solution to minimize the sensitivity to this type of noise was to increase the size of two small transistors. This idea was successfully tested in a small test chip [36]. Hence, the dimensions of transistors responsible for the coupling capacitance and preamplifier voltage gain stage of the front-end of TJ-Monopix2 were enlarged in order to increase the signal-to-noise ratio by a factor of 3 and reduce its RTS noise component [37].

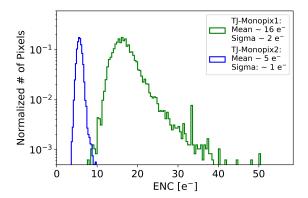

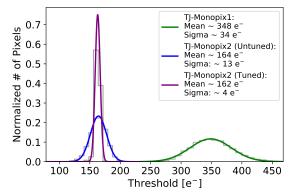

The positive effects of the changes in the TJ-Monopix2 front-end are illustrated in the ENC (Fig. 16) and threshold (Fig. 17) distributions obtained from injection scans in both versions of TJ-Monopix. In comparison to previously reported measurements [17], these scans synchronized the timestamp clock distribution across the column with the injection pulse for a more reliable sampling of the s-curves. For the ENC, its mean value was reduced by a factor of 3 in the latest prototype and the long tail due to RTS noise towards the high end of the distribution is gone. Besides, the untuned threshold dispersion in TJ-Monopix2 ( $\sim 13\,\mathrm{e}^-$ ) is about 60% smaller than the one in its predecessor, and thanks to the changes in ENC a minimum operational threshold of  $\sim 160\,\mathrm{e}^-$  can be reached. Moreover, the dispersion can be tuned down to  $\sim 5\,\mathrm{e}^-$  with the 3-bit local tuning DAC.

**Fig. 16.** ENC in TJ-Monopix1 and TJ-Monopix2. The mean and dispersion values were obtained from a gaussian fit to the data.

**Fig. 17.** Threshold distributions in TJ-Monopix1 and TJ-Monopix2. Only the TJ-Monopix2 front-end counts with local threshold tuning circuitry.

Given the significant improvement of the front-end, it is reasonable to expect that future charge collection measurements in TJ-Monopix2 devices with a Czochralski substrate and pixel edge modifications result in uniform high detection efficiencies.

## 4. Conclusions

The latest Monopix DMAPS prototypes, LF-Monopix2 and TJ-Monopix2, have a fully functional and fast synchronous read-out operating in a 1.7 cm-long pixel column. In addition to that, initial tests on unirradiated samples show promising improvements in their sensor and front-end performance with respect to their predecessors, as summarized in Table I.

LF-Monopix2 was successfully thinned and backside processed down to a thickness of  $100 \,\mu m$ . Its sensor can be fully depleted before irradiation with a bias voltage  $> 20 \, V$ , a value reliably distant from its improved breakdown voltage of at least  $460 \, V$ . Test beam measurements showed an uniform

|                                      | LF-Monopix1             | LF-Monopix2               | TJ-Monopix1                | TJ-Monopix2          |

|--------------------------------------|-------------------------|---------------------------|----------------------------|----------------------|

| CMOS process                         | LFoundry 150 nm         |                           | Tower Semiconductor 180 nm |                      |

| DMAPS type                           | Large electrode design  |                           | Small electrode design     |                      |

| P-type substrate                     | Czochralski (>2)        |                           | Epi-layer (~ 1) or         |                      |

| (Resistivity [k $\Omega \cdot cm$ ]) |                         |                           | Czochralski (>3)           |                      |

| <b>Dimensions</b> [cm <sup>2</sup> ] | $0.98 \times 0.95$      | $0.9 \times 2$            | 2 × 1                      | 2 × 2                |

| Matrix size [Pixels]                 | 36 × 129                | 56 × 340                  | 448 × 224                  | 512 × 512            |

| Pixel size [μm <sup>2</sup> ]        | 250 × 50                | 150 × 50                  | 40 × 36                    | $33.04 \times 33.04$ |

| Active col. length [cm]              | 0.65                    | 1.7                       | 0.8                        | 1.7                  |

| Analog power [µW/Pix]                | ~ 45                    | ~ 28                      | ~ 1                        | ~ 1                  |

| $([mW/cm^2])$                        | (360)                   | (370)                     | (70)                       | (90)                 |

| Gain [μV/e <sup>-</sup> ]            | $\sim 12 (C_f = 5  fF)$ | $\sim 13 (C_f = 5  fF)$   | ~ 400                      | ~ 1200               |

|                                      |                         | $\sim 26 (C_f = 1.5  fF)$ |                            |                      |

| ENC [e <sup>-</sup> ]                | ~ 150 ± 25              | ~ 100 ± 15                | $\sim 16 \pm 2  (+RTS)$    | ~ 5 ± 1              |

| Threshold Disp. [e <sup>-</sup> ]    | ~ 100                   | ~ 100                     | ~ 35                       | ~ 5                  |

| Max. bias voltage [V]                | 260 - 300               | 460 - 500                 | 50                         | 50                   |

**Table I.** Design and characteristic performance values of the Monopix DMAPS designs before irradiation.

hit detection efficiency of 99.6% and an in-time efficiency of at least 99.1% for a fully depleted chip with a tuned threshold of  $\sim (2 \pm 0.1) \, \text{ke}^-$ .

TJ-Monopix2 has implemented in its small electrode design well-tested process modifications that are known to increase its depletion region (Czochralski-grown substrate) and the collection efficiency of charges created at the pixel edges (n-layer gap or extra p-implant). Moreover, key transistors in its front-end were enlarged to increase its gain and avoid RTS noise, resulting in a mean ENC and untuned threshold dispersion three times smaller than the ones of its predecessor. A new 3-bit TDAC circuit can tune the threshold dispersion between pixels down to  $\sim 5e^-$ , allowing for a mean threshold as low as  $160\,e^-$  in the chip.

## Acknowledgements

This project has received funding from the Deutsche Forschungsgemeinschaft DFG (grant WE 976/4-1), the German Federal Ministry of Education and Research BMBF (grant 05H15PDCA9) and the European Union's Horizon 2020 Research and Innovation programme under grant agreements No. 675587 (STREAM), 654168 (AIDA-2020) and 101004761 (AIDA-Innova). The measurements leading to these results have partially been performed at the Test Beam Facility in DESY Hamburg (Germany), a member of the Helmholtz Association (HGF).

## References

- [1] R. Turchetta et al., Nucl. Instrum. Methods Phys. Res. Sect. A 458, 677-689 (2001).

- [2] I. Peric et al., Nucl. Instrum. Methods Phys. Res. Sect. A **582**, 876-885 (2007).

- [3] H. Augustin et al., Nucl. Instrum. Methods Phys. Res. Sect. A 979, 164441 (2020).

- [4] I. Peric et al., IEEE J. Solid-State Circuits **56** (**8**), 2488–2502 (2021).

- [5] M. Havránek et al., J. Instrum. 10, P02013 (2015).

- [6] T. Hirono et al., Nucl. Instrum. Methods Phys. Res. Sect. A 831, 94-98 (2016).

- [7] W. Snoeys et al., Nucl. Instrum. Methods Phys. Res. Sect. A 871, 90-96 (2017).

- [8] T. Wang et al., J. Instrum. 13, C03039 (2018).

- [9] K. Moustakas et al., Nucl. Instrum. Methods Phys. Res. Sect. A 936, 604-607 (2019).

- [10] E. Mandelli et al., IEEE Trans. Nucl. Sci. 49 (4), 1774-1777 (2002).

- [11] I. Peric et al., Nucl. Instrum. Methods Phys. Res. Sect. A 565, 178-187 (2006).

- [12] The ATLAS Collaboration, ATLAS-TDR-30. CERN-LHCC-2017-021 (2017).

- [13] T. Hirono et al., Nucl. Instrum. Methods Phys. Res. Sect. A 924, 87-91 (2019).

- [14] I. Caicedo et al., J. Instrum. 14, C06006 (2019).

- [15] M. Barbero et al., J. Instrum. 15, P05013 (2018).

- [16] C. Bespin et al., Nucl. Instrum. Methods Phys. Res. Sect. A 978, 164460 (2020).

- [17] J. Dingfelder et al., Nucl. Instrum. Methods Phys. Res. Sect. A 1034, 166747 (2022).

- [18] C. Bespin et al., Nucl. Instrum. Methods Phys. Res. Sect. A **1040**, 167189 (2022).

- [19] I. Caicedo et al., Nucl. Instrum. Methods Phys. Res. Sect. A 1040, 167224 (2022).

- [20] LFoundry (Company Website), http://www.lfoundry.com/en/Accessed: 2023-01-20

- [21] T. Wang et al., J. Instrum. **12**, C01039 (2017).

- [22] I. Caicedo and K. Moustakas, STREAM-ITN Deliv. Rep. D-3.1, EC Ref. Ares(2017)3777070.

- [23] S. Zhang, private communication.

- [24] P. Rymaszewski et al., Proc. Sci. 313, 024 (2018).

- [25] R. Diener et al., Nucl. Instrum. Methods Phys. Res. Sect. A 922, 256-286 (2019).

- [26] N. Heurich et al., Proc. 7th Int. Particle Accelerator Conf., 4088-4090 (2016)

- [27] H. Jansen et al., EPJ Tech. Instrum. 3, 7 (2016).

- [28] M.Garcia-Sciveres et al., Nucl. Instrum. Methods Phys. Res. Sect. A 636, S155-S159 (2011).

- [29] Beam Telescope Analysis (Software Repository), https://github.com/SiLab-Bonn/beam\_telescope\_analysis Accessed: 2023-01-20

- [30] Tower Semiconductor (Company Website), https://towersemi.com/ Accessed: 2023-01-20

- [31] M. Mager et al., Nucl. Instrum. Methods Phys. Res. Sect. A **824**, 434-438 (2016).

- [32] H. Pernegger et al., J. Instrum. 12, P06008 (2017).

- [33] I. Berdalovic et al., J. Instrum. 13, C01023 (2018).

- [34] R. Cardella et al., J. Instrum. 14, C06019 (2019).

- [35] M. Munker et al., J. Instrum. 14, C05013 (2019).

- [36] M. Dyndal et al., J. Instrum. 15, P02005 (2020).

- [37] K. Moustakas, Dr. Thesis, Physikalisches Institut, University of Bonn, Bonn (2021).