# The RD53C-CMS Pixel Readout Chip Manual

ABSTRACT: Manual for the RD53C design in the CMS chip implementation.

5

# Contents

|    | 1. | Overview      |                                                    | 4  |

|----|----|---------------|----------------------------------------------------|----|

|    | 2. | Dimensions    | s, Floorplan and Pads                              | 6  |

|    |    | 2.1 Bump      | Bond Pads                                          | 8  |

| 0  |    | 2.2 Wire E    | Bond Pads and Alignment Marks                      | 8  |

|    | 3. | Basic Opera   | ation and Reset (Intro and Quick Start Guide)      | 10 |

|    |    | 3.1 Chip S    | Startup                                            | 10 |

|    |    | 3.1.1         | Default and User Configurations                    | 12 |

|    |    | 3.2 Reset     |                                                    | 13 |

| 5  |    | 3.2.1         | Command Activity Detector                          | 14 |

|    | 4. | Power and     | References                                         | 16 |

|    |    | 4.1 Shunt     | LDO Regulator                                      | 16 |

|    |    | 4.2 Refere    | ences and Startup                                  | 17 |

|    |    | 4.2.1         | Offset Voltage Start-up                            | 19 |

| 20 |    | 4.3 Offset    | Voltage and Low Power Mode                         | 20 |

|    |    | 4.4 Under-    | -shunt Current Protection                          | 21 |

|    |    | 4.5 Over-v    | voltage Protection                                 | 23 |

|    | 5. | Analog Fro    | nt End                                             | 24 |

|    |    | 5.1 Front l   | End Bias Generation and Distribution               | 24 |

| 25 |    | 5.2 CMS A     | Analog Front End                                   | 25 |

|    |    | 5.2.1         | Front-end registers                                | 28 |

|    |    | 5.2.2         | Krummenacher current: KRUM_CURR_LIN                | 29 |

|    |    | 5.2.3         | Global threshold: Vthreshold_LIN                   | 29 |

|    |    | 5.2.4         | Threshold trimming: LDAC_LIN                       | 30 |

| 30 |    | 5.2.5         | Secondary settings                                 | 31 |

|    | 6. | Calibration   | Injection                                          | 32 |

|    |    | 6.1 Genera    | ation of S0 and S1 signals                         | 33 |

|    |    | 6.2 Cal Ca    | ommand                                             | 34 |

|    |    | 6.3 Injection | on Voltages                                        | 37 |

| 35 | 7. | Digital Core  | e                                                  | 38 |

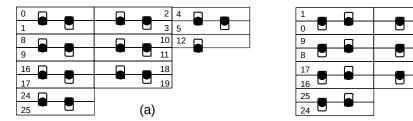

|    |    | 7.1 4-Pixe    | l Region                                           | 38 |

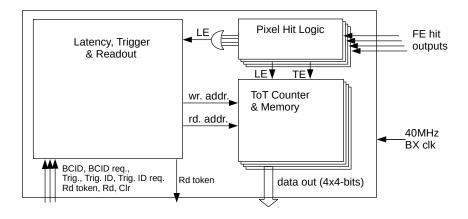

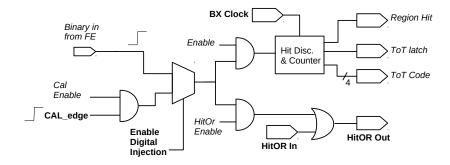

|    |    | 7.2 Pixel H   | Hit Logic                                          | 39 |

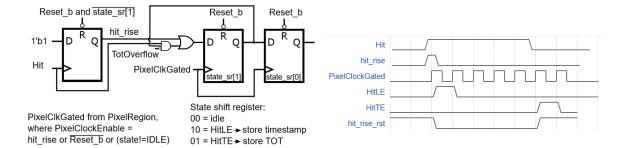

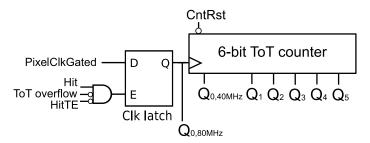

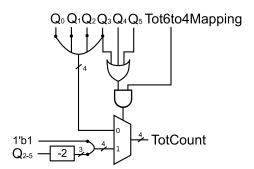

|    |    | 7.3 ToT co    | ounter and storage                                 | 39 |

|    |    | 7.4 Latence   | ey, Trigger and Readout (LTR) block                | 41 |

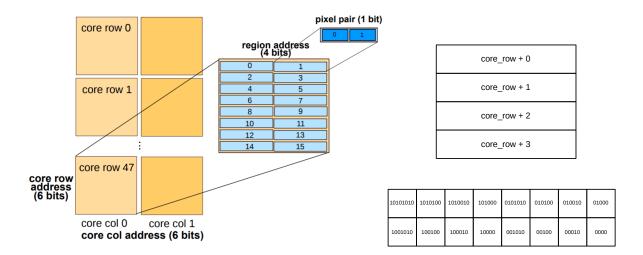

| 10 |    | 7.5 Pixel A   | Addressing                                         | 43 |

|    |    | 7.5.1         | $25 \mu\mathrm{m} \times 100 \mu\mathrm{m}$ pixels | 43 |

|    | 8.  | Commands and Configuration                | 45 |

|----|-----|-------------------------------------------|----|

|    |     | 8.1 Receiver Circuit                      | 45 |

|    |     | 8.2 Command Protocol                      | 46 |

| 45 |     | 8.2.1 Short Commands                      | 47 |

|    |     | 8.2.2 Long Commands                       | 48 |

|    |     | 8.3 Command Protocol Initialization       | 49 |

|    |     | 8.4 Command Protocol Transmission         | 50 |

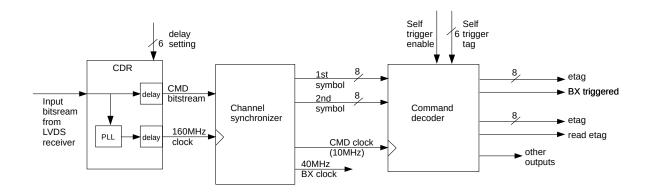

|    |     | 8.5 Command Protocol Decoding             | 50 |

| 50 |     | 8.6 Command Protocol Timing               | 51 |

|    |     | 8.7 Global Configuration                  | 51 |

|    |     | 8.8 Pixel Configuration                   | 52 |

|    | 9.  | Trigger Processing, Tags, and Data Flow   | 55 |

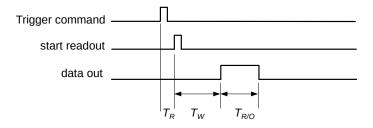

|    |     | 9.1 Pixel Matrix Processing and Wait Time | 56 |

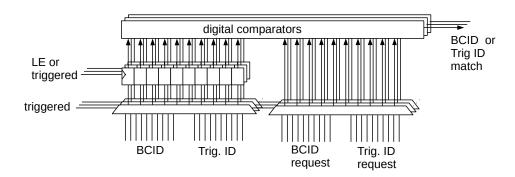

| 55 |     | 9.2 Tags                                  | 57 |

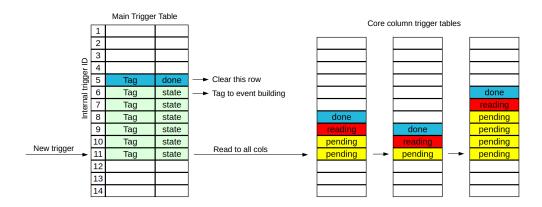

|    |     | 9.3 Trigger Table                         | 57 |

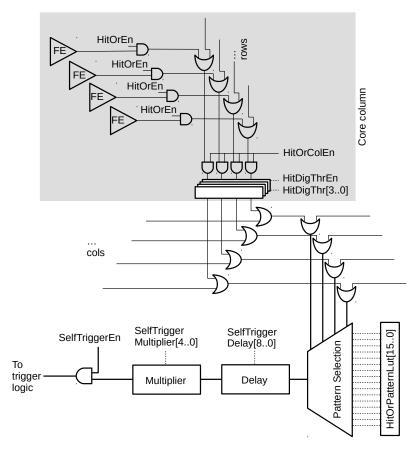

|    |     | 9.4 Self Trigger Source                   | 59 |

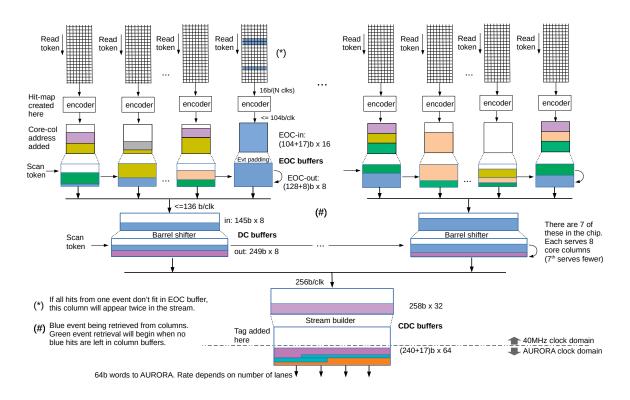

|    |     | 9.5 Data Flow                             | 59 |

|    | 10. | Data Output                               | 63 |

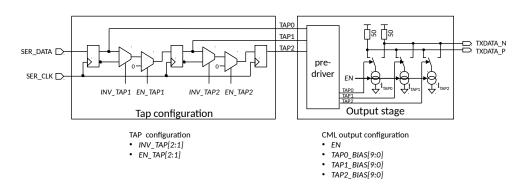

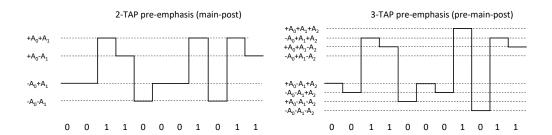

| 60 |     | 10.1 Data Output Drivers                  | 63 |

|    |     | 10.2 Aurora and RD53C Data                | 65 |

|    |     | 10.3 Aurora and streams                   | 67 |

|    |     | 10.4 Hit data encoding                    | 68 |

|    |     | 10.5 Stream construction and efficiency   | 70 |

| 65 |     | 10.6 Hit map construction                 | 70 |

|    |     | 10.7 Multi-chip encoding                  | 72 |

|    |     | 10.8 Event size limit and data filtering  | 73 |

|    |     | 10.9 Precision ToT data                   | 74 |

|    |     | 10.10 Format Options                      | 75 |

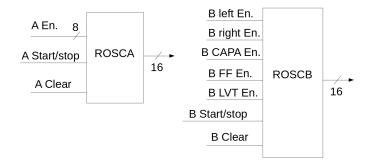

| 70 | 11. | Multi-Chip Data Aggregation               | 76 |

|    |     | 11.1 Data Receivers                       | 76 |

|    |     | 11.2 Setup and Operation                  | 76 |

|    |     | 11.3 Data flow, alignment, and idles      | 78 |

|    | 12. | Sensing and Monitoring Functions          | 79 |

| 75 |     | 12.1 Analog Multiplexer (MUX)             | 80 |

|    |     | 12.1.1 Multiplexer Configuration          | 80 |

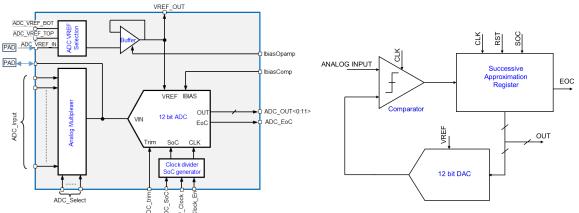

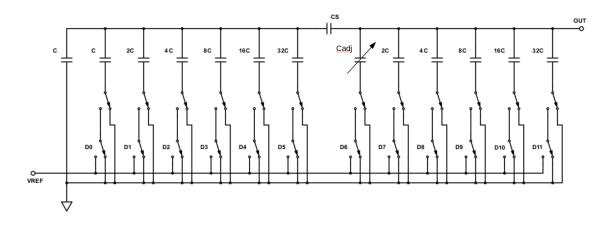

|    |     | 12.2 General Purpose ADC                  | 80 |

|    |     | 12.2.1 12-bit DAC                         | 81 |

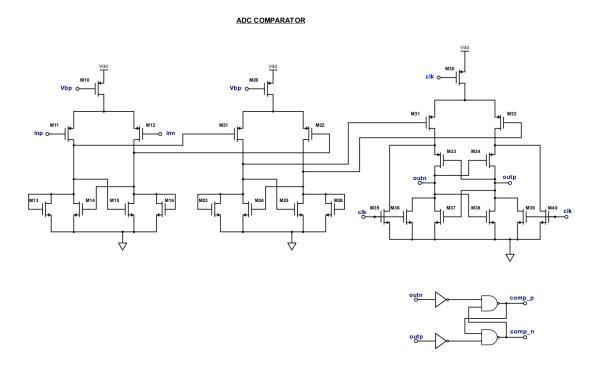

|    |     | 12.2.2 ADC comparator                     | 82 |

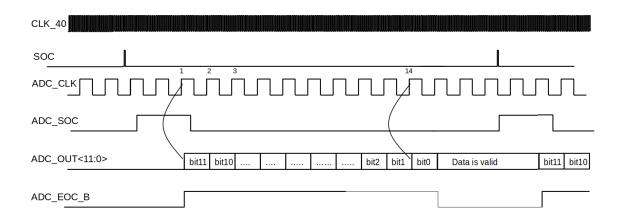

| 80 |     | 12.2.3 ADC conversion timing              | 83 |

|    |     | 12.2.4 ADC Configuration                  | 83 |

|     |     | 12.3                                                 | Transistor-based Temperature and Radiation Sensors                                                                                                                                           | 84                                    |

|-----|-----|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

|     |     | 12.3                                                 | 12.3.1 Transistor Sensor Theory                                                                                                                                                              | 84                                    |

| 85  |     |                                                      | 12.3.2 Precision Biases                                                                                                                                                                      | 85                                    |

|     |     |                                                      | 12.3.3 Measurement Approaches                                                                                                                                                                | 85                                    |

|     |     | 12.4                                                 | Resistive Temperature Sensors                                                                                                                                                                | 86                                    |

|     |     |                                                      | Sensor Configuration                                                                                                                                                                         | 87                                    |

|     | 13. | Test                                                 | and Miscellaneous Functions                                                                                                                                                                  | 88                                    |

| 90  |     | 13.1                                                 | General purpose LVDS and CMOS outputs                                                                                                                                                        | 88                                    |

|     |     | 13.2                                                 | Bypass mode                                                                                                                                                                                  | 88                                    |

|     |     | 13.3                                                 | Scan Chains                                                                                                                                                                                  | 88                                    |

|     |     | 13.4                                                 | Hit OR                                                                                                                                                                                       | 88                                    |

|     |     | 13.5                                                 | Heartbeat and test patterns                                                                                                                                                                  | 88                                    |

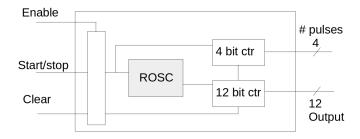

| 95  |     | 13.6                                                 | Ring Oscillators                                                                                                                                                                             | 88                                    |

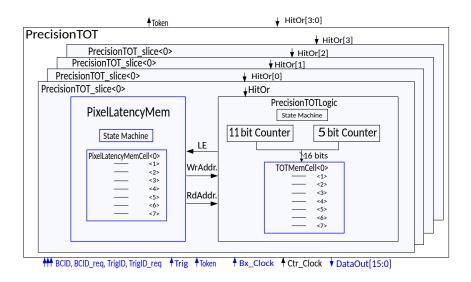

|     |     | 13.7                                                 | Precision ToT module                                                                                                                                                                         | 90                                    |

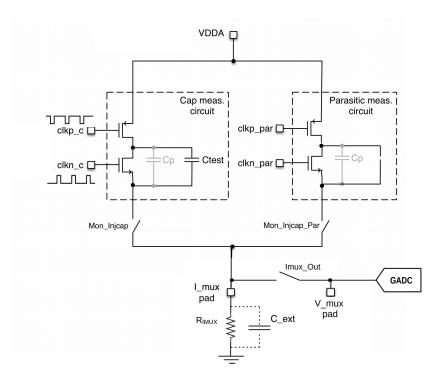

|     |     | 13.8                                                 | Capmeasure circuit                                                                                                                                                                           | 91                                    |

|     | 14. | Cloc                                                 | ck Generation and Data Recovery Technical Details                                                                                                                                            | 94                                    |

|     | 15. | Knov                                                 | wn Issues                                                                                                                                                                                    | 95                                    |

| 100 | 16. | Refe                                                 | erence Tables (pinouts, configuration, etc.)                                                                                                                                                 | 97                                    |

|     |     | 16 1                                                 | Wine Danding Dingert                                                                                                                                                                         | 0.7                                   |

|     |     | 10.1                                                 | Wire Bonding Pinout                                                                                                                                                                          | 97                                    |

|     |     |                                                      | Global Configuration                                                                                                                                                                         | 99                                    |

|     |     | 16.2                                                 |                                                                                                                                                                                              |                                       |

|     |     | 16.2<br>16.3                                         | Global Configuration                                                                                                                                                                         | 99                                    |

| 105 |     | 16.2<br>16.3<br>16.4                                 | Global Configuration IMUX and VMUX selection values                                                                                                                                          | 99                                    |

| 105 |     | 16.2<br>16.3<br>16.4<br>16.5                         | Global Configuration IMUX and VMUX selection values General Purpose LVDS and CMOS Output Assignments                                                                                         | 99<br>106<br>107                      |

| 105 |     | 16.2<br>16.3<br>16.4<br>16.5<br>16.6<br>16.7         | Global Configuration IMUX and VMUX selection values General Purpose LVDS and CMOS Output Assignments Internal and External Component Nominal Values Command and Trigger Encoding Output Tags | 99<br>106<br>107<br>108               |

| 105 |     | 16.2<br>16.3<br>16.4<br>16.5<br>16.6<br>16.7         | Global Configuration IMUX and VMUX selection values General Purpose LVDS and CMOS Output Assignments Internal and External Component Nominal Values Command and Trigger Encoding             | 99<br>106<br>107<br>108<br>109        |

| 105 |     | 16.2<br>16.3<br>16.4<br>16.5<br>16.6<br>16.7<br>16.8 | Global Configuration IMUX and VMUX selection values General Purpose LVDS and CMOS Output Assignments Internal and External Component Nominal Values Command and Trigger Encoding Output Tags | 99<br>106<br>107<br>108<br>109<br>111 |

#### 1. Overview

This manual provides a technical description of the RD53C chip design and operation adequate for simulation, testing, debugging and DAQ development. A basic familiarity with pixel systems and readout chips is assumed. A more general introduction explaining the basic functions and principles can be found in [6].

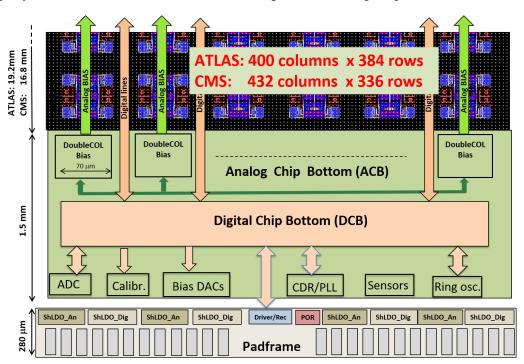

The production readout chips for the ATLAS and CMS HL-LHC pixel detectors are two separate instances of a common design framework called RD53C. The main differences between ATLAS and CMS are the size of the pixel matrix and the pixel analog front end. There are other differences partly stemming for the sequential fabrication: RD53C-ATLAS in spring and RD53C-CMS in fall of 2023. RD53C-CMS has a few minor added features relative to RD53C-ATLAS. For convenience this manual is compiled in two separate versions, RD53C-ATLAS and RD53C-CMS. This version is for the RD53C-CMS chip, designated by CMS as CROC-V2. Both manual versions use the same revision number as most of the elements are common. RD53C is an evolution of the RD53B framework [?] and RD53B-ATLAS and RD53B-CMS pre-production chips. The requirements were defined by the experiments for RD53B [2] and have not changed for RD53C.

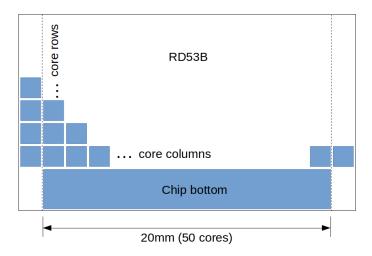

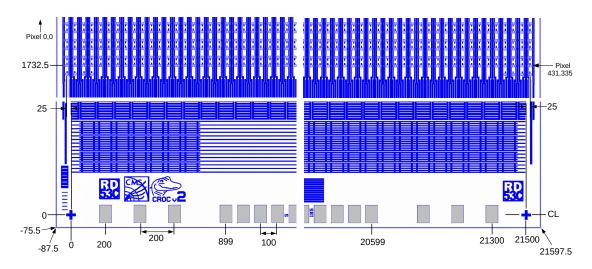

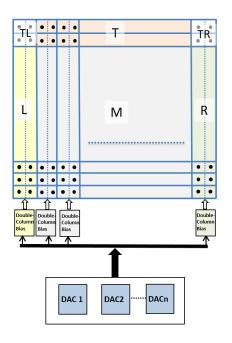

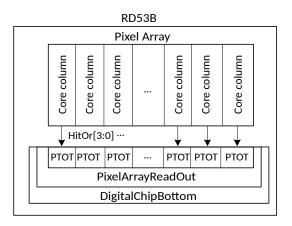

RD53C is a pixel readout chip framework that can be instantiated into different size physical chips. The design work and much of the verification are largely independent of the final instantiated size. RD53C consists of a *pixel matrix* and a *chip bottom*. The pixel matrix is built up of identical 8 by 8 pixel *cores* stepped and repeated in columns and rows. A core is physically  $400 \,\mu\text{m}$  by  $400 \,\mu\text{m}$ . The selected numbers of core columns and rows determine the chip size. The chip bottom contains all the system functionality and should be viewed as a fixed element that does not depend on matrix size. A physical chip, therefore, cannot be *narrower* than  $20 \,\text{mm}$  (50 cores), because that is the width of the unique wire bonding pad frame in the chip bottom, but it can be wider. The *height* (number of core rows) is not constrained by the chip bottom, but is limited to a maximum of 50 by power and bias distribution as well as readout timing. This high level organization concept is shown in Fig. 1. The instantiated dimensions are detailed in Sec. 2.

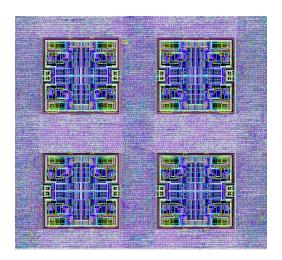

The core contains 64 pixel front ends organized in 16 identical so-called *analog islands* with 4 fronts ends each, which are embedded in a flat digital synthesized "sea" as shown in Fig. 2. The analog front end and island design are described in Sec. 5. The digital core design is described in Sec. 7. The pixel matrix is produced by stepping and repeating identical cores, which also takes care of the distribution of analog biases, as described in Sec 5.1.

The chip bottom contains all system functionality and the wire bond pads. RD53C is a system-on-chip including power management, sophisticated digital communication, sensing and monitoring. An overview of the basic operation, including a description of the reset scheme, is given in Sec 3. Sec 3 also serves as an introduction to the more detailed content of other sections. All tabular information, including pinout and configuration register values, is collected in the Reference section (Sec 16).

Power management, including design of the Shunt-LDO regulators are covered in Sec 4. The command and control interface (how one talks to the chip) and the configuration are covered in Sec 8. The data output (what comes out of the chip), including special (non-hit data) and the aggregation of data from multiple chips, are described in Sec. 10. The sensing and monitoring functions are described in Sec 12. Test features and miscellaneous functions are covered in Sec 13.

**Figure 1:** Conceptual depiction of RD53C framework, with a matrix composed of 50 or more columns by up to 50 rows of identical cores, and a fixed chip bottom. The dashed lines indicate the minimum width of 50 cores. Core number 0,0 is at the top left of the figure, while the highest column, row numbered core is at the bottom right.

**Figure 2:** Layout view of analog islands within synthesized logic. Four complete islands can be seen in the center of the figure. One core contains four by four analog islands.

The designs of the bump bond and wire bond pads are covered in Sec. 2.1 and 2.2. RD53C only has wire bond pads along the bottom edge, to make it 3-side abuttable.

| Parameter                         | ATLAS                                    | CMS       |  |  |

|-----------------------------------|------------------------------------------|-----------|--|--|

| Pixel bump pitch                  | $50\mu\mathrm{m} \times 50\mu\mathrm{m}$ |           |  |  |

| pixel rows (H)                    | 384                                      | 336       |  |  |

| pixel columns (W)                 | 400                                      | 432       |  |  |

| core rows                         | 48                                       | 42        |  |  |

| core columns                      | 50                                       | 54        |  |  |

| Chip width (including seal ring)  | 20.050 mm                                | 21.654 mm |  |  |

| Chip height (including seal ring) | 21.0213 mm                               | 18.622 mm |  |  |

**Table 1:** Size of ATLAS and CMS chips in cores and outline measured from outside edge of seal ring.

# 2. Dimensions, Floorplan and Pads

165

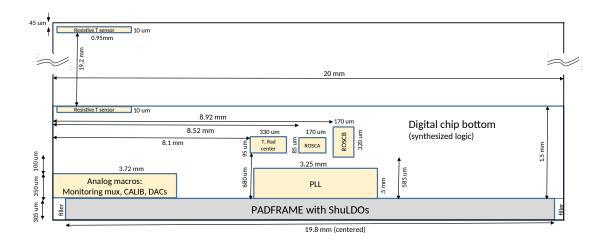

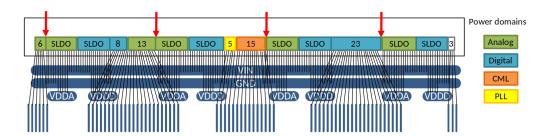

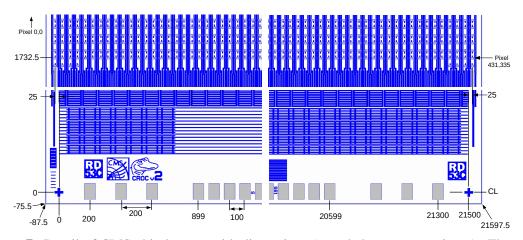

RD53C uses a 9 metal layer stack, consisting of 7 thin, 1 thick and 1 ultra-thick metal layers. In addition, the 28K AP layer is also used for power lines distribution. In Fig. 3 the layout and functional view of RD53C floorplan are shown. The sensitive area of the chip is placed at the top of the chip and is arranged as a matrix of pixel bump pads on  $50 \,\mu\text{m} \times 50 \,\mu\text{m}$  pitch according to Table 1. The peripheral circuitry is placed at the bottom of the chip and contains all global analog and digital circuitry needed to bias, configure, monitor and readout the chip. The wire bonding pads are organized as a single row at the bottom chip edge and are separated from the first row of bumps by 1.7 mm in order to allow for wire bonding after sensor flip-chip (Sec. 2.2).

Figure 3: RD53C floorplan, functional view.

In the chip periphery, all the analog building blocks are grouped in a macroblock called Ana-

log Chip Bottom (ACB), which is fully assembled and characterized in an analog environment. The ACB block is surrounded by a synthesized block, called Digital Chip Bottom (DCB), which implements the Input, Output and Configuration digital logic.

**Figure 4:** Size and location of elements in the CMS chip bottom and top (Not to scale). The outline is the chip seal ring (tightest possible diced edge).

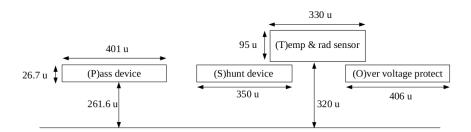

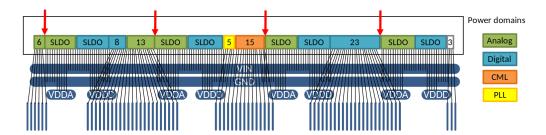

**Figure 5:** Size and vertical position of power devices relative to the chip seal ring (tightest possible diced edge). Horizontal placement is given in Table 2

| Device         | AO    | AS    | AP    | DP    | DS    | DO    | AO    | AS    | AP    | DP    | DS    | DO    |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Left edge (um) | 954   | 1371  | 1715  | 2734  | 3139  | 3480  | 6154  | 6571  | 6715  | 7934  | 8339  | 8680  |

| Device         |       |       |       |       |       |       |       |       | AT    | DT    |       |       |

| Left edge (um) |       |       |       |       |       |       | 7125  | 7825  |       |       |       |       |

| Device         | AO    | AS    | AP    | DP    | DS    | DO    | AO    | AS    | AP    | DP    | DS    | DO    |

| Left edge (um) | 11354 | 11771 | 12115 | 13134 | 13539 | 13880 | 16654 | 17071 | 17415 | 18434 | 18839 | 19180 |

**Table 2:** Companion table to Fig. 5 showing the position of the left edge of power devices in ATLAS chip relative to the outside edge of the seal ring: A=Analog, D=Digital, O=Over voltage protection, P=Pass device, S=Shunt device, T= Temperature and radiation sensor. The devices are arranged in four groups (delimited by double lines) as can be seen in Fig. 8.

#### 2.1 Bump Bond Pads

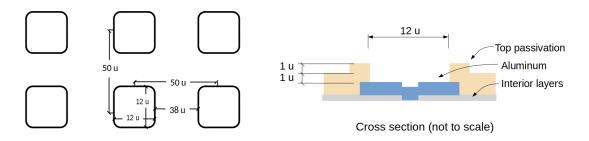

The bump bonds pads are defined by a regular pattern of openings in the passivation as shown in Fig. 6 (left). The alignment of aluminum metal shape under each passivation opening can vary by up to 1 μm from pixel to pixel, but as the shapes are bigger than the opening there is always exposed aluminum for the entire pad. The bump bond pads do not have ESD protection. The passivation opening is square with 45 degree corners, which will appear rounded in the as-built chip. Fig. 6 (right) shows the expected height profile across the center of a bump pad as derived from the metal stack. Aluminum metal is exposed in the 12 μm passivation opening and extends below the passivation beyond the opening, resulting in a passivation ridge surrounding the opening, as shown. The exposed metal may not be completely flat: it can have depressions less than 1 μm deep due to vias below. The figure shows such a depression.

Figure 6: Bump bond pad dimensions. Matrix layout on the left and cross section on the right.

#### 2.2 Wire Bond Pads and Alignment Marks

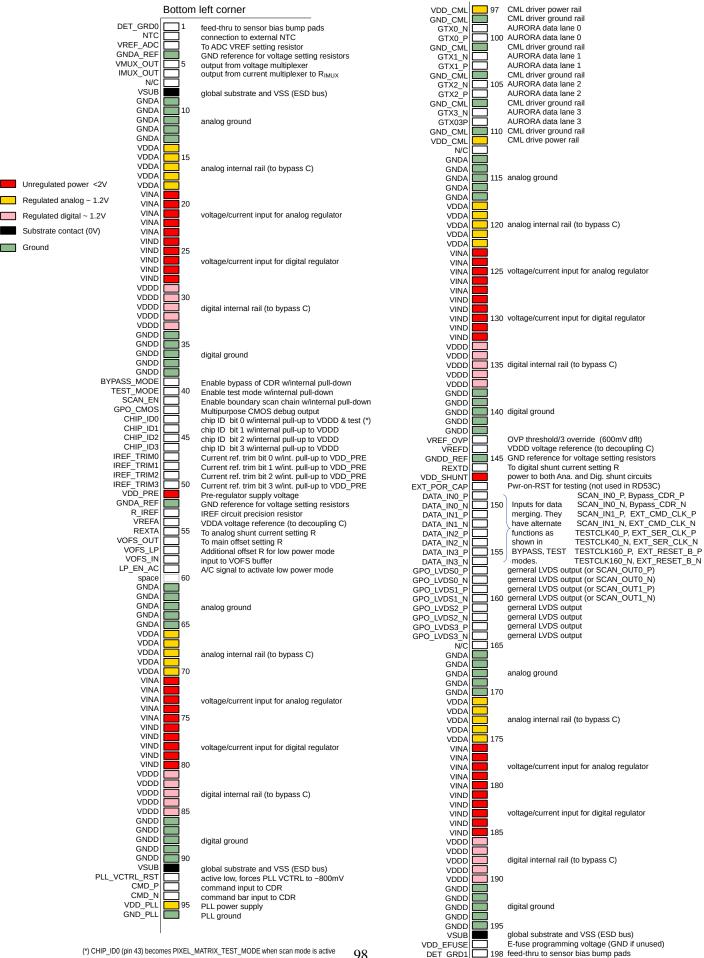

The wire bond pads are along the chip bottom on a  $100 \,\mu\text{m}$  pitch. The pad area is large enough to meet production requirements (Fig. ??). There are 198 pads, 4 of which are not used and not connected to any internal net. The location of these unused pads was chosen to eliminate wire bonding tool interference at the edges of fanout regions. Most pads are for power and ground and are grouped strategically for PCB/module layout as shown in Fig. 8. The detailed pinout is given in Sec. 16.1.

The wire bond pads have visible numbering on the chip (the numbers label the pads to their right), and are flanked by alignment marks, as can be seen in Fig. 7.

The RD53C chip has internally four separate power domains:

• Analog: VDDA, GNDA

190

- Digital: VDDD, GNDD

- PLL (PLL/CDR + CMD\_IN LVDS receiver): VDD\_PLL, GND\_PLL

- CML (serializer + cable driver): VDD\_CML, GND\_CML

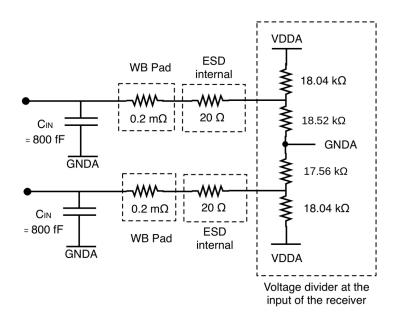

The local ESD devices connect to both power and ground rails or to the ground rail only in case of over-voltage tolerant pads (OVT). OVT pads are used where the input voltage could potentially exceed the local power rail (see pad listing in Sec. 16.1). In a typical environment, all ground rails are wire-bonded to the same system ground, which enables ESD paths between the (otherwise

isolated) power domains. However, during assembly or wafer probing, a common external ground rail might not be established yet. To account for this, a common ESD bus (VSS) has been used to connect the different ground rails via on-chip anti-parallel diodes to create a safe ESD path between power domains at all times. This net (VSS, also used for connecting the global substrate VSUB) **should be wire-bonded first** (pads 9, 91, and 196), then all remaining ground pads, and finally the rest of the pads.

200

**Figure 7:** Detail of CMS chip dimensions. The location of the first and last pixel bump bonds on the matrix is also indicated. There are 4 bump bond pads below the full matrix on each of left and right sides to contact sensor bias/guard rings.

**Figure 8:** Organization of wire bond pad frame and generic bonding scheme. All wire bonds are shown, including connections for testing (not used on detector modules). The number of fanned-out signal bonds is written in each box, while the power supply bonds run parallel (not fanned out). The red arrows indicate the four unused pads.

## 3. Basic Operation and Reset (Intro and Quick Start Guide)

This section walks through the steps for basic, beginner level operation of a single chip on the bench. It also describes how the chip is reset- a critical point for correct start-up. Advanced users will often do things differently than stated in this introductory section, and so the more detailed sections of the document are referenced as appropriate. Thus, this section can also be used as a guide to the rest of the document. Each item in this section is just one choice out of several possible connections and configuration values (recommended for initial operation). Whenever registers or pins are mentioned they can be found in the reference section (16).

## 3.1 Chip Startup

The startup sequence is power, clock, communication, configuration, operation.

**Power** Typical bench testing will use the LDO powering option, in which the internal regulators are used as classic linear regulators fed from a constant voltage power supply, rather than serial power regulators fed from a constant current supply as they will be used in the experiment. LDO powering is more convenient for single chip testing (LDO stands for Low Drop Out voltage). A single chip card will contain jumpers to select LDO mode. A single power supply will be connected to all the chip's V\_IN pins, while the shunt mode controller voltage, VDD\_SHUNT, will be disconnected, which is all that is needed to disable shunt mode. For details see Sec. 4, which also describes the serial power and direct power configurations. External components should be set to their nominal values (Table 30). A power supply current limit of 2 A (half analog and half digital) will be typical.

LDO mode allows to view the internal current consumption. (VINA and VIND can be connected individually to monitor currents in analog and digital domains). The supply voltage should be a minimum of 1.4 V and never more than 2.0 V. 1.6 V should be a typical setting to have comfortable margin for cable voltage drops. When power is turned on, the current consumption will be determined by the default configuration, which is low (normal) power for the ATLAS (CMS) chip. Typical current consumption is given in Table 3. The VDDA and VDDD regulator outputs, which connect to external decoupling capacitors, should produce approximately 1.2 V, which is the default setting (one should verify that this is the case when first testing a chip). Both the regulated voltages and current consumption will be affected by the main reference current (Iref), which has a nominal value of  $20 \,\mu\text{A}$  and can be trimmed with wire bonds (or jumpers on a single chip test card) if needed (Sec. 4.2). Without any IREF wire bonds (or jumpers on a single chip test card) the current reference will be at its maximum value, significantly more than 20 µA, while default and recommended configuration settings assume  $20 \,\mu A$ . Since all internal biases are derived from this current reference, all bias currents will be high in this case. A very quick and dirty solution to this is to wire bond (or load the jumper on a single chip card) the most significant bit, which will trim to the middle of the trimming range.

Clock The PLL Clock Data Recovery circuit will become active as soon as it has power and will produce clock edges on all the internal clocks even in the absence of any external command input. But these will have arbitrary frequency and phase. This arbitrary clock is useful as a diagnostic: it will drive the data output stage (all four CML outputs) and produce a "heartbeat" idle pattern that

|                            | A'     | ΓLAS (mA | <b>(</b> ) | CMS (mA) |         |       |  |

|----------------------------|--------|----------|------------|----------|---------|-------|--|

| Status                     | Analog | Digital  | Total      | Analog   | Digital | Total |  |

| Power only (I/O unplugged) | 160    | 185      | 345        | 650      | 400     | 850   |  |

| Communication up           | 165    | 270      | 435        | 650      | 430     | 1080  |  |

| Configured for testing     | 700    | 740      | 1440       | 800      | 740     | 1540  |  |

**Table 3:** Typical current consumption for single chip bench test operation, assuming a nominal  $(20 \,\mu\text{A})$  reference current (Iref). Unconnected Iref pins/jumpers can result in 15% higher values. The total column is what should be observed when using a single power supply, as recommended.

can be observed to confirm that the chip is alive and the data connections present. But this arbitrary clock is not useful for operation. For that one needs a known frequency and phase clock that is obtained by locking to the incoming command bitstream.

The initialization and reset procedures needed to establish a proper clock and communication will be carried out automatically by the DAQ without user intervention, but they are described here to provide a basic introduction to how the chip operates and allow troubleshooting.

250

The reset organization is described in Sec. 3.2. Regardless of the state of the command input during power up, after power is stable, communication must be initialized by first "idling" the command line to a nominal bitrate of 1 Mbps<sup>1</sup> for at least 10  $\mu$ s, and then supplying a 160 Mbps clock pattern (80 MHz effective clock frequency) for at least 1 ms. The clock pattern is an uninterrupted stream of PLL\_LOCK symbols (Sec. 8.2). This is equivalent to a No Operation (NOOP) command in many processors, and can be used as filler when no other commands must be sent, but it will be referred to as PLL LOCK or PLLlock in RD53C.

This "idling" of the command line is the main hard reset mechanism for RD53C. It can be done at any time to recover the chip from a bad state without a need to power cycle. It should be thought of as the equivalent of power cycling hard reset, so it is a reset tool of last resort. After the command idle reset, the PLL will enter lock mode, and supplying a clock pattern is critical for it to lock to the correct frequency. The locking of the PLL can be verified with an optional diagnostic output (see below), but during detector operation this diagnostic will not be available and there will be no external indication that the PLL has locked. It will therefore be necessary to hold the clock pattern long enough to leave no doubt that there has been enough time to lock (1 ms). Further details are given in Sec 14.

**Optional Diagnostics** During bench testing it is possible to access a variety of test outputs. The chip has one CMOS and four LVDS general purpose outputs that can show a selection of internal signals (see Sec. 16.4). By default these carry the following information:

CMOS: gpo\_ch\_sync\_lock: 1 if the ChannelSync is locked, 0 when it is unlocked (see below). LVDS\_0: CMD\_raw: repeater of the chip command serial input. A buffered version of what the chip receives.

LVDS\_1: cdr\_cmd\_data\_predel: sampled input command pattern before applying any delay (should be very similar to the above).

<sup>&</sup>lt;sup>1</sup>A DC level- low or high- instead of 1 Mbps will also work for initiating the reset, but is not advised for A/C coupled command lines.

LVDS\_2: PorResetB: output of Power On Reset circuit (active low) in case it is needed (not normally used in RD53C).

LVDS\_3: gpo\_cdr\_lock\_status: PLL Lock signal. 1 if Locked, 0 otherwise (see clock above).

Communication Now the all clocks will be at the correct frequency and the gpo\_cdr\_lock\_status shown above should be high. But the chip is not yet ready to understand commands, because the alignment of the incoming command frames has not yet been established (gpo\_ch\_sync\_lock should still be low). This alignment is done by a circuit called the channel synchronizer, that recognizes unique bit patterns called sync symbols (all command symbols are described in Sec. 8). Therefore, after the clock pattern, the sending of sync symbols will be enabled (once again, the DAQ system will do this automatically). One can send a constant string of sync symbols or simply enable automatic insertion of one sync every N frames (where N is set by configuration, default 32). So either (sync, sync, sync,...) or (PLLlock, PLLlock, PLLlock, sync, PLLlock, PLLlock,...)-it makes no difference. The important thing is to send a large number of sync symbols (exceeding a minimum number set by configuration, default 16) before sending any commands. When the channel synchronizer locks, the gpo\_ch\_sync\_lock signal will go high on the general purpose CMOS output. Commands will not be accepted (so the chip configuration cannot be changed) unless this lock signal is high. Again, the DAQ will normally ensure the correctness of this sequence with no need to look at the diagnostic signals.

The CMS chip has a reduced power default configuration. The chip starts with a power consumption a bit lower than nominal: the analog FE are set to absorb  $4 \mu A$  instead of the nominal  $5 \mu A$ , the global threshold is set to a very high value and the comparators are set in such a way to prevent anomalous currents at startup. Moreover, only 1/3 of pixels receive the clock.

In general a new configuration will have to be loaded for most single chip testing. Test setups will include a baseline configuration suitable for most tests (which may also be called default in test setup documentation, should not be confused with the internal chip default configuration).

#### 3.1.1 Default and User Configurations

275

295

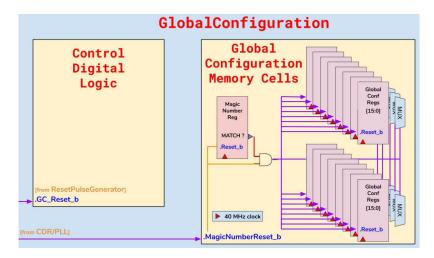

When the chip starts up and is reset, (A) the global configuration will be supplied by internal hard-wired default values and (B) the user programmable configuration registers will be automatically loaded with those same default values. This complex scheme of having two configurations (hard-wired and programmed) is needed to ensure that the default configuration is present immediately upon power-up or upon CMD idle reset, regardless of the presence of a clock, or of the time it takes to load the programmable configuration registers. Which of the two configurations controls the chip is determined by multiplexers associated with each register, as indicated in Fig. 9. At start-up, the hard-wired default global configuration will be controlling the chip. The same mechanism is implemented for the pixel configuration, but unlike the pixel matrix, where the programmed configuration has no reset at all, the global configuration has both the MUX and a synchronous reset, so that whenever the MUX selects the hard-wired configuration, the programmed values will soon (when clocks arrive) be reset to equal the hard-wired values.

In order to use a programmed configuration different from the default, control of the chip must first be switched over from the hard wired to the programmable configuration. The configuration selection is controlled by both the CMD idle reset signal and a logic comparator that

**Figure 9:** Configuration selection and reset.

compares the value stored in a pair of special configuration registers (32 bits total) to a hard-wired key code or "magic number" (labeled MagicNumberReg in the figure). When the stored value does not match the key, the hard-wired configuration is selected. Since at power-up the registers will contain something arbitrary, and will be reset to zero as soon as clock edges are present, the hard-wired configuration will be selected. To switch over control of the chip to the programmed configuration, the user must write the key into the magic number registers (the key code is Hex AC75 in GCR\_DEFAULT\_CONFIG and Hex 538A in GCR\_DEFAULT\_CONFIG\_B, as can be seen in Table 22). Since at start-up the programmable registers will have been initialized to the default configuration, when the magic number is written and the control of the chip switches over, nothing should actually change, because each register is switched from the hard-wired default to the same default in a its programmable register. This is important to avoid a sudden current jump since all registers switch over at the same time. Now each programmable register can be written to the desired value, one at a time.

To guard against SEU, in addition to being triple redundant (as are all global configuration registers), any permutation of the key codes with one bit flipped will also select the programmed configuration. In addition to a possible bit flip in the key code, an SEE could put a glitch in the MUX control level and that will cause the active configuration bits to switch between hard-wired and programmed for the duration of the glitch. This is relatively benign and not persistent: after the glitch everything will be in the original state and there is no corruption of the stored configuration. Most configuration bits control DACs, which have a slow response time and will therefore not propagate a glitch in their control bits to their output analog level.

#### 3.2 Reset

340

The driving requirements of the RD53C reset scheme are:

Avoiding introduction of Single Event Effect vulnerability. This led to having reset capability

only on circuits that absolutely need it, and to use only synchronous reset for them. A

synchronous reset signal is a logic level that is sampled locally every clock edge. Spurious

glitches on this reset signal have no effect (in contrast to an asynchronous reset, for which a transition produces a reset regardless of clock).

- Need for a default configuration present immediately upon power up. This is done without the use of a power-on reset, as this would require an asynchronous reset on the global configuration registers. The default configuration is not stored in registers, but hard-wired and selected by a 2-to-1 multiplexer (Sec. 3.1.1)

- The ability to reset a chip (or a subcircuit within) without cycling the power, which would require tuning off and on an entire serial chain. This is accomplished with activity detection on the command input (Sec. 3.2.1)

Figure 10: Block diagram of reset signals in the RD53C chip as described in the text.

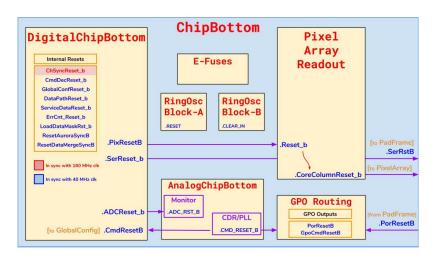

The overall reset organization is shown in Fig. 10. All signal use negative logic: low means reset. There is a power-on reset generation circuit in the chip, inherited from RD53A, but the output of this circuit is not used to reset anything in RD53C and is only sent to the general purpose output multiplexer so that is available for external routing. The only asynchronous reset signal that is used in RD53C is the command activity detector (Sec. 3.2.1), labeled .CMD\_RESET\_B in the figure. This signal performs 3 functions: (1) it resets the PLL circuit that recovers the clock, (2) it selects the default configuration (Sec. 3.1.1), and (3) it is used (after synchronization) to actuate all the synchronous resets in the digital chip bottom.

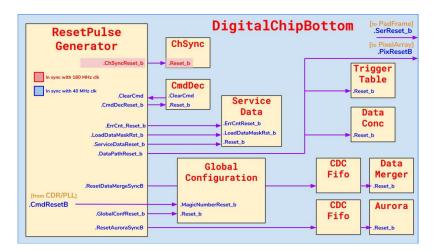

All digital blocks have synchronous resets. These can be individually actuated at any time using the Global Pulse command, in addition to the actuation by the synchronized .CMD\_RESET\_B signal in (3) above. The organization of the digital block resets is shown in Fig. 11. The global configuration registers are explained in Sec. 3.1.1. The logic to write and read global configuration has its own synchronous reset, labeled .GlobalConfReset\_B in the figure.

# 3.2.1 Command Activity Detector

345

350

The purpose of this circuit is to provide a "hard reset" mechanism for PLL/CDR block that recovers the clock from the input command stream and controls internal resets. The command activity

Figure 11: Block diagram of reset signals in the RD53C digital bottom as described in the text.

detector measures the rate of transitions in the incoming command signal. A positive edge rate below a nominal 10 MHz causes a reset to be asserted, while a higher frequency removes the reset. This nominal 10 MHz threshold has a significant uncertainty, with process, voltage, and temperature dependence. Thus, an edge rate <10 MHz (called idling) should be provided to guarantee reset, while normal command activity has a positive rate always between 30 MHz and 80 MHz. The circuit bandwidth is low enough that it takes of order 2  $\mu$ s after command line idling for the reset to be asserted. It will take of order 0.5  $\mu$ s to release the reset once the command line is returned to normal.

The activity detector is part of the PLL/CDR block. It directly resets the PLL, which means it puts it back into frequency lock mode.

This is the main hard reset mechanism of the RD53C chip, conceptually equivalent to cycling the power in a typical system. This is necessary because in a serial power chain, cycling the power is truly an action of last resort that should never be needed.

## 4. Power and References

RD53C is designed for operation in a serial powered system, where multiple chips are powered in parallel within a module, and multiple modules are connected in series. All circuits needed for such operation are built into the chip, such that only passive external components are needed to implement serial power chains. The foundation of this system a custom constant current regulator called Shunt LDO (SLDO). In addition to the SLDO proper, RD53C contains auxiliary circuits including voltage/current references with automatic start-up (Sec. 4.2), "under-shunt" transient protection analogous to a current limit for constant voltage supplies (Sec. 4.4), overvoltage protection (Sec. 4.5), and a low current operation mode for detector tests with limited cooling (Sec. 4.3).

## 4.1 Shunt LDO Regulator

The Shunt LDO regulator (SLDO) regulator is a combination of a linear Low Drop-Out voltage regulator (LDO) and a shunt element. The goal is to provide constant current operation with multiple devices connected in parallel (which is not possible for conventional shunt regulators). The circuit was invented as part of the FE-I4 chip development [4], but the design has evolved significantly towards the final implementation in RD53C.

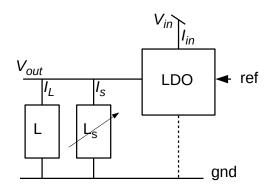

The basic principle of operation of the SLDO circuit can be explained using Fig. 12. A conventional LDO voltage regulator is used to power the main load, L, as usual, plus an internal load,  $L_s$ , in parallel. This internal load (referred to as the shunt element, hence  $L_s$ ) is actively controlled to achieve the desired behavior at the input, no matter what the main load L does. To first order, the desired behavior is  $I_{in} = I_L + I_s = constant$ .

**Figure 12:** Concept of SLDO operation as a linear regulator (LDO) powering an main load L and a variable internal shunt load  $L_s$ .

The real needed behavior for serial power operation is more complex in order to achieve efficient current sharing among parallel chips and is given by Eq. 4.1.

$$I_{in} = I_L + I_s = \frac{V_{in} - V_0}{R_{\text{eff}}}$$

$[V_{in} > V_0]$  (4.1)

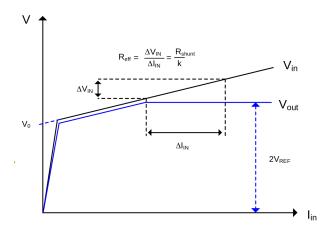

where  $V_0$  is a constant but programmable offset needed for high efficiency and  $R_{\text{eff}}$ , also user programmable, gives an ohmic behavior necessary to share current evenly among parallel devices. A diagram of the desired behavior is shown in Fig. 13.

**Figure 13:** Desired current vs. voltage characteristics for SLDO. The unregulated input voltage and regulated output voltage are shown. Indicated values are discussed in the text.

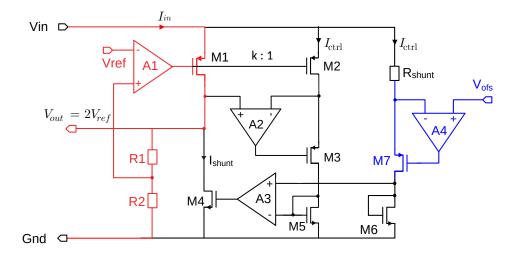

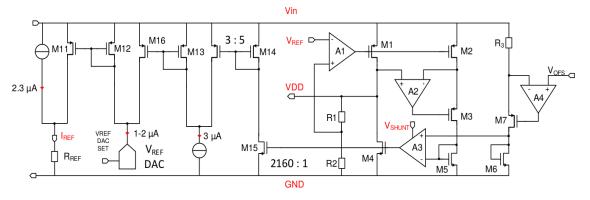

The simplified circuit schematic of the RD53C SLDO is shown in Fig. 14. The red part of the circuit is a classic LDO regulator with pass device M1. The rest of the circuit can be disabled in order to operate in pure LDO mode, which is useful for testing individual chips and for observing the current consumption. The main load L (external to the SLDO) is not shown- it is the chip itself. Device M4 is the internal load,  $L_s$ , of Fig. 12 and the rest of the black circuitry is the active control. This control ensures that the current in the pass device M1 is equal to the the current through  $R_{\text{shunt}}$  ( $I_{ctrl}$  for control current) times the scale factor K, which has a design value of 1000.  $R_{\text{shunt}}$  is an external resistor to allow the user precise control  $R_{\text{eff}}$ . It can be seen that  $R_{\text{eff}} = R_{\text{shunt}}/1000$ . Finally, the blue circuit provides the offset  $V_0$ . This is controlled by a reference voltage labeled  $V_{\text{ofs}}$ . User control of  $V_{\text{ofs}}$  is described in Sec. 4.3.

The SLDO circuit is designed to be compatible with 2 V input voltage. All transistors are cascoded in order to always have more than two transistors between voltage supply and ground, with supply voltage distributed across several transistors. Device voltage limits checks in static and dynamic simulations show that no transistor sees more than 1.32 V across any two terminals, even during transients. The one exception is the pass device M1, where cascoding to protect against over-voltage would cause higher drop-out voltage and therefore higher power consumption. This lack of cascoding of device M1 leads a lower limit to the undershunt protection range equal to Vref (Sec. 4.4). The SLDO circuit also uses a Low-ESR output capacitor compensation scheme, such that careful control of the external component equivalent series resistance (ESR) is not necessary.

#### 4.2 References and Startup

For serial chain operation the SLDO must become active immediately upon current flow, before communication is possible. Once operational, it must work with high efficiency and uniformity among chips in the chain. Furthermore, startup must work reliably over a wide temperature range,

**Figure 14:** Simplified schematic RD53C SLDO regulator. The colors differentiate the LDO (red), shunt (black), and offset (blue) functions as discussed in the text.

from room temperature for bench testing and wafer probing, to the evaporative cooling base temperature (taken to be  $-40^{\circ}$ C, that may be reached before power is applied. The generation of current and voltage references is intimately connected to the startup behavior.

**Figure 15:** Generation of references and recommended connection to internal grounds. See Fig. 16 for further detail on R\_OFS, shown here as a single resistor.

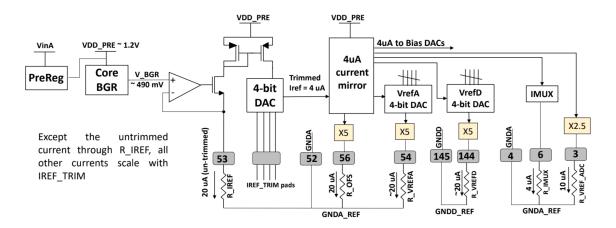

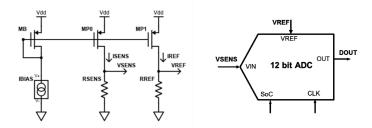

The RD53C reference scheme is shown in Fig. 15. RD53C does not use the SLDO output to power any reference circuit. A dedicated low current linear regulator (the *preregulator*) is used to power the main reference current generator. All other references are then derived from this unique main reference current. The preregulator is outside of and in parallel to the chip power delivered by the SLDO, but because it is low current it does not noticeably alter the behavior of Eq. 4.1 and Fig. 13. The preregulator includes its own dedicated bandgap voltage reference, which does not

430

need to be very precise, as the preregulator output does not need to be exactly 1.2 V, but merely between 1.1 V and 1.32 V. The preregulator is a low power device capable of a current of order 20 mA. This maximum current can be reached at very high shunt current  $I_s$ , well beyond normal operation values, and symptoms of a saturated pre-regulator can include increased jitter in the PLL leading to worsening of the output data eye diagram.

The Core Bandgap generates the main reference current, which can be adjusted with a 4-bit trim set by wire bond pads with internal pull-up resistors. This allows to compensate for process variations and equalize all chips to the design reference current value of  $20 \,\mu$ A. Note that unless some of the pads are externally grounded the reference current will be at its maximum value. The generated main reference current also depends on the external resistor  $R_{Iref}$  (Table 30), which is external in order to avoid the temperature variation of internal devices. The two LDO reference voltages,  $V_{ref}$  analog and  $V_{ref}$  digital, are each generated by a known current (derived from the main reference) across a dedicated external resistor (Table 30). Each  $V_{ref}$  is independently adjustable by configuration to allow some fine adjustment of the chip internal operating voltage.  $V_{ref}$  adjustment does not change the  $V_{in}$  vs.  $I_{in}$  behavior of the chip, making sudden jumps due to configuration upset or operator error harmless for serial chain operation. The offset reference  $V_{ofs}$  is common to both SLDOs and is not adjustable by configuration, as sudden jumps in  $V_{ofs}$  would be problematic for serial chain operation. The generation is shown in Fig. 16.

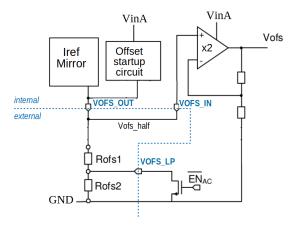

**Figure 16:** Offset voltage generation and startup. See text for description. The resistors in series Rofs1 and Rofs2 may sometimes be referred to as simply Rofs. The dashed blue line separates internal from external components and connections, while wire bonds pads are indicated by the pin symbol and blue labels. See Fig. 18 for optional connection of the VOFS\_OUT and VOFS\_IN wire bond pads on a module.

#### 4.2.1 Offset Voltage Start-up

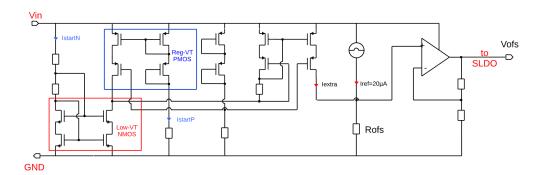

As the main current reference that all bias currents are derived from is powered from a dedicated linear regulator (the preregulator), circular dependencies requiring start-up circuits are generally absent from RD53C. However, the offset voltage (Vofs\_half) does require a startup (Fig. 16), because a very low offset voltage would cause the shunt device (M4 of Fig. 14) to be fully on, and this would clamp the input voltage,  $V_{in}$ , to a low value even if a large current were supplied. This

is especially critical for low power mode (Sec. 4.3). The built-in start-up circuit shown in Fig. 17 boosts the offset voltage to follow  $V_{in}$  until  $V_{in}$  is high enough for the preregulator to work and all references to be at their correct values. The circuit injects a current into the offset voltage setting resistor until the preregulator reference voltage rises. The rise of the preregulator reference shuts off this startup circuit.

**Figure 17:** Offset voltage startup circuit. The Resistor Rofs is either Rofs1 in normal operating mode or Rofs1 + Rofs2 in low power mode (see Fig. 16).

### 4.3 Offset Voltage and Low Power Mode

475

The SLDO offset voltage plays critical roles. It is the most important voltage for regulators operating in parallel, because the total current in a given SLDO,  $I_{in}$ , is very sensitive to  $V_0$  (and therefore to  $V_{ofs}$ ), as can be seen by the  $dI_{in}/dV_0$  derivative to Eq. 4.1, which is  $-1/R_{eff}$ . (This is also true for  $dI_{in}/dV_{in}$ , but  $V_{in}$  is by construction equal for all SLDOs wired in parallel.) It is very important to note that the actual offset voltage,  $V_0$ , in Fig. 13 is twice the generated Vofs\_half voltage. This is because the actual offset voltage may need to be higher than the preregulator output voltage, and so is impossible to generate directly. A  $\times 2$  buffer with  $V_{in}$  rail internally generates the true offset voltage from Vofs\_half (Fig. 16). Only Vofs\_half is accessible outside the chip and can be manipulated via the VOFS\_OUT, VOFS\_IN and VOFS\_LP wire bond pads.

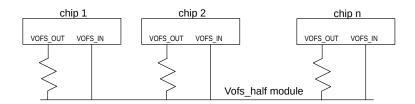

$V_{\rm ofs}$  may not necessarily be equal for different chips placed in parallel, and this can lead to current imbalance. While a small value of  $R_{\rm eff}$  will make a single SLDO more efficient (lower voltage drop between  $V_{in}$  and  $V_{out}$ ), it can make a multi-chip module less efficient by amplifying a small  $V_{\rm ofs}$  chip-chip mismatch into a large current imbalance. Two solutions to this problem are possible in RD53C  $^2$ . First, it is possible to trim the main current reference to produce a target  $V_{\rm ofs}$  value, rather than to produce a target current value. This will result in a larger chip-chip variation of reference current, but since all internal biases are adjusted with dedicated DACs this is not a problem. In return for the larger variation of reference current there will be a smaller variation in offset voltage. The second solution is to tie together the  $V_{\rm ofs}$  outputs of all chips in the same module via resistors (Fig. 18). For this purpose, in RD53C the  $V_{\rm ofs}$  output of Fig 16 and the  $V_{\rm ofs}$  input of Fig 14 are on separate wire bond pads.

$<sup>^2</sup>$ Assuming the  $R_{

m ofs}$  resistors cannot be practically trimmed individually

**Figure 18:** Common offset voltage wiring option for a multi-chip module. The VOFS\_OUT and VOFS\_IN wire bond pads can be seen in Fig. 16 and Table 22. For single chip operation VOFS\_OUT should be simply looped back to VOFS\_IN.

The common  $V_{\text{ofs}}$  wiring of Fig. 18 is robust against chip failure. Should one of the  $V_{\text{ofs}}$  outputs be grounded, the common  $V_{\text{ofs}}$  will be reduced. This will cause the working chips to draw more current for a given  $V_{in}$ , which is actually beneficial in the case the failing chip draws low current, as the working chips must now carry the extra current from the failing one.

Rather than a single external resistor to set  $V_{\rm ofs}$ , Fig 16 shows two resistors with a center tap switch- effectively a 1-bit variable resistor. The switch is internal in RD53C, while the resistors are external. This allows implementation of a low power serial chain mode. For normal serial chain operation the switch is conducting and the resistor value is just  $R_{\rm ofs1}$ . When the switch is off, the resistor becomes  $R_{\rm ofs1} + R_{\rm ofs2}$ , leading to a higher  $V_{\rm ofs}$ . A higher  $V_{\rm ofs}$  means that a small current will develop a high enough value of  $V_{in}$  needed for the SLDO output to reach 1.2 V. This also requires the default configuration to be very low current, as is the case in RD53C ATLAS.

The switch is controlled by a dedicated A/C input as this mode is only intended for use during detector construction, when additional contacts can be made. An A/C signal on this special input will turn the switch off, and the absence of a signal (as will be the case for normal operation) will leave the switch conducting. Note that if this high  $V_{ofs}$  low power mode is never needed one can simply leave out  $R_{ofs2}$  and connect  $R_{ofs1}$  to ground, in which case it no longer even matters what the state of the switch is.

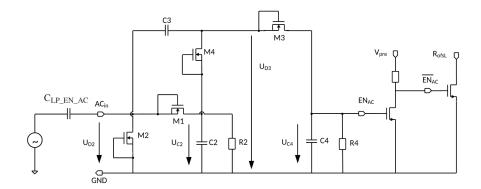

The amplitude of the A/C signal to activate low power mode should be 1.2 V peak-to-peak and should not exceed 1.32 V. A square wave with a rise time below 100 ns should have any frequency larger than 80 kHz, while a sine wave should have a frequency larger than 130 kHz. This assumes the A/C signal is coupled to the chip by a 100 nF external capacitor (Table 30). The rectification circuit that turns the A/C signal into an internal logic level is shown in Fig. 19. It consists of a 2 stage rectifier using low threshold NMOS transistors with applied forward-body biasing as rectification elements to achieve the minimum possible threshold voltage.

#### 4.4 Under-shunt Current Protection

490

510

The variable internal shunt load  $L_s$  of Fig. 12 can act to keep the total current constant as long as the load current drawn by the chip,  $I_L$ , is less than the programmed total current  $I_{in}$ . But if due to an error or fault condition  $I_L > I_{in}$ , then there is nothing the variable load  $L_s$  can do to prevent the total current from exceeding  $I_{in}$ . An additional function is need to react to the condition  $I_L > I_{in}$ . The under-shunt circuit acts to prevent the  $I_L > I_{in}$  condition. It is different from a classic current

**Figure 19:** Rectification circuit for external A/C signal that enables low power mode.

limiting circuit, because the programmed value of  $I_{in}$  is not fixed in advance, but set by an external resistor. Thus it is not possible to have a hard-wired absolute current limit.

Turning around Eq. 4.1,  $I_s = I_{in} - I_L$ , where  $I_s$  is the internal shunt current in M4 of Fig. 14. The desired condition  $I_L < I_{in}$  is equivalent to a non-zero shunt current,  $I_s > 0$ . Thus, the undershunt protection compares a scaled replica of the M4 current to a threshold (which does not have to be precise), and if it goes below threshold (known as the under-shunt condition), it reduces  $V_{ref}$  (by reducing the current it is derived from). Lowering the voltage powering the load L will reduce the load current  $I_L$ . The circuit is shown in Fig. 20. However, the  $V_{ref}$  is not allowed to drop below 0.35 V, to avoid the possibility of a voltage greater than 1.32 V across M1 of Fig. 20, which could cause permanent damage to the device.

Figure 20: Under-shunt protection circuit.

The under-shunt protection is disabled by default and must be enabled in the global configuration. It can prevent internal shorts from being visible outside the chip, as long as their effective resistance is greater than  $0.7 \text{ V/}I_{in}$ . It can also prevent transient "shorts" (for example due to a simultaneous firing all comparators or a wrong configuration setting) from drawing more than the programmed  $I_{in}$ . Simulations of selected test cases show that the under-shunt protection generally mitigates both DC shorts and transients, but it can also lead to internal oscillation when the reduction of the load voltage removes the under-shunt condition, but then the condition returns when the load voltage recovers. These internal oscillations are not expected to be a problem for the system

outside the chip. Ultimately, the use or not of under-shunt protection will have to be informed by system tests.

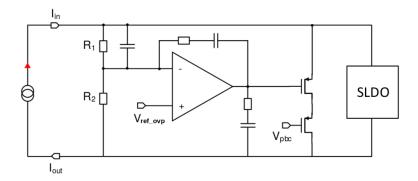

### 4.5 Over-voltage Protection

535

In the SLDO design the shunt element M4 of Fig. 14 is placed after the pass device M1. The total current draw is limited by the pass device and additional current cannot be shunted by M4. Therefore, classic over-voltage protection (OVP) is implemented with a current clamp in parallel to the SLDO. Since the voltage being clamped is  $V_{in}$ , which is common to both SLDOs, there is only one single clamp for the whole chip. The circuit is shown in Fig. 21.

Figure 21: Over-voltage protection clamp.

The OVP must only become active if the input voltage is close to 2 V. The clamp threshold is  $0.333 \times Vref\_ovp$ , where  $Vref\_ovp$  is an internal reference obtained as a copy of the preregulator bandgap output voltage  $Vref\_PRE$  and is expected to be around 0.6 V. This value can be overridden with the wire-bond pad  $VREF\_OVP$ , without affecting  $Vref\_PRE$ . OVP can be disabled by driving  $VREF\_OVP$  to a high value (for example  $VDD\_PRE$ ). Note that if multiple chips in parallel go into OVP, there is no current balancing mechanism for this function, so the chip with the lowest effective OVP threshold will take most of the current.

# 5. Analog Front End

The ATLAS and CMS chips use different front ends (FE). However, they are treated the same way by the design framework and share many features. Much about the RD53C FE can be described generically, applying equally to ATLAS and CMS. The FE is a pure analog circuit: it contains no memory latches, flip-flops or counters. Static configuration values are provided by the digital core, which receives only the comparator output signal from the analog part. The design is a small-area, low-power, free-running amplifier and discriminator for negative input charge. All necessary biases are generated in the chip bottom as described in Sec. 5.1. The calibration charge injection circuit and operation are described in Sec. 6.

The FE circuits are laid out in analog islands of 4 FE's each, as was described in Sec. 1.

#### 5.1 Front End Bias Generation and Distribution

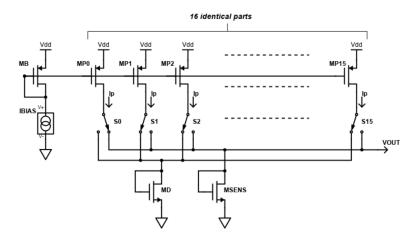

The bias voltages for the analog front-ends are provided by a set of programmable 10-bit DACs placed in the Analog Chip Bottom, near the pad frame. The list of configuration registers of the bias DACs is available in Sec. 16.2.

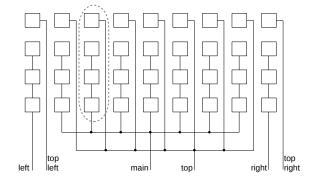

The bias distribution to the pixel array is based on a 2-stage scheme, as shown in Fig. 22. The biases from the DACs are distributed in parallel to the DOUBLE\_COLUMN\_BIAS blocks placed at the bottom of the pixel matrix. Then, each DOUBLE\_COLUMN\_BIAS generates and distributes the bias and threshold voltages to two pixel columns. The chosen granularity allows a certain level of redundancy, so that a hard failure in one pixel will not affect the bias of the full pixel array.

Figure 22: Bias distribution scheme.

**Figure 23:** Clarification of input device bias scheme. Each square is a 2 by 2 pixel analog island. All columns are identical, with two bias lines (an arbitrary column is circled). Six DACs at the chip bottom control different lines as indicated. The distinction between center, sides, top, and corners is made by which DACs connect to which columns.

The distribution scheme takes also care to provide dedicated biases to the edge and top pixels, that will serve larger than normal sensor pixels to span the gap between adjacent chips in quad or dual chip modules. Edge/top pixels may need different bias to cope with greater capacitance and leakage current than the normal pixels. Simulations of the analog front-end showed that the only bias requiring different setting is the current of the preamplifier input transistor: a higher current allows both to align in time the response of the edge pixels and also partially recover the noise increase due to the greater capacitance. Therefore, only the input transistor bias can be adjusted differently for edge/top pixels, while all other biases are the same everywhere. The distribution of the input transistor bias is illustrated in Fig. 23. This distribution creates six groups of 4-pixel islands: Main (the interior if the chip), Left edge, Right edge, Top, Top Left corner, and Top Right corner. Each group has its own dedicated DAC for the input transistor bias, and these DACs can be set to the same or different values as needed by changing the value of the corresponding DAC\_PREAMP\_{M,L,R,TL,TR}\_DIFF registers (ATLAS) or the DAC\_PREAMP\_{M,L,R,TL,TR}\_LIN registers (CMS) (see Table 22).

In addition to the input transistor bias, the global thresholds setting is also modular for the left and right edge double-columns. Instead, the pixels of the top edge do not have an independent threshold. Therefore, the chip is equipped with three global threshold DACs: <u>Left</u> double column, <u>Main array and Right</u> double column. The global threshold is then set by setting a fixed value to the DAC\_VTH2\_DIFF register, and adjusting the value of the DAC\_VTH1\_{L,M,R}\_DIFF registers (ATLAS) or adjusting the DAC\_GDAC\_{L,M,R}\_LIN registers (CMS) as needed (see Table 22).

# 5.2 CMS Analog Front End

590

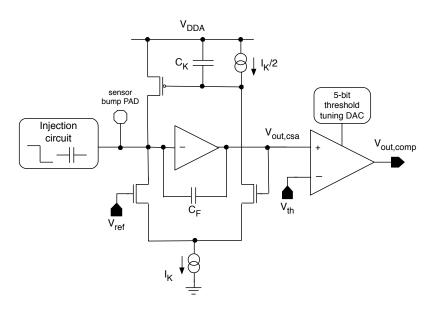

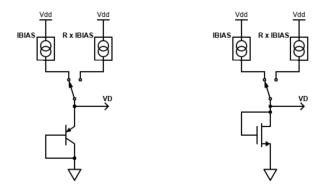

Figure 24: Schematic of the CMS analog front-end

The analog front-end (FE) for the CMS pixel readout chip is based on the RD53A Linear FE, with improved comparator and threshold-tuning DAC. The FE block diagram, with some transistor

level details, is shown in figure 24. The readout chain includes a charge sensitive amplifier (CSA) with Krummenacher feedback complying with the expected large radiation induced increase in the detector leakage current and providing a linear discharge of the feedback capacitor  $C_F$ . The designed charge sensitivity, set by  $C_F$ , is around 26 mV/ke<sup>-</sup>. The signal from the CSA is fed to a low power comparator that, combined with a time-over-threshold counter, is exploited for time-to-digital conversion. Channel to channel dispersion of the threshold is addressed by means of a local circuit for threshold adjustment, based on a 5-bit, current-mode binary weighted DAC. The front-end chain has been optimized for a maximum input charge around 30 000 electrons and features an overall current consumption close to 5  $\mu$ A.

600

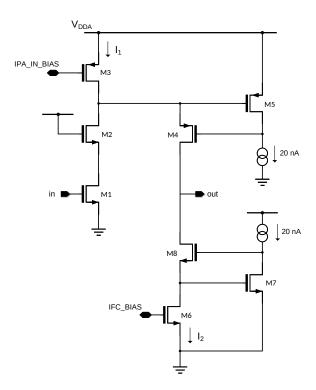

Figure 25: Charge sensitive amplifier forward gain stage.

The core element of the charge sensitive amplifier is the gain stage shown in figure 25. This is a folded cascode architecture including two local feedback networks, composed by the M4-M5 and M7-M8 pairs, boosting the signal resistance seen at the output node. With a current flowing in the input branch equal to 3  $\mu$ A and a current in the cascode branch close to 200 nA, the CSA is responsible for most of the power consumption in the analog front-end. The DC gain and the -3dB cutoff frequency of the open loop response, as obtained from simulations, are 76 dB and 140 kHz, respectively.

The noise performance of the charge preamplifier is mainly determined by the contributions from the CSA input device and from the PMOS transistor part of the feedback network. The preamplifier gain stage is identical to the one integrated in the RD53A Linear front-end. Notice that

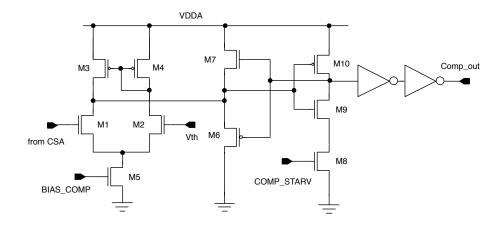

Figure 26: Threshold discriminator schematic diagram.

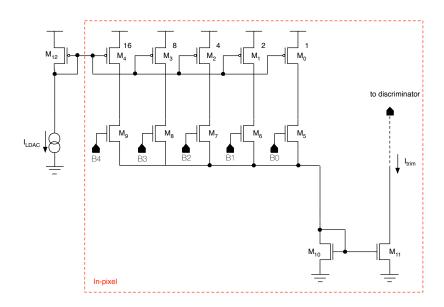

Figure 27: Threshold tuning DAC schematic diagram.

a gain selection bit was implemented in the RD53A version, whereas a single gain configuration is used in the CMS FE. Detailed simulation results are presented in [?].

The comparator schematic diagram is shown in figure 26. It includes a transconductance stage (M1-M5) whose output current is fed to the input of a transimpedance (TIA) amplifier providing a low impedance path for fast switching. A couple of inverters is used after the TIA in order to consolidate the logic levels. With respect to RD53A, the main modifications to the comparator are in its transimpedance stage. In particular, the TIA feedback network (transistors M6 and M7) has been modified with the aim of improving the time-walk performance of the front-end. A starving mechanism (transistor M8) has been added in the gain stage (M9 and M10) to limit the power consumption of the TIA. The trimming DAC schematic diagram is shown in figure 27. This is a 5-

**Table 4:** Linear AFE settings

|                | Rec | Std Range                      |

|----------------|-----|--------------------------------|

| FC_BIAS_LIN    | 20  | 10-70                          |

| Vthreshold_LIN | -   | REF_KRUM_LIN-900               |

| COMP_LIN       | 110 | 70-250                         |

| COMP_STAR_LIN  | 110 | 50-300                         |

| LDAC_LIN       | 110 | $80\text{-COMP\_LIN} \times 2$ |

| KRUM_CURR_LIN  | 70  | 5-200                          |

| PA_IN_BIAS_LIN | 300 | 100-700                        |

| REF_KRUM_LIN   | 360 | 300-450                        |

bit, current-mode, binary weighted DAC featuring regular current mirrors. The DAC output node, sinking a current  $I_{trim}$ , is connected to the output of the transimpedance stage of the comparator.

## **5.2.1 Front-end registers**

Table 4 reports a list of the DAC settings for the CMS AFE, showing the recommended (Rec) values and the operating range (Std range). The recommended values are used to operate the front-end with a total analog current of 5  $\mu$ A, with a ToT close to 130 ns for an input charge of 6000 electrons. Some simulation results are given in this section and more detailed results can be found in [?]. The DAC settings can be divided into two categories, in particular:

Main settings:

630

635

- Vthreshold\_LIN

- LDAC\_LIN

- KRUM\_CURR\_LIN

- Secondary settings

- FC\_BIAS\_LIN

- COMP\_LIN

- COMP\_STAR\_LIN

- PA\_IN\_BIAS\_LIN

- REF\_KRUM\_LIN

- The main DAC settings can be modified to achieve different threshold and ToT operation, whereas secondary settings should be in principle kept at their default value.

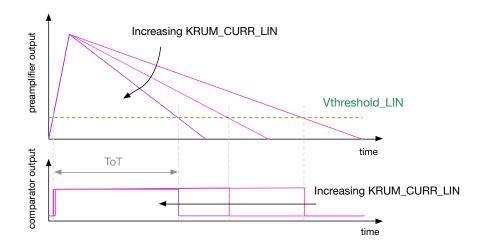

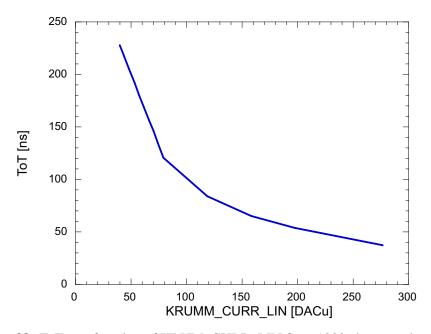

**Figure 28:** Effects of KRUM\_CURR\_LIN on preamplifier output waveform and ToT.

**Figure 29:** ToT as a function of KRUM\_CURR\_LIN for a 1000 electrons threshold.

# 5.2.2 Krummenacher current: KRUM\_CURR\_LIN

KRUM\_CURR\_LIN sets the current in the Krummenacher feedback, used to linearly discharge the preamplifier feedback capacitance. Increasing KRUM\_CURR\_LIN results in a faster preamplifier return to baseline and a reduced Time Over Threshold (ToT), as schematically shown in Fig. 28. The recommended value, 70, should results in a ToT close to 133 ns for an input charge of 6000 electrons. The simulated relationship between KRUM\_CURR\_LIN and the ToT is shown in Fig. 29, for a threshold set around 1000 electrons.

# 5.2.3 Global threshold: Vthreshold\_LIN

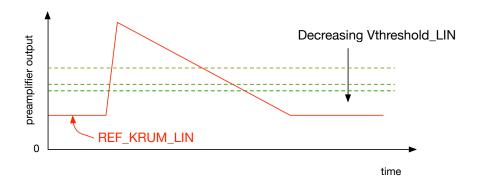

Vthreshold\_LIN sets the global threshold of the Linear AFE, corresponding to the DC thresh-

Figure 30: Effects of Vthreshold\_LIN on the global threshold.

old voltage applied to the discriminator input. Increasing Vthreshold\_LIN results in an increased global threshold, as conceptually shown in Fig. 30. It is worth noticing that the effective threshold is the difference between Vthreshold\_LIN and REF\_KRUM\_LIN which, in turn, sets the preamplifier output DC baseline (increasing REF\_KRUM\_LIN results in a higher baseline). Vhreshold\_LIN=400 should provide a threshold (after tuning) close to 1000 electrons (as REF\_KRUM\_LIN is kept to 360).

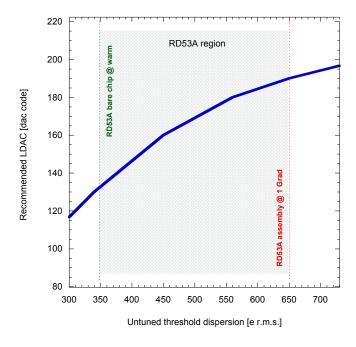

Figure 31: Recommended LDAC\_LIN values as a function of the un-tuned threshold dispersion.

#### 5.2.4 Threshold trimming: LDAC\_LIN

LDAC\_LIN sets the LSB of the in-pixel threshold trimming DAC and, in turn, its output dynamic range. In particular, LDAC\_LIN controls the current  $I_{LDAC}$  shown in the schematic of Fig. 27. Increasing LDAC\_LIN results in increased LSB and output range. An increase in the un-tuned

threshold dispersion is expected for the Linear AFE after irradiation. In that case it could be required to operate the front-end with an increased LDAC\_LIN in order to compensate for the larger dispersion.

Recommended values of LDAC\_LIN are shown in Fig. 31 as a function of the un-tuned threshold dispersion. Typical values of the untuned threshold dispersion before irradiation are in the range 350-550 electrons (as obtained from RD53A and prototype measurements, depending on sensors geometry, temperature, ...). As shown in the figure, the untuned threshold dispersion can get up to 650 electrons after irradiation at 1 Grad (from RD53A measurements).

#### 5.2.5 Secondary settings

675

680

- The DAC settings listed in this section are mainly related to preamplifier and comparator bias and should be, in principle, kept at their default value. A brief overview of these settings is given in the following.

- FC BIAS LIN: sets the current in the preamplifier folded cascode branch.

- COMP\_LIN: sets the bias current in the threshold discriminator input (transconductance) stage. This parameter can be slightly increased to improve speed.

- COMP\_STAR\_LIN: sets the maximum current flowing in the comparator output branch (controlled by the starving transistor M8 in Fig. 26).

- PA\_IN\_BIAS\_LIN: sets the current in the preamplifier input branch. This current represents

the main contribution to the Linear AFE current consumption. This parameter can be slightly

decreased to reduce power, at the cost of an increased noise.

- REF\_KRUM\_LIN: as explained in section 2.2, this parameter sets the preamplifier output DC baseline (V<sub>out,csa</sub> in Fig. 24).

## 6. Calibration Injection

The calibration injection circuit can internally inject signals into any combination of pixels without the need for a sensor or radiation. There are two types of calibration injection: digital and analog. The same command (Sec. 6.2) is used for both, and which one is active is selected by configuration in register CalibrationConfig (Table 22). Digital injection bypasses the front end and inputs a digital pulse to the hit processing logic as shown in Fig. 41. It is therefore relatively simple: the digital pulse generated by the Cal command is directly what the hit processing uses and is fully deterministic (no noise). It is useful to test proper functioning of the readout chain, as a timing reference for each pixel's FE analog delay, etc. The rest of this section is concerned with analog injection.

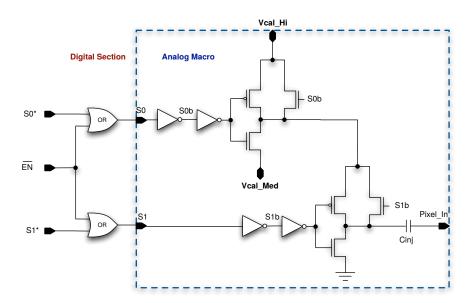

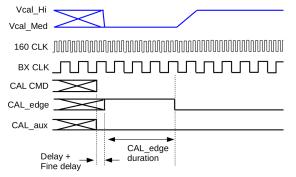

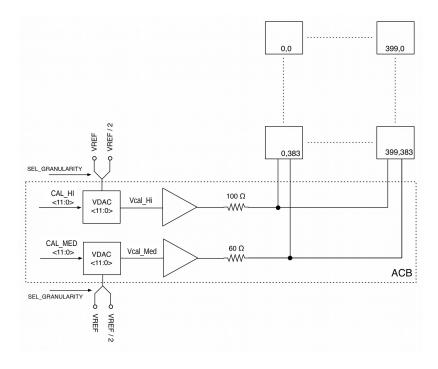

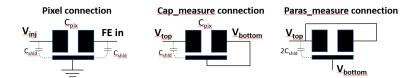

The calibration injection circuit uses two distributed DC voltages plus in-pixel switches to chop them and generate steps fed to an injection capacitor. Having two voltages allows a precise differential voltage that will be independent of local ground drops in the chip, as well as two consecutive injections into the same pixel. The injection circuit is implemented in every pixel and its topology is shown in Fig. 32. The control signals, S0 and S1, are generated in the digital domain as explained in Sec. 6.1. They can be phase shifted relative to the bunch crossing clock with a fine delay, which is global for the whole chip. The enable bit (EN) is programmable for each pixel and injection takes place only for enabled pixels. Charge is injected when either S0 or S1 switch from low to high. Analog injection must therefore be primed by setting at least one control signal low, prior to being able to inject. This priming is not automatic, so that the user is able to control the amount of settling time allowed prior to injection. The CAL command is used for both functions: prime and inject (see Sec. 6.2). The value of the injection capacitor can deviate from nominal due to process variations, so a dedicated circuit is provided to measure a replica capacitor array in each chip during wafer probing (Sec 13.8).

**Figure 32:** Calibration injection circuit in each pixel. The injection capacitor nominal value is 8.02 fF.

The injection circuit resembles two CMOS inverters, and just as in a common inverter, there will be a switching transient when a control signal switches from low to high, but simulations show these transients to have a negligible impact on the distributed Vcal\_Hi and Vcal\_Med voltages. Note that at the top of each inverter the injection circuit adds an NMOS transistor in parallel with the PMOS, which switches first (before the PMOS) when injecting. This allows the switches to operate for any choice of voltages Vcal\_Hi>Vcal\_Med>GND, but since the top NMOS switches first, it does not contribute transients during injection. During priming, on the other hand, the top NMOS switches first, while the bottom NMOS is still conducting, resulting in a short circuit lasting one inverter delay. This will cause a transient on the Vcal\_Hi and Vcal\_Med voltages, and the user must therefore allow some settling time between priming and injection. In addition to this transient, priming injects a positive polarity pulse into each enabled front end, so one must allow for the front end to settle in any case. The use of two voltages means that the charge injected by S0 is given by a differential voltage and not affected by local ground potential differences. Keeping S1=0 and only toggling S0 will result in single pulse differential injection. Conversely, the twovoltage injection circuit also allows injection of two successive pulses without priming in between, and with arbitrary delay between these pulses (one pulse differential and another referenced to ground). An additional control feature exploits the use of two voltages to inject a different amount of charge simultaneously in neighboring pixels, by changing the meaning of S0 and S1 in different pixels (see Sec. 6.1).

Finally, since the voltage distribution lines have finite impedance, injecting into too many pixels simultaneously will cause the voltages to droop, introducing a nonlinearity in the injected charge vs. number of pixels injected. Simulations show this nonlinearity to be less than 1% for simultaneous injection into 3 full rows of pixels and less than 2% for 4 rows, but the exact value of this nonlinearity should be measured in actual chips by measuring threshold vs. number (and pattern) of injected pixels.

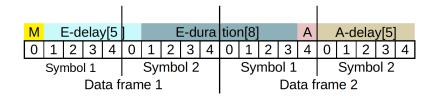

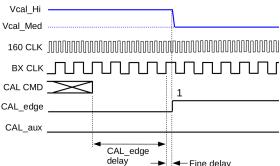

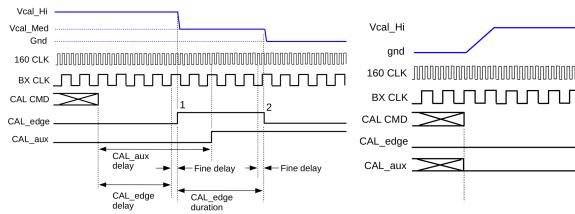

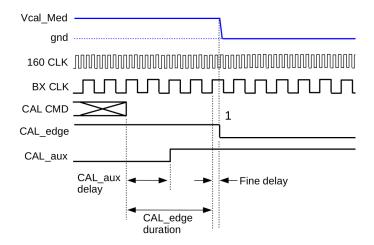

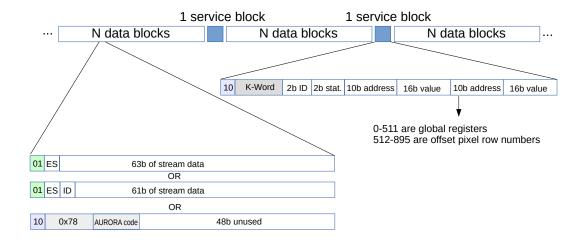

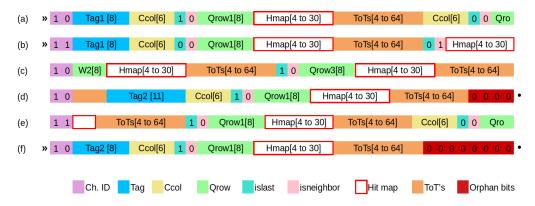

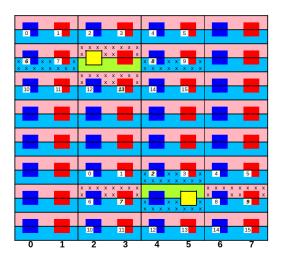

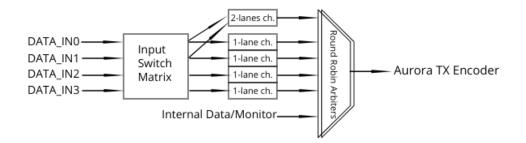

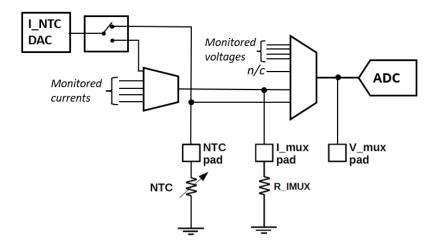

# 6.1 Generation of S0 and S1 signals