## Analysis of MOS capacitor with p-layer with TCAD simulation

Y. Unno<sup>c.\*</sup>, E. Bach<sup>b</sup>, J. Dandoy<sup>a</sup>, V. Fadeyev<sup>d</sup>, C. Fleta<sup>b</sup>, C. Jessiman<sup>a</sup>, J. Keller<sup>a</sup>, C.T. Klein<sup>a</sup>, T.Koffas<sup>a</sup>, E. Staats<sup>a</sup>, and M. Ullan<sup>b</sup>

<sup>a</sup>Physics Department, Carleton University, 1125 Colonel By Drive, Ottawa, Ontario, K1S 5B6, Canada

<sup>b</sup>Instituto de Microelectronica de Barcelona (IMB-CNM), CSIC, Campus UAB-Bellaterra, 08193 Barcelona, Spain

<sup>c</sup>Institute of Particle and Nuclear Study, High Energy Accelerator Research Organization (KEK), 1-1 Oho, Tsukuba, Ibaraki 305-0801, Japan

<sup>d</sup>Santa Cruz Institute for Particle Physics (SCIPP), University of California, Santa Cruz, CA 95064, USA

\*Corresponding author (e-mail: yoshinobu.unno@kek.jp).

Abstract - The ATLAS18 strip sensors of the ATLAS inner tracker upgrade (ITk) are under production since 2021. Along with the large-format n\*-in-p strip sensor in the center of the wafer, test structures are laid out in the open space for monitoring the performance of the strip sensor and its fabrication process. One of the structures is a 1.2×1.0 mm² test chip that includes representative structures of the strips, and Metal-Oxide-Silicon (MOS) capacitors. In addition to the standard MOS capacitor, a MOS capacitor with a p-layer in the surface of silicon, the MOS-p capacitor, is designed with a p-density representative of the p-stop doping for isolating the n' strips. The C-V curve of the MOS capacitor shows characteristic behavior in the accumulation depletion, and inversion regions as a function of bias voltage. behavior in the accumulation, depletion, and inversion regions as a function of bias voltage, from which one can estimate the amount of the interface charge. The MOS-p capacitor shows the C-V curve modulated by the properties of the p-layer.

shows the C-V curve modulated by the properties of the p-layer. With over 50% of the full production complement delivered, we have observed consistent characteristics in the MOS-p capacitors. Rarely and currently only in 3 batches, we have observed abnormalities. To further study them, we have simulated the MOS-p capacitor with TCAD software, which successfully reproduces the normal behavior, including a feature caused by a geometrical setback of the p-layer to the metal area, with the p-density and the interface charge within the expected range. By contrast, the overall shapes of the abnormal cases are only reproduced with 1/10 of the p-density to the specification and possible charge traps in the p-layer area. A smaller but distinctive feature in the behavior may require a non-uniform distribution of the p-density and the interface charge or something else. These simulations help to take final decisions for the batches in production.

**Introduction** – We are producing 20800 strip sensors for the upgrade ATLAS inner tracker (ITk), in 8 different shapes (2 in the barrel and 6 in the endcap sections) [1]. The strip sensors are made of n readout strips in the p-type silicon bulk, with p-stop isolation structure between the n strips. In the wafer layout (Fig. 1), we have implemented two Metal-Oxide-Silicon (MOS) capacitors in the Quality Assurance (QA) chips, for evaluating the interface charge and the density of the p-stop implantation (Fig. 2), (1) the standard capacitor (MOS) and (2) a special MOS capacitor with p-layer in the surface of the silicon bulk with the density of p-stop isolation (MOS-p) (Fig. 3).

Fig. 1 Wafer layout of barrel sensor, Short-strip type (SS) QA chips are groups of test structures (encircled in blue), diced out in orange into Testchip&MD8 and Mini&MD8, one set per wafer.

As of November 2023, we have received over 50% of the sensors, in 300 or more batches. We have observed abnormal behavior in the MOS-p capacitors in 3 batches: VPA37921, 42646, and 46225 [2]. Such abnormal behaviors are shown together with a normal case of VPA37914 et al (Fig. 4). We have tried to understand the source of such abnormalities with a technology CAD program (TCAD) [3].

**TCAD setup** – We have used a TCAD 3D device simulator, HyDeLEOS VER. 8.5k [3]. The MOS structure is implemented in 2D geometry (Fig. 3). Geometrical parameters are listed in Table 1. We have varied mainly the interface charge (shown with "x" in Fig. 3) and the density of p-layer, which surface density is *Qif* and *Ds*, respectively. We set the insulator thickness to a typical value obtained by the flatband voltage measurement of the standard MOS capacitor.

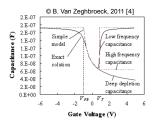

MOS capacitor (standard) – "Flatband voltage measurement" (capacitance measurement with an AC frequency as a function of DC bias voltage between the metal and the backplane) is to estimate the interface charge (Qif) and the thickness of the insulator (Fig. 5) [4].

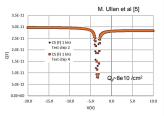

We have a typical measurement (Fig.6) [5], with which we estimate *Qif* being approximately 8e10 /

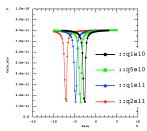

We have simulated the capacitance with Qif of 1e10, 5e10, 1e11, 2e11  $/\mathrm{cm}^2$  (Fig. 7). The simulation with 5e10 is consistent with the measurement.

Fig. 5 Typical behavior of the capacitance as a function of DC voltage. A certain negative voltage is required to compensate the attracted charge with the interface charge in the surface of silicon bulk (which voltage is called "Flatband voltage (V<sub>FM</sub>)); over the voltage the silicon surface gets depleted; further above a voltage, creation of e-/r pairs with the electric field cancels the depletion.

Fig. 6 Typical measurement of "Flatband voltage" with standard MOS capacitor [5].

Fig. 7 TCAD simulations of "Flatband voltage Qif of 1e10, 5e10, 1e11, 2e11 /cm<sup>2</sup>.

Device simulator simulates at thermal equilibrium, i.e. low frequency capacitance. Dynamic response of the charge in the inversion layer to AC voltage is not implemented in the program.

MOS capacitor with p-layer (I) – We have specified the surface density of p-stop structure to be approximately 4e12 cm² [1]. Under an interface charge Qff of 1e11 cm², we have simulated the behavior, with the p-layer density Ds of 2e12, 4e11, 2e11 cm² (Fig.8). The triangular behavior with 2e12 is consistent with that of the normal batch of VPA37914 (in Fig. 4).

A lower density moves the location of dip towards correct location, however, an order lower density *Ds* of 2e11 cm² is not enough to be consistent with the abnormal one. Lowering the density further does not help; the location of the dip tends to saturate. An increase of the interface charge *Qif* to 3e11 cm<sup>2</sup> moves the location further lower voltage to be consistent with the abnormal ones.

With these values of the p-density and the interface charge, the shape of the simulations are too sharp.

MOS capacitor with p-layer (II) – "Traps in p-layer" - the p implantation creates charge traps as radiation damage remnants, which are "annealed" away with temperature treatment in the fabrication process. The traps can be negatively (p-type) or positively (n-type) charged-up sites after absorbing/releasing electrons or holes.

We have introduced charge traps in the p-layer area. Only positive traps (n-type) have affected the behavior. With the introduction, the dips are flattened in the abnormal behavior (red circles). Even in the normal one, the charge traps introduce a kink (red circle) which we observe in the VPA37914 (in Fig. 4). We set the density of the traps not to deviate too much in the normal one.

We have to tune the p density Ds a bit, but the relative locations of the dips of normal and abnormal stay the same (Fig.9).

Fig. 8 TCAD simulations of "Flatband voltage measurement" with Ds of 2e12, 4e11, 2e11 /cm² (under Qif of 1e11 /cm²). An extra is Ds of 2e11 (under Qif of 3e11 /cm²)

Fig. 9 TCAD simulations of "Flatband voltage measurement" with *Ds* of 6e12 and 6e11 /cm², under *Qif* of 1e11 /cm² and n-type charge traps in the p-layer region, together with the introduction of "setback" of p-layer to the metal

**MOS** capacitor with p-layer (III) – We have observed a tiny dip at around -3 V in the normal behavior in Fig. 4. With simulation, this dip (Fig. 8, encircled in blue) is identified being caused by the "setback" of the p-layer to the metal area in reality.

We understand the two factors from the simulation: one is affecting the location and the other the depth of the dip. The former is the p density of the "setback" area, and the latter the wideness of the "setback". We set a smearing of p from the p-layer area with a sigma of 1 µm, otherwise the p density of the "setback" area is that of the silicon bulk. The "setback" is 4.5 µm in layout which results in the ratio of p-layer to metal area being 0.976. A bit smaller ratio of 0.97, which corresponds the setback of 5.5 um, reproduces the depth of the dip better the depth of the dip better.

MOS capacitor with p-layer (IV) – The introduction of charge traps in the p-layer is not enough to reproduce the "width" of the dip in the abnormal behaviors. For in case, we have introduced a surface contamination with n-type impurity, with the surface density of Null (black), 6e10 (green), 8e10 (blue), and 1e11 (red) cm² (Fig.10). The location of the dips has moved. The bottom of the dips seems to be flatter, but the widths are stayed

We also observe that the introduction of n-type surface contamination induces very similar effect as the interface charge, as expected.

Fig. 10 TCAD simulations of "Flatband voltage measurement" with n-type surface contamination, under *Ds* of 6e11 /cm², and n-type charge traps in the p-layer region.

**Discussion** – TCAD simulations show that the abnormal behaviors can be reproduced in general with low p-density and charge traps in the p-layer, and interface charge and/ or extra surface contamination with n-type impurity. One of the abnormal case with a rather wide width of the dip, however, still requires further investigation. We have understood that the location and the shape of the dip are affected by the

We have understood that the location and the shape of the dip are affected by the charge in the interface (either interface charge or n-type surface contamination, or both) and p-density. There could be local variation of these factors while we have applied the factors uniformly over the relevant area in the previous sections. We have already tried the possibility but have not reached a reasonable conclusion yet.

The results that we have already obtained imply that there could be issues in the fabrication process such as p-implantation, etching, insulator deposition, heat treatment, and even very local non-uniformity, which are being communicated with the vendor.

Conclusion – We have understood the general behavior of the MOS capacitors, with or without p-layer in the surface of silicon (MOS or MOS-p, respectively) with TCAD simulations. The rare but abnormal behavior of the MOS-p capacitor has been understood with a low p-density (1/10 or less of the specification) and potentially other factors such as interface charge, insufficient heat treatment, and else. The results have helped to make a final decision on the relevant batches with confidence.

## Acknowledgements

We gratefully acknowledge HPK for their close communication and collaboration. This work was supported in part by the Canada Foundation for Innovation and the Natural Science and Engineering Research Council of Canada, as well as the Alexander von Humboldt Foundation, the Spanish R&D grant PID2021-1263270B-C22, funded by MCIN/AEI/10.13039/501100011033 / FEDER, UE, and the US Department of Energy, grant DE-

References

[1] Y. Unno et al., "Specifications and pre-production of n^+-in-p large-format strip sensors fabricated in 6-inch silicon wafers, ATLAS18, for the Inner Tracker of the ATLAS Detector for High-Luminosity Large Hadron Collider", 2023 JINST 18 T03008

[2] E. Bach-Marques et al, "Analysis of the quality assurance results from the initial part of production of the ATLAS18 ITK strip sensors"; P. Miyagawa et al, "Analysis of the results from Quality Control tests performed on ATLAS18 Strip Sensors during on-going production", in this conference

[3] Keio University, TCAD R&D Center (TRDEC), "HyDeLEOS Ver. 8.5k User's manual", 2019

2019

[4] B. Van Zeghbroeck, "Principles of Semiconductor Devices", University of Colorado, http://ece-www.colorado.edu/~bart/book/ [2/28/2002 5:26:10 PM]

[5] M. Ullan et al., "Quality Assurance methodology for the ATLAS Inner Tracker strip sensor production", Nuclear Inst. and Methods in Physics Research, A 981 (2020) 164521, https://doi.org/10.1016/j.nima.2020.164521