# PAPER • OPEN ACCESS

# The New Small Wheel electronics

To cite this article: G. lakovidis et al 2023 JINST 18 P05012

View the article online for updates and enhancements.

# You may also like

- Electronics performance of the ATLAS New Small Wheel Micromegas wedges at <u>CERN</u> P. Tzanis

- <u>Trigger algorithms and electronics for the</u> <u>ATLAS muon new small wheel upgrade</u> L. Guan

- The Detector Control System of the New Small Wheel for the ATLAS experiment Polyneikis Tzanis

inst

Received: *March 23, 2023* Accepted: *April 11, 2023* Published: *May 11, 2023*

# The New Small Wheel electronics

G. lakovidis,<sup>a,\*</sup> L. Levinson,<sup>b,\*</sup> Y. Afik,<sup>t,7</sup> C. Alexa,<sup>f</sup> T. Alexopoulos,<sup>d</sup> J. Ameel,<sup>p</sup> D. Amidei,<sup>p</sup>

**D.** Antrim, v, 1 A. Badea, j C. Bakalis, a, d, 2 H. Boterenbrood, q R.S. Brener, t, 3 S. Chan, j, 4

J. Chapman, $^p$  G. Chatzianastasiou, $^g$  H. Chen, $^a$  M.C. Chu, $^l$  R.M. Coliban, $^e$  T. Costa de Paiva, $^o$

G. de Geronimo,<sup>*a*,5</sup> R. Edgar,<sup>*p*,6</sup> N. Felt,<sup>*j*</sup> S. Francescato,<sup>*j*</sup> M. Franklin,<sup>*j*</sup> T. Geralis,<sup>*h*</sup>

K. Gigliotti,<sup>c</sup> P. Giromini,<sup>j</sup> P. Gkountoumis,<sup>*a,d,p,7*</sup> I. Grayzman,<sup>*b,8*</sup> L. Guan,<sup>*p*</sup>

J. Guimaraes da Costa,  $j^{j,9}$  L. Han, <sup>k</sup> S. Hou, <sup>s</sup> X. Hu, <sup>p</sup> K. Hu, <sup>k,10</sup> J. Huth, <sup>j</sup> M. Ivanovici, <sup>e</sup>

G. Jin,<sup>k</sup> K. Johns,<sup>c</sup> E. Kajomovitz,<sup>t</sup> G. Kehris,<sup>j</sup> I. Kiskiras,<sup>h</sup> A. Koulouris,<sup>a,d,7</sup> E. Kyriakis,<sup>w</sup>

A. Lankford, <sup>v</sup> L. Lee, j,11 H. Leung, <sup>l</sup> F. Li, <sup>k</sup> Y. Liang, <sup>p</sup> H. Lu, <sup>k</sup> N. Lupu, <sup>t</sup> V. Martinez, <sup>o</sup>

S. Martoiu,<sup>f</sup> D. Matakias,<sup>a,d</sup> I. Mehalev,<sup>t</sup> I. Mesolongitis,<sup>a,w</sup> P. Miao,<sup>k</sup> G. Mikenberg,<sup>b</sup>

L. Moleri,<sup>t,3</sup> P. Moschovakos,<sup>a,d,7</sup> J. Narevicius,<sup>b,12</sup> J. Oliver,<sup>j</sup> D. Pietreanu,<sup>f</sup>

R. Pinkham,<sup>*p*,13</sup> E. Politis,<sup>*w*</sup> V. Polychronakos,<sup>*a*</sup> S. Popa,<sup>*e*</sup> M.M. Prapa,<sup>*h*</sup> I. Ravinovich,<sup>*b*</sup>

A. Roich,<sup>b</sup> R.A. Rojas Caballero,<sup>r,u,14</sup> Y. Rozen,<sup>t</sup> M. Schernau,<sup>v</sup> T. Schwartz,<sup>p</sup> G. Scott,<sup>c</sup>

O. Shaked,<sup>b,15</sup> M. Solis,<sup>c</sup> S. Sun,<sup>p,16</sup> A. Taffard,<sup>v</sup> S. Tang,<sup>a</sup> Z. Tarem,<sup>t</sup> W. Tse,<sup>l</sup> Y. Tu,<sup>m</sup>

A. Tuna, j,g P. Tzanis, a,d,7 S. Tzanos, a,d R. Vari, M. Vasile, A. Vdovin, J. Vermeulen, q

J. Wang,  $p^{,17}$  X. Wang,  $p^{,p}$  A. Wang,  $j^{,j}$  R. Wang,  $j^{,j}$  X. Xiao,  $p^{,p}$  L. Yao,  $a^{,18}$  C. Yildiz,  $v^{,19}$

K. Zachariadou,<sup>w</sup> B. Zhou,<sup>p</sup> J. Zhu,<sup>p</sup> S.U. Zimmermann<sup> $i,\dagger$ </sup> and O. Zormpa<sup>h,g</sup>

<sup>a</sup>Physics Department, Brookhaven National Laboratory, Upton NY, U.S.A.

<sup>3</sup>Now at Weizmann Institute of Science, Rehovot, Israel.

<sup>6</sup>Now at ArborMetrix, Ann Arbor, MI, U.S.A.

9Now at Institute of High Energy Physics, Chinese Academy of Sciences, Beijing, China.

<sup>13</sup>Now at Meta, CA, U.S.A.

- <sup>15</sup>Now at Orbotech, Yavne, Israel.

- <sup>16</sup>Now at Investivity, Geneva, Switzerland.

<sup>19</sup>Now at Ecole Polytechnique Federale de Lausanne, Lausanne, Switzerland.

© 2023 CERN. Published by IOP Publishing Ltd on behalf of Sissa Medialab. Original content from this work may be used under the terms of the Creative Commons Attribution 4.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

<sup>&</sup>lt;sup>1</sup>Now at Google, CA, U.S.A.

<sup>&</sup>lt;sup>2</sup>Now at SLAC National Accelerator Laboratory, Stanford CA, U.S.A.

<sup>&</sup>lt;sup>4</sup>Now at Keystone Strategy, NY 10012, U.S.A.

<sup>&</sup>lt;sup>5</sup>Now at DG Circuits, Syosset, NY 11791, U.S.A.

<sup>&</sup>lt;sup>7</sup>Now at CERN, Geneva, Switzerland.

<sup>&</sup>lt;sup>8</sup>Now at Beit Hakerem School, Jerusalem, Israel.

<sup>&</sup>lt;sup>10</sup>Now at Shandong University, Jinan, China.

<sup>&</sup>lt;sup>11</sup>Now at University of Tennessee, Knoxville, U.S.A.

<sup>&</sup>lt;sup>12</sup>Now at Department of Physics, Technische Universität, Dortmund, Germany.

<sup>&</sup>lt;sup>14</sup>Now at University of Massachusetts, Amherst MA, U.S.A.

<sup>&</sup>lt;sup>17</sup>Now at University of Science and Technology of China, Hefei, China.

<sup>&</sup>lt;sup>18</sup>Now at Institute for Interdisciplinary Information Sciences, Tsinghua University, Beijing, China.

<sup>&</sup>lt;sup>†</sup>Deceased.

<sup>\*</sup>Corresponding author.

- <sup>b</sup>Department of Particle Physics and Astrophysics, Weizmann Institute of Science, Rehovot, Israel

- <sup>c</sup>Department of Physics, University of Arizona, Tucson AZ, U.S.A.

- <sup>d</sup>Physics Department, National Technical University of Athens, Zografou, Greece

- <sup>e</sup>Electronics and Computers Department, Transilvania University of Brasov, Brasov, Romania

- <sup>f</sup> Department of Elementary Particles Physics, Horia Hulubei National Institute of Physics and Nuclear Engineering, Bucharest, Romania

- <sup>g</sup>CERN, Geneva, Switzerland

- <sup>h</sup>National Centre for Scientific Research "Demokritos", Agia Paraskevi, Greece

- <sup>i</sup>Physikalisches Institut, Albert-Ludwigs-Universität Freiburg, Freiburg, Germany

- <sup>j</sup>Laboratory for Particle Physics and Cosmology, Harvard University, Cambridge MA, U.S.A.

- <sup>k</sup>Department of Modern Physics and State Key Laboratory of Particle Detection and Electronics,

- University of Science and Technology of China, Hefei, China

- <sup>1</sup>Department of Physics, Chinese University of Hong Kong, Shatin, N.T., Hong Kong, China

- <sup>m</sup>Department of Physics, University of Hong Kong, Hong Kong, China

- <sup>n</sup>Dipartimento di Fisica, Sapienza Università di Roma, INFN Sezione di Roma, Roma, Italy

- <sup>o</sup>Department of Physics, University of Massachusetts, Amherst MA, U.S.A.

- <sup>p</sup>Department of Physics, University of Michigan, Ann Arbor MI, U.S.A.

- <sup>q</sup>Nikhef National Institute for Subatomic Physics and University of Amsterdam, Amsterdam, Netherlands

- <sup>r</sup> Departamento de Física, Universidad Técnica Federico Santa María, Valparaíso, Chile

- <sup>s</sup>Institute of Physics, Academia Sinica, Taipei, Taiwan

- <sup>t</sup>Department of Physics, Technion, Israel Institute of Technology, Haifa, Israel

- <sup>u</sup>Department of Physics and Astronomy, University of Victoria, Victoria, Canada

- <sup>v</sup> Department of Physics and Astronomy, University of California Irvine, Irvine CA, U.S.A.

- <sup>w</sup> Department of Electrical and Electronics Engineering, University of West Attica, Egaleo, Athens

*E-mail:* giakovidis@bnl.gov, lorne.levinson@weizmann.ac.il

ABSTRACT: The increase in luminosity, and consequent higher backgrounds, of the LHC upgrades require improved rejection of fake tracks in the forward region of the ATLAS Muon Spectrometer. The New Small Wheel upgrade of the Muon Spectrometer aims to reduce the large background of fake triggers from track segments that don't originate from the interaction point. The New Small Wheel employs two detector technologies, the resistive strip Micromegas detectors and the "small" Thin Gap Chambers, with a total of 2.45 million electrodes to be sensed. The two technologies require the design of a complex electronics system given that it consists of two different detector technologies and is required to provide both precision readout and a fast trigger. It will operate in a high background radiation region up to about 20 kHz/cm<sup>2</sup> at the expected HL-LHC luminosity of  $\mathcal{L} = 7.5 \times 10^{34} \,\mathrm{cm}^{-2} \,\mathrm{s}^{-1}$ . The architecture of the system is strongly defined by the GBTx data aggregation ASIC, the newly-introduced FELIX data router and the software based data handler of the ATLAS detector. The electronics complex of this new detector was designed and developed in the last ten years and consists of multiple radiation tolerant Application Specific Integrated Circuits, multiple front-end boards, dense boards with FPGA's and purpose-built Trigger Processor boards within the ATCA standard. The New Small Wheel has been installed in 2021 and is undergoing integration within ATLAS for LHC Run 3. It should operate through the end of Run 4 (December 2032). In this manuscript, the overall design of the New Small Wheel electronics is presented.

KEYWORDS: Data acquisition concepts; Electronic detector readout concepts (gas, liquid); Front-end electronics for detector readout; Trigger concepts and systems (hardware and software)

ArXiv ePrint: 2303.12571

In memory of Dr. Stephanie Ulrike Zimmermann (1973–2020).

# Contents

| 1 Introduction |            |                                                                        |    |  |

|----------------|------------|------------------------------------------------------------------------|----|--|

|                | 1.1        | Radiation and magnetic field tolerance                                 | 3  |  |

| 2              | Ove        | rall architecture of the electronics                                   | 4  |  |

|                | 2.1        | The GBTx ASIC and FELIX                                                | 4  |  |

|                | 2.2        | Synchronization, trigger, reset, test pulse signals and LHC clock path | 5  |  |

|                | 2.3        | Digitized detector data path                                           | 6  |  |

|                | 2.4        | Configuration, command and status path                                 | 6  |  |

|                | 2.5        | Busy path                                                              | 6  |  |

|                | 2.6        | Trigger data path                                                      | 7  |  |

| 3              | FELIX      |                                                                        |    |  |

|                | 3.1        | Geographic names                                                       | 9  |  |

| 4              | Trig       | ger processor                                                          | 10 |  |

|                | 4.1        | Hardware                                                               | 10 |  |

|                | 4.2        | FPGA firmware                                                          | 12 |  |

|                |            | 4.2.1 Micromegas specific trigger processing                           | 12 |  |

|                |            | 4.2.2 sTGC specific trigger processing                                 | 14 |  |

|                |            | 4.2.3 Segment merging and duplicate removal                            | 16 |  |

|                |            | 4.2.4 Ancillary functions                                              | 16 |  |

|                | 4.3        | Bunch crossing synchronization of the trigger paths                    | 18 |  |

| 5              | CERN ASICs |                                                                        |    |  |

|                | 5.1        | GBTx — GigaBit Transceiver                                             | 18 |  |

|                | 5.2        | SCA — Slow Control Adapter                                             | 19 |  |

|                | 5.3        | FEAST — DC-to-DC converter                                             | 19 |  |

|                | 5.4        | VTRx, VTTx — optical interfaces                                        | 19 |  |

| 6              | NSV        | W ASICs                                                                | 19 |  |

|                | 6.1        | VMM — Mixed-signal front-end ASIC                                      | 19 |  |

|                |            | 6.1.1 Requirements                                                     | 20 |  |

|                |            | 6.1.2 Architecture                                                     | 21 |  |

|                |            | 6.1.3 Readout schema                                                   | 23 |  |

|                |            | 6.1.4 Trigger outputs                                                  | 23 |  |

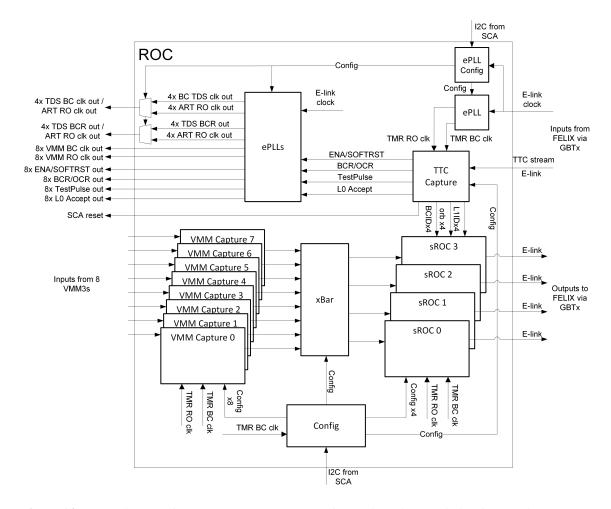

|                | 6.2        | ROC — Read out Controller ASIC                                         | 24 |  |

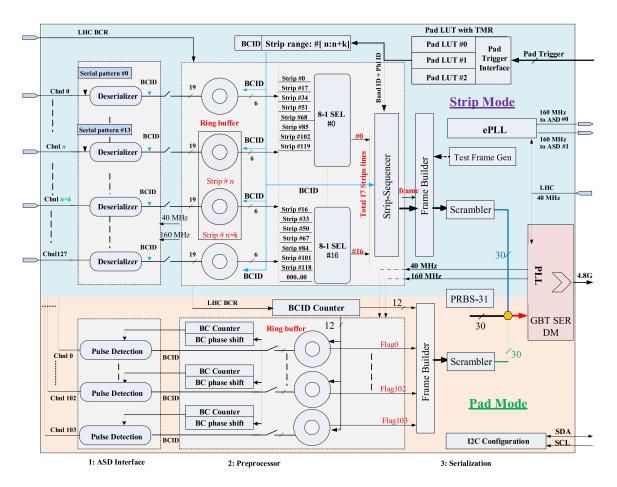

|                | 6.3        | TDS — sTGC Trigger Data Serializer ASIC                                | 26 |  |

|                |            | 6.3.1 Pad TDS mode                                                     | 26 |  |

|                |            | 6.3.2 Strip TDS mode                                                   | 28 |  |

|                |            | 6.3.3 Test functions                                                   | 28 |  |

|    |       | 6.3.4 The 4.8 Gb/s serializer                                    | 28 |

|----|-------|------------------------------------------------------------------|----|

|    |       | 6.3.5 Radiation tolerance                                        | 29 |

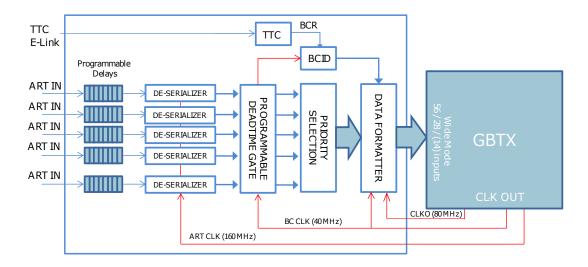

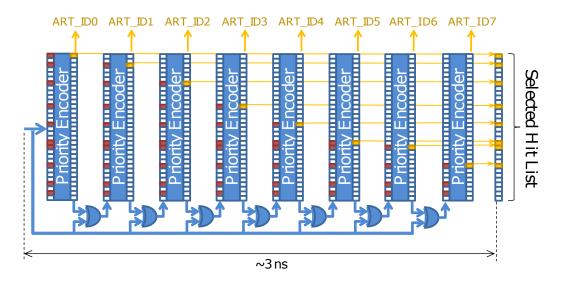

|    | 6.4   | ART — Micromegas trigger data aggregator and serializer ASIC     | 29 |

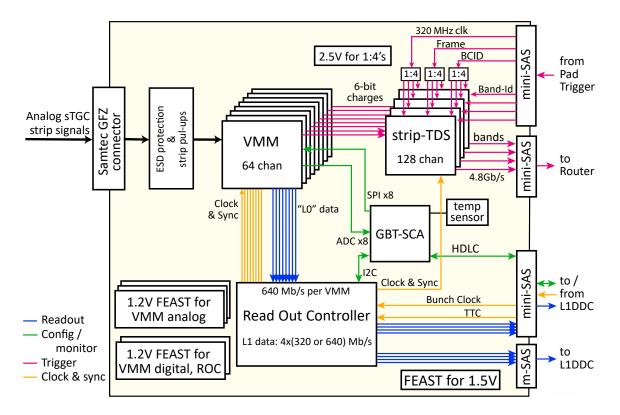

| 7  | NSV   | V boards                                                         | 32 |

|    | 7.1   | Micromegas Front-end board — MMFE8                               | 32 |

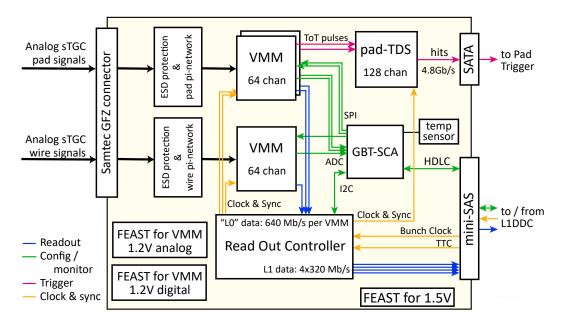

|    | 7.2   | sTGC Front-end boards — sFEB and pFEB                            | 34 |

|    | 7.3   | Aggregation of several electrical links to optical links — L1DDC | 37 |

|    | 7.4   | Micromegas trigger data serializer — ADDC                        | 39 |

|    | 7.5   | sTGC Pad Trigger                                                 | 40 |

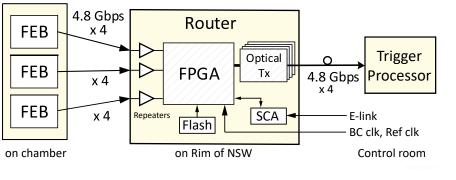

|    | 7.6   | sTGC Router                                                      | 42 |

|    | 7.7   | Twin-ax serial and LVDS repeaters                                | 44 |

|    | 7.8   | Direct low jitter FPGA transceiver reference clock               | 45 |

|    | 7.9   | Board and ASIC counts                                            | 45 |

| 8  | Opti  | cal fibre interconnects                                          | 46 |

| 9  | Trig  | ger latency                                                      | 47 |

| 10 | Con   | figuration                                                       | 47 |

| 11 | Cali  | bration                                                          | 48 |

|    | 11.1  | Phase alignments                                                 | 48 |

|    | 11.2  | SCA-ADC based calibration                                        | 49 |

|    | 11.3  | Data-driven calibration                                          | 50 |

|    | 11.4  | Configurable delays                                              | 51 |

| 12 | Pow   | er distribution and grounding                                    | 51 |

|    | 12.1  | Power                                                            | 51 |

|    | 12.2  | Grounding                                                        | 51 |

| Gl | ossar | y                                                                | 52 |

# 18 P05012

2023 JINST

# 1 Introduction

The New Small Wheel (NSW) [1] is an upgrade of the innermost forward station of the Muon Spectrometer at the ATLAS experiment [2] at CERN. The High Luminosity LHC (HL-LHC) will provide substantially increased luminosity; therefore, higher background rates are expected. The upgrades to ATLAS for HL-LHC are done in two phases: Phase 1 for Run 3, which began in mid-2022 and Phase 2 for Run 4, which is expected to begin in mid-2029. The initial configuration of the Small Wheels of the Muon Spectrometer does not allow the rejection of the fake triggers from the increased background, and moreover, efficiency loss is expected at high particle rate. The New

Small Wheel will reduce the significant background of fake triggers from track segments that do not originate from the interaction point by providing a track segment to the ATLAS Level 1 trigger logic to match with hit coincidences in the Big Wheel [3]. Also, it will cope with a ten-fold increase in the ATLAS Level-1 trigger rate. It was installed in the ATLAS cavern in 2021 and is undergoing commissioning. Operating in a high background radiation region (up to about 20 kHz/cm<sup>2</sup> at the expected HL-LHC luminosity of  $\mathcal{L} = 7.5 \times 10^{34} \text{ cm}^{-2} \text{ s}^{-1}$ ), it reconstructs muon tracks with high precision and furnishes pointing track segments to the ATLAS Level-1 trigger. In this manuscript, the overall design of the New Small Wheel electronics is presented.

The NSW employs two gaseous detector technologies: sTGC [4] and Micromegas [5]. The sTGC provides bunch crossing assignment with high radial resolution from strips and rough  $\phi$  resolution from pads; the Micromegas strips provide even better radial resolution, and a good  $\phi$  coordinate due to its stereo strips layout. Both technologies are used for triggering and for track reconstruction. For triggering, the sTGC is expected to provide better timing resolution than Micromegas and a higher angular resolution due to its greater separation between its first four and last four layers. This performance is still to be demonstrated during Run 3 operation of the NSW.

The NSW envelope is a disk, ~ 10 m in diameter and ~ 1 m thick. It lies between the Endcap Liquid Argon Calorimeter and the Endcap Toroid, centred at z = 7.3 m. Each NSW comprises 16 sectors, 8 small and 8 large alternating each other. Each sector consists of eight layers of each detector technology, arranged along the beam axis as follows: a 4-layer sTGC wedge, two 4-layer Micromegas wedges on either side of a support structure and another 4-layer sTGC wedge. There are ~ 2.1 million Micromegas strips (4 of the 8 layers have stereo strip layout) ~ 282 k sTGC strip, ~ 47 k sTGC pad and ~ 24 k sTGC wire analog readouts for a total of ~ 2.45 million channels. The NSW electronics follows the NSW detector organization in a hierarchy from endcaps, sectors, layers, and finally, radial position. A large and a small sector cover one octant. The sectors overlap slightly, but are independent, with no communication between them.

The NSW performance criteria are demanding. In particular, the precision reconstruction of track segments for the offline analysis requires a spatial resolution of ~ 100  $\mu$ m per layer to provide good momentum resolution along the radial direction, over a 4 m active radius surface. The track segments for the Level-1 trigger must be reconstructed online with a polar angular resolution of approximately 1 mrad, in order to match the 1 mrad angular resolution of the middle and outer muon stations planned for the Phase 2 upgrade for the HL-LHC. The trigger requires that for a valid NSW segment, the angle between it and the infinite momentum track from the interaction point be less than ±15 mrad. (The angle is configurable up to ±15 mrad in steps of 1 mrad.) In Phase 1, NSW segments found at every bunch crossing are extrapolated to match the *hit* coincidences in the muon stations downstream from the endcap toroid magnet. In Phase 2, they are used with *segments* in the downstream muon stations to measure a track's transverse momentum, *p*<sub>T</sub>, for the trigger algorithm.

Constraints strongly affecting the design of the electronics include:

- Sophisticated Front-end readout is required for 2.45 million analog channels with differing signal characteristics.

- Tightly limited latency for the Phase 1 trigger path of  $\sim 1.1 \,\mu s$  including  $\sim 500 \,ns$  of time-of-flight, fibre and cable propagation

- Radiation at the inner radius (ten-year total dose of 350 kRad, simulated, with safety factors, requires radiation and Single Event Upset tolerant ASICs and testing of any commodity electronics used). FPGAs can be used only on the rim of the wheel and only if they use SEU mitigation techniques.

- Magnetic fields up to 5 kG strongly limit the use of non-air-core inductors in filters and DC-DC converters.

- Limited space implies dense circuit boards, active cooling.

- Limited access after installation requires redundancy.

- Since the on-detector electronics cannot be replaced for Phase 2, the Phase 2 requirements must be met with Phase 1 technology.

- The decision between a single level and a two-level hardware trigger could not be made before freezing the NSW ASIC requirements, thus requiring the readout ASIC to support both.

- Need to support two detector technologies with as many shared elements as possible.

- Need for state-of-the-art gigabit serial transceivers and interconnections

- Need of on-board voltage conversion requires very careful design of the power distribution to maintain a high signal-to-noise ratio.

Actual clock frequencies. All the NSW clocks are inherited from the LHC bunch crossing clock, which is 40.079 MHz. However, for convenience in this document, the bunch crossing (BC) clock and its integer multiples are referred to as 40 MHz, 80 MHz, 160 MHz, etc. For example, the actual frequency of the 160 MHz clock is 160.316 MHz.

#### 1.1 Radiation and magnetic field tolerance

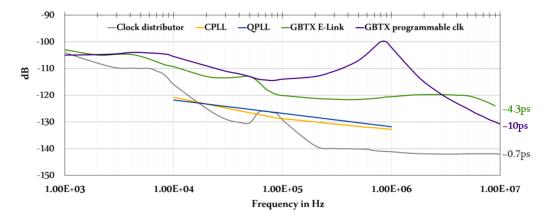

The radiation level diminishes as the radius increases; see table 1. It is high enough to force using ASICs on the detectors, but FPGAs are manageable, with Single Event Upset (SEU) mitigation, on the rim of the wheel. All on-detector components were tested to confirm that they withstand the expected Total Ionisation Dose (TID). All on-detector non-ASIC components are stateless, so their SEUs are not fatal. The modern jitter cleaners required by FPGA gigabit transceivers have both

**Table 1**. Simulated radiation loads and magnetic fields, from [9] for the NSW after 10 years at high luminosity LHC,  $\mathcal{L} = 5 \times 10^{34} \text{ cm}^{-2} \text{ s}^{-1}$ , for Total Ionization Dose (TID), Non-Ionizing Energy Loss (NIEL), Single Event Effect (SEE). Safety factors are not included. Adapted from [9]. CC BY 4.0.

|                      | Inner radius (R=1 m)                  | Outer Rim (R=5 m)                     |

|----------------------|---------------------------------------|---------------------------------------|

| TID $(\gamma)$       | 780 Gy                                | 26 Gy                                 |

| NIEL (fast neutrons) | $3.9 \times 10^{13}  n/\mathrm{cm}^2$ | $1.2 \times 10^{12}  n/\mathrm{cm}^2$ |

| SEE (protons)        | $6.7 \times 10^{12}  p/\mathrm{cm}^2$ | $2.2 \times 10^{11}  p/\text{cm}^2$   |

| B field              | $\leq 1  \mathrm{kG}$                 | max 5 kG                              |

analog and digital logic and, unfortunately, were found to have fatal Single Event Effects even in the radiation environment on the Rim. See [6-9].

The magnetic field, combined from the solenoid and endcap toroid, is neither uniform in radius, R, nor azimuth,  $\phi$ . Its highest value lies exactly on the Rim and the edges of the detectors where the electronic boards are located. Either air-core inductors, or inductors that could be shielded and oriented to minimize the effect of the magnetic field, were used [9].

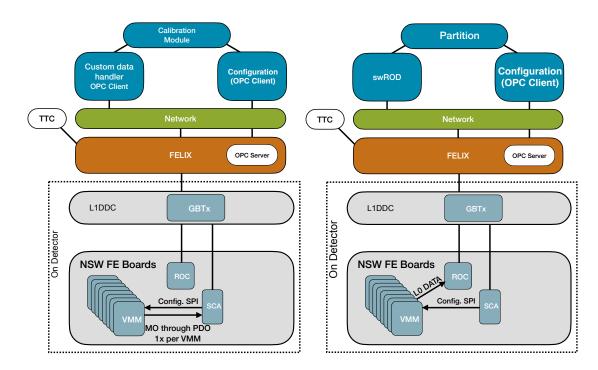

# **2** Overall architecture of the electronics

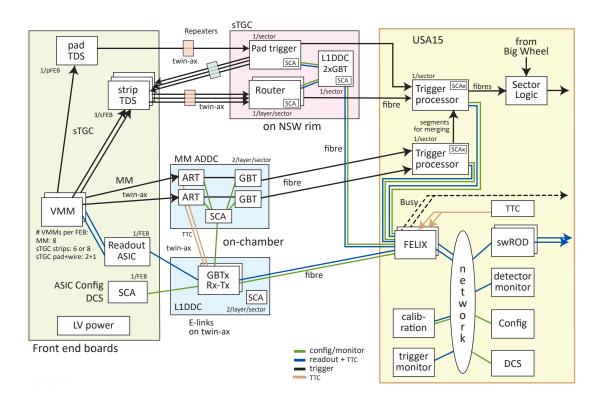

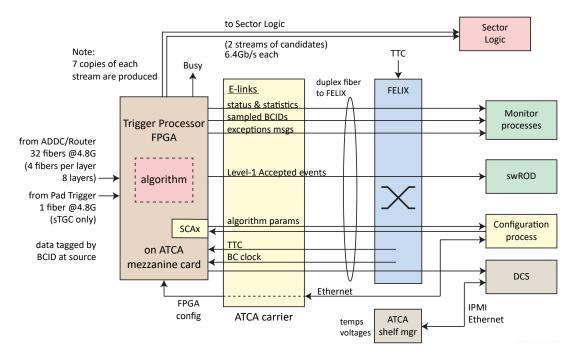

The overall architecture of the NSW electronics is shown in figure 1. There are five data and signal paths:

- Synchronization, trigger, test pulse and reset signals and the LHC bunch-crossing clock

- · Digitized readout data from the detector including monitoring and calibration data

- Configuration parameters and commands to the Front-ends and status indicators from the Front-ends

- Busy signal path

- Digitized data from the detector for the trigger path

These five paths are elaborated below.

#### 2.1 The GBTx ASIC and FELIX

The use of the radiation-hard GBTx ASIC [10, 11] to provide fibre connections between the collision cavern and the radiation-protected room, drastically impacts the architecture of the NSW electronics. The first three paths are time-multiplexed together on fibres to and from a GBTx ASIC which interfaces to separate electrical "E-links" on twin-ax cables (also known as MiniSAS cables) [12, 13] to electronics boards on the detector. These slow links carry Front-end readout, calibration and detector monitoring data from the Front-end, and configuration and control data to the Front-end. They are aggregated to the 4.8 Gb/s fibres by the GBTx ASICs on the Level-1 Data Driver Cards (L1DDC). See sections 5.1 and 7.3. In the Micromegas trigger path, the GBTx is used as a point-to-point 4.8 Gb/s link between the ADDC and the Trigger Processor. The data transported are not considered as E-links. See sections 5.1 and 7.4.

The fibres from the L1DDCs that carry the E-links connect to FELIX, the Front End Link eXchange (FELIX) [14–20]. The use of FELIX also strongly impacts the architecture of the NSW Electronics. FELIX routes E-links to and from endpoints on a standard Ethernet network. It replaces the previous ATLAS front-end readout architecture. FELIX is part of all but the trigger data paths. FELIX separates data transport from data processing: data are transported by FELIX, a detector-neutral custom hardware plus software device; data are processed or sent by detector-specific software; for example, readout data is processed by the swROD [21]. FELIX is described in more detail in section 3.

Following figure 1, the components and data flow for each of the five paths are summarized here, with details for all the components in sections 6 and 7.

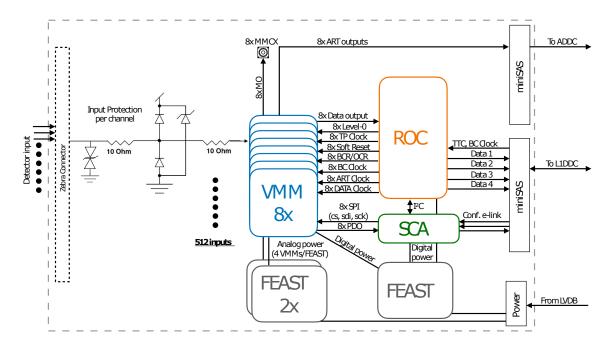

**Figure 1**. Overview of the NSW electronics. There are electronics boards on the detector, on the rim of the wheel and in the radiation-protected room (USA15). The objects shown connected to the network, except FELIX, may be computers or processes. The Sector Logic, FELIX and swROD are part of the ATLAS Trigger & DAQ project. The quantities of each board and ASIC is given in table 6.

# 2.2 Synchronization, trigger, reset, test pulse signals and LHC clock path

This path begins with the ALTI [22] Timing, Trigger & Control (TTC) module, which sends a serial stream containing the LHC Bunch Crossing (BC) clock and control signals via optical fan-outs and dedicated fibres to each FELIX FPGA. The control signals can be sent synchronously to the BC clock with a defined offset in BC's from the beginning of the LHC orbit. FELIX decodes the control signals, recovers and jitter-cleans the BC clock. The control signals, Level-1 Trigger Accept (L1A), Level-0 Trigger Accept (L0A), Event Counter Reset (ECR), Bunch Crossing Counter Reset (BCR), Test-Pulse (TP), Soft-Reset (SR), Orbit Count Reset (OCR) and the BC clock are sent to the Readout Controller (ROC), see section 6.2, on the Front-end boards, to the Rim boards and to the Micromegas trigger boards via the GBTx ASIC on the L1DDC boards. The BC clock is recovered by the GBTx ASIC and is sent to all ASICs in the system. The Trigger Processors receive the same signals via firmware [23, 24] that emulates the GBTx. The higher speed reference clocks of all serial links are multiples of the recovered BC clock. The Readout Controller on each Front-end board forwards the needed control signals and bunch crossing clock, with configurable delays, to the various ASICs on the board. This path has a fixed latency, reproducible across power cycles, from the Central Trigger Processor (CTP) to ALTI to the Front-end ASICs.

# 2.3 Digitized detector data path

The digitized detector data path begins with the 64-channel VMM Front-end ASIC, see 6.1, which senses the detector readout electrodes. Both Micromegas and sTGC strips as well as sTGC pad and wire signals are processed by digitizing their peak voltage after amplification and shaping. The time of the peak or threshold crossing (configurable) relative to the BC clock edge is also digitized. The digitized data is tagged by the VMM with the value, the "BCID", of a BC counter which remains attached to the data as it moves through the system. The charge and time information are buffered in the VMM until the L0A (Level-0 Accept) trigger signal is received and sent to the ROC. The data are held in the buffer until they become older than the BC window of interest. The ROC buffers the data until the L1A (Level-1 Accept) trigger signal is received.<sup>1</sup> The Read Out Controller aggregates up to eight VMMs and sends the data for those BCs selected by the L1A trigger to a GBTx ASIC on the L1DDC card via one or more copper twin-ax serial readout "E-links". The GBTx aggregates several up to 320 Mb/s readout E-links onto a 4.8 Gb/s optical link. FELIX then receives data from several optical links and routes the data from the readout E-links to the "software Read Out Driver" (swROD) which subscribes to and processes many readout E-links. The swROD finally sends the Front-end data in an ATLAS standard format to the High Level Trigger (HLT). The swROD provides a sampled data stream for monitoring user-defined parameters and data flow directly or by other separate monitoring processes.

In addition to the L1A event flow, calibration triggers can move Front-end data along the path, either to a swROD for offline calibration or to a separate swROD that does not connect to the HLT, but instead acts as a dedicated calibration processor. Additionally, the Trigger Processors send monitoring data for non-triggered bunch crossings to an instance of the swROD (without connection to HLT) that monitors the Trigger Processors.

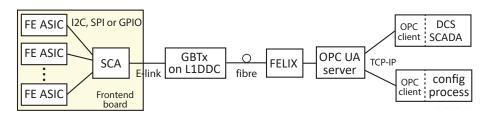

# 2.4 Configuration, command and status path

The configurable operating parameters for all NSW electronics components are controlled via the SCA ASIC [25] on every board, or its emulator in FPGA firmware, SCAx [26] (as shown in figure 1). An SCA server based on the OPC UA [27] architecture is the software interface to the SCA and SCAx. The communication is realized via FELIX and GBTx E-links. Configuration and status reporting processes access the various SCA and SCAx configuration and status registers through several OPC UA clients. Commands such as resets, are also sent on this path. The same path is shared with the Detector Control System's (DCS) OPC UA client for monitoring board and ASIC conditions, such as voltages and temperatures, that are sampled by the SCA.

# 2.5 Busy path

Should a FELIX FPGA or server be near to overflowing its buffer space, it can assert a BUSY signal on a dedicated electrical line. The "OR" of all such lines requests the Central Trigger to stop generating the Level-1 Accept triggers, thus preventing the Front-ends from (eventually) sending more data, thereby allowing FELIX to clear its buffers. Busy can be asserted when FELIX suspends transmission of events in response to the swROD sending an XOFF via Ethernet. The NSW Read

<sup>&</sup>lt;sup>1</sup>The L1A originates from the ATLAS Central Trigger. On receipt of L1A, FELIX sends out L0A; it then sends L1A after a configurable delay. This allows time for the transfer from VMM to ROC.

Out Controller can send BUSY requests to FELIX, but this feature is not foreseen to be active during normal detector operation. The Pad Triggers and Trigger Processors will assert BUSY should their buffers become full.

#### 2.6 Trigger data path

The trigger paths contain hits from the VMM "Time-over-Threshold" (ToT) outputs for the sTGC pads, the VMM "direct" 6-bit charge data outputs for sTGC strips, and the VMM "Address in Real Time" (ART) output for the Micromegas. The digitized data is tagged by the trigger data serializers (the ART and TDS ASICs) with the value, the "BCID", of a BC counter which remains attached to the data as it moves through the system. All the trigger primitives are sent to the Trigger Processors, one per sector per detector type. The sTGC and Micromegas Trigger Processors separately find track segments from hits in their respective detectors. For sTGC, hits are the centroids of charges induced on strips. For Micromegas, hits are the channel number of the first hit in the bunch crossing per Front-end VMM ASIC. Hits are used to find track segments pointing to the Interaction Point. On every bunch crossing, the sTGC Trigger Processor merges the sTGC and Micromegas segments and sends them to the Sector Logic. The Trigger Processor is described in section 4.

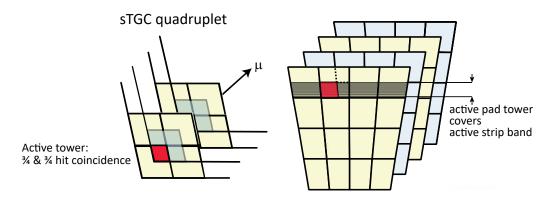

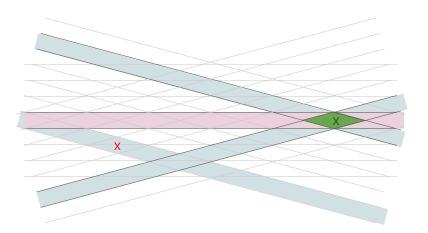

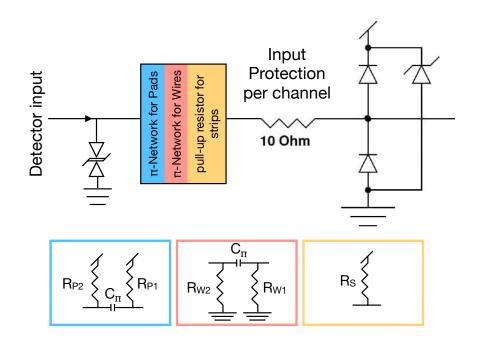

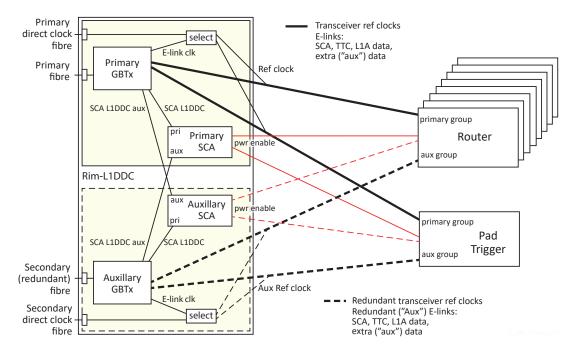

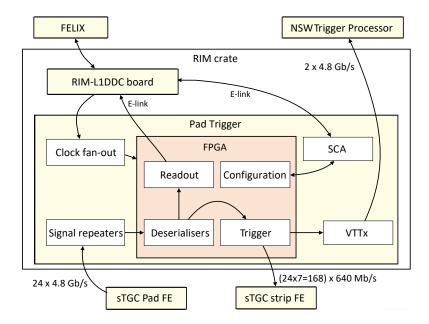

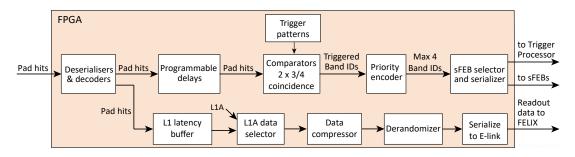

**The sTGC trigger.** Ideally, one would read out all the strips in a sector directly to that sector's Trigger Processor. However, reading out a 6-bit charge for each of 282,000 strips on every bunch crossing would require the huge bandwidth of almost 70 Tb/s. The power, cooling, and cost of current electronics are prohibitive. In order to reduce the number of strips to be transferred to the Trigger Processor, the NSW uses eight-layer towers of sTGC pads pointing to the interaction point to provide a pre-trigger. See figure 2.

**Figure 2**. A band of strips in each layer is selected by a particle making a 3-out-of-4 hit coincidence in a pointing tower of sTGC pads in each quadruplet. The pads in half of the layers are shifted by half a pad in both directions to increase the resolution. Eight-layer towers pointing to the interaction point are defined by the overlapping physical pads (shown in grey) which identify a logical pad (in red) in each layer.

The pre-trigger per sector is formed by the Pad Trigger board (section 7.5) on the rim of the NSW. Coincidences between layers of the towers identify up to four bands of strips in each of the eight layers. The Pad Trigger signals the TDS ASICs that contain those bands to transmit the strip charges to the Trigger Processor via the Router (section 7.6). Note the zigzag path in figure 1 and its consequent significant increase in trigger latency. The Trigger Processor receives the strip charges

and calculates a centroid for each layer. These are used to calculate r and  $\Delta\theta$  of a track segment and to apply the  $\Delta\theta$  cut mentioned above.

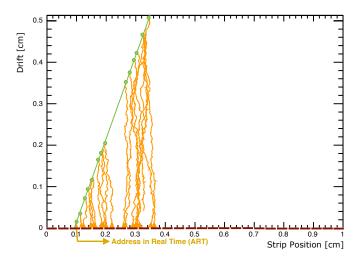

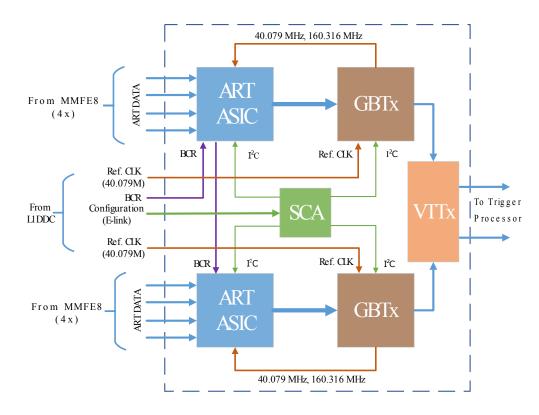

The Micromegas trigger. although being a 2.1 M channel system, utilises the Address in Real Time (ART) output of the VMM to scale down the system to  $\sim 262$  k channels for the trigger. The concept utilises the fine pitch of the Micromegas detectors and the spread of ionisation charge for particles crossing the detector at an angle [28]. The VMM sends out the address of the channel that presents the earliest signal in every bunch crossing. For the fine  $\sim 0.45$  mm strip pitch, this is a good approximation of the coordinate perpendicular to the strips direction; see figure 3. The address is sent to the ART ASIC on the ADDC board which receives the addresses of 32 VMMs and selects eight of them to be sent out to the Trigger Processor. The 32 ART ASICs in a sector collect the addresses from all the eight layers and transmit them serially on 32 fibres to the Trigger Processor (one per sector) which forms track segments. Since the drift time of the Micromegas detectors can extend up to 150 ns, the ART ASIC has the option to mask the input of a VMM which has already provided the strip with the earliest time within the drift time of the Micromegas. Therefore, signals originating from the same particle track, but from a different strip, can be discarded if desired.

**Figure 3**. A simulated event showing the ionisation from a particle crossing the Micromegas detector at an angle. The address of the strip to which the charge arrives first is output as an ART signal. Reproduced with permission from [28].

# **3 FELIX**

The Front End Link eXchange (FELIX), developed by the ATLAS Trigger and DAQ project [14–20], interfaces 4.8 Gb/s optical links from GBTx ASICs that aggregate several slow serial copper "E-links", to an industry standard Ethernet network. These slow links carry Front-end readout, configuration, calibration and detector monitoring data. Acting similarly to a network switch, FELIX routes these slow links individually between Front-end electronics and software processes on the network, such as those shown in figure 1. Furthermore, it distributes the TTC (Timing, Trigger and Control) signals,

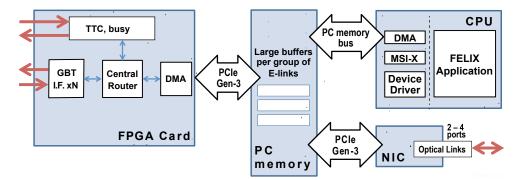

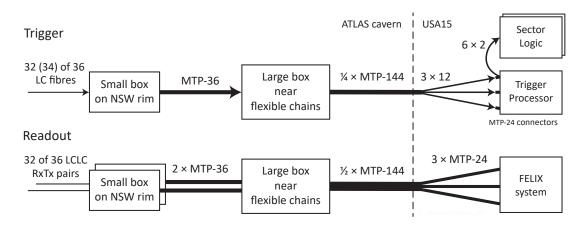

including the LHC Bunch Crossing clock, to all the NSW electronics. FELIX is built from custom PCIe FPGA cards [18] hosted in commercial Linux servers, each equipped with a high-performance Ethernet interface card; see figure 4. FELIX provides a common platform for some ATLAS Phase 1 subsystems and will do so for all ATLAS subsystems in Phase 2. The use of commodity components and the sharing of a common platform reduces hardware, firmware and software effort.

The New Small Wheel uses the version of the FELIX FPGA card with 24 4.8 Gb/s links in each direction in so-called GBT mode. Each From-detector optical link carries data from between 9 and 21 slow, copper twin-ax serial links, "E-links"; To-detector links carry between 7 and 18 serial E-links. The slow serial E-links are aggregated to the 4.8 Gb/s fibre by the GBTx ASICs on L1DDC boards or directly by the Trigger Processor Carrier FPGA.

**Figure 4**. Block diagram of the FELIX server. A server may contain up to two FPGA cards. The Network Interface Card (NIC) for NSW has two 25 Gb/s ports and supports RDMA [29].

FELIX receives TTC information from an ALTI [22] Timing, Trigger & Control (TTC) module via a fibre connection. It also asserts BUSY on a dedicated electrical line should its FELIX FPGA or server buffers be near to overflowing.

For Phase 1, there are 60 FELIX FPGA boards in 30 servers. Phase 2 requires 40 additional boards (based on 24 input links per FPGA). Although the Phase 2 fibres reach the radiation-protected underground room (USA15), the Phase 2 FELIX boards and servers will not be installed until Phase 2.

#### 3.1 Geographic names

There are over 22,000 E-links in the NSW. For the software to have the ability to address them according to their data type and the exact region of the NSW to which they are connected, each one is given a geographical or logical name, a so-called Detector Resource Name [30]. Referencing by geographic name is much clearer, less error prone and easier to maintain than by its physical FELIX connection. Also switching to spare fibres or spare FELIX servers is transparent to the software. The names are independent of specific connections of the multi-fibre bundles from the detector to FELIX boards and servers. The mapping is done via "FELIX-ID"s [31], with NSW experts maintaining the translation from fibres and E-links to FELIX-IDs and FELIX experts maintaining the translation from FELIX servers. An example geographical name is: "MM-A/V0/L1A/strip/S4/L3/R11/E3". It refers to L1A data from Micromegas, Version 0, Endcap A, strips, Sector 4, Layer 3, Radial position 11, Readout controller E-link 3. Corresponding to the string is a 32-bit binary representation that can be used within data records to identify their data.

#### 4 Trigger processor

The Trigger Processor for each sector is located in the radiation-protected room, USA15. On every bunch crossing, each NSW Trigger Processor sends to the Sector Logic up to eight unique track segments that point to the Big Wheel. The segments must point within  $\pm 15$  mrad of the infinite momentum track from the interaction point. If there is a NSW track segment that matches a Big Wheel track segment, the Sector Logic sends the  $p_T$  information of the segment from the Big Wheel with a "NSW" flag to the Muon-to-Central Trigger Processor Interface (MUCTPI). If there is no NSW track segment with a Big Wheel track segment, the Sector Logic sends the  $p_T$  information of the segment without the flag. The MUCTPI/CTP can make a decision, according to the Level-1 trigger menu, based on the  $p_T$  and the flags. Due to the mismatch in Big Wheel and New Small Wheel sector coverage, the Trigger Processor sends its segments to up to seven Sector Logic modules. A context diagram for the Trigger Processor is shown in figure 5.

Figure 5. Context diagram for the Trigger Processor.

The Trigger Processors find track segments from the trigger primitives that they receive as described in section 2.6. The Micromegas ART ASICs collect hits from the Micromegas Front-end boards and serialize them onto a fibre link to the Trigger Processor. For bands of strips, the sTGC strip-TDS ASICs send their strip charge information to the sTGC Trigger Processor via the Routers. In both cases, 32 fibres at 4.8 Gb/s connect to the Trigger Processor per sector. The sTGC Trigger Processor also receives input from the Pad Trigger board of its sector.

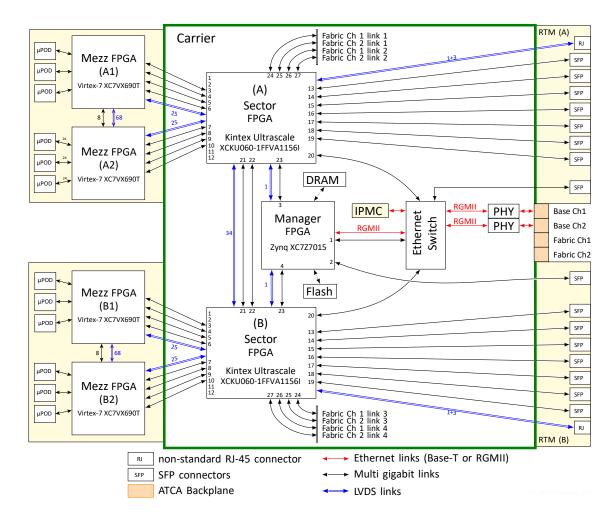

#### 4.1 Hardware

The NSW Trigger Processor platform is built according to the Advanced Telecommunications Computing Architecture (ATCA) standard [32]. A Trigger Processor "blade" consists of a carrier

**Figure 6**. Block diagram of the Trigger Processor ATCA card showing the Carrier, two mezzanines, the Rear Transition Module (RTM) and an Intelligent Platform Management Controller (IPMC) card. Each mezzanine hosts an sTGC FPGA and a Micromegas FPGA for a sector.

card, two mezzanine cards and a Rear Transition Module (RTM). See figure 6. The sTGC and Micromegas use the same hardware for their trigger logic, but with different firmware. A single mezzanine card with two Xilinx FPGAs,<sup>2</sup> one for Micromegas data and one for sTGC data, handles one sector. The two FPGAs can communicate with each other via 68 fast (640 Mb/s) low-latency LVDS signals. The ATCA blade supports two such mezzanines. The backplane signal connections are so far not used. More information on the Trigger Processor hardware can be found in [33].

**Carrier.** The Carrier conforms to the ATCA standard. Two Xilinx Ultrascale FPGAs,<sup>3</sup> one for each sector, hold the FELIX interface. Should it be required, buffering and preparing the Level-1 accepted data could be moved here from the mezzanines. A Xilinx Zynq System-on-Chip FPGA,<sup>4</sup> running Linux CentOS 7 on the Zynq's 32-bit ARM CPU, provides some board management functions. An on-board Ethernet switch connects the Carrier's Sector FPGAs, the Zynq processor, the Zynq FPGA

<sup>&</sup>lt;sup>2</sup>XC7VX690T. <sup>3</sup>XCKU060-1FFVA1156I. <sup>4</sup>XC7Z7015 [34].

fabric and the CERN IPMC card [35] to the external network. Board management functions include configuring the Carrier and Mezzanine FPGAs, via the Xilinx Virtual Cable (XVC) [36] over the Ethernet network, configuring jitter cleaners, clocks and the Ethernet switch and reading the board ID. XVC can also be used as a debug interface for the firmware of all the other FPGAs. Other board management functions are provided by the IPMC card. In addition, there is a dedicated high-speed serial link between the Zynq and each of the two Carrier FPGAs which may be used for debugging or monitoring purposes.

**Mezzanines.**<sup>5</sup> In addition to the two FPGAs mentioned above, the mezzanine connects to 72 fibres via three 12-channel 10 Gb/s microPOD [37] optical receivers, three 12-channel 10 Gb/s microPOD optical transmitters per FPGA and jitter cleaners for the required design clocks and FPGA transceiver reference clocks. A Module Management Controller (MMC) from Samway Electronic SRL [38, 39] on each mezzanine communicates with the IPMC management card on the Carrier.

**Rear Transition Module (RTM).** The RTM provides several SFP cages for serial transceivers: one connected to the on-board switch for an Ethernet transceiver, another to the Zynq, and several connected to the Sector FPGAs for the fibre transceivers to FELIX. The RJ-45 connectors provide four LVDS lines to each of the Sector FPGAs. The RTM provides also a clock input which may alternatively supply a clock to the entire Carrier system. For self-triggering of the NSW, an LVDS trigger output signal is available from one of the RJ-45 connectors. There is also an MMC on the RTM.

# 4.2 FPGA firmware

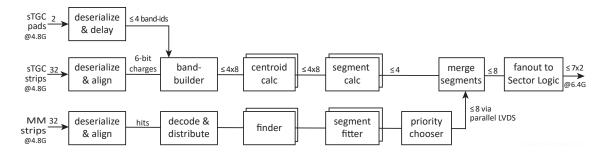

The Trigger Processor segment finding pipeline in the mezzanine FPGAs is shown in figure 7. A brief overview is given below and further details can be found in [40].

Figure 7. The Trigger Processor segment finding pipelines implemented in the mezzanine FPGAs.

#### 4.2.1 Micromegas specific trigger processing

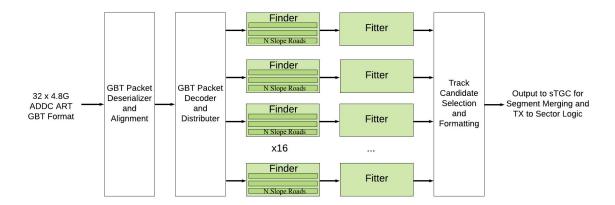

The main blocks of the Micromegas Trigger Processor (MMTP) algorithm are shown in figure 8. Its functionality requires sixteen copies of the algorithm operating in parallel. Each copy is sharing information with its neighbour to avoid boundary issues. The algorithm generates its 320 MHz clock from the main BC clock.

<sup>&</sup>lt;sup>5</sup>The custom mezzanines do not conform to the ATCA mezzanine standard.

Figure 8. The Micromegas Trigger Processor block diagram.

**Input capture and alignment.** The first stage of the firmware receives data from 32 GBT links from the 16 ADDC boards in one sector. The deserializer uses the 320 MHz clock derived from the main bunch crossing clock. The data from the GBTx ASICs on the ADDC boards are captured by fixed latency receiver firmware [41]. In order though to account for each fibre length and provide fixed latency to a single BC clock, the data is registered twice using a clock that is phase aligned to the recovered BC clock. The first register is used to account for any individual fibre length differences. The second register provides a configurable phase adjustment but the phase is a single constant set for all fibres. This register aligns the data from all fibres and provides a fixed latency.

**Decoder.** Incoming strip hit addresses are decoded into global slope values. A strip's stored slope value is defined as the orthogonal distance between a given strip and the beam-line divided by the z location of the relevant detection plane. It is pre-computed taking into account a strip offset and a z position stored for each of the 8 planes and 16 radial segments of each wedge. The slope range is divided into approximately 1000 slope-roads which are used to form a track candidate.

**Finder.** The track finding algorithm is slope-road based with the wedge divided from bottom to top into approximately 1000 roads which corresponds to about eight detector strips per road. Hit data from the decoder is routed to the corresponding road and that road is marked as being hit. Each slope-road can hold a single hit for each plane and this hit expires after the hit configurable integration time of up to eight BC clocks. The slope-roads will overlap each other to accommodate tracks on the boundaries. Each slope-road is checked once per bunch crossing to determine if a coincidence threshold has been met. Coincidence requires a minimum number of planes to be hit and the oldest hit of the track to be expiring. Coincidence identification is accomplished using combinatorial logic and a priority encoder. The strip number and slope for each hit are calculated and passed to the track fitting algorithm.

The Finder algorithm separates the X-plane (perpendicular to the  $\eta$  coordinate) and the UVplane coincidences (±1.5° with respect to the X-plane respectively). The fitter will first identify a coincidence trigger on the X planes and then scan from left to right all of the UV-roads that overlap the triggered X-road. The overlapping area of UV-roads are the so-called "diamonds". Figure 9 shows such a trigger coincidence. For each X trigger there can be up to 57 UV-roads that are searched. The number of diamonds is configured for each algorithm region to match the length of the Micromegas detector strips. Every bunch crossing, each of the 16 algorithm regions can process two independent X-road coincidences. For every X-road coincidence, the Finder can process three UV-road coincidences. The amount of resources used by the Finder is proportional to the product of the number of roads and the number of planes. The Finder implementation focuses on minimizing the resources used in each slope-road. In the total design, it uses the most resources.

**Figure 9**. Illustration of the Micromegas XUV trigger candidate. The X-plane candidate is merged with the UV-candidate to form a coincidence on the so-called diamond road which corresponds to the geometrical coincidence of the strips.

**Fitter.** In the fit, individual hit slopes in a slope-road are used to calculate global slopes associated with each plane type. From these slopes, the expressions for the fit quantities  $\theta$  (the zenith), and  $\phi$  (the azimuth) can be derived. The  $\Delta\theta$  (the difference in  $\theta$  between the direction of the segment extrapolated back to the interaction point and its direction when entering the detector region) can be derived.

The expected tolerance for installation of the Micromegas chambers is roughly 2 mm, although it is possible to have larger deviations. In order to retain the optimal performance of the trigger, alignment corrections need to be performed. The corrections need to be performed rapidly to minimize latency, and also to have a small number of constants to avoid large look-up tables.

**Candidate selection and output.** The process starts by collecting the segments from the 16 algorithm regions. Each region can generate eight segments every bunch crossing. A priority encoder is used to select eight total segments each bunch crossing from all regions. The selected segments are transferred to the sTGC FPGA using sixteen 640 Mb/s LVDS signals. The receiver in the sTGC FPGA, uses independently delayed versions of the same signal to set the sampling point to the center of the data "eye" and provide segment data to the sTGC logic that will be aligned to the sTGC clock with no additional clock domain crossing being necessary.

# 4.2.2 sTGC specific trigger processing

**Input capture and deskew.** The FPGA multi-gigabit serializer-deserializer pairs do not have fixed latency. After every power cycle or link reset, the data are written to the deserializer's parallel output bus with an uncertain shift of  $\pm 1$  deserializer output bus clock. The capture block waits for a

configurable worst-case delay, including differing cable delays, to ensure all the data has arrived. This delay has been determined by observation, and all inputs are continuously monitored to confirm that they never exceed the configured worst case. The strip-TDS band data are transmitted in four 30-bit scrambled packets in one BC. The packet format is shown in [42].) The Xilinx FPGAs in the Router and Trigger Processors work with 20-bit packets. The capture block unscrambles the data and rebuilds the 104-bit payload.

**Band-builder.** The Pad Trigger may find up to four coincidence towers. For each band of strips passing through a tower, each of eight strip-TDS ASICs, one (or two for split bands) per layer, will transmit the band's strip charge information via the Router handling its layer to the Trigger Processor. Each Router has four fibres to be able to transmit up to four bands. In the case of multiple bands, the bands' strip charge information arrives at the Trigger Processor on one of the four fibres from each Router, but not necessarily with the same fibre id for all of the eight layers. For each band, the Band-builder routes the data for all eight layers of that band to one of the four instances of the trigger algorithm. Latency is reduced by using the Band-ids and  $\phi$ -ids provided by the Pad Trigger a few BC's earlier than the Router data arrive to address all the Look-up Tables needed to process that data for that Band-id and  $\phi$ -id. The 128 channels of the strip-TDS are not necessarily aligned with the boundaries of the bands. Consequently, about 7% of the bands in a layer span over two strip-TDS ASICs. The Band-builder concatenates the two charge vectors received from the two input fibres. There are 86 bands for which all eight layers are available for use in the trigger.

**sTGC algorithm.** There are four identical instances of the algorithm that take the strip charge information of the bands in eight layers and calculates a track segment. A track segment consists of a radial R-index, an azimuthal  $\phi$ -id and a  $\Delta \theta$  as described in section 2.6. They are calculated from the centroids of the charge distributions received for each layer. Each stage of the algorithm is described below.

*Cluster selection.* If the charge distribution in a layer of a band is inconsistent with a minimum ionizing particle, then that layer of the band is rejected. Valid charge distributions, "clusters", are defined by a look-up table whose address is a vector with "ones" for strips above a threshold and whose value gives the location of the beginning of the cluster (or -1 for an invalid cluster). The look-up table requires cluster widths between two and five and with at most one extra isolated noise strip. This rejects bands with ionization from neutrons and  $\delta$ -rays.

Layer centroid. The centroid of each cluster is calculated and projected onto the plane of the wires.

*Quadruplet centroid.* The required three or four valid centroids of a quadruplet are projected onto the central plane of the quadruplet, assuming the track originates from the interaction point, and the average radial position is calculated. This accounts for the different *z* positions of the valid planes.

Segment calculation. To calculate  $\Delta \theta$ , a piecewise linear approximation to  $\tan(\theta_{\rm IP} - \theta_{\rm local})$  is made. Each linear segment corresponds to the region of a Band-id. The extrapolation of *R* is done to the sTGC wire plane furthest from the Interaction Point and assigned to an R-index. The  $\phi$ -id is provided by the Pad Trigger data.

#### 4.2.3 Segment merging and duplicate removal

The Micromegas Trigger Processor finishes finding segments before the sTGC does. It transfers up to eight track segments found to the sTGC Trigger Processor. They are transferred via sixteen 640 Mb/s LVDS signals within one BC clock. They are held until the sTGC Trigger algorithms complete. From the up to four sTGC segments and up to eight Micromegas segments, a maximum of eight segments can be sent to the Sector Logic. The Merge block removes duplicates and drops segments beyond the eight allowed. Priority is currently given to sTGC segments. There are options to ignore one or the other of Micromegas or sTGC segments and for "duplicates", to take the  $\phi$ -id from Micromegas and the other variables from the sTGC segment.

#### 4.2.4 Ancillary functions

**Connection to FELIX.** The Trigger Processor interfaces to FELIX with the Xilinx GTH serializer/deserializer and CERN's GBT-FPGA firmware [23, 24]. Together they emulate the GBTx ASIC. This firmware runs on the Carrier Sector FPGAs. Each Micromegas and sTGC sector have a FELIX link. The GBT-FPGA recovers the BC clock with fixed latency and decodes/encodes a received/transmitted 120-bit GBT packet every BC clock. The received and transmitted 120-bit words are mirrored between Carrier and mezzanine FPGAs every BC via 8b/10b encoded serial transmission at 6.4 Gb/s. The mezzanines connect to the appropriate fields in the 120-bit word that correspond to specific E-links. This mirror connection does not have fixed latency, and so is suitable only for the readout, configuration and monitoring paths, but not for the eight TTC signals. These are transferred to the mezzanine via eight LVDS lines along with the BC clock. Zero-delay PLL jitter cleaners recondition the BC clock and ensure fixed latency of the FELIX link interface. A soft processor implemented in the Carrier Sector FPGA manages the PLL and GTH transceiver during the clock acquisition sequence and runtime operation.

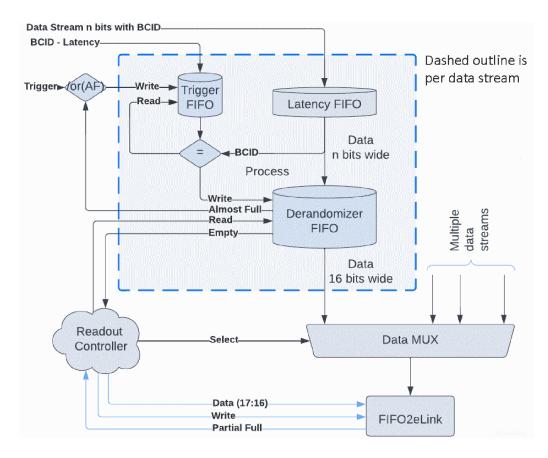

**Readout of Level-1 Accept data.** All input data, output segments and some intermediate data are captured every bunch crossing in FIFOs. When a Level-1 Trigger arrives at the Trigger Processor, data from a configurable window of bunch crossings is formatted and queued in a derandomizer for output to FELIX via E-links. To increase the total bandwidth, several 320 Mb/s E-links can be used by sending groups of input channels and segment output via different E-links. Furthermore, since Level-1 Triggers on consecutive bunch crossings are allowed (Phase-2), the readout block allows the data for a given bunch crossing to be transmitted in more than one output event packet.

**Configuration of operating parameters and reporting status.** The SCAx package [26, 43] provides read/write access to operating parameters, configurable look-up tables and status words. It emulates the I<sup>2</sup>C channel of the SCA ASIC. This enables the configuration and status reporting to be done using the same software based on OPC UA, [27] as used for the Front-ends. Unexpected conditions such as BCID mismatch, can be reported by sending an exception code and context information via an exception E-link. These exceptions are further handled by software.

**Monitoring "interesting" non-Level-1 Accepted bunch crossings.** A separate readout E-link exists for monitoring bunch crossings of interest, e.g. receiving a 3-out-of-4 Pad Trigger coincidence or corner cases and anomalies. Figure 10 shows the architecture of the monitoring logic. Intermediate pipeline data such as band-builder output, segments, and merge candidates are buffered in the

Latency FIFOs. Various points along the processing pipeline may trigger the current bunch crossing as one to be monitored. The data from triggered BC's are transferred to the Derandomizer FIFOs. For bunch crossings that have been triggered, the Monitoring Readout Controller builds the data for that bunch crossing from all Derandomizer FIFOs, into a monitoring packet that is sent out on an E-link dedicated to monitoring. In this way, the FPGA firmware can be debugged and verified.

Figure 10. Monitoring in the Trigger Processor.

Level-1 readout of all ATLAS for monitoring "interesting" NSW bunch crossings. If data only from bunch crossings that are accepted by the Level-1 trigger are recorded, we cannot know if NSW segments did not result in a trigger due to improper functioning of the NSW trigger. To address this, the Trigger Processor can flag in the packet sent to the Sector Logic that this bunch crossing is "interesting", e.g. a 3-out-of-4 coincidence. The Sector Logic forwards the flag via the MUCTPI to the CTP, which generates a Level-1 Accept with trigger type "NSWMON", unbiased by any other detector or trigger processing. This allows a monitoring process to correlate NSW trigger data with the more detailed NSW front-end data, the Sector Logic and the MUCTPI data for that bunch crossing. The NSWMON trigger type is broadcast to all swRODs via TTC; it allows other detectors and NSW sectors that did not generate that NSWMON event to exclude these events from their monitoring sample. The CTP ensures that the rate of these events does not exceed a few 10's of Hertz.

#### 4.3 Bunch crossing synchronization of the trigger paths

Data from the sTGC Pad Trigger, Routers and the Micromegas Trigger Processor for a given orbit and bunch crossing must arrive at a point in the sTGC Trigger Processor simultaneously. This alignment is done by defining the first bunch crossing in the first orbit in a run by broadcasting an Orbit Count Reset Request via the TTC path to the Pad Trigger and Micromegas Trigger Processor just before the start of the run. A flag in the data transferred to sTGC from Micromegas and the Pad Trigger indicates if the data are before the first bunch crossing in the first orbit in the run. The sTGC Trigger Processor then discards such data but saves unflagged data in a FIFO that holds it until needed in the sTGC pipeline. For the sTGC path, the Pad Trigger sends the non-existent band-id, 0xFE, on the first bunch crossing of the first orbit in the run. The reception of a data packet with this band-id by the sTGC Trigger Processor begins the tagging of bunch crossings in its pipeline as being in the run.

# 5 CERN ASICs

The ASICs described in this section were developed by the CERN Electronic Systems for Experiments Group for use in several experiments.

#### 5.1 GBTx — GigaBit Transceiver

The GBTx ASIC [10, 11], aggregates many slow (2, 4, or 8 bits per bunch crossing, i.e. 80, 160 or 320 Mb/s) serial data links called *E-links* into a single serial link running at 4.8 Gb/s. It provides one such link in each direction; the two directions are completely independent. The GBTx ASIC is radiation hard and uses forward error correction to assure uncorrupted data transmission. Its net throughput is 3.2 Gb/s with error correction, or 4.48 Gb/s without error correction in "Widebus mode" used by the ADDC (see section 7.4.). The 120-bit payload frames are transported with fixed latency, synchronous with the LHC bunch crossing clock. One GBTx can transport event, configuration, control and monitoring streams, and, by virtue of its fixed latency, the bunch crossing clock and TTC (Timing, Trigger and Control [44, 45]) signals. The GBT-FPGA firmware [23, 24] implements the GBTx protocol into an FPGA.

**E-links** consist of a serial input, a serial output and an output clock, all of whose rates are separately configurable. E-links use the SLVS [46] standard. The properties of different E-links are somewhat constrained (see [20]). The output data and the output clock are transmitted with a fixed phase with respect to the recovered BC clock. To accurately capture the input data, each E-link's internal receive clock phase with respect to data arrival must be calibrated. Data is transmitted transparently. In the NSW, all E-links carry 8b/10b [47] encoded data, except the SCA E-links which carry High-Level Data Link Control protocol (HDLC) [48] encoded data and the TTC links which are not encoded. The 8b/10b encoding further reduces the throughput to 2.56 Gb/s. Control symbols in the 8b/10b standard are used to delineate start and end of packets. The jitter of the E-link clocks is of the order of 5 ps which is within the working range of the data acquisition but is marginal for FPGA gigabit transceiver reference clocks [49]. To accurately capture the input data, each E-link's internal receive clock phase with respect to data arrival must be calibrated. See section 11.1.

# 5.2 SCA — Slow Control Adapter

The SCA ASIC (Slow Control Adapter) [25], developed by CERN, is used to configure all the ASICs in the NSW. It is part of the GBT chip-set and communicates to FELIX through a 80 Mb/s GBTx E-link. The E-link is encoded in HDLC. It provides communication to other chips using I<sup>2</sup>C, SPI, JTAG protocols as well as General Purpose I/O. The industry-standard OPC UA [27] was chosen as the software interface to the SCA to be easily compatible with the Detector Control System's SCADA program and to take advantage of industry standard software. Although initially the ASIC was featuring a faster ADC with more accurate sampling, in the end, this could not be realised and a slower implementation based on a Wilkinson architecture was adopted. The ADC implemented is a 12-bit ADC [50] based on a single-slope Wilkinson architecture with a range up to 1.0 V with a maximum conversion rate of 3.5 kHz. Conversions are triggered by software commands. This implementation underestimates the VMM's measured ENC and scaling should be implemented (see section 11.2).

#### 5.3 FEAST — DC-to-DC converter

The CERN FEAST ASIC [51] provides up to 10 W of Point-of-Load non-isolated DC power from  $\sim 10 \text{ V}$  input. FEASTMP pluggable modules [52] are also used. The output voltage is set by a resistor. Several voltages between 1.2 V and 3.3 V are required by the various NSW boards. The device is radiation tolerant for Total Ionization Dose (TID) above 200 Mrad(Si) and has an adjustable switching frequency between 1 and 3 MHz. For the FEAST ASICs in the NSW, the range is between 1.3 and 1.7 MHz.

## 5.4 VTRx, VTTx — optical interfaces

The VTRx and VTTx are radiation tolerant bi-directional and dual transmitter optical link interfaces respectively. They target data transmission between the on-detector and off-detector electronics at rates up to 5 Gb/s with an emphasis on High luminosity LHC level radiation resistance, low power dissipation and low mass components. They are protocol-agnostic and use a standard LC-LC optical connector mounted on a pluggable module. Their development was a joint ATLAS-CMS project, the Versatile Link project [53–55]. Care must be taken to adequately cool them which was foreseen in the NSW project.

# 6 NSW ASICs

The four NSW ASICs (VMM, ROC, TDS, ART) are fabricated in the Global Foundries 130 nm 8RF-DM CMOS process on a common 8-inch wafer. The reticle plan is shown in figure 11.

# 6.1 VMM — Mixed-signal front-end ASIC

The VMM [56–58] is a custom Application-Specific Integrated Circuit (ASIC). It is designed to be the front-end ASIC of both the Micromegas and sTGC detectors of the New Small Wheels. For the NSW, it is packaged in a 400-ball  $21 \times 21 \text{ mm}^2$  Ball Grid Array (BGA) with 1 mm ball pitch.

|              | AE            | AC       | AB           | AB           | AB           |

|--------------|---------------|----------|--------------|--------------|--------------|

|              | ART2          | LARTDS17 | Nevis15_chip | Nevis15_chip | Nevis15_chip |

|              | AH            | AA       |              |              |              |

| R            | IOC2          |          |              |              |              |

| AF           |               | VMM3a    |              |              |              |

| F            | ROC1          |          |              |              |              |

|              | AD<br>Cx2_130 | AA       |              |              |              |

| AG<br>TDSVII |               |          |              |              |              |

|              |               | VMM3a    |              |              |              |

**Figure 11**. The NSW wafer reticle, showing the locations and relative sizes of two copies of the VMM3a, one ROC1 and one ROC2 along with the TDSvII and the ART2 ASIC. There are other ASICs for the ATLAS Calorimeter in the same reticle. As seen, the reticle contains two versions of the ROC ASIC. This was done in case the ROC2 version had an issue and the fall-back solution for scheduling reasons was the ROC1. There are 86 reticles in the 8-inch wafer. Those on the perimeter, however, could not be used. Each wafer contains 113 VMM3a, 66 ART2, 62 ROC1, 65 ROC2 and 65 TDSvII chips. The number that can be extracted depends on how the wafer is cut. The reticle size is  $20798.32 \times 20795 \,\mu\text{m}$ .

# 6.1.1 Requirements

The 64 channels with highly configurable parameters meet the processing needs of signals from all sources of both detector types.

**The Micromegas** signals from the anode strips (negative polarity signals), depending on the chosen gas gain and shaper integration time, can be up to a maximum 250 fC, but typically half or even smaller charge is expected. The fast electron current is followed by the positive ion current which typically lasts for  $\sim 150$  ns [28]. In addition to the current signal duration and maximum input charge, the other relevant parameter is the electrode (anode strip) capacitance which varies from about 50 to 300 pF depending on the length of the strips. The noise is a critical parameter for the Micromegas determined by the requirement of single primary electron detection with a threshold five times the RMS noise, a gas gain of 10,000, and the maximum possible electrode capacitance of 300 pF. These conditions determine the required noise level to be at 0.5 fC or about 3,000 electrons RMS.

**The sTGC** feature three different types of active elements on a detector: strips, wires, and pads. All three are read out via the VMM. Strips provide the precision radial coordinate measurement for track reconstruction, wires the azimuthal coordinate; pads are used for a "pre-trigger" that requires a configurable coincidence performed by the Pad Trigger (see sections 2.6 and 7.5) firmware among the signals of pads in consecutive layers. The wire signals have negative polarity, while both the strip and pad signals are positive. Hence the need for the VMM to handle both polarities. The total charge and the long ion tail impose specific requirements on the processing of the sTGC signals. The VMM should recover from wire and pad signals of 6 pC and 3 pC, respectively, within 250 ns

while maintaining linearity up to 2 pC. For pads, it should provide the Time-Over-Threshold (ToT) and recover within 1  $\mu$ s from high charges up to 50 pC. The pads impose challenging requirements since their capacitance can be up to 3 nF. For the strips, an average charge of 1 pC is expected while the input capacitance is ~ 200 pF. As mentioned above, the sTGC signals span a very large range from 1 pC on a given strip to about 50 pC on a pad. The dynamic range for the precision strip measurement is 2 pC. The need to measure 2.5% of this charge with a 2% resolution and a 200 pF electrode capacitance, requires a noise level for a 25 ns integration time to be about 1 fC RMS. The noise for the signals from the pads with much larger capacitance (up to 3 nF) is substantially higher.

Both detectors have similar readout requirements as the architecture is the same. A maximum trigger latency of 10  $\mu$ s must be supported, so the VMM needs deep enough FIFOs to buffer the data for this length of time. Moreover, a hit rate of up to 1 MHz per channel is expected. On the other hand, the two detectors have different trigger requirements. The Micromegas need to provide the address of the VMM channel that fired first in a bunch crossing. For the sTGC pad pre-trigger, which requires binary pad hits to select relevant strips, the VMM provides a Time-over-Threshold signal. For the sTGC trigger, the VMM provides a 6-bit charge measurement of the strips within  $\sim 50$  ns. The sTGC wires do not participate in the trigger formation.

The VMM will operate in a harsh radiation environment, see table 1 and [1, 6–8]. Design techniques are applied to mitigate issues that may affect the operation of the ASIC under the above-targeted conditions. Although TID (Total Ionisation Dose) may degrade the performance of the ASIC, the VMM3a was tested for TID tolerance in the <sup>60</sup>Co source irradiation facility at BNL for the expected radiation and no performance degradation was noticed. Single event upsets (SEU), though, become increasingly more serious. To overcome SEU's in the vulnerable logic blocks (see table 2), Dual Interlocked storage Cells (DICE) [59, 60] and Triple Module Redundancy (TMR) [61] protection techniques are used. For the large storage elements such as the latency FIFO, an upset is just flagged once detected and the FIFO is reset.

| Block                                      | Type of protection                            |

|--------------------------------------------|-----------------------------------------------|

| Global configuration and channel registers | DICE                                          |

| VMM State Machine                          | TMR                                           |

| Bunch Crossing Counter                     | TMR                                           |

| L0 FIFO Control                            | TMR                                           |

| L0 Event Builder                           | TMR                                           |

| L0 Accept register, NSkip Circuit          | TMR                                           |

| Latency FIFO                               | Parity on pointer, FIFO reset on parity error |

Table 2. Single Event Upset protection schema in the VMM.

# 6.1.2 Architecture

The analog front-end section of each channel integrates a three-stage low-noise charge amplifier (CA) followed by a third-order shaper. The charge amplifier implements a programmable input polarity, a test capacitor connected to the integrated pulse generator, a power-down option, a fast recovery option for very high-charge events, and several programmable bias adjustments to accommodate a

broad range of signals. The input MOSFET is a p-channel. It is followed by a dual cascode stage and a mirrored rail-to-rail output stage. The shaper features programmable peaking time of 25, 50, 100, and 200 ns. The gain is adjustable in eight values (0.5, 1, 3, 4.5, 6, 9, 12, 16 mV/fC). A low-frequency non-linear feedback baseline holder (BLH) stabilizes the output baseline, referenced to an on-chip band-gap reference circuit set at 160 mV. The BLH has a programmable bandwidth that allows the user to enable either a mild or a strong (effective bipolar shape) compensation introduced to handle the sTGC long current due to the long drift of ions.

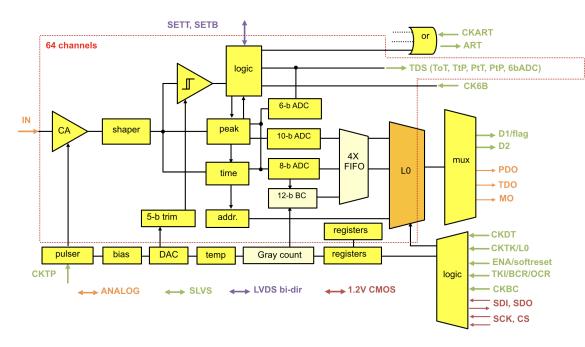

Following the analog front-end is the mixed-signal section that includes discrimination, peak and timing detection measurements and the corresponding analog-to-digital conversions. The threshold is adjusted by a 10-bit Digital to Analog Converter (DAC) common to all channels plus a local 5-bit trimming DAC independently adjustable in each channel in 31 steps of approximately 1 mV each. The peak detector measures the peak amplitude and stores its output (PDO) in an analog memory. Additionally, it provides the timing signal at the time of the peak of the analog pulse. The time detector measures the timing using a time-to-amplitude converter (TAC) which arms at the rising edge of the bunch crossing clock (CKBC) and latches at its falling edge. The time detector output (TDO) value is stored in an analog memory. The ramp duration can be configured to 60, 100, 350 or 650 ns. For the NSW, the value of 60 ns is used; this is enough to cover the duration of the CKBC while the TAC is in its linear range. The block diagram of one of the 64 identical channels is shown in figure 12, delimited with a dashed box, along with the relevant parts shared by all the 64 channel circuits and signals.

The VMM neighbor option triggers the two neighbors of a triggered channel, irrespective of whether they cross threshold. This allows raising the threshold while still digitizing the edges of a spatial charge distribution. The functionality is applicable across different VMMs through dedicated electrical lines.

Figure 12. Overview of the VMM architecture. Reproduced from [57]. © IOP Publishing Ltd. CC BY 3.0.

The mixed-signal part of the ASIC is followed by three current mode ADCs per channel. A pedestal of 150 mV is subtracted before digitization. This way the range of the ADC's is increased. The 10-bit and 8-bit ADC's are two-stage conversion digitizers providing charge and time measurements, respectively. The per-channel dead-time is driven by the 10-bit ADC conversion that is configurable down to  $\sim 250$  ns, giving an effective rate of  $\sim 4$  MHz per channel. The 8-bit ADC and a coarse 12-bit BC counter provide a 20-bit time stamp. Each channel has a direct dedicated output (DDO) where the 6-bit ADC provides the same charge measurement from the PDO but in a much faster dedicated path with  $\sim 50$  ns dead-time. The channel remains inactive until the 10-bit ADC completes the conversion. The ASIC provides the ability to interrupt the 10-bit conversion once the 6-bit conversion finishes, such that the DDO dead-time is small. In that case, the 10-bit information is unusable. The same DDO can be configured to provide pulses indicating Time-Over-Threshold (ToT), Time-To-Peak (TtP), Peak-To-Threshold (PtT) or a Pulse-at-Peak (PtP) of 10 ns duration. The address of the channel that registered the first hit per CKBC cycle, is output on a dedicated per-chip serial line. This is called the Address-in-Real-Time (ART).

#### 6.1.3 Readout schema

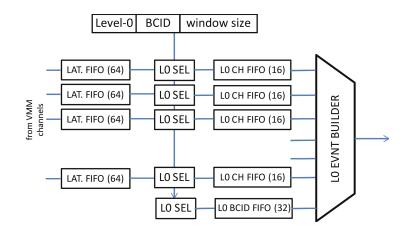

Although the VMM features more than one readout schema, the so-called "L0" mode is designed for operation within the ATLAS experiment. The output of the 10-bit and 8-bit ADCs enter into a 64-deep FIFO per channel called the "Latency FIFO". Given the size of this FIFO and the 250 ns dead-time per channel, a maximum guaranteed latency of  $16.0 \,\mu\text{s}$  where no data is lost can be achieved. This is larger than the minimum  $10 \,\mu\text{s}$  required by ATLAS Trigger-DAQ [62]. Note that each channel is autonomous and this FIFO is filled asynchronously.

Each channel has a Level-0 Selector circuit that is connected to the output of the channel's latency FIFO. The selector finds events within the BCID window (configurable at a maximum size of 8 BC's and the BC is offset by the latency) of a Level-0 Accept and copies them to the "L0 channel" FIFO. If a channel's L0 selection circuit does not find a hit within the BC window, a "no data" item is passed to the "L0 channel" FIFO. In this way the "L0 channel" of all 64 channels overflow synchronously. The "L0 BCID" FIFO is made deeper, 32-deep, than the "L0 channel" FIFO. This way, once the "L0 channel" overflows, the VMM data can still indicate on which BC this happened and can skip a configurable number of triggers to recover from the overflow while still maintaining its synchronous data-taking. The buffering scheme of the VMM L0 is shown in figure 13.

The data transfer from the VMM is done via two serial lines running at 160 MHz with Double Data Rate (DDR), giving a total bandwidth of 640 Mb/s. Two lines are used to reduce the clock rate. The Readout Controller supplies the clock for this transfer. The data is encoded in 8b/10b with one or more comma characters transmitted continuously between Level-0 events. The 8b/10b encoding reduces the effective bandwidth to 512 Mb/s.

#### 6.1.4 Trigger outputs

The VMM must provide different trigger primitives for the four different detector elements connected. This is achieved through different data outputs and specific configuration. It is possible to turn off the SLVS drivers of trigger output lines not in use in order to reduce power consumption.

Figure 13. Overview of the L0 buffer. Reproduced from [57]. © IOP Publishing Ltd. CC BY 3.0.