PS/BR/OP 76-22 18 January 1977

## THE CONTROLS OF THE NEW PSB MULTIPOLES

G. Baribaud, G.P. Benincasa, J. Donnat, B. Frammery, F. Giudici and P. Horne

## ABSTRACT

The controls of the new multipoles of the PSB are implemented from the existing IBM 1800 control computer using STAR as the data transmission system. The implementation of hardware and software is the result of a close collaboration between all people involved in the project, in the operation, and in the maintenance, of the new multipoles. Some new features have been incorporated in the design: a flexible power supply-magnet connection with identification, some equipment monitoring facilities, and a built-in analogue observation system automatically controlled from the KNOBS system.

Provisions have been made for future extension, and easy and inexpensive transition ot the forthcoming new computer system if serial CAMAC is used.

The report deals with both hardware and software implementations.

Geneva 1977

# - iii -

# CONTENTS

| 1. | INTR                                | INTRODUCTION                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |  |  |

|----|-------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|

| 2. | DESCRIPTION OF THE CONTROL HARDWARE |                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |  |  |

|    | 2.1                                 | General layout                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |  |  |

|    |                                     | 2.1.2                                                                    | Control hardware sch <b>ema</b><br>Hardware layout<br>STAR-CAMAC crate controller                                                                                                                                                                                                                                                                                                                                                    | 2<br>2<br>3                                                        |  |  |

|    | 2.2                                 | Control word, identification word, and status word specifications        |                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |  |  |

|    |                                     | 2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6                                | Control word<br>Identification word<br>Power supply status word<br>Test word<br>Reading of the control word (local control memory)<br>READY/ON/OFF status word<br>Crate equipment monitoring configuration                                                                                                                                                                                                                           | 4<br>5<br>5<br>6<br>6                                              |  |  |

|    | 2.3                                 | Equipment interface for control                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |  |  |

|    |                                     | -                                                                        | Transceiver and Control Unit modules<br>Description of the interconnection bus                                                                                                                                                                                                                                                                                                                                                       | 6<br>6                                                             |  |  |

|    |                                     |                                                                          | <pre>2.3.2.1 Data bus (1)<br/>2.3.2.2 Function bus (2)<br/>2.3.2.3 Strobe line (3)<br/>2.3.2.4 Address lines (4)<br/>2.3.2.5 READY lines (5)<br/>2.3.2.6 ON/OFF lines (6)<br/>2.3.2.7 Sign lines (7)<br/>2.3.2.8 Analogue lines (8)<br/>2.3.2.9 Analogue lines (8)<br/>2.3.2.9 Analogue input test line<br/>2.3.2.10 CIM crate power supply surveyor<br/>2.3.2.11 Initial reset line (11)<br/>2.3.2.12 Monitor reset line (12)</pre> | 7<br>7<br>7<br>7<br>7<br>7<br>7<br>8<br>8<br>8<br>8<br>8<br>8<br>8 |  |  |

|    | 2.4                                 | Analogue-to-digital conversion and<br>computer data acquisition hardware |                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |  |  |

|    |                                     | 2.4.2                                                                    | Generalities .<br>General layout of the computer acquisition system<br>Technical characteristics                                                                                                                                                                                                                                                                                                                                     | 8<br>8<br>9                                                        |  |  |

|    |                                     |                                                                          | 2.4.3.1 The Sign Multiplexer<br>2.4.3.2 The mixer<br>2.4.3.3 The AMX 16/1 analogue multiplexer<br>2.4.3.4 The analogue-to-digital converter (ADC)<br>2.4.3.5 The memory interface<br>2.4.3.6 The memory buffer                                                                                                                                                                                                                       | 10<br>10<br>10<br>11<br>11                                         |  |  |

|    | 2.5                                 | Analogue signal observation system                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |  |  |

|    |                                     | 2.5.1<br>2.5.2                                                           | Analogue observation in the Main Control Room (MCR)<br>General layout of the analogue observation system                                                                                                                                                                                                                                                                                                                             | 11<br>12                                                           |  |  |

•

|          |                         | 2.5.3                                                 | Technical characteristics                                          | 12       |  |

|----------|-------------------------|-------------------------------------------------------|--------------------------------------------------------------------|----------|--|

|          |                         |                                                       | 2.5.3.1 Transceiver                                                | 12       |  |

|          |                         |                                                       | 2.5.3.2 Bus driver                                                 | 13       |  |

|          |                         |                                                       | 2.5.3.3 Analogue observation multiplexer OMX 16/4                  | 13       |  |

|          |                         |                                                       | 2.5.3.4 Sign Multiplexer                                           | 14       |  |

|          |                         |                                                       | 2.5.3.5 Analogue driver                                            | 14<br>15 |  |

|          | 2.6                     | VARILOG using microprocessor                          |                                                                    |          |  |

|          |                         | 2.6.1                                                 | 6.1 VARILOG for power supplies                                     |          |  |

|          |                         | 2 4 2                                                 | driven by an analogue function                                     | 15<br>15 |  |

|          |                         | 2.6.2                                                 | 2 Implementation                                                   |          |  |

|          |                         |                                                       | 2.6.2.1 Software implementation<br>2.6.2.2 Acquisition of results  | 16       |  |

|          |                         |                                                       | using the CAMAC/STAR system                                        | 17       |  |

|          | 2.7                     | Hardware for equipment monitoring                     |                                                                    |          |  |

|          |                         | 2.7.1                                                 | Monitoring by the 64-Line Surveyor module                          | 18       |  |

|          |                         | 2.7.2                                                 | Power supply monitor circuit                                       | 18       |  |

| 3.       | DESCRIPTION OF SOFTWARE |                                                       |                                                                    |          |  |

|          | 3.1                     | Generalities<br>Modification of the existing software |                                                                    |          |  |

|          | 3.2                     |                                                       |                                                                    |          |  |

|          |                         |                                                       | Data bank                                                          | 20       |  |

|          |                         |                                                       | Data bank management programs                                      | 21       |  |

|          |                         | 3.2.3                                                 | The KNOBS system                                                   | 22       |  |

|          |                         |                                                       | Other modifications                                                | 22<br>22 |  |

|          | 3.3                     | New programs                                          |                                                                    |          |  |

|          |                         |                                                       | The NEW MULTIPOLES program                                         | 22       |  |

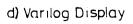

|          |                         | 3.3.2                                                 | The IDENT routine (Fig. 17)                                        | 22       |  |

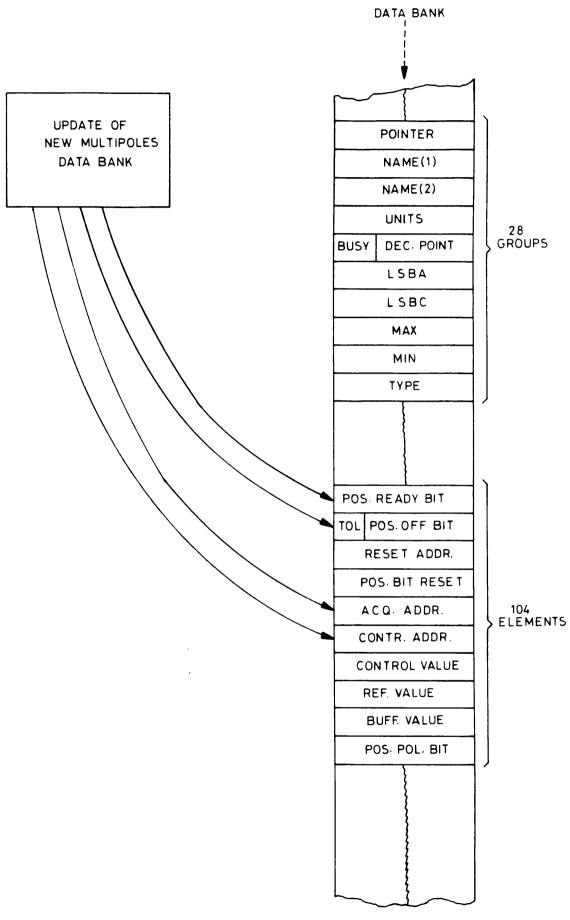

|          |                         | 3.3.3                                                 | The update new multipoles DATA BANK program                        | 22       |  |

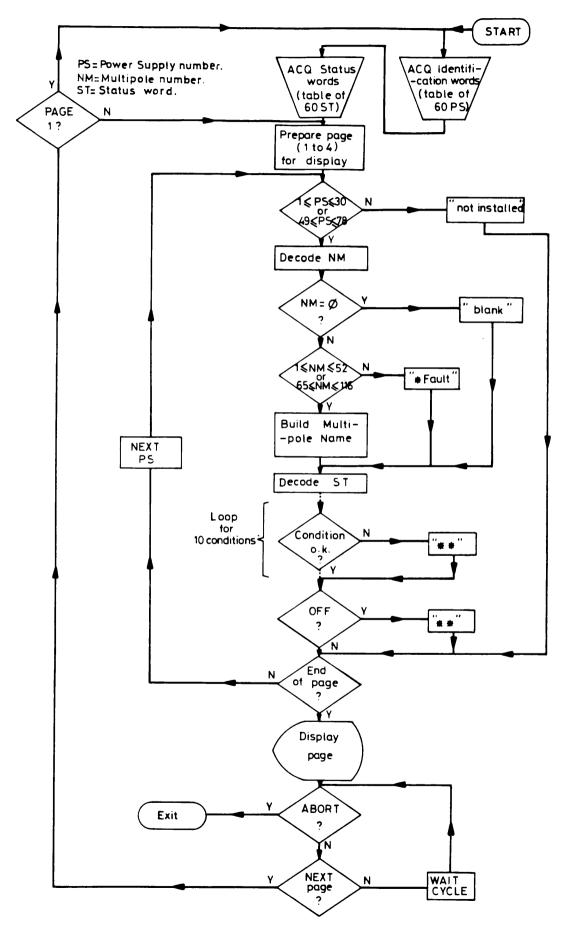

|          |                         | 3 3 4                                                 | (Figs. 18 and 19)<br>The STATUS DISPLAY program (Figs. 20 and 16b) | 23<br>23 |  |

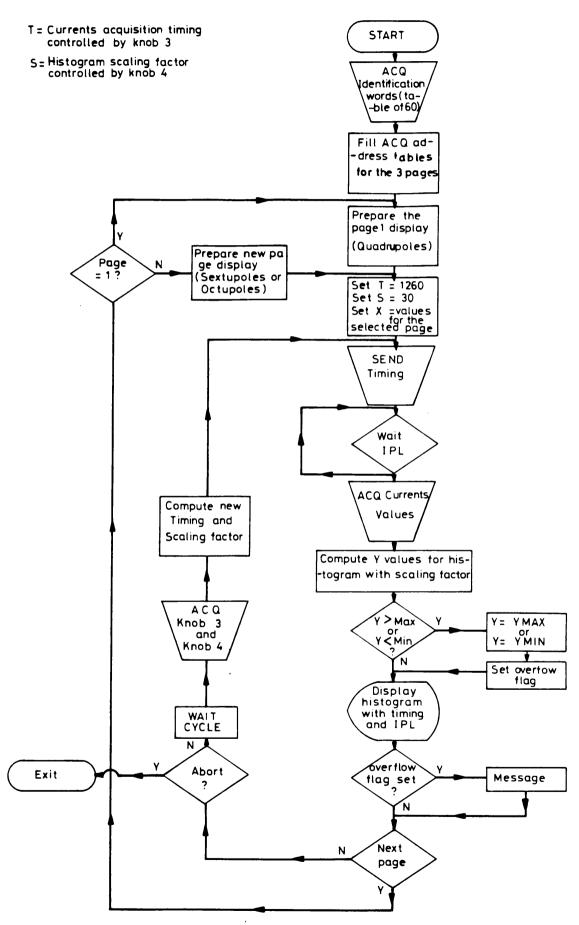

|          |                         | 3.3.5                                                 | The CURRENTS HISTOGRAM program (Figs. 21 and 160)                  | 24       |  |

|          |                         |                                                       | Other programs                                                     | 24       |  |

| REFE     | ERENCI                  | .s                                                    |                                                                    | 26       |  |

|          |                         |                                                       |                                                                    |          |  |

| FIGU     |                         |                                                       |                                                                    | 27       |  |

| APPENDIX |                         |                                                       | CAR ADDRESSES                                                      | 47<br>53 |  |

| APPENDIX |                         | 2: CONTROL AND ACQUISITION FORMATS                    |                                                                    |          |  |

| APPENDIX |                         | 3: TI                                                 | TRANSCEIVER MODULE AND INTERCONNECTION BUS FUNCTIONS               |          |  |

| APPENDIX |                         | 4: L                                                  | LISTING OF MICROPROCESSOR PROGRAM                                  |          |  |

# Page

#### 1. INTRODUCTION

Ninety-six new multipoles have been added to the PS Booster to compensate the stopbands in order to improve high-intensity beam qualities<sup>1)</sup>.

As the 96 new magnets will not be used simultaneously, at least for the time being, the number of power supplies was limited to 56 units. A manually operated switching system is provided so that any multipole can be connected to any unused power supply at will. This new feature implies the implementation of some identification process to update the computer data bank automatically whenever the connection pattern is modified by the operator.

The control software must be such that no difference can be noticed between the operation of the conventional old multipoles and the new ones (see Section 3.1). Owing to some delay in the implementation of the new PS computer system, it was decided to control the new multipoles from the existing IBM 1800.

The control hardware is built in CAMAC technology. CAMAC will probably be used for the new PS computer system<sup>2)</sup> and many CAMAC modules are now available either from commercial firms or from other groups within CERN. The CAMAC Analogue Acquisition System (CAAS), developed in the PS Division (CCI group) in collaboration with SPS for the memory part, is used in this project (see Section 2.4 for more detailed descriptions).

A close collaboration between all people involved in the project and in the future operation of the multipoles led to the elaboration of some equipment monitoring facilities and an automatic analogue observation system.

A new VARILOG facility using microprocessor in a CAMAC crate is also provided.

The implementation of the new multipoles is based on the use of new technologies to improve operation, reliability, and maintenance. The transition from the present control computer to the new one is also taken into account throughout the design. Only two serial CAMAC crate controllers will be required to interface these 96 new elements to a CAMAC serial loop system (provided serial CAMAC is selected). The present software is implemented to cope with up to 104 new multipoles and up to 96 power supplies; the number of new multipoles can be expanded if enough room can be found in the PSB data bank. The present control hardware is designed to provide complete acquisition and control facilities for up to 72 power supplies; at the moment 60 power supplies are actually installed. Ninety-six new multipoles and 56 power supplies were requested in the project.

#### 2. DESCRIPTION OF THE CONTROL HARDWARE

#### 2.1 General layout

## 2.1.1 Control hardware schema

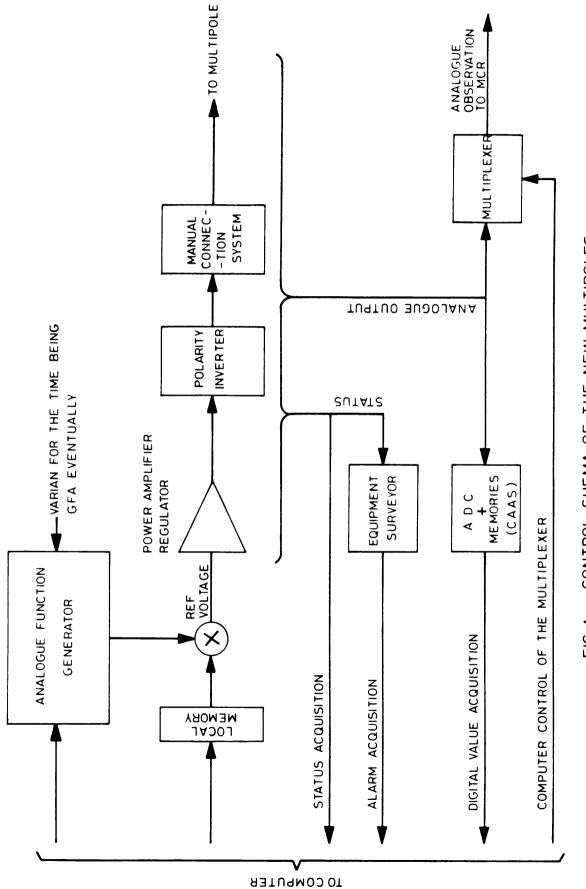

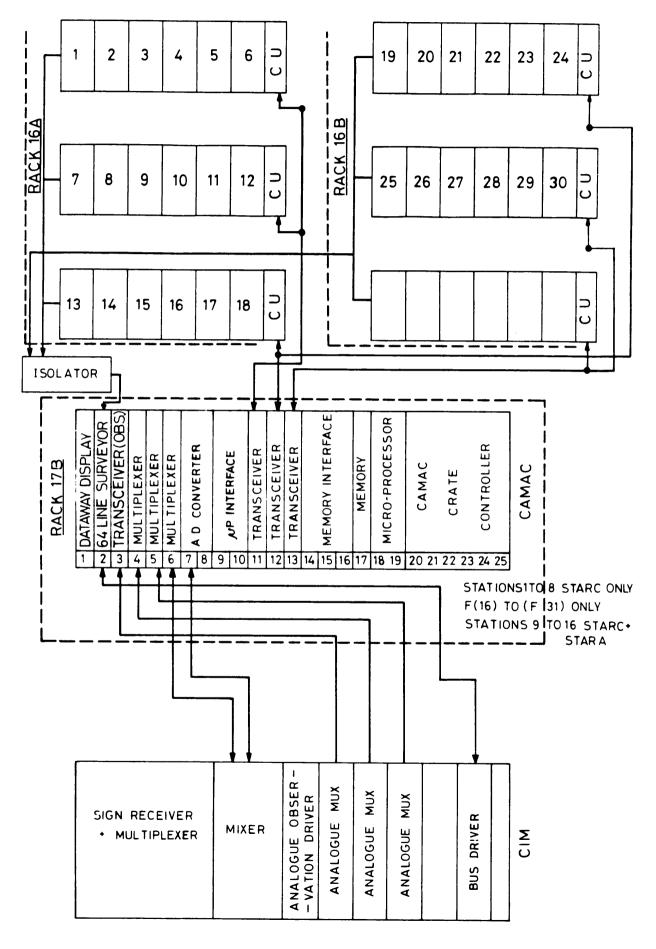

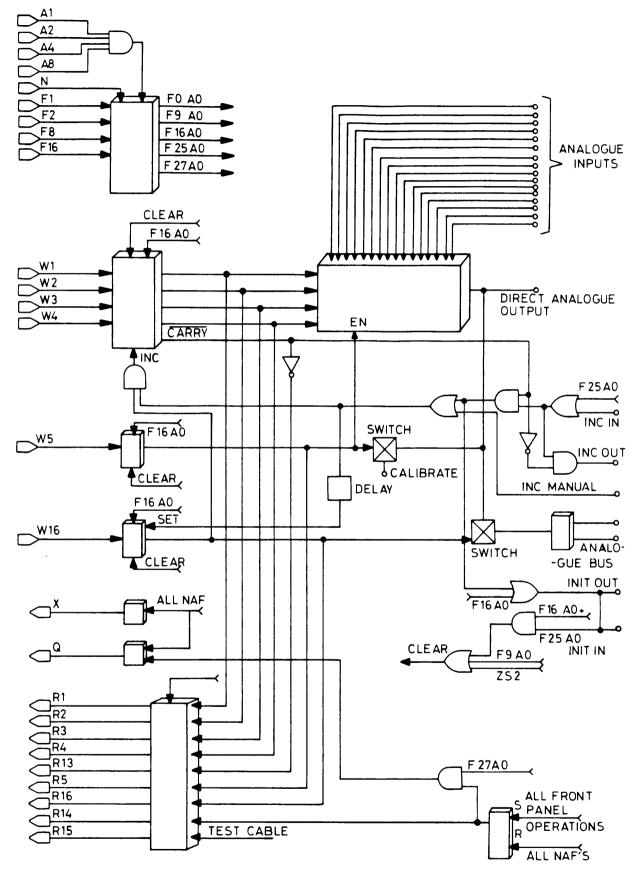

The control hardware schema of the new multipoles is shown in Fig. 1. Apart from some new features to improve the operation, the control hardware of a power supply is rather well known and it is extensively used at the PS Booster.

The analogue reference voltage at the input of the power supply amplifier is the product of an analogue function and a 10-bit digital word stored in a local memory. The analogue function is supplied by the Varian-620i-driven Function Generator for the time being. It will be replaced by some GFAs (Générateurs de Fonction Autonomes) in the new computer system; provision is made to cope with the difference in analogue output voltages of the various types of analogue function generators.

The contents of the local memory is controlled by the IBM 1800 via STAR C and CAMAC (see below); the specifications of the control word are given in Section 2.2.1. The shunt current of each power supply is processed to be interfaced to CAAS for acquisition, on the one hand, and is fed to an analogue observation multiplexer system, on the other hand.

Status bits can be directly acquired by the computer (STATUS ACQUISITION); they can also be surveyed locally by an equipment surveyor which detects any variation in the status bit pattern (see Section 2.7: Equipment surveyor). A part of the status words is formed by the identification word.

2.1.2 Hardware layout

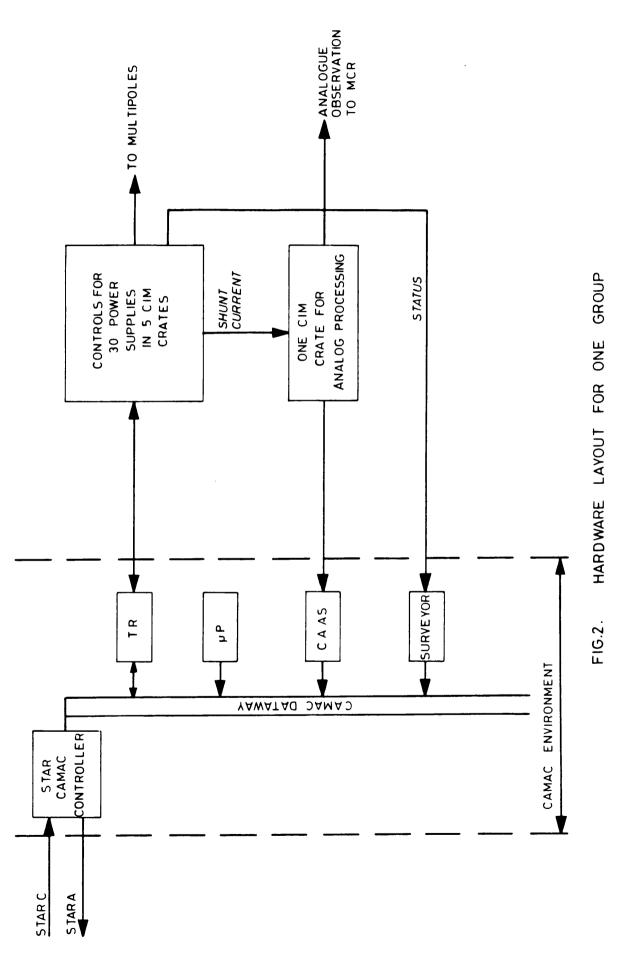

The 60 power supplies to be controlled are in fact divided into two identical groups; the two control equipments are installed in the racks BAT 17 and BAT 60. As the two groups are identical, we shall describe only one.

Though the electronics of the regulator of the power supplies are built in a modular form, they cannot be put into CAMAC modules for the following reasons:

- i) CAMAC power would not be used efficiently.

- ii) Too many STAR adddresses would be required (see STAR-CAMAC crate controller in Section 2.1.3).

- iii) The electronics of the power supply regulators must be isolated, while the common point of CAMAC power supplies is connected to ground.

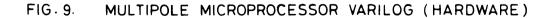

It was then decided to house the electronics of the regulators of the power supply in isolated CIM crates equipped with adequate auxiliary power supplies. The electronics for six regulators can be plugged into one CIM crate; they occupy 24 CAMAC units in space, leaving one unit to interface the CIM crate to the CAMAC dataway. In such a way five CIM crates are required per group to control 30 power supplies. The hardware layout is shown in Fig. 2. The analogue processing of the shunt currents is also performed in a separate CIM crate.

Analogue signals are treated in this CIM crate to be interfaced to the CAAS system (in CAMAC) for acquisition by the computer (see Section 2.4) and to the analogue observation system (see Section 2.5).

The status surveyor and the microprocessor are both installed in the CAMAC crates. The microprocessor is an auxiliary controller having access to the CAAS through the CAMAC dataway.

The power supply hardware is dealt with in a separate report<sup>3)</sup>.

The layout of the hardware in the CAMAC crate is shown in Fig. 3, together with the main interconnections between CAMAC and CIM crates (for rack BAT 17).

#### 2.1.3 STAR-CAMAC crate controller

As the control hardware is built in CAMAC technology (see Fig. 2) it was necessary to interface the CAMAC crates to the IBM 1800 control computer, since we could not wait until the new computer is operational. The simplest way was to interface CAMAC and STAR by means of a specially designed CAMAC crate controller proposed and built by the CCI group<sup>4)</sup>. We use two such crate controllers.

This crate controller performs all CAMAC functions on the 16 leftmost positions in the crate<sup>5)</sup>. Blocks of 128 STAR A addresses and blocks of 128 STAR C addresses can be provided independently to equip eight successive CAMAC positions. A STAR-CAMAC crate controller can utilize up to 256 STAR A addresses and 256 STAR C addresses for a fully equipped crate (16 stations).

It should also be noticed that there is no LAM handling facility with the STAR-CAMAC crate controller, but there is no need for it in our application. The STAR-CAMAC crate controller gives access to the "N" lines via a rear-panel connector; this allows the implementation of auxiliary controllers in the CAMAC crate. This feature is used by the microprocessor which can access the Analogue-to-Digital Converter (ADC) and the analogue multiplexers (MPX) of the CAAS through the CAMAC dataway<sup>6</sup>.

The HOLD<sup>7)</sup> function is also implemented in the STAR-CAMAC crate controller; it is used for the acquisition of the status words, identification words, and test words.

The lists of the STAR A and STAR C addresses are given in Tables Al to A4 of Appendix 1 for racks BAT 17 and BAT 60, respectively. These lists are edited by G. Surback. Each CAMAC crate is equipped with 256 STAR C addresses and with 128 STAR A addresses.

- 3 -

A special CAMAC hardware test<sup>6)</sup> is provided to facilitate interaction with modules installed in those two CAMAC crates; a third crate used for Q calculation is also concerned. Up to 12 CAMAC dataway operations can be performed sequentially from a list of parameters (C, N, A, and F, and data for  $F \ge 16$ ) specified by the user through the console, either in the Main Control Room (MCR) or from the mobile in the Booster building.

## 2.2 Control word, identification word, and status word specifications

In this section we define clearly all transfer words implemented in the design. The exact definition of these terms is indispensable for the coordination of the work of various teams (power hardware, control hardware and software).

#### 2.2.1 Control word

The control word is stored in a local memory which drives a digital-to-analogue converter (DAC) whose reference voltage is connected to the output of an analogue function generator. Only one local memory is provided; anyhow, pulse-to-pulse intensity modulation (PPM) can be achieved directly from the IBM 1800 for the time being. In the future two more possibilities can be envisaged with the new computer system:

i) a local digital modulator can be incorporated in the CAMAC crate<sup>9)</sup>:

ii) GFAs can be installed in large quantities to replace the Varian computer.

The format of the control word is given in Fig. Al of Appendix 2 (MEMORY CONTROL WORD): it can be read by the computer for data transfer analysis (see Section 2.2.5). The local memory is physically located in the power supply electronics<sup>3)</sup> as well as the DAC; they will not be described in this report.

## 2.2.2 Identification word

Each new multipole has its own hardwired identification number as shown on Fig. A2 in Appendix 2, Bit 1 (LSB) is used as a continuity test to detect whether a power supply multipole connection is actually done; the next eight bits (2 to 9) are used to code up to 256 multipoles per group.

Bit 11 to bit 16 are used to code the identification number of the analogue function, which is connected to the power supply and hence to the multipole. The coding of these two identification numbers is implemented in the hardware of the power supply, so it is described in a separate note<sup>3)</sup>.

The acquisition of these identification words by the computer is done via the hardware address of the power supply. They are used to modify the data-bank configuration and are displayed on the screen of the PDS 1 as connection tables (see Section 3.3).

- 4 -

Though the philosophy of the manual connection system was to reduce the number of useful power supplies, it can also be used for quick repair in case of failure of one power supply; we have to keep in mind that the time devoted to machine experiment is rather limited. With the help of the equipment monitoring facility, it is easy to localize a fault, so a suspected power supply can be replaced by an unused one and the data bank rebuilt.

## 2.2.3 Power supply status word

A 10-bit status word is provided per power supply. The format of the status word is the same for all power supplies, as is shown in Fig. A3 of Appendix 2. A close collaboration between all people involved in the design (power hardware, control hardware, software, and operation) was necessary to define the meaning of every bit of that status word. This does not mean at all an attempt to standardize status words; they depend on the application we deal with, up to 15 independent status bits can be incorporated in a single status word.

This status word is used as input for an equipment monitoring program (see Section 3 for Software and display of results).

#### 2.2.4 Test word

In order to increase the efficiency of fault diagnostic, a manually programmable 16-bit test word is hardwired in each power supply. This test word can be acquired by the control computer and compared to a reference test word; this allows a fast test of the digital acquisition system. The use of local digital displays (on CAMAC dataway as an example), in conjunction with a local mobile console, helps to localize faults. The acquisition of the test word is carried out by the following CAMAC commands:

- a) HOLD MODE A(0,5) •F(14) for first CIM crate A(8,13) •F(14) for second CIM crate

- b) NORMAL MODE  $A(0,5) \cdot F(14) + A(0,5) \cdot F(1)$  for first CIM crate  $A(8,13) \cdot F(14) + A(8,13) \cdot F(1)$  for second CIM crate

- 2.2.5 <u>Reading of the control word</u> (local control memory)

The contents of the control word stored in the local memory can be read by the computer. This facility combined with the test word (Section 2.2.4) can be used to test fully the digital data transmission system.

The acquisition of the contents of the local control memory is carried out by the following CAMAC commands:

a) HOLD MODE A(0,5) • F(6) for first CIM crate A(8,13) • F(6) for second CIM crate

b) NORMAL MODE A(0,5) •F(30) + A(0,5) •F(6) for first CIM crate A(8,13) •F(30) + A(8,13) •F(6) for second CIM crate

- 5 -

- 6 -

## 2.2.6 READY/ON/OFF status word

To facilitate the use of the knobs (see Section 3.2.2) the READY and ON/OFF status bits are grouped in a single word. As only six power supplies are found in a CIM crate the READY/ON/OFF status word contains only six bits of each. The MSB (bit 16) is a status bit generated by the common power rectifier when current overload is reached. The bit pattern is shown in Fig. A4 of Appendix 2.

## 2.2.7 Crate equipment monitoring configuration

A complementary 8-bit status word is defined in each crate for equipment monitoring purposes. The format of the word is shown in Fig. A5 of Appendix 2. Not all those equipment monitoring facilities are fully used with the present computer system; they are ready for the implementation of a more elaborate equipment monitoring program to be developed within the forthcoming computer system.

#### 2.3 Equipment interface for control

## 2.3.1 Transceiver and Control Unit modules

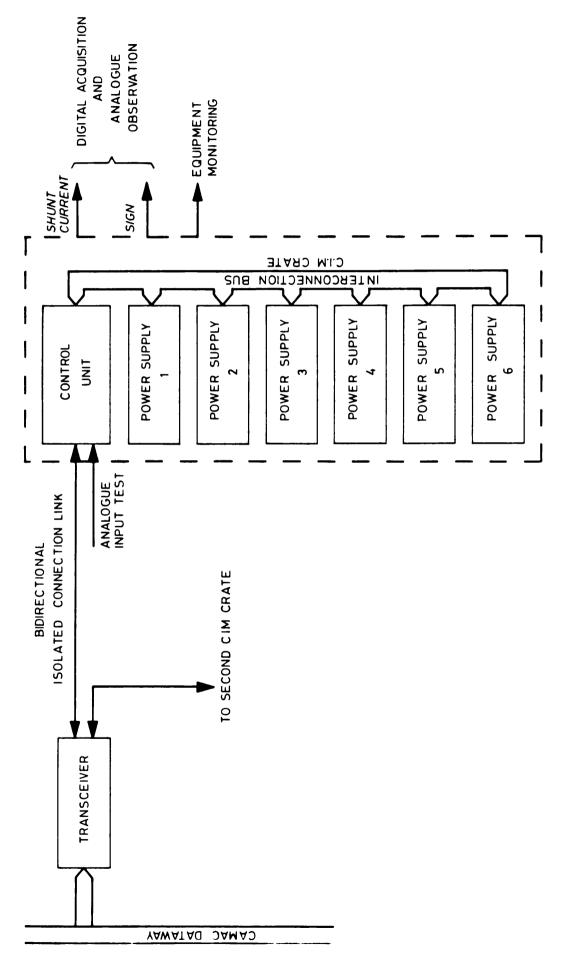

As mentioned earlier, the electronics of the power supplies could not economically be housed in CAMAC crates (see Section 2.1.2). Figure 4 shows the block diagram of the hardware required to interface CAMAC dataway to the interconnection bus in the CIM crate (for six power supplies). Two complementary modules were designed to perform this interface.

The first module, called Transceiver, is a one-unit-wide CAMAC module which can interface two different CIM crates referred to as crate 1 and crate 2. This feature allows a rather good utilization of CAMAC power, since up to 12 power supplies can be controlled from a single CAMAC slot.

The second module, called Control Unit (CU), was designed as a complement to the Transceiver; it is a one-unit-wide module installed in the 25th position of a CIM crate (see Fig. 3). Both modules are described in detail in a separate note by Hallgren<sup>10)</sup>; we only list the CAMAC functions performed by the Transceiver in Appendix 3. The galvanic isolation between the CAMAC and the CIM crates is achieved through the use of fast optocouplers in the Transceiver and in the CU. An ESAU program was written to perform a computer-driven test of the Transceiver and CU connected together.

## 2.3.2 Description of the interconnection bus

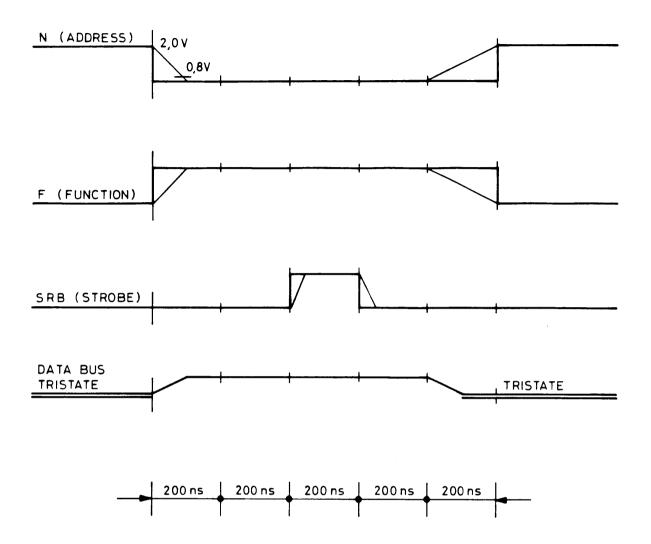

The interconnection bus in each CIM crate is worth describing, since it was used as a "team interface" between control hardware designers and power hardware designers during the project. The technology used is low-power Schoottky TTL; the layout of the bus is shown in Fig. 5, with timing references and logical levels in Fig. 6. We will describe all parts of this interconnection bus.

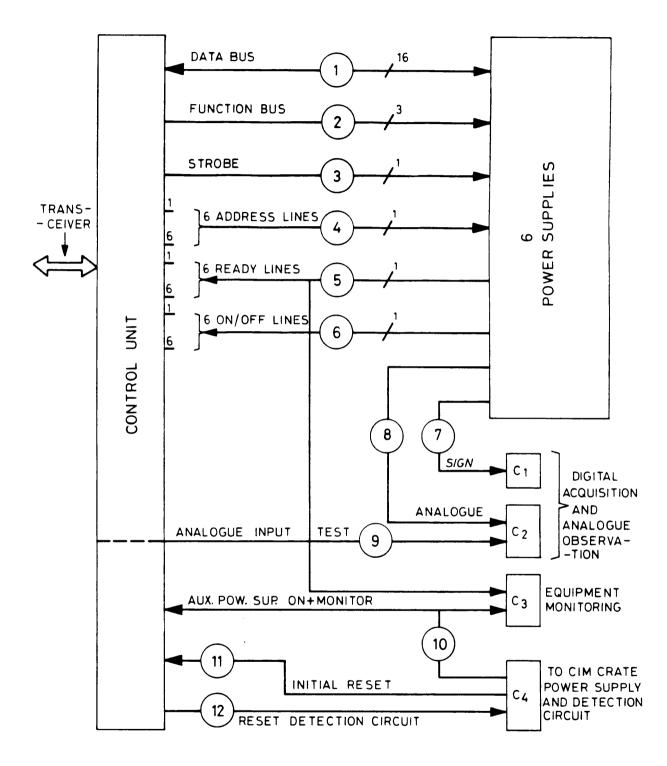

#### 2.3.2.1 Data bus (1)

Referred to as (1) in Fig. 5, it is a bidirectional bus using a tri-state circuit to transfer 16-bit data words from CU to a selected power supply or vice versa.

2.3.2.2 Function bus (2)

This 3-parallel-line bus is controlled by CU and specifies which function will be performed in the selected power supply. These functions are derived from CAMAC functions; they are listed in Appendix 3 [reprinted from Hallgren's note]<sup>10)</sup>.

2.3.2.3 Strobe line (3)

This single line is used to synchronize the operations on the interconnection bus as shown in Fig. 6.

2.3.2.4 Address lines (4)

These six individual lines are controlled by CU; they are used to address directly the power supplies; they correspond to the "N" lines of CAMAC.

2.3.2.5 READY lines (5)

The six READY lines are generated by the six power supplies; they represent the sum of all status bits of the concerned power supplies (see Fig. 6). Each READY line is routed towards two different paths:

i) to CU to be grouped in a single word for computer acquisition (see Section 2.2.6), to be compatible with the present KNOBS system.

ii) to a rear-panel connector for equipment monitoring purposes (see Section 2.7).The logical levels are as follows:

READY = 0 V (TTL logical-zero level)

NOT READY = 5 V (TTL logical-one level)

2.3.2.6 ON/OFF lines (6)

The six ON/OFF lines are generated by the six power supplies; they are grouped in CU in a single word for computer acquisition (see Section 2.2.6) to be compatible with the present KNOBS system.

```

The logical levels are as follows:

ON = 5 V (TTL logical-one level)

OFF = 0 V (TTL logical-zero level)

2.3.2.7 Sign lines (7)

```

The six sign lines are generated by the six power supplies; they represent the state of the current inverter; they are patched to a rear-panel connector Cl for digital computer acquisition and analogue observation of shunt currents. Cl is connected to the CIM crate for analogue processing (see Fig. 2 and Sections 2.4 and 2.5).

#### - 8 -

#### 2.3.2.8 Analogue lines (8)

The six analogue lines are in fact twisted pairs patched to the rear-panel connector C2 for connection to the analogue processing CIM crate (Fig. 5). The analogue voltage on each twisted pair is proportional to the shunt current of the corresponding power supply. These voltages are used for digital computer acquisition and for analogue observation in the MCR (see Sections 2.4 and 2.5).

## 2.3.2.9 Analogue input test line

An analogue signal (0 to +10 V) can be applied on an isolated LEMO connector placed on the front panel of CU. This signal is also patched to connector C2 and will be processed as a shunt current; this feature can be used to calibrate or to check the digital computer acquisition system.

## 2.3.2.10 CIM crate power supply surveyor

The auxiliary power supplies to power electronics in the CIM crates are continuously monitored by a special circuit. Whenever the +5 V power supply is distributed, the volatile memories can be modified accidentally. The power supply monitor circuit indicates all possible disturbances to the control computer which can then refresh the contents of the local memories. The output of the power supply monitor circuit is patched in the crate status word (see Fig. A5 in Appendix 2). Another bit is set when all auxiliary power supplies are on. The power supply monitor circuit is described in detail in Section 2.7.2.

## 2.3.2.11 Initial reset line (11)

Whenever the auxiliary CIM power supplies are turned on, the power supply monitor generates a pulse which resets all local memories in the CIM crate. This precaution prevents an accidental overload of the main rectifier as well as a perturbation of the circulating beams.

2.3.2.12 Monitor reset line (12)

This line is used to reset the power supply monitor; it is under computer control.

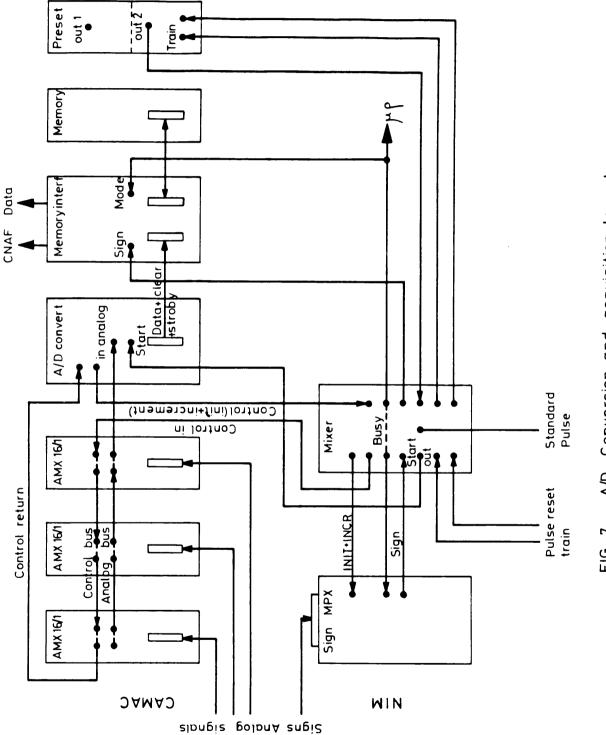

# 2.4 Analogue-to-digital conversion and computer data acquisition hardware

#### 2.4.1 Generalities

Two identical computer data acquisition systems are provided in racks BAT 17 and BAT 60, to acquire the 30 analogue shunt signals from the 30 power supplies of each group (see Section 2.1). The unipolar analogue shunt signals with their corresponding sign bit (state of the polarity inverter) are provided to the acquisition hardware on separate cables; up to 36 analogue shunt signals can be processed per system. The analogue shunt signals are multiplexed for analogue-todigital conversion and mixed for storage. The system operates either in sequential mode or in random mode, depending on the occurrence of an external START pulse (standard Booster pulse or preset counter output). Some extra test signals are provided to check the quality of the analogue-to-digital conversion and the digital data transmission system (see Section 2.3.2.9).

## 2.4.2 <u>General layout of the</u> computer acquisition system

Twisted pairs are used to transmit the analogue shunt signals. Twelve shunt signals, one test signal and a ground level signal are patched to the same connector to be multiplexed by 3 AMX 16/1 CAMAC analogue multiplexers developed for CAAS (CAMAC Analog Acquisition System) by the CCI group<sup>11)</sup> for the new computer system. The outputs of the analogue MPXs are linked to a common analogue bus connected to the input of a 12-binary-bit ADC whose conversion time is 7 µsec.

A specially designed CIM module, called Sign Multiplexer, used both for computer acquisition and analogue observation systems, collects sign bits through a 14-pin Hughes connector. The Sign Multiplexer unit receives INIT. and INCREMENT pulses from CAAS through the mixer unit.

Sign bits are sent to the CAMAC memory interface unit through the mixer unit so that both the sign and corresponding 12-binary-bit digital value are stored in the corresponding address of the 256-word buffer memory.

The contents of the buffer memory can be read in a random addressing mode by the computer through the memory interface unit and the STAR-CAMAC crate controller (see Sections 2.1.3 and 2.4.3.5).

Timing pulses (standard Booster pulses or pulse trains) are level-translated within the mixer unit, which also generates a fixed-duration BUSY signal to warn other CAMAC equipment users (see Section 2.6). The sequential analogue-to-digital conversion process is the highest-priority task, though it does not use the CAMAC dataway except for computer acquisition.

Two dual preset counters and one 256-word buffer memory (48 words are required at the moment) have been provided for future improvements such as sampling. At the moment, the analogue-to-digital conversion is triggered by standard Booster pulse RTPS04, which is also used for the old multipoles.

Remark: Some units are involved both in the computer data acquisition system and in the analogue observation system; they will be described partly in this section and partly in the next.

## 2.4.3 <u>Technical characteristics</u>

In this section it is not intended to give a complete detailed description, but every unit will be described as a block diagram with relevant technical information on inputs and outputs (see Fig. 7).

- 9 -

TTL and MOS-TTL compatible technologies are used to implement the hardware, and most of the CIM units contain on-card power regulators to fit with NIM standard power supplies.

2.4.3.1 The Sign Multiplexer

This four-unit NIM plug-in contains a mother board to which up to four 16-signal input boards can be connected.

RANDOM ACCESS bit and BUSY bit are sent by the mixer unit to enable the ADC to control the Sign Multiplexer (see Fig. 7). The INIT. pulse will reset the address counter; INCREMENT pulses will increment the 8-binary-bit synchronous counter. Each input card is equipped with a 4-bit address and one strobe signal. Input signals are galvanically isolated by optocouplers and selected through a 16 to 1 data selector MPX.

Buffer memory and 13 front-panel LEDs, mainly used in conjunction with the analogue observation system, are provided in this unit.

Eight 14-pin Hughes connectors located on the rear panel of the CIM crates are used to input the sign bits from the power supplies.

#### 2.4.3.2 The mixer

The mixer is a CIM unit performing the following functions:

- i) it delays and shapes the START pulse (from a CAMAC preset counter or a standard Booster pulse) to initialize the ADC and the Sign Multiplexer;

- ii) it generates the 400  $\mu sec$  BUSY signal to warn the microprocessor (see Section 2.6.2);

- iii) it gates and shapes the INCREMENT pulse from the ADC for the Sign Multiplexer;

- iv) it translates the standard 30 V/1 µsec pulse into TTL levels;

- v) it supplies a fixed-duration MARK pulse to be mixed with the analogue signal to ease analogue observation in the MCR;

- vi) it temporarily buffers SIGN bits for the memory interface.

This unit can easily be modified to cope with some new requirements.

2.4.3.3 The AMX 16/1 analogue multiplexer

The analogue observation MPX (see Section 2.5) units process the analogue shunt signals for analogue observation and send 12 of these signals to each AMX 16/1 analogue MPX in view of the analogue-to-digital conversion. Each AMX 16/1 either gates the INCREMENT pulses for its own use or sends them to the next AMX 16/1. The mixer unit has been placed in the control loop between the ADC and the first AMX 16/1 to get all INCREMENT pulses generated by the ADC. This unit is fully described in Ref. 11 and a block diagram is shown on Fig. 11.

#### 2.4.3.4 The analogue-to-digital converter (ADC)

The basic ADC unit developed for the CAAS has been modified to house a 12-bit, 3.5  $\mu$ sec, ADC module from Hybrid Systems. It is now registered as MPS/BR 861 7002. It is used as a unipolar ADC with a 10 V input range and it performs a conversion every 7  $\mu$ sec; half of this time is required for analogue signal selection and for data storage in the memory buffer.

## 2.4.3.5 The memory interface

A 3-unit-wide CAMAC module was necessary to house rather simple electronics because of the characteristics of CAMAC, which allocate a maximum of 16 random acquisition addresses for slot-in random mode on function F(0). Three CAMAC units are then required to provide 48 addresses. Tri-state buffers, controlled by BUSY signal through MODE input, transmit data and sign bits to the buffer memory. A CLEAR MEMORY ADDRESS signal and a STROBE pulse are sent with data bits by the ADC; these two bits are used to settle the internal address counter of the buffer memory. The transmission of data between the memory interface, the ADC, and the buffer memory is done through 52-pin Cannon connectors on front panels.

During the data acquisition procedure by the crate controller, an NAF command is generated on the CAMAC dataway; this command is fully decoded in the memory interface module to create the internal address to retrieve the relevant data from buffer memory. The data are transmitted to the dataway through open collector buffers gated by the NAF decoder. Access to stored data is done in a random fashion to be compatible with the present KNOBS system.

## 2.4.3.6 The memory buffer

Two slight modifications were made to the module developed by the SPS<sup>12</sup>; these two modifications do not alter the standard functions of the device; they concern the following parts:

- i) Input mode is controlled by the BUSY signal through the front panel Cannon connector instead of internal jumper.

- ii) The memory chips used are of Totem Pole type; otherwise internal pull-up resistors have to be added to the output of all memory chips.

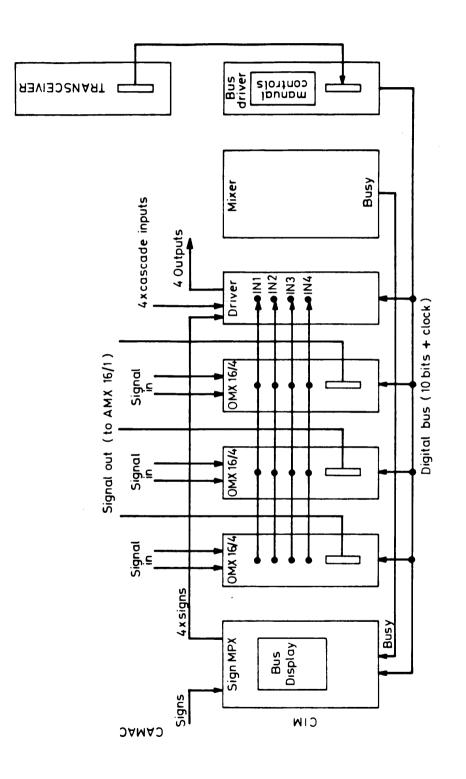

#### 2.5 Analogue signal observation system

## 2.5.1 <u>Analogue observation in the</u> <u>Main Control Room (MCR)</u>

The analogue observation of shunt currents in the MCR on conventional oscilloscopes is indispensable for the easy operation of an accelerator, although all parameters of the machine can be controlled and acquired through digital form. In view of these operational requirements a built-in analogue observation MPX is implemented in the controls of the new multipoles.

#### - 11 -

As hardware is shared in two parts, two analogue MPXs had to be provided. One of these systems acts as the master receiving the outputs of the slave as cascade input. The system allows the simultaneous observation of four bipolar analogue shunt signals; it is controlled by the central control computer through STAR and CAMAC. Hooking a knob to a multipole automatically selects the corresponding analogue shunt signals on the MPX outputs for observation on an oscilloscope in the MCR (see Section 3.2.2 for software modification in the KNOBS system).

## 2.5.2 <u>General layout of the analogue</u> observation system

A multipole Transceiver (see Section 2.3.1) sends a control word to the bus driver (see Fig. 8) specifying the desired signal and channel of the MPX to be used. The bus driver stores this control word and transmits it sequentially on a digital bus referred to as a CIM digital bus in this section; it also sends a clock pulse to synchronize read-write operation on the bus.

As long as the BUSY signal generated by the mixer unit is not active, the Sign Multiplexer selects the sign bit and the concerned analogue MPX selects the corresponding analogue shunt signal. The selected analogue signal (on a highimpedance analogue bus) and the selected sign bit are fed to the analogue driver unit to restore bipolar signals on coaxial cables to the MCR. If the selection deals with some signals from the slave subsystem, a CLEAR control signal is first transmitted to the master system to enable the cascade input of the analogue driver to be linked to the output in the MCR.

The format of the control word is as follows

| Bit 1         | : | crate number   |

|---------------|---|----------------|

| Bits 2 to 4   | : | module number  |

| Bits 5 and 6  | : | output channel |

| Bits 7 to 10  | : | signal address |

| Bits 11 to 16 | : | unused         |

The crate bit is usually one, except when a CLEAR signal is sent to the master subsystem.

2.5.3 Technical characteristics

2.5.3.1 Transceiver

This CAMAC unit is already used to control the multipoles (see Section 2.3.1). It is used to send one control word per channel to the bus driver unit; the HOLD function of the Transceiver is not used in this application.

#### 2.5.3.2 Bus driver

Channel bits are used to select locations where other significant bits of control words will be stored in  $4 \times 4$  register files allowing simultaneous readwrite operations. When the storage is done, a pulse is returned to the transceiver to finish up the transmission.

Those registers are sequentially scanned at a rate of 1 kHz and their contents are sent to the CIM digital bus through MPXs and buffers. Clock pulses derived from the internally generated 1 kHz clock synchronize writing operations in the other CIM units. The CIM digital bus is connected to the OMX 16/4 MPXs, to the analogue driver, and to the Sign Multiplexer.

Test facilities through front-panel switches and LEDs are provided. In TEST position, data can be simulated by means of 10 front-panel switches and stored in registers by pushing a button. A flashing LED warns the user when the TEST is on.

## 2.5.3.3 Analogue observation multiplexer OMX 16/4

The analogue part of the CIM unit consists of low-bandwidth unity gain amplifiers to convert balanced signals into COMMON mode analogue signals prior to multiplexing. Each amplifier drives four identical 16 to 1 MOS MPXs corresponding to the four output channels. These MPXs have ENABLE CONTROL features which allow high impedance output.

The analogue signals are entered through twisted pairs on two 14-pin Hughes connectors mounted on the rear panel (each of them contains six analogue shunt signals, one analogue test signal, and a ground level signal). The analogue signals are directly linked to front-panel Hughes connectors for direct connection to the AMX 16/1 analogue MPXs for analogue-to-digital conversion (see Section 2.4.3).

The digital part of the board consists of:

- i) A decoder processing control bits from the bus driver. Four bits are provided for module location instead of the three bits in the bus driver: for future uses of this unit one can envisage up to 256 analogue signals. A multiple switch on the card has to be set according to the location the plug-in occupies in the CIM crate.

- ii) A buffer storing channel bits and generating ENABLE signals for the MPX circuits and displaying the selected channels on LEDs. Four other buffers each store the signal address bits to be sent to the MPX. Four of these MPXs are used in each CIM crate in the multipole system. The analogue outputs are linked together per channel and entered in the analogue driver.

#### 2.5.3.4 Sign Multiplexer

When the BUSY signal from the mixer unit is down, the control of the Sign Multiplexer is performed through the CIM digital bus.

The control bits select the sign address and store it in the register corresponding to the involved channel. Thirteen front-panel LEDs indicate the used output channels, the binary address of the signal (crate, module, signal bits), and the sign of the selected address.

The MPX is used in a random fashion in the analogue observation system, while it is used in sequential mode for the analogue-to-digital conversion.

2.5.3.5 Analogue driver

This CIM unit essentially consists of four programmable amplifiers (PRAM) followed by complementary pairs of transistors to drive 50  $\Omega$  cables for analogue voltages in the range of ±10 V.

The MARK pulse (600 mV, 600  $\mu$ sec) generated by the mixer unit is added to the output signals to indicate when the analogue-to-digital conversion takes place: in case of automatic selection according to the knob specifications, the digital value of the shunt current measured at RTPSO4 follows the name of the multipole on the screen of the console (PDS-1), so an immediate comparison can be made by the operator between the digital computer acquisition path and the actual analogue parameter.

Three of the four inputs of the PRAMs are used as follows:

- i) one with unity gain (+1);

- ii) one with inverted unity gain (-1);

- iii) one with direct unity gain.

Two bits control the selection of the PRAM input: the first two inputs correspond to analogue bus signals, the sign bit from the Sign Multiplexer selecting the right one; the last one is dedicated to cascade input for signals from the other crate. The selection of this input is made with the crate bit of the control word. The bandwith of this unit exceeds 100 kHz.

The analogue signals are transmitted to the MCR in a COMMON mode, so the receiving amplifiers in the MCR eliminate 50 Hz ripple and compensate for losses in the cables. This rather simple system achieves a signal-to-noise ratio better than  $4 \times 10^{-4}$ .

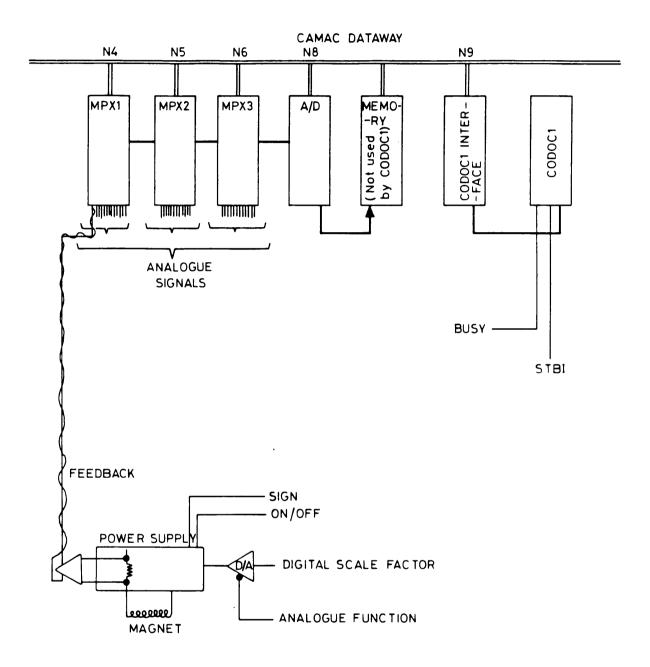

## 2.6 VARILOG using microprocessor

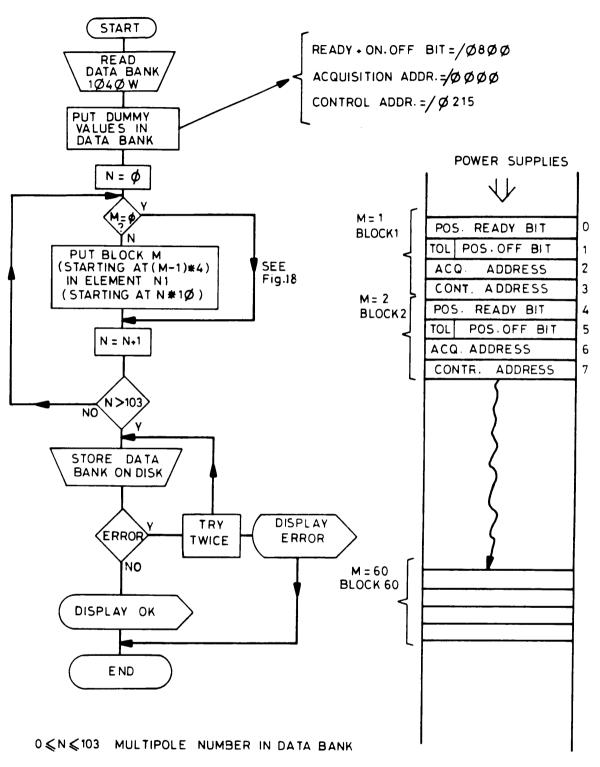

## 2.6.1 <u>VARILOG for power supplies</u> driven by an analogue function

A proposal for the use of a microprocessor in the new PSB multipole power supply control system has already been presented<sup>13)</sup>, and arose from the need to measure the shape of the function produced by each of the 60 power supplies. In this application it is known that a simple area measurement will give a good approximation to the function, but requires the acquisition of some 3840 values (64 samples per power supply) each Booster cycle. With a serial crate system, each acquisition takes approximately 50  $\mu$ sec, and therefore the total transmission time would be nearly 200 msec, which represents a large part of the Booster cycle. By introducing a microcomputer facility locally, in the CAMAC crate responsible for monitoring the power supplies, it is possible to perform all the necessary calculations to obtain the areas and then only transmit 60 values.

This microcomputer facility is in the form of CODOC 1<sup>14)</sup> and its interface to CAMAC, which acts as an auxiliary controller. Such an "intelligent" auxiliary controller in the CAMAC crate also allows us to perform equipment status monitoring and provides this information as data to be acquired by the central computer, thus once again reducing the data transmission rate.

For the moment only one microprocessor and its associated CAMAC interface have been built and tested; the second crate will be equipped with an identical microprocessor in 1977.

#### 2.6.2 Implementation

The equipment to monitor these supplies is in the two CAMAC crates used for control and acquisition (see Sections 2.3 and 2.4). The MPX and ADC with memory are already used by the acquisition system once per cycle so that the auxiliary controller must be informed when the equipment is not available (by a BUSY signal, see Section 2.4.3.1). Further, the CAMAC crate is also used  $\sim$  30 times/cycle for the transmission of the control word (see Section 2.2.1) to the DAC driving the power supplies. The microcomputer must therefore be interrupted if it is in the process of using the dataway when the controller also requires its use. These two interrupts are the only change in context of the task required during its otherwise simple operation.

A block diagram of the monitoring system is shown in Fig. 9 and consists of three MPXs, an ADC, and the auxiliary controller (CODOC 1 + interface). The task of the auxiliary controller is to set the MPXs to the required address (see Fig. 10) and read the digitized data from the ADC. This is repeated 64 times for each power supply during the Booster cycle, commencing at STB1 and finishing before EBC. [See Timing system for the PSB<sup>15</sup>.]

To control the MPX (see Fig. 11) and ADC, a daisy-chain connection of the equipment is required, such that on writing an address  $[F(16)A(\emptyset)]$  to an MPX [or an increment function F(25)A(0)], the ADC will also be triggered. The hard-ware internal to the ADC copes with the necessary set-up time of the MPX address before triggering the conversion. Also, in this configuration, when writing to one MPX the others are automatically cleared, and incrementing one MPX until overflow occurs will cause the next MPX in the chain to be incremented. Thus by only controlling the first MPX, the analogue signals on all of them can be accessed. The only time the other two MPXs need to be accessed directly is after an interrupt by either CAMAC or the BUSY signal.

#### 2.6.2.1 Software implementation

The software to perform this VARILOG resides in PROM memory on the CODOC 1 module and is written in the ASSEMBLER language of the INTEL 8080 microprocessor. The development of this program was performed on the INTELLEC 8/MOD 80 MCS development system which was acquired by the Booster group.

As mentioned previously, the task is to acquire 64 samples from the power supplies during each Booster cycle, calculate the area, and supply these results as integer values (range 0-32768) to be acquired by the central computer. A status word will also be generated by the program, which will give the validity of the results and the status of the equipment controlled by the task.

The sequence of events required of the program is as follows:

- i) Power up in a state ready to accept the STB1 signal;

- ii) Monitor the multipole power supplies, sampling each one 64 times during the Booster cycle.

- a) If CAMAC is busy (B enabled), halt any auxiliary controller operation in progress and interrupt the program. When CAMAC is free, return to the main program with all hardware set to the condition it was in before the interrupt.

- b) If the MPXs or the ADC are used (BUSY signal enabled), interrupt the program. Count the time spent, in the interrupt routine, waiting for the BUSY signal to be disabled. When the equipment is free, return to the main program with all hardware set to the condition it was in before the interrupt occurred.

- c) If STB1 occurs, initiate a PROGRAM RESTART.

- iii) When the task is finished, put the processor in the HALT state and wait for the next STB1.

A detailed description of this program is given in the listing in Appendix 4.

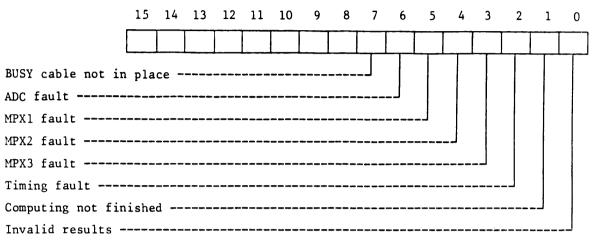

There are seven possible errors that may occur during the operation of this VARILOG program, and this information will be placed in a status word to be acquired by the central computer along with the results. The definitions of the status words and the errors are:

If the cable for the BUSY signal is not in place, the program will not commence and this error bit (7) will be set. A "Timing fault" will occur if the program is interrupted too many times during one Booster cycle, as the rate at which the power supplies are sampled will be too unevenly spaced leading to unpredictable results. The "Computing not finished" error bit is set at the beginning of the program and is only reset when the results are available to be acquired by the central computer. Finally, the "Invalid result" bit is of course just the OR of all other bits (the ADC and MPX faults are not yet implemented).

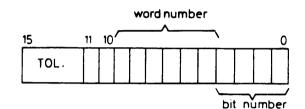

2.6.2.2 Acquisition of results using the CAMAC/STAR system

To acquire the results from CODOC 1 in a single step mode, the following sequence of operations must be performed:

- Perform the CAMAC command N(9)A(7)F(16) with data = FBFF (hexadecimal): STAR C - address = 08A1 with data = FBFF. This operation puts the microprocessor in the HALT mode and loads the DMA address register with 0400; it also reads the first result into the CAMAC READ register in CODOC 1.

- 2) Do the CAMAC command N(9)A(1)F(0) (READ RESULT) 31 times to read the 30 results and the status word: STAR A - address = 4940.

- 3) The final command is to remove the HOLD signal from the microprocessor by performing the CAMAC function N(9)A(6)F(16) with data = 0. STAR C - address = 48Al with data = 0000.

For the second microprocessor, the above addresses must be changed as follows: 08A1 to 08E1, 4940 to 4980, and 48A1 to 48E1.

The IBM VARILOG program using these results as input is described in Section 3.3.6; the PPM facility still has to be implemented.

#### 2.7 Hardware for equipment monitoring

#### 2.7.1 Monitoring by the 64-Line Surveyor module

All READY bits (sum of all internal status bits) can be monitored continuously through a 64-Line Surveyor CAMAC module<sup>\*)</sup>.

We only summarize the main features of this one-unit-wide CAMAC module also used in the new Linac project:

i) 64 different status bits (TTL level, open collector) are continuously scanned.

- ii) As soon as a bit is found in the wrong state, scanning is stopped.

- iii) By reading the module output, one gets the address (and the state) of the wrong status line.

- iv) Faulty status bits can be masked if necessary.

We use one such module in each CAMAC crate; the bits to be monitored are galvanically isolated in a separate chassis.

The status of the 60 power supplies is then limited to two bits to be tested by the computer. The state of the +5 V power supplies is also monitored through the power supply monitor circuit described below and the 64 Line Surveyor. At the moment there is no active survey of the status bits by the IBM 1800 for the multipoles. The hardware is installed and the equipment monitoring facilities will be implemented with the forthcoming new PS computer system. It was felt that manpower should now be reserved for the new computer system.

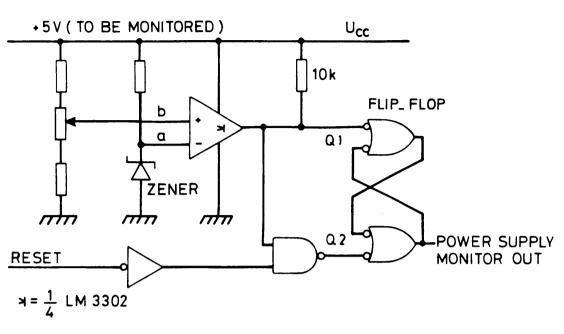

## 2.7.2 Power supply monitor circuit

In the present state of the art of memory technology, local memories used in computer control application are based on bipolar or MOS circuits. These memories are cheap, fast, and reliable, but they are volatile; this means that any lack of power supply destroys the contents of the memories; this is rather bad when the power network is prone to noticeable disturbances (industrial, thunderstorms, etc.).

Non-volatile memories such as magnetic core memories or bubble memories are not fitted for small local memory applications. Other new technologies will be available soon; the MNOS (Metal Nitrure Oxide Silicon) seem to be limited as far as the number of WRITE operations is concerned, while the DIFMOS (Double Injection Floating-grid Metal Oxide Silicon from Texas Instruments) require a writing time of 100 msec or so.

<sup>\*)</sup> Designed and manufactured by the Société d'Electronique nucléaire (SEN).

For the new multipoles, TTL memories were the only possible solution to implement local control memories; a power supply monitor circuit is associated with all +5 V power supplies.

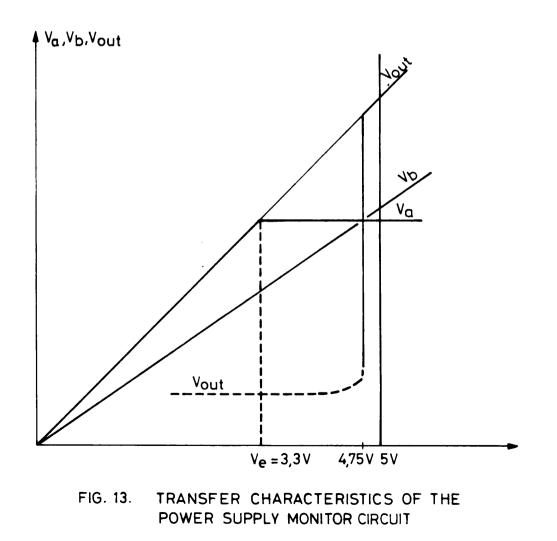

The power supply monitor circuit is shown on Fig. 12 with its transfer characteristic in Fig. 13. The +5 V power supply  $(V_{cc})$  to be monitored is also used to power the operational amplifier which acts as voltage comparator. The operational amplifier can operate correctly with a single power supply in the range from +2.5 V to +18.0 V (characteristics published by NSC). When  $V_{cc}$  is larger than 4.75 V, the  $Q_1Q_2$  flip-flop on Fig. 12 can be reset by the RESET pulse; if  $V_{cc}$  gets into the +2.0 V to 4.75 V range, the  $Q_1Q_2$  flip-flop will be set to one, and will remain in that state even if  $V_{cc}$  returns to the 4.75 V to 5.25 V range. The power supply monitor output can be sensed by the computer, which can refresh all relevant local memories and reset the  $Q_1Q_2$  flip-flop.

Two such circuits can be combined to monitor a power supply in a defined range (e.g. 4.75 V to 5.25 V). All other power supplies (not connected to memories) are monitored by conventional relays whose contacts are placed in series to create the power supply on (PS ON) status bit shown in Fig. A5 of Appendix 2.

The power supply monitor circuit is housed in a module plugged into the auxiliary power supply crate.

#### 3. DESCRIPTION OF SOFTWARE

#### 3.1 Generalities

As already mentioned, it has been agreed to have in this project<sup>16)</sup> the minimum control facilities compatible with an easy operation. This implies:

- i) no sophisticated treatments of the multipoles, e.g. no harmonics, non-linear couplings, etc.;

- ii) use, when possible, of the existing control systems, e.g. KNOBS system, data bank, etc.

This second item permits the operator to deal with new multipoles in the same way as it was accustomed to deal with other PSB parameters and, first of all, to control at the same time the new and the old multipoles.

An implication of this solution is that an important part of the software consists in modifications of the existing control programs. These modifications permit the adaptation of programs to the peculiarities of the new multipoles in a way that is, as far as possible, transparent to the user. The functional aspect of the software is intimately related to the operation of the new multipoles. However we have tried here to separate the two things and all operational aspects are dealt with elsewhere  $1^{7-18}$ .

## 3.2 Modification of the existing software

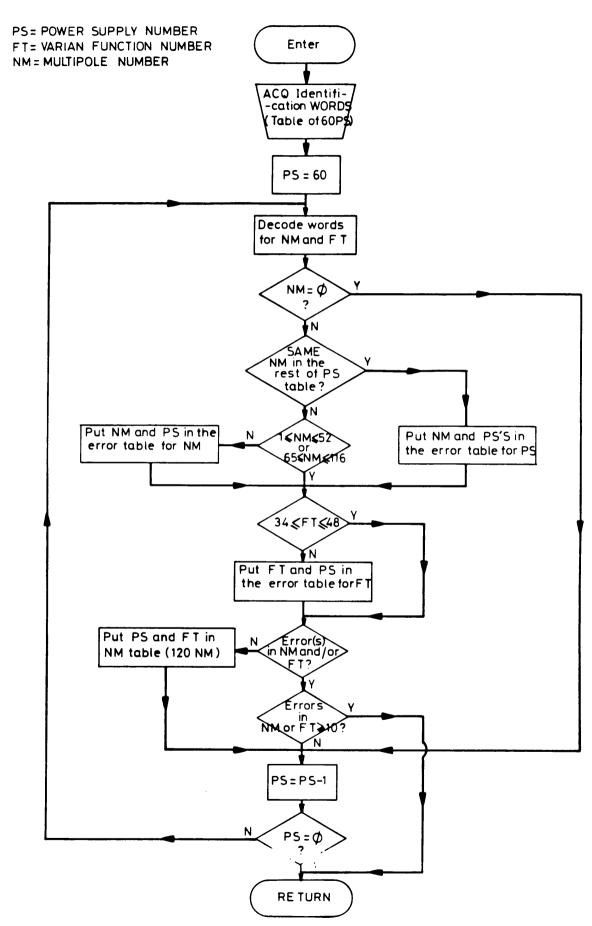

#### 3.2.1 Data bank

The new multipoles are organized<sup>19)</sup> in 28 groups, each one containing two or four elements: the number of one element represents the period in which the multipole is installed (between 1 and 16). Owing to the organization of the PSB data bank<sup>20)</sup>, the elements must be numbered progressively and room must be reserved on disk for all elements from the lowest to the highest numbered ones, no matter whether they exist physically or not.

In our case that means we need  $16 \times 28 \times 10 = 4480$  words on disk (each element specification takes 10 words). Unfortunately, that much free room does not exist in the PSB data bank. This difficulty has been overcome in the following way. The elements in each group are numbered only from 1 to 4 (or 1 to 2): the data bank management programs (see Section 3.2.2) provide the translation from the user name (1 to 16) to the data bank name (1 to 4). For example, the group containing the elements (periods) 4, 9, 13, 16 is translated into a group containing the elements 1, 2, 3, 4. The "trick" is transparent to the user. This "compression" permits the storage of the element specifications of the 104 multipoles in only 1040 words (Fig. 14). The user numbers are in parentheses. No problems exist for storing

of the group specifications  $(28 \times 10 = 280 \text{ words})$ . The group and element specifications are the same as for the other PSB parameters except for the ON-OFF and READY bits position words<sup>20)</sup>. In these two words the bits 10 and 11 have a new signification:

bit 10 = 1 means element is a new multipole

bit 11 = 1 means element is not connected

STATUS BIT POSITION WORD

## 3.2.2 Data bank management programs

i) The SOFTC routine

This routine permits the link between the name of a parameter and its specifications on data bank. It has been modified to permit the translation mentioned before between user and data bank names.

ii) The IN-CORE status word table

This table, which is updated at each PSB cycle, contains information about the status of most of the PSB elements (READY, ON-OFF, polarity conditions, etc.). Twelve acquisition words have been added for the new multipoles. Each word refers to a CIM crate and contains the ON-OFF and READY conditions for six power supplies (see Section 2.1). It also contains the overflow conditions for a bank of transistors.

iii) The READY and ON-OFF routines

These two routines are very similar: following the instructions contained in the data bank (position of the READY and ON-OFF bits, see Section 3.2.1) they read in the table mentioned in (ii) if the parameter is READY (ON) or not.

If the element is not connected (bit 11 in the status bit position word, see Section 3.2.1) the answer NOT READY or OFF is given without reading in that table. - 22 -

#### 3.2.3 The KNOBS system

Two new functions have been added to this system<sup>21)</sup>. They are activated at each machine cycle if the element connected to a knob is recognized as a new multipole (bit 10 in the status bit position word, see Section 3.2.1):

- i) The WARNING RECTIFIER bit of the CIM crate to which the multipole belongs is tested and, if ON, the message OUT OF RANGE is sent to the display (PDS 1).

- ii) The analogue MPX is activated (see Hardware, in Section 2.4) and the current function corresponding to the selected multipole is sent to the four-trace oscilloscope in the MCR. The number of the chosen trace on the oscilloscope is the same as the one of the selected knob.

## 3.2.4 Other modifications

The programs PRINT DATA BANK and UPDATE DATA BANK have been modified to treat also the new multipoles. The output of the first one is printed from the data bank names. The second one allows interaction with the data bank through the user name (see Section 3.2.1).

#### 3.3 New programs

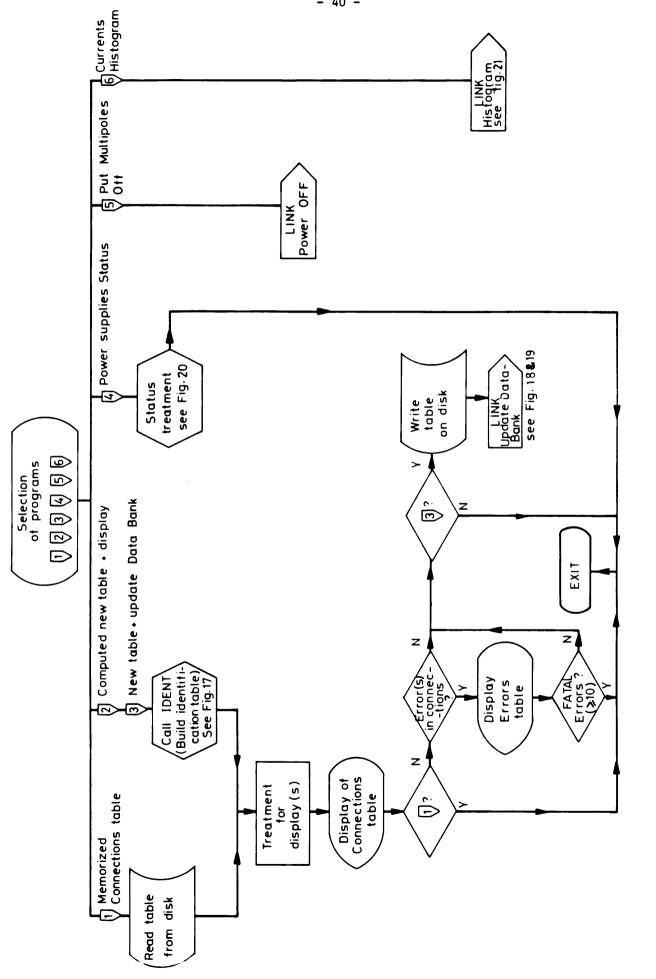

## 3.3.1 The NEW MULTIPOLES program

The functional flow chart of this program is shown in Fig. 15. The main tasks of this program are to build the connection table (see Section 3.3.2) between multipoles and power supplies<sup>17)</sup> (Fig. 16a) and to execute a status information treatment (Section 3.3.3 and Fig. 16b).

The connection table can be, on request, either simply displayed, or stored on disk and used to update the data bank. The last table stored on disk can be displayed using the first option of the program.

One important treatment concerns the error detection (see Section 3.3.2). Errors are checked, classified according to their type  $^{17,18}$ , and displayed. If their number is unacceptable, the data bank is not updated.

#### 3.3.2 The IDENT routine (Fig. 17)

The input for this routine is a table of 60 identification words, acquired from each power supply (in the future 96 power supplies are foreseen) and containing the identification word (see Section 2.2.2) of the multipole and of the analogue function driving the power supply. The output is a table of 120 words, each one assigned to a multipole (for the moment only 104 exist) and containing the reference number of the power supply and of connected analogue function.

This table is called the connection table. During the execution of this kind of table inversion, each acquired word is checked for three types of errors 17,18:

- the reference number of the multipole is not within the limits of 1 to 52 and 65 to 116 representing the two groups existing at present;

- the same multipole number is found on two or more power supplies;

- the reference number of the analogue function is not within the limits of 34 to 48.

The multipoles affected with errors of the first two types are considered as non-connected. The connection and the error tables are returned to the main program and used as explained before.

3.3.3 The update new multipoles DATA BANK program (Figs. 18 and 19)

The PSB data bank is organized<sup>20)</sup> in groups and elements specifications: both of these are usually fixed and are defined at the moment of the design. This is no longer true for the new multipoles: owing to the freedom in connections, four element specifications must be updated after each modification in the connections.

These specifications are (Fig. 18):

- the acquisition address

- the control address

- the READY bit position word

- the ON-OFF bit position word.

The program reads the element specifications of all new multipoles into core (1040 words for the 104 elements; see Fig. 14). The four concerned specifications are first filled with dummy or special values:

- acquisition address = /0000 (dummy address)

- control address = /0215 (dummy address)

- READY word = /0800 (not connected)

- ON-OFF word = /0800 (not connected).

Then, following the instructions contained in the connection table, the program fills the actual four specifications only in those multipoles that are connected without identification errors (see Section 3.3.2). Finally, the updated data bank is stored on disk.

3.3.4 The STATUS DISPLAY program (Figs. 20 and 16b)

The program provides the user with detailed information on the power supplies behaviour.

In fact the NOT READY message occurring in certain cases on the KNOBS display<sup>21)</sup> is only an OR-ed sum of many conditions; each one of them can stop the supply.

Nine NOT READY, one WARNING, and one OFF condition per power supply are checked and displayed. This information is contained in status words, one per power supply; they are acquired at the beginning of the program. At the same time identification words are acquired (see Section 3.3.2) to attribute multipole names on the display. The display is divided into four pages, each one referring to a group of power supplies.

If a multipole number error is detected (see Section 3.3.2) the message FAULT replaces the multipole name in front of the corresponding power supply reference number. After the display of the last page (page 4) it is possible to come back to page 1: in this case a new acquisition is done permitting one to follow the evolution of the status bits when hardware is being repaired.

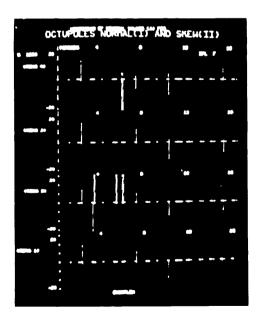

3.3.5 The CURRENTS HISTOGRAM program (Figs. 21 and 16c)

This program concerns the new and the old multipoles (except for the zeroharmonic multipoles).

An identification process, similar to that described in Section 3.3.2, permits the attribution to each new multipole of the acquisition address of the power supply to which it is connected.

Three pages of histograms are available, one for the quadrupoles, another for the sextupoles, and a third one for octupoles. On each page the four rings of the PSB are represented separately. The currents are acquired in a selected Intensity Programme Line (IPL). The initial value of the full-scale histogram is ±30 A and the acquisition timing corresponds to a B-value of 1260 G.

By turning knobs 4 and 3 respectively, it is possible to change these two parameters during the execution of the program: this avoids the tedious preselection of the starting values.

Knobs are used in the incremental mode with reset after each reading, i.e.  $P_1 = P_0 + \Delta P$ , where  $P_1$  and  $P_0$  are buffered in the computer memory and  $\Delta P$  is the knob's acquired value.

MIN ( $\pm$ 1 A) and MAX (the selected full scale) values are checked by software, and if a current exceeds these limits its representation in the histogram is truncated to these limits and a message is given.

A similar limiting check is done for timing.

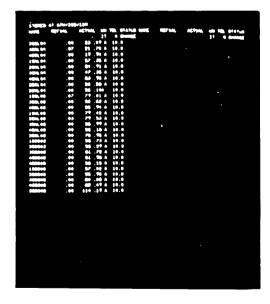

3.3.6 Other programs

A LOG program which permits one to have:

- printed information on the new multipoles in a form similar to that of other PSB elements;

- a VARILOG<sup>\*)</sup> program (see Section 2 and Fig. 16d). This program compares the actual acquired current value of each multipole with a reference value. If a

<sup>\*)</sup> The analysis of this program has been done by John Stark<sup>22)</sup>.

difference exceeding a predefined tolerance or a status change are detected, alarm messages are displayed as in Fig. 16d.

Two message pages exist for the two groups of power supplies.

The acquired values and the reference values concern time-integrated current area measurements as explained in Section 2 and in Ref. 13. For this reason the displayed values can be totally different from these given by the KNOBS or LOG programs.

## Acknowledgements

This work was carried out in continuous collaboration with many of our colleagues involved in the project. We would like to thank G. Nassibian, K.H. Reich and H. Schindl for their help in defining the system, the BR/power team members P. Burla, M. Métais, R. Gailloud, J.P. Royer and F. Völker for their close collaboration, J. Stark for his help in the VARILOG and the STAR maintenance team, and J. Philippe and G. Surback for the installation and the test of the two STAR-CAMAC controllers.

Distribution: open.

#### - 26 -

#### REFERENCES

- K. Schindl, A quoi servent les nouveaux multipôles du PSB, PS/BR Note 76-23 (1976).

- 2) The working party of the CPS controls, Improvement programme for the CPS controls, PS/CCI Note 76-33 (1976).

- P. Burla, L'électronique de commande et régulation pour les alimentations des nouveaux multipôles PSB, PS/BR/76-16 (1976).

- 4) J. Philippe et G. Surback, Contrôleur STAR-CAMAC, MPS/CCI Note 75-5 (1975).

- 5) G. Surback, Caractéristiques et particularités du contrôleur STAR-CAMAC, MPS/CCI Note 75-19 (1975).

- 6) G. Baribaud, G. Benincasa, P. Horne and D. Williams, Microprocessors help in control and beam observation at the CERN PS Booster, to appear.

- 7) F. Bel et al., CAMAC timing with special reference to crate controller timing, CERN-NP CAMAC, Note 3800 (1971).

- 8) F. Giudici, Note technique test CAMAC, October 1976.

- 9) G. Baribaud, Mémoires locales pour le PPM, PS/BR Note 76-19 (1976).

- B. Hallgren, The transceiver and the control unit for the control of the new PSB multipoles using CAMAC MPS/BR Note 75-20 (1975).

- 11) E. Marcarini, Convertisseur analogique digital, PS/CCI/Note 76-13 (1976).

- 12) C. Guillaume, Mémoire 256 × 16 mots, Lab. II CO/CC/Int. Note/CG/75-6 (1975).

- G. Benincasa and B. Hallgren, Using a microprocessor in an improved VARILOG facility, MPS/BR Note 75-2 (1975).

- 14) P. Horne, CODOC 1, Computing device for CAMAC, PS/BR Note 76-4 (1976).

- 15) G. Gelato, Timing system for the PSB, SI/Note EL/70-3 (1970).

- 16) G. Baribaud, G. Benincasa, G. Gelato, P. Heymans, K.H. Reich and K.H. Schindl, Computer control requirements for the control of the PSB multipoles, the pulse to pulse intensity modulation and the PSB equipment monitoring, MPS/BR Note 74-22 (1974).

- 17) F. Giudici, Table de connexion des alimentations des nouveaux multipôles du PSB, MPS/BR Note 75-24 (1975).

- 18) G. Benincasa et F. Giudici, Opération par ordinateur des nouveaux multipôles du PSB, PS/BR Note 76-21 (1976).

- G. Benincasa, Proposition de "baptêmes" des nouveaux multipôles du PSB, MPS/ER memorandum 27.11.74.

- D. Daneels, A data bank for on-line process control, CERN/SI/Int. DL. 72-3 (1972).

- 21) G. Benincasa, Le système KNOBS pour le contrôle du PSB, SI/BR Int. 72-3 (1972).

- 22) J. Stark, The PSB varilog, MPS/BR Note 73-16 (1973).

## FIG. 3. FINAL LAYOUT OF THE HARDWARE

- 29 -

FIG. 5. INTERCONNECTION BUS

N: TTL OPEN COLLECTOR, NEGATIVE LOGIC DATA TTL TRISTATE POSITIVE LOGIC (9 TTL LOADS) FUNCTIONS AND STROBE: TTL TOTEM POLE POSITIVE LOGIC (29 TTL LOADS)

# FIG. 6. TIMING AND LOGICAL LEVELS FOR THE INTERCONNECTION BUS

FIG. 8. Analog signal observation layout

-

.

| SUPPLY | MPX | (MPX) |

|--------|-----|-------|

| 1      | 1   | 0     |

| 1      |     |       |

| 2      |     | 1     |

| 3      |     | 2     |

| 4      |     | 3     |

| 5      |     | 4     |

| 6      |     | 5     |

| 7      |     | 7     |

| 8      |     | 8     |

| 9      |     | 9     |

| 10     | "   | 10    |

| 11     |     | 11    |

| 12     |     | 12    |

| 13     | 2   | 0     |

| 14     | "   | 1     |

| 15     | **  | 2     |

| 16     | "   | 3     |

| 17     | .,  | 4     |

| 18     |     | 5     |

| 19     |     | 7     |

| 20     |     | 8     |

| 21     |     | 9     |

| 22     |     | 10    |

| 23     |     | 11    |

| 24     | "   | 12    |

| 25     | 3   | 0     |

| 26     | "   | 1     |

| 27     |     | 2     |

| 28     | "   | 3     |

| 29     | "   | 4     |

| 30     | "   | 5     |

### FIG. 10. MULTIPLEXER / POWER SUPPLY CONNECTION

FIG. 11. ANALOG MULTIPLEXER 16/1

- 38 -

# PSB DATA BANK ELEMENT SPECIFICATIONS

(FILE 14)

(FILE 13)

(FILE 12)

(FILE 15)