# The VELO optical and power board

# **LHCB** Public Note

Issue: Revision: Published 2.0

**Reference:**

LHCB-PUB-2021-012

Authors: M. van Beuzekom<sup>1</sup>, J. Buytaert<sup>6</sup>, C. T. Dean<sup>9</sup>, K. De Bruyn<sup>2</sup>, R. Dumps<sup>6</sup>,

L. Eklund<sup>5</sup>, A. Fernándesz Prieto<sup>4</sup>, K. Hennessy<sup>8</sup>, A. Leflat<sup>3</sup>, E. Lemos Cid<sup>4</sup>,

I. Longstaff<sup>7</sup>, S. Naik<sup>7</sup>, M. Schiller<sup>7</sup>, A. Smith<sup>8</sup>, G. Visser<sup>1</sup>

<sup>1</sup> Nikhef National Institute for Subatomic Physics, Amsterdam, Netherlands

<sup>2</sup> Van Swinderen Institute, University of Groningen, Groningen, Netherlands

<sup>3</sup> Institute of Nuclear Physics, Moscow State University (SINP MSU), Moscow, Russia

<sup>4</sup> Instituto Galego de Física de Altas Enerxías (IGFAE), Universidade de Santiago de Compostela, Santiago de Compostela, Spain

- <sup>5</sup> Department of Physics and Astronomy, Uppsala University, Uppsala, Sweden

- <sup>6</sup> European Organization for Nuclear Research (CERN), Geneva, Switzerland

- <sup>7</sup> School of Physics and Astronomy, University of Glasgow, Glasgow, United Kingdom

- <sup>8</sup> Oliver Lodge Laboratory, University of Liverpool, Liverpool, United Kingdom

<sup>9</sup> Los Alamos National Laboratory (LANL), Los Alamos, United States

## Abstract

The optical and power boards (OPB) are part of the on-detector electronics system for the LHCb Vertex Detector (VELO) and they are used in LHCb upgrade 1 which is installed in the second long LHC shutdown period. The OPBs are assembled printed circuit boards (PCBs) that are located immediately outside of the VELO detector vacuum tank, in custom made mechanical crates. They perform the following main functions: optical-electrical conversion of the high-speed data and control signals that are sent to and from the detector module; DC/DC conversion of the supply voltage that is distributed to the detector module and to the components on the OPB; local slow control of the detector module and the OPB; and monitoring of the temperatures and supplied voltages of on the detector module and the OPB. The OPB operates in an environment with radiation, a magnetic field and limited cooling facilities, which is reflected in the design. This document gives and overview of the VELO electronics system and describes in detail the design of the OPB, providing diagrams to illustrate the functionality and tables to define the connectivity.

# **Table of Contents**

| 1 | IN                                     | TRODUCTION                                                                                                                                                                                                                                                                     | 1                                |

|---|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|   | 1.1                                    | OPTICAL AND POWER BOARD OVERVIEW                                                                                                                                                                                                                                               | 1                                |

| 2 | LV                                     | SUPPLY AND MONITORING                                                                                                                                                                                                                                                          | 3                                |

|   | 2.1<br>2.2<br>2.3<br>2.4<br>2.5        | GROUNDING AND POWERING SCHEME OF THE PRODUCTION OPB<br>Power dissipation estimates<br>LV supply and cable requirements<br>DC/DC converter implementation<br>Monitoring of the VeloPix voltages                                                                                 | 3<br>6<br>6<br>7<br>9            |

| 3 | ТН                                     | IE VERSATILE TRANSCEIVER (VTRX) IMPLEMENTATION                                                                                                                                                                                                                                 | 10                               |

|   | 3.1<br>3.2                             | THE VERSATILE TRANSCEIVER FOR THE OPB CONTROL SIGNALS<br>THE VERSATILE TRANSCEIVERS FOR THE DETECTOR MODULE CONTROL SIGNALS                                                                                                                                                    | 10<br>11                         |

| 4 | ТН                                     | IE VERSATILE TWIN TRANSMITTER (VTTX) IMPLEMENTATION                                                                                                                                                                                                                            | 12                               |

| 5 | TH                                     | IE GBLD IMPLEMENTATION                                                                                                                                                                                                                                                         | 15                               |

| 6 | GB                                     | <b>3T-SCA AND GBTX IMPLEMENTATION</b>                                                                                                                                                                                                                                          | 16                               |

| 7 | TR                                     | ANSMISSION LINE EQUALISATION                                                                                                                                                                                                                                                   | 18                               |

| 8 | CO                                     | DNNECTOR DEFINITIONS AND PINOUTS                                                                                                                                                                                                                                               | 20                               |

|   | 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6 | PCIE CONNECTOR INTERFACING THE OPB TO THE VACUUM FEEDTHROUGH<br>LV CONNECTORS INTERFACING THE OPB TO THE VACUUM FEEDTHROUGH<br>HIGH SPEED DATA TAPE CONNECTORS<br>OPB INPUT LV POWER SUPPLY CONNECTOR<br>MONITORING CONNECTORS<br>USB PROGRAMMING AND E-FUSE BURNING CONNECTOR | 22<br>23<br>23<br>26<br>27<br>28 |

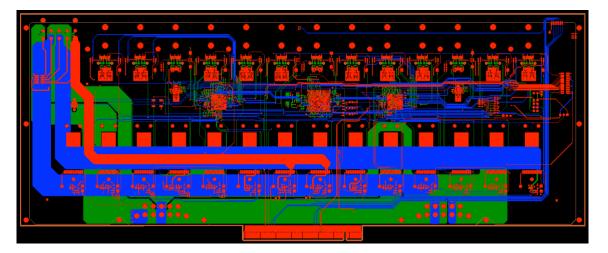

| 9 | MF                                     | ECHANICAL DESIGN AND OPB CRATE                                                                                                                                                                                                                                                 | 29                               |

| R | EFER                                   | RENCES                                                                                                                                                                                                                                                                         | 31                               |

# **List of Figures**

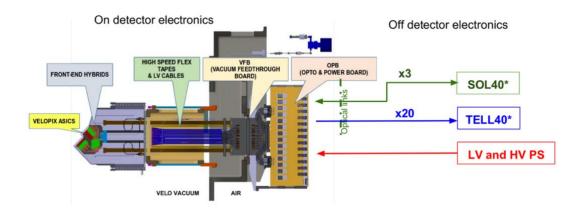

Figure 1: Schematic view of the components of the VELO on-detector electronics. .......1

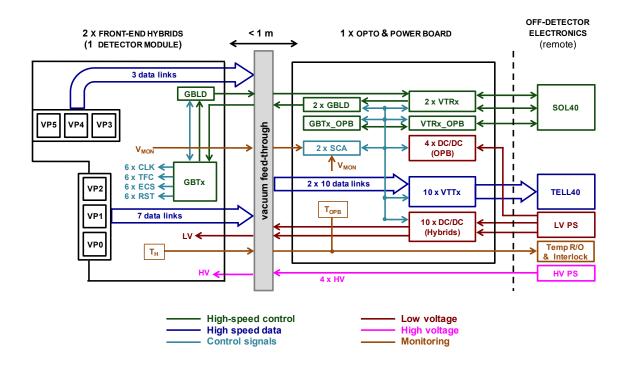

| Figure 2: Overview of the VELO Upgrade electronics showing the role and functionality of the OPB. The main components on the OPB and the hybrid are shown as boxes where the colours of the boxes and lines indicate the type of signal or supply it represents: dark blue indicate the 5.12 Gbit/s data links; dark green indicate the 4.8 Gbit/s control links; light blue (or turquoise) indicate slower control signals, either 40 MHz clock and control, I <sup>2</sup> C configuration or logical signals; red indicate low voltage supply; magenta indicate high voltage supply; and brown indicate analogue voltage or temperature monitoring signals. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

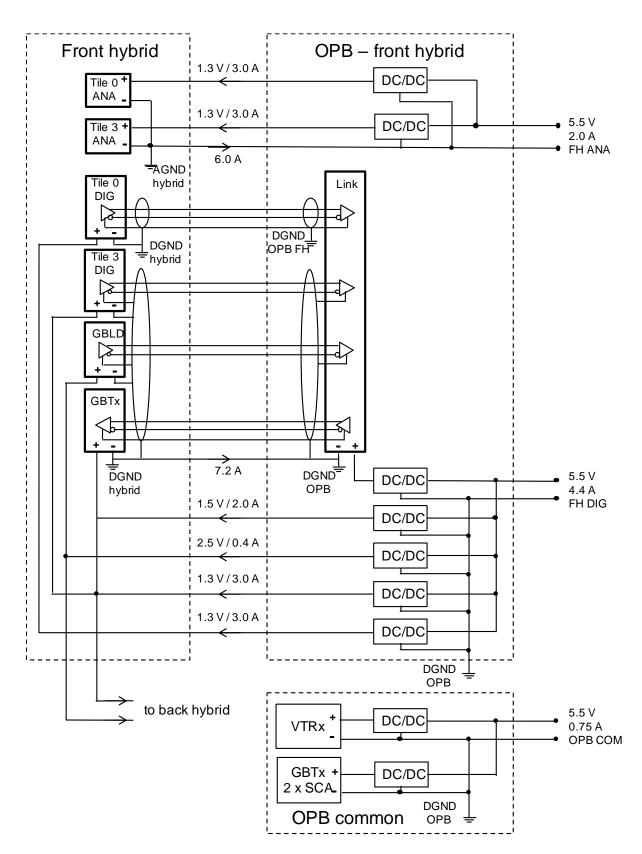

| Figure 3: Grounding and powering scheme of the front hybrid and the electronics on the OPB related to the front hybrid. The figure also includes the common electronics on the OPB                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

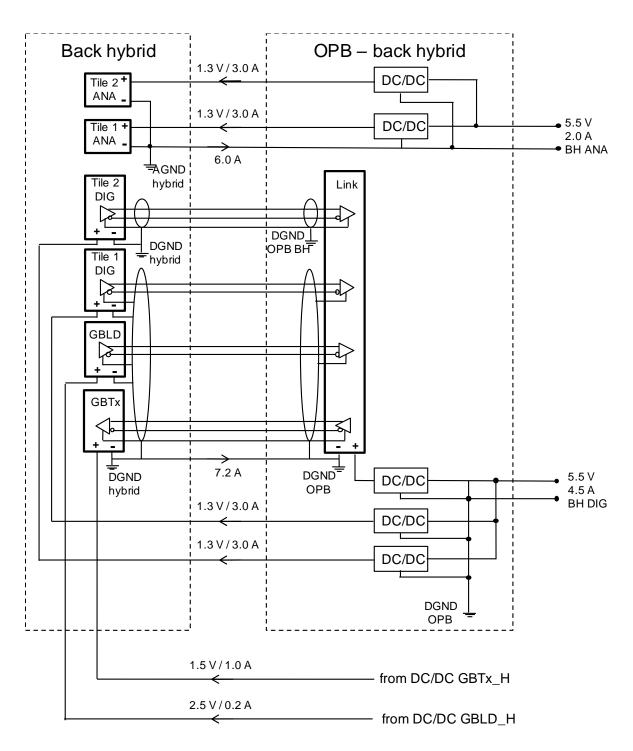

| Figure 4: Grounding and powering scheme for the back hybrid and the electronics on the OPB related to the back hybrid5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 5: Illustration of the voltage dividers used to bring the analogue voltages into the range of the ADC in the GBT-SCA (0 - 1 V) Two channels are used since the ground reference is not the same as that of the ADC7                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 6: Voltage divider internal to the VeloPix ASIC [22] providing the two voltages per<br>supply that are multiplexed out for voltage monitoring9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 7: Voltage divider to monitor current proportional to the received optical power (I <sub>RSSI</sub> ). The schematic shows its connection to the ADC on the GBT-SCA [13,14] 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 8: Schematic (left) and layout of the CTLE circuit for the data (middle) and control (right) links, as implemented on the OPB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

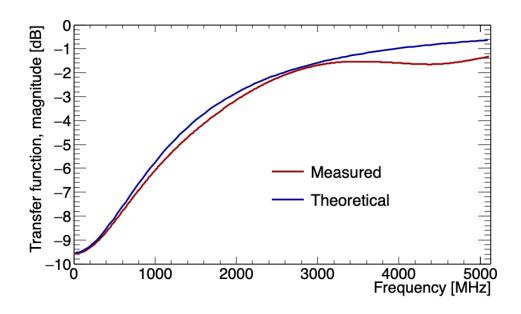

| Figure 9: Transfer function of the CTLE circuit on the OPB, magnitude in dB versus frequency, with the component values for the data links given in Table 15. The blue curve gives the theoretical transfer functions, and the red curves gives the transfer function measured on a prototype circuit                                                                                                                                                                                                                                                                                                                                                          |

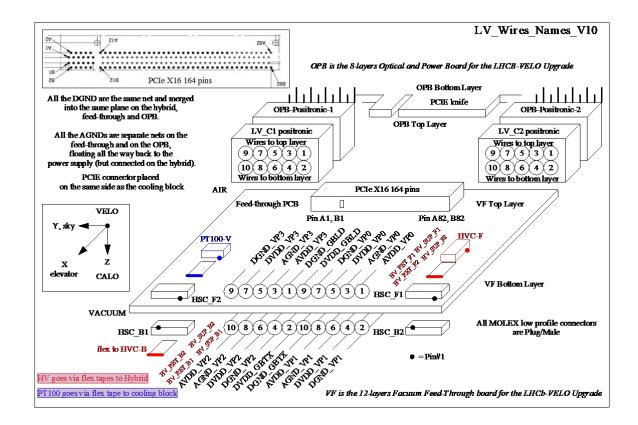

| Figure 10: 3D view of the connectors on the production vacuum feedthrough with signal names20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

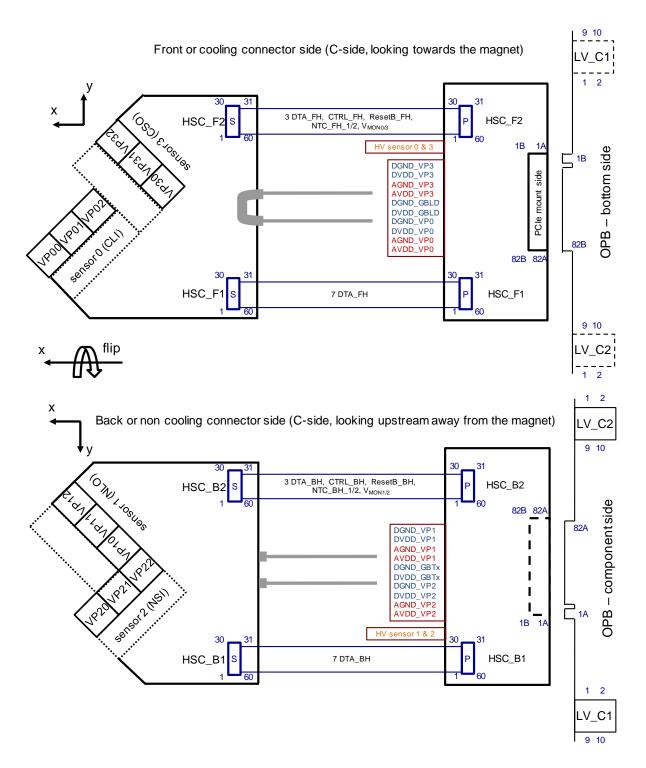

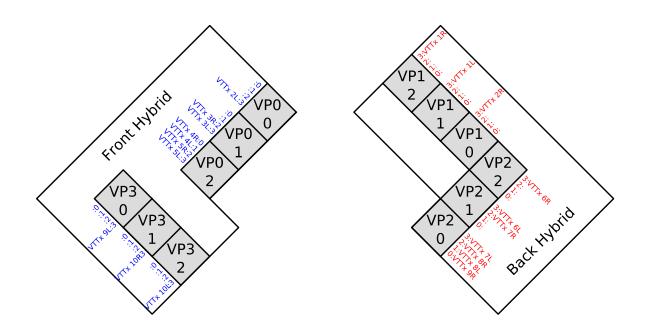

| Figure 11: Overview of the detector module, cables and feedthrough for the production boards, defining sensor numbers, VeloPix numbers and connector orientations. The letters P and S stand for plug and socket, which defines the connector gender on the PCBs with pin numbers as indicated. The hybrids on the modules are implemented as three separate flex circuits to reduce the mechanical stresses that arise from differences in thermal expansion coefficients                                                                                                                                                                                     |

# List of Tables

- Table 7: Connections for the VTRx o/e transceiver that is connected to the GBTx located on the OPB.

10

| Table 11: Connections for the second set of VTTx optical transmitters reading out the two<br>tiles close to the 'short' edge of the module. The common connections are given in<br>Table 9                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 12: Connections for the two GBLD ASICs driving the signals between the VTRx on the OPB and the GBTx on the hybrid. The components are labelled _FH or _BH depending on if they are driving signals for the front or back hybrid                                                                                |

| Table 13: Connections to the two GBT-SCA ASICs on the OPB, omitting the GPIO, ADC,         I <sup>2</sup> C and power connections.         16                                                                                                                                                                        |

| Table 14: Connections to the GBTx on the OPB, omitting power connections17                                                                                                                                                                                                                                           |

| Table 15: Values for the CTLE components and the parameters of the filter                                                                                                                                                                                                                                            |

| Table 16: Pin-out for the 16x PCIe on the OPB interfacing the feedthrough22                                                                                                                                                                                                                                          |

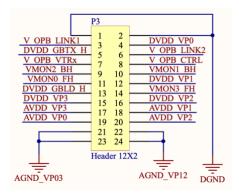

| Table 17: Pin-out of LV connectors facing the vacuum feedthrough on the production boards                                                                                                                                                                                                                            |

| Table 18: Pin-out of the front (cooling connector) side high-speed connectors close to the'long' edge of the module (HSC_F1) for the production boards. All non-listed pins areconnected to GND                                                                                                                      |

| Table 19: Pin-out of the front (cooling connector) side high-speed connector close to the<br>'short' edge of the module (HSC_F2) for the production boards. All non-listed pins are<br>connected to GND. NB: CTRL_UP has a logic inversion due to routing constraints<br>(corrected for in the firmware)             |

| Table 20: Pin-out of the back (non-cooling connector) side high-speed connector close to the 'short' edge of the module (HSC_B1) for the production boards. All non-listed pins are connected to GND. NB: all data lines have a logic inversion due to routing constraints (corrected for in the firmware)           |

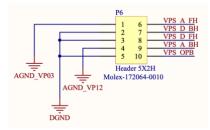

| Table 21: Pin-out of the back (non-cooling connector) side high-speed connector close to the 'long' edge of the module (HSC_B2) on the production boards. All non-listed pins are connected to GND. NB: all data lines and CTRL_UP have a logic inversion due to routing constraints (corrected for in the firmware) |

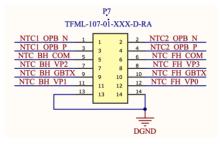

| Table 22: Pin-out of the power supply connector for the production OPB, Molex 172064-0010                                                                                                                                                                                                                            |

| Table 23: Pin-out of the front-panel connector for the temperature monitoring of the production OPB, Samtec TFM-107-01-L-D-RA                                                                                                                                                                                        |

| Table 24: Pin-out of the on-PCB monitoring connector for the supply voltages for the production OPB.       27                                                                                                                                                                                                        |

| Table 25: Pin-out of the on-PCB monitoring connector for the temperature (NTC) signals,DC/DC output voltages and hybrid monitoring voltages for the production OPB.27                                                                                                                                                |

Table 26: Pin-out of the E-Fuse programming connector, compatible with the USB programming dongle.

28

# 1 Introduction

This document describes the functionality of the optical and power board (OPB) for the VELO upgrade [1], used in the first upgrade of the LHCb Experiment [2] which is installed in the second long LHC shutdown 2018-2021. The OPBs are part of the on-detector electronics system of the VELO and they are the interface between the detector modules located inside the detector vacuum and the off-detector electronics located at 60 m cable distance. They interface the off-detector electronics in two ways. The control, trigger and DAQ systems are interfaced via optical fibres, and the low voltage power supplies and temperature monitoring system via copper cables. The document also gives and overview of the VELO on-detector electronics and gives some details of the other parts of that system.

Section 1.1 gives a general overview of the board and Sections 2 to 6 describes each functional block in detail. The principal design of the parts is illustrated with diagrams and the connectivity of all the components, mainly in tables. Section 7 describes the CTLE equalisation of the high-speed link and Section 8 gives the pin-out of all the connectors of the board. The schematics and design files for the OPB can be found in Ref. [3].

### 1.1 Optical and power board overview

The optical and power boards (OPBs) are located immediately outside the VELO detector vacuum, placed in custom crates mounted on the vacuum tank. They provide the following functionality:

- Electrical to optical conversion for the data sent from the detector module;

- Electrical to optical conversion of the timing, trigger and fast control signals;

- Electrical to optical conversion of the control signals for the components of the OPB;

- DC/DC conversion of the supply voltages for the hybrids and OPB itself;

- Monitoring of the supplied voltages on the OPB and detector module;

- Routing of the temperature monitoring signals (NTCs) from the detector module and the OPB.

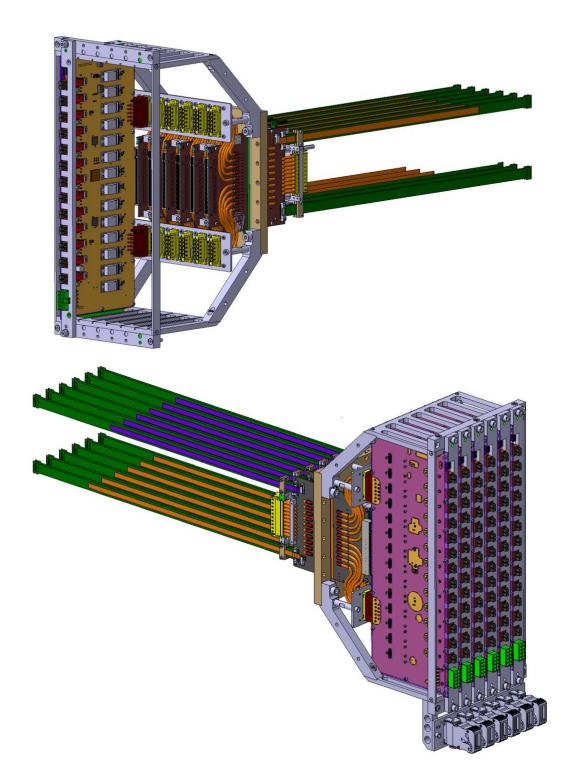

Each OPB services the front-end hybrid circuits that are attached on the two sides of a VELO detector module. It communicates with the control interface boards (SOL40) [4,5] through three bidirectional optical links and transmits the data to the DAQ boards (TELL40) [5,6] through 20 optical links. It is supplied by five low voltage power supply channels, each with a voltage of  $6 - 9 V^1$ . A schematic overview of the on-detector parts of VELO detector is shown in Figure 1, and a schematic view of the VELO electronics and the OPB is shown in Figure 2.

Figure 1: Schematic view of the components of the VELO on-detector electronics.

<sup>&</sup>lt;sup>1</sup> The minimum is given by the minimal voltage required by the DC/DC converters to produce a reliable output. The maximum is given by the voltage dividers from the input voltage used for enable signals (absolute max 10 V).

Figure 2: Overview of the VELO Upgrade electronics showing the role and functionality of the OPB. The main components on the OPB and the hybrid are shown as boxes where the colours of the boxes and lines indicate the type of signal or supply it represents: dark blue indicate the 5.12 Gbit/s data links; dark green indicate the 4.8 Gbit/s control links; light blue (or turquoise) indicate slower control signals, either 40 MHz clock and control, I<sup>2</sup>C configuration or logical signals; red indicate low voltage supply; magenta indicate high voltage supply; and brown indicate analogue voltage or temperature monitoring signals.

The OPBs are mounted in custom crates on the VELO vacuum tank where the vacuum feedthrough are placed at the back of the crate. The data and control signals are transmitted to the front-end hybrids through flexible high-speed data tapes and the low voltage is supplied on separate cables. The high voltage supply is not routed through the OPB, it is connected directly to the same vacuum feedthrough and routed on separate cables to the detector module. There are additional temperature monitoring signals for the cooling system that are routed through separate cables as well.

The three bidirectional optical control links are received by VTRx transceivers [7-9] operating at 4.8 Gbits/s. One link is connected to a GBTx ASIC [10-12] that provides the local control of the OPB, through the two slow control adaptor ASICs (GBT-SCA) [13,14]. These SCA ASICs provide the I<sup>2</sup>C buses to configure the laser drivers (GBLD) [15-17] on the VTTx and VTRx modules and the logical I/O signals required for the DC/DC converters [18-21]. The other two control links are connected to the two front-end hybrids. As the VTRx transceiver is not designed to drive the signals to a remote GBTx (located on the detector module) the signals are driven by the GBLD ASICs [15-17].

The 20 high-speed data links are routed from the backplane (PCIe) connector to the 10 VTTx optical transmitter modules mounted on the OPB [7-9].

The ten voltages needed for the front-end hybrids on one module are provided by separate DC/DC converters, one analogue and one digital voltage for each of the four tiles and voltages for the GBTx and GBLD that are shared between the two sides of the module. The OPB itself require four voltages that are provided by DC/DC converters. Five LV supply channels are needed to power the system. Analogue power is supplied on separate channels for the front and back hybrids. The digital voltages of each hybrid share a power supply channel with the electronics on the OPB that are mostly associated with that side of the module. The electronics on the OPB is not strictly divided between the front and back side of the module due to routing constraints. The control electronics for the OPB itself, that is required to be always on to communicate with the board, is supplied from a separate OPB input LV channel.

# 2 LV supply and monitoring

### 2.1 Grounding and powering scheme of the production OPB

The input voltage to the OPB is 6-9 V, which is given by the minimum input voltage required by the DC/DC converters [18-20] and the maximum tolerated by the inputs fed from voltage dividers derived from the supply voltage. There are four DC/DC converters providing the voltages for the OPB and eight DC/DC converters used to supply the voltages for the VeloPix ASICs, and two DC/DC converters that the supply voltages for the GBTx [10-12] and GBLD [15-17] on the hybrid shared between the two sides of the module. The powering schemes of the front and back hybrids are shown in Figure 3 and Figure 4.

DC/DC converters that are supplied from the same LV channel have the same ground reference even though they regulate independent output voltages. Moreover, the distance between the DC/DC converters and the hybrid implies that there is a non-zero impedance in the supply line. These two facts are important considerations when defining the grounding and powering scheme.

The analogue VeloPix [22-23] voltages are supplied through separate LV channels for the front and back side hybrids with no ground reference on the OPB. This ensures that the analogue return currents from the two hybrids are separate and not mixed with the digital return current.

The digital grounds on the hybrid and the OPB have to be firmly linked since the shield ground planes on the high-speed links have to be connected to digital grounds of both the sender and receiver. Hence the digital supply voltages of the hybrid and the electronics on the OPB associated to that hybrid are provided by the same LV channel. The remaining electronics that do the local control of the OPB is powered from a separate LV supply channel. There is only one digital ground on the OPB, common to these three supply channels. The DC/DC converters, the maximal current consumption of the components they supply, and their supply voltages are summarised in Table 1.

The analogue and digital grounds of all the supplies are linked on the on the module, from both sides of the module. There is a shield ground on the OPB that is linked to the crate and the mechanical structure, that can be connected to the OPB digital ground through a resistor, capacitor or inductor. This defines the ground reference for the different LV supply channels on the OPB.

| Powering components               | Supply                     | V [V] | I <sub>max</sub> [A]    | DC/DC converter |

|-----------------------------------|----------------------------|-------|-------------------------|-----------------|

| VTRx_OPB                          | OPB                        | 2.5   | 0.3                     | DCDC_OPB_VTRx   |

| GBTx_OPB, SCA_OPB_1, SCA_OPB_2    | common                     | 1.5   | $1 + 2 \ge 0.3$         | DCDC_OPB_CTRL   |

| VTRx_FH, GBLD_FH, VTTx_5 – VTTx_8 |                            | 2.5   | $0.3 + 0.2 + 5 \ge 0.4$ | DCDC_OPB_LINK2  |

| GBTx on both hybrids              | DIG front                  | 1.5   | 2 x 1                   | DCDC_GBTx_H     |

| GBLD on both hybrids              | hybrid                     | 2.5   | 2 x 0.2                 | DCDC_GBLD_H     |

| Tile 0 front hybrid digital       | nyona                      | 1.3   | 3 x 1                   | DCDC_VPD0       |

| Tile 3 front hybrid digital       |                            | 1.3   | 3 x 1                   | DCDC_VPD3       |

| VTRx_BH, GBLD_BH, VTTx_1 – VTTx_4 | DIC healt                  | 2.5   | $0.3 + 0.2 + 5 \ge 0.4$ | DCDC_OPB_LINK1  |

| Tile 2 back hybrid digital        | DIG back 1.3<br>hybrid 1.2 |       | 3 x 1                   | DCDC_VPD2       |

| Tile 1 back hybrid digital        | nybrid                     | 1.3   | 3 x 1                   | DCDC_VPD1       |

| Tile 0 front hybrid analogue      | ANA front                  | 1.3   | 3 x 1                   | DCDC_VPA0       |

| Tile 3 front hybrid analogue      | hybrid                     | 1.3   | 3 x 1                   | DCDC_VPA3       |

| Tile 2 back hybrid analogue       | ANA back                   | 1.3   | 3 x 1                   | DCDC_VPA2       |

| Tile 1 back hybrid analogue       | hybrid                     | 1.3   | 3 x 1                   | DCDC_VPA1       |

Table 1: Summary of the active components indicating which DC/DC converter that supplies them, with upper limits of their current consumption. The table also indicate which LV PS channel that supplies each DC/DC converter.

Figure 3: Grounding and powering scheme of the front hybrid and the electronics on the OPB related to the front hybrid. The figure also includes the common electronics on the OPB.

Figure 4: Grounding and powering scheme for the back hybrid and the electronics on the OPB related to the back hybrid.

### 2.2 Power dissipation estimates

The power dissipation estimates of the detector module and the OPB are shown in Table 2. These estimates are based on the maximum values given in the data sheets of the components and hence are upper limits used for the design of the system. The estimated power dissipation on the OPB includes the losses in the DC/DC converters, where the assumed efficiencies vary between 0.70 and 0.85 depending on the output voltage and current as specified in the data sheet.

A fully configured OPB and detector module were measured in systems tests during the production phase, which gave a power consumption of 26 W for the detector module and 14 W for the OPB. This is significantly lower than the 35 W and 34 W estimated in Table 2 and provides a good operational margin for the system. The power consumption is expected to increase with increased occupancy during operation, hence this margin is necessary.

Table 2: Power dissipation estimates, where the values in the columns correspond to the dissipation on the detector module, the OPB and in total. The dissipation estimates are split by power supply channel and summed up for the module, the detector half and the full VELO. This is assuming 6.0 V input voltages to the OPB, maximal current consumption for all components (as given in Table 1) and the DC/DC conversion efficiencies from the datasheet.

| Supply voltage (6.0 V) | I [A] | P module [W] | P OPB [W] | P total [W] |

|------------------------|-------|--------------|-----------|-------------|

| OPB common             | 0.66  | 0            | 4.0       | 4.0         |

| Front hybrid digital   | 4.0   | 12           | 12        | 24          |

| Front hybrid analogue  | 1.9   | 7.8          | 3.3       | 11          |

| Back hybrid digital    | 3.1   | 7.8          | 11        | 19          |

| Back hybrid analogue   | 1.9   | 7.8          | 3.3       | 11          |

|                        |       |              |           |             |

| Total (one module)     |       | 35           | 34        | 69          |

| Total (detector half)  |       | 915          | 875       | 1790        |

| Total (VELO)           |       | 1830         | 1750      | 3580        |

### 2.3 LV supply and cable requirements

The low voltage power supplies are located in D3 which is approximately 60 m cable distance from the detector. Each OPB is supplied with five voltages with the specifications given in Table 2, adding up to a total of 260 power supply channels for the whole VELO. The voltage supplies are regulated to compensate for the voltage drops in the cables. Table 3 shows the requirements of the power supply channels using an estimate of the cabling. The output capacity of each LV channel for the EASY A3009 supplies used for the current VELO are  $I_{max} = 9$  A,  $V_{max} = 8$  V and  $P_{max} = 45$  W.

Table 3: Voltage, current and power requirements on the LV power supplies. These estimates are based on the planned LV cabling as detailed in Ref [24] and assumes a 6.0 V input voltage to the OPB.

| Supply voltage (6.0 V) | Cable cross              | Cable      | Voltage | Cable  | PS output | PS output |

|------------------------|--------------------------|------------|---------|--------|-----------|-----------|

|                        | section                  | resistance | drop    | power  | voltage   | power     |

| OPB common             | 2/10/2.5 mm <sup>2</sup> | 0.40 Ω     | 0.26 V  | 0.17 W | 6.3 V     | 4.1 W     |

| Front hybrid digital   | 3/10/2.5 mm <sup>2</sup> | 0.36 Ω     | 1.43 V  | 5.7 W  | 7.4 V     | 30 W      |

| Front hybrid analogue  | 3/10/2.5 mm <sup>2</sup> | 0.36 Ω     | 0.67 V  | 1.3 W  | 6.7 V     | 12 W      |

| Back hybrid digital    | 3/10/2.5 mm <sup>2</sup> | 0.36 Ω     | 1.13 V  | 3.5 W  | 7.1 V     | 22 W      |

| Back hybrid analogue   | 3/10/2.5 mm <sup>2</sup> | 0.36 Ω     | 0.67 V  | 1.3 W  | 6.7 V     | 12 W      |

|                        |                          |            |         |        |           |           |

| Total (one module)     |                          |            |         | 12 W   |           | 81 W      |

| Total (VELO)           |                          |            |         | 616 W  |           | 4200 W    |

The DC/DC converters regulate the voltage at their output on the OPB, hence the voltage supplied to the hybrid will be reduced by the voltage drop over the cables in the vacuum. The minimum required surface area of these cables and the estimated voltage drops are given in Table 4.

Table 4: Voltage drops and dissipated power over the cable through the VELO vacuum. The estimated voltage drops assume 10 m $\Omega$  for the cables and 2 m $\Omega$  each for the OPB, feedthrough and hybrid, including contact resistances. The estimated resistances are consistent with but slightly larger than the measured values of the prototype system.

| Supply voltage      | Output<br>voltage | Current | Total resistance | Voltage<br>drop | Cable<br>power | Supplied voltage |

|---------------------|-------------------|---------|------------------|-----------------|----------------|------------------|

| VeloPix DIG 0/2     | 1.3 V             | 3.0 A   | 16 mΩ            | 47 mV           | 86 mW          | 1.21 V           |

| VeloPix DIG 1/3     | 1.3 V             | 3.0 A   | 16 mΩ            | 47 mV           | 86 mW          | 1.21 V           |

| 2 x GBTx            | 1.5 V             | 2 A     | 13 mΩ            | 25 mV           | 27 mW          | 1.43 V           |

| 2 x GBLD            | 2.5 V             | 0.4 A   | 13 mΩ            | 5 mV            | 1 mW           | 2.45 V           |

| Digital return      | N/A               | 7.2 A   | 6 mΩ             | 6 mV            | 165 mW         | N/A              |

|                     |                   |         |                  |                 |                |                  |

| VeloPix ANA 0/2     | 1.3 V             | 3.0 A   | 16 mΩ            | 47 mV           | 86 mW          | 1.21 V           |

| VeloPix ANA 1/3     | 1.3 V             | 3.0 A   | 16 mΩ            | 47 mV           | 86 mW          | 1.21 V           |

| Analogue return     | N/A               | 6.0 A   | 16 mΩ            | 47 mV           | 86 mW          | N/A              |

|                     |                   |         |                  |                 |                |                  |

| Total per hybrid    |                   | 26.4 A  |                  |                 | 0.71 W         |                  |

| Total per module    |                   | 52.8 A  |                  |                 | 1.42 W         |                  |

| Total per VELO half |                   | 1373 A  |                  |                 | 37 W           |                  |

### 2.4 DC/DC converter implementation

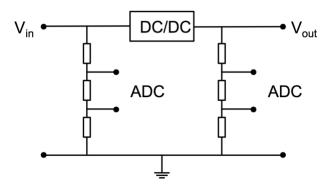

The common connections for the DC/DC converters are given in Table 5 and the specific connections for the individual converters are given in Table 6. The ADC of the GBT-SCA [13,14] is referenced to the digital ground of the OPB which may be at a small DC offset compared to the analogue grounds on the OPB due to the voltage drop over the cables between the OPB and the hybrid. Hence, two ADC channels are used to monitor voltage and ground of the analogue DC/DC converter, for both the input and output voltages. These voltages are divided down to match the range of the GBT-SCA ADC, as illustrated in Figure 5. The digital voltages are referenced to the same ground as the GBT-SCA and hence divided down to the ADC range and monitored by a single channel.

Figure 5: Illustration of the voltage dividers used to bring the analogue voltages into the range of the ADC in the GBT-SCA (0 - 1 V) Two channels are used since the ground reference is not the same as that of the ADC.

| 1            | 1 0   |

|--------------|-------|

| DCDC convert | er    |

| Pin          | Name  |

| 12           | En    |

| 1            | PGood |

| 7-11, 18-22  | Vout  |

| 2 3 13 14    | Vin   |

|   | 2, 5, 15, 14 | V III |  |

|---|--------------|-------|--|

|   |              |       |  |

|   |              |       |  |

|   |              |       |  |

| I | 7 11 10 00   | Vant  |  |

|   | 7-11, 18-22  | Vout  |  |

|   | 4-6, 15-17   | GND   |  |

|   | + 0, 15 17   | UND   |  |

Vin

2, 3, 13, 14

| SCA_OPB_FH, SCA_OPB_BH      |

|-----------------------------|

| Name                        |

| GPIO_pad <k></k>            |

| GPIO_pad <l></l>            |

| ADC_in_pad <m>, <n></n></m> |

| ADC_in_pad, <q></q>         |

| Power connections |

|-------------------|

| OPB/Hybrid power  |

| GND               |

| LV PS connector   |

Table 6: Overview of DC/DC converters on the production OPB listing the output voltage and maximum output current, the LV PS channel and its specific connections to the GBT-SCA. The enable signals for DCDC\_OPB\_VTRx and DCDC\_OPB\_CTRL are also connected via jumpers to the E-Fuse programming connector pins 8 and 6 respectively to enable power cycling during programming.

| DC/DC name     | V <sub>out</sub> | T [A]                | LV PS                | SCA_X: GPIO channel |            | SCA_X: ADC channel |                  |

|----------------|------------------|----------------------|----------------------|---------------------|------------|--------------------|------------------|

| DC/DC name     | [V]              | I <sub>max</sub> [A] | channel              | En                  | PGood      | Vin                | V <sub>out</sub> |

| DCDC_VPA0      | 1.3              | 3                    | ELL ANIA             | 1:7                 | 1:16       | 2.1.2              | 1:5,6            |

| DCDC_VPA3      | 1.3              | 3                    | FH ANA               | 2:8                 | 2:16       | 2:1,2              | 2:8,9            |

| DCDC_VPD0      | 1.3              | 3                    |                      | 1:7                 | 1:18       |                    | 1:4              |

| DCDC_VPD3      | 1.3              | 3                    | FH DIG               | 2:8                 | 2:18       | 2:3                | 2:4              |

| DCDC_GBTX_H    | 1.5              | 2                    |                      | 1:9                 | 1:20       |                    | 1:11             |

| DCDC_GBLD_H    | 2.5              | 0.4                  |                      | 1:11                | 1:21       |                    | 1:12             |

| DCDC_OPB_LINK2 | 2.5              | 2.5                  |                      | 2:12                | 2:15       |                    | 2:10             |

|                |                  |                      |                      |                     |            |                    |                  |

|                |                  | SCA_X GPIO           | O channel SCA_X: ADC |                     | DC channel |                    |                  |

|                |                  |                      |                      | En                  | PGood      | Vin                | V <sub>out</sub> |

| DCDC VDA1      | 1.2              | 2                    |                      | 1.9                 | 1.10       |                    | 1.0.0            |

|                |     |     |        | En   | PGood | V <sub>in</sub> | V <sub>out</sub> |

|----------------|-----|-----|--------|------|-------|-----------------|------------------|

| DCDC_VPA1      | 1.3 | 3   | BH ANA | 1:8  | 1:19  | 1.1.2           | 1:8,9            |

| DCDC_VPA2      | 1.3 | 3   | DI ANA | 2:7  | 2:19  | 1:1,2           | 2:5,6            |

| DCDC_VPD1      | 1.3 | 3   |        | 1:8  | 1:17  |                 | 1:7              |

| DCDC_VPD2      | 1.3 | 3   | BH DIG | 2:7  | 2:17  | 1:3             | 2:7              |

| DCDC_OPB_LINK1 | 2.5 | 2.4 |        | 1:10 | 1:15  |                 | 1:10             |

|                |     |     |        |      |       |                 |                  |

|               |     |     |     | SCA_FH GPI | C     | SCA_FH A        | DC               |

|---------------|-----|-----|-----|------------|-------|-----------------|------------------|

|               |     |     |     | En         | PGood | V <sub>in</sub> | V <sub>out</sub> |

| DCDC_OPB_VTRx | 2.5 | 0.3 | OPB | N/A        | 1:24  | 1:0             | 1:13             |

| DCDC_OPB_CTRL | 1.5 | 1.6 | COM | N/A        | 1:25  | 1.0             | 1:14             |

Table 5: Connections for the DC/DC converters supplying the OPB and the hybrids. The specific connection pads, labelled k, l, m, n, p and q are given in Table 6.

### 2.5 Monitoring of the VeloPix voltages

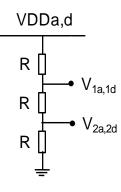

The voltages supplied to the VeloPix ASICs [22] are monitored through a circuit implemented in the VeloPix ASIC. The analogue and digital supply voltages to each VeloPix ASIC are divided across the resistor bridge shown in Figure 6, giving the voltages  $V_{1a,1d}$  and  $V_{2a,2d}$ . The four voltages from each VeloPix ASIC are routed through an analogue multiplexer to an output pad that can be configured to be in either high-impedance mode or provide a voltage output. The voltage monitoring pads for all the VeloPix ASICs for one tile are connected to a bus line that is routed out to the OPB. These four lines are connected to the SCA ADC (tile 0: SCA\_2 ADC<27>, tile 1: SCA\_1 ADC<27>, tile 2: SCA\_1 ACD<28> & tile 3: SCA\_2 ADC<28>) which gives access to the all the supply voltages on the hybrids by appropriately configuring the analogue multiplexers in the VeloPix ASICs. Assuming that the three resistors are identical, the ground and supply voltages can be calculated from

| VDD <sub>a, d</sub>       | $= 2 \ x \ V_{1a, \ 1d} - V_{2a, \ 2d,}$ |

|---------------------------|------------------------------------------|

| GND                       | $= 2 \ x \ V_{2a, \ 2d} - V_{1a, \ 1d,}$ |

| VDD <sub>a, d</sub> – GND | $= 3 x (V_{1a, 1d} - V_{2a, 2d}).$       |

The analogue multiplexer also provides access to the outputs of the internal DAC in the VeloPix ASIC, which can be used to monitor their performance. These voltages are read out through the same ADCs on the SCA that are used for the supply voltage monitoring and are accessed by selecting the appropriate input for the analogue multiplexer. See the VeloPix operations manual for details [23].

Figure 6: Voltage divider internal to the VeloPix ASIC [22] providing the two voltages per supply that are multiplexed out for voltage monitoring.

# 3 The versatile transceiver (VTRx) implementation

There are three versatile transceivers on the OPB, one for the local control of the OPB described in Section 3.1 and two for the control of the detector module described in Section 3.2.

### 3.1 The versatile transceiver for the OPB control signals

The electro-optical transceiver used for the control of the OPB (VTRx\_OPB) [7-9] is connected to the GBTx [10-12] located on the OPB (GBTx\_OPB) which together with the GBT-SCA [13-14] provide the signals necessary to configure and monitor the OPB. The connections of this VTRx are given in Table 7.

| VTRx_C | )PB  | Comment      | GBTx_OPB |     |

|--------|------|--------------|----------|-----|

| Pin    | Name |              | Name     | Pin |

|        |      | N/C          | LDRST    | J7  |

| 5      | SCL  | 1.5V pull-up | LDSCL    | K8  |

| 4      | SDA  | 1.5V pull-up | LDSDA    | H8  |

| 12     | RD+  |              | RXINP    | T1  |

| 13     | RD-  |              | RXINN    | U1  |

| 18     | TD+  |              | TXOUTP   | E1  |

| 19     | TD-  |              | TXOUTN   | D1  |

Table 7: Connections for the VTRx o/e transceiver that is connected to the GBTx located on the OPB.

|   |      |                                | SCA_1      |          |

|---|------|--------------------------------|------------|----------|

|   |      |                                | Name       | Pin      |

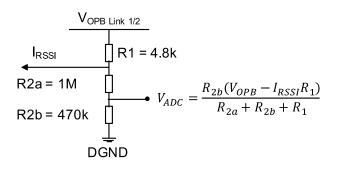

| 8 | RSSI | Connected as shown in Figure 7 | ADC_in_pao | d<26> N5 |

|          |                  | Power connections |

|----------|------------------|-------------------|

| 3        | Tx_Disable       | GND               |

| 6        | Mod_ABS          | GND               |

| 15       | V <sub>CCR</sub> | 2.5 V supply from |

| 16       | V <sub>CCT</sub> | DCDC_OPB_VTRx     |

| 10,11,14 | V <sub>EER</sub> | GND               |

| 1,17,20  | V <sub>EET</sub> | GND               |

| 2,7,9    | N/C              | N/C               |

Figure 7: Voltage divider to monitor current proportional to the received optical power ( $I_{RSSI}$ ). The schematic shows its connection to the ADC on the GBT-SCA [13,14].

### 3.2 The versatile transceivers for the detector module control signals

The OPB has one versatile transceiver [7-9] for each hybrid it provides signals for, labelled VTRx\_FH and VTRx\_BH for the front and back hybrids. These two VTRx are connected to the SCA\_1, SCA\_2, GBLD\_FH, GBLD\_BH, the high-speed hybrid connector and power as specified in Table 8. The two component names (\_FH and \_BH) and the two pin numbers correspond to the two different optical transceivers supplying the two hybrids.

Table 8: Connections for the VTRx transmitting the signals for the two front-end hybrids. The SCA\_FH (SCA\_BH) and GBLD\_FH (GBLD\_BH) are connected to the VTRx transmitting the signals for the front (back) hybrid.

| VTRx_FH, V | VTRx_BH | Comment | SCA_2(FH), SCA_1 (BH) |     |

|------------|---------|---------|-----------------------|-----|

| Pin        | Name    |         | Name                  | Pin |

|            |         |         |                       |     |

| 5 | SCL        | 1.5V pull-up                   | SCL_pad<14>    | L3  |

|---|------------|--------------------------------|----------------|-----|

| 4 | SDA        | 1.5V pull-up                   | SDA_pad<14>    | L2  |

| 3 | Tx_Disable |                                | GPIO_pad<0>    | B13 |

| 8 | RSSI       | Connected as shown in Figure 7 | ADC_in_pad<25> | M5  |

|            |                  |            | Power connections                 |

|------------|------------------|------------|-----------------------------------|

| 6          | Mod_ABS          |            | GND                               |

| 15         | V <sub>CCR</sub> | Decoupling | 2.5 V supply from DCDC ODD LINK   |

| 16         | V <sub>CCT</sub> | Decoupling | - 2.5 V supply from DCDC_OPB_LINK |

| 10, 11, 14 | V <sub>EER</sub> |            | - GND                             |

| 1, 17, 20  | V <sub>EET</sub> |            | UND                               |

| 2, 7, 9    | N/C              |            | N/C                               |

|    |     | GBLD | FH, GBLD_BH |

|----|-----|------|-------------|

|    |     | Name | Pin         |

| 12 | RD+ | DIN+ | 10          |

| 13 | RD- | DIN- | 9           |

|    |     |                       | PCIe connector      |          |

|----|-----|-----------------------|---------------------|----------|

|    |     |                       | Name                | Pin      |

| 18 | TD+ | VFT con: F2-50, B2-50 | CTRL_UP_FH_P, _BH_P | A25, A68 |

| 19 | TD- | VFT con: F2-49, B2-49 | CTRL_UP_FH_N, _BH_N | A24, A69 |

# 4 The versatile twin transmitter (VTTx) implementation

The OPB supports 20 data links converted to optical signals by 10 VTTx optical transmitters [7-9]. The common pin connections of the VTTx modules are given in Table 9, the specific connections for each VTTx are given in Table 10 and Table 11 for the 20 optical transmitters on the OPB.

Table 9: Common connections for the 10 VTTx optical transmitters on the OPB. The pin connections differ between the individual VTTx are given in Table 10 and Table 11.

| VTTx_N connection     |                   | Comment    | Common connections           |

|-----------------------|-------------------|------------|------------------------------|

| Pin                   | Name              |            | Name                         |

| 6                     | Mod_ABS           |            | GND                          |

| 16                    | V <sub>CCT</sub>  | Decoupling | 2.5 V from DCDC OPB LINK1/2  |

| 15                    | V <sub>CCT2</sub> | Decoupling | 2.3 V HOIII DCDC_OFB_LINK1/2 |

| 1, 10, 11, 14, 17, 20 | V <sub>EET</sub>  |            | GND                          |

| 2,8                   | N/C               |            | N/C                          |

Table 10: Connections for the first set of VTTx optical transmitters reading out the two tiles close to the 'long' edge of the module. The common connections are given in Table 9.

| Optical tr      | ansmitter | (VTTx_N)   | Signal name or  | PCIe or SCA_1 | Hybrid pin | Feedthrough pin |

|-----------------|-----------|------------|-----------------|---------------|------------|-----------------|

| Number Pin Name |           |            | SCA_1 input pad | pin           |            |                 |

|                 |           |            |                 |               | HSC_B2     |                 |

|                 | 18        | TD1+       | DTA_VP113_N     | A77           | 24         | 37              |

|                 | 19        | TD1-       | DTA_VP113_P     | A76           | 23         | 38              |

|                 | 12        | TD2+       | DTA_VP123_N     | B79           | 28         | 33              |

|                 | 13        | TD2-       | DTA_VP123_P     | B78           | 27         | 34              |

| 1               | 5         | SCL        | SCL_pad<1>      | C2            |            |                 |

|                 | 4         | SDA        | SDA_pad<1>      | C1            |            |                 |

|                 | 7         | SCL2       | SCL_pad<2>      | D2            |            |                 |

|                 | 9         | SDA2       | SDA_pad<2>      | D1            |            |                 |

|                 | 3         | Tx_Disable | GPIO_pad<1>     | A13           | HSC_B2 / H | ISC_F1          |

|                 | 18        | TD1+       | DTA_VP003_P     | A73           | 3          | 58              |

|                 | 19        | TD1-       | DTA_VP003_N     | A72           | 4          | 57              |

|                 | 12        | TD2+       | DTA_VP103_N     | B75           | 20         | 41              |

|                 | 13        | TD2-       | DTA_VP103_P     | B74           | 19         | 42              |

| 2               | 5         | SCL        | SCL_pad<3>      | E2            |            |                 |

|                 | 4         | SDA        | SDA_pad<3>      | E1            |            |                 |

|                 | 7         | SCL2       | SCL_pad<4>      | D3            |            |                 |

|                 | 9         | SDA2       | SDA_pad<4>      | C3            |            |                 |

|                 | 3         | Tx_Disable | GPIO_pad<2>     | B12           | HSC_F1     |                 |

|                 | 18        | TD1+       | DTA_VP013_P     | A55           | 11         | 50              |

|                 | 19        | TD1-       | DTA_VP013_N     | A54           | 12         | 49              |

|                 | 12        | TD2+       | DTA_VP012_P     | B57           | 7          | 54              |

|                 | 13        | TD2-       | DTA_VP012_N     | B56           | 8          | 53              |

| 3               | 5         | SCL        | SCL_pad<5>      | F2            |            |                 |

|                 | 4         | SDA        | SDA_pad<5>      | F1            |            |                 |

|                 | 7         | SCL2       | SCL_pad<6>      | F3            |            |                 |

|                 | 9         | SDA2       | SDA_pad<6>      | E3            |            |                 |

|                 | 3         | Tx_Disable | GPIO_pad<3>     | A12           | HSC_F1     |                 |

|                 | 18        | TD1+       | DTA_VP021_P     | A51           | 19         | 42              |

|                 | 19        | TD1-       | DTA_VP021_N     | A50           | 20         | 41              |

|                 | 12        | TD2+       | DTA_VP020_P     | B53           | 15         | 46              |

|                 | 13        | TD2-       | DTA_VP020_N     | B52           | 16         | 45              |

| 4               | 5         | SCL        | SCL_pad<7>      | G2            |            |                 |

|                 | 4         | SDA        | SDA_pad<7>      | G1            |            |                 |

|                 | 7         | SCL2       | SCL_pad<8>      | G4            |            |                 |

|                 | 9         | SDA2       | SDA_pad<8>      | G3            |            |                 |

|                 | 3         | Tx_Disable | GPIO_pad<4>     | C11           | HSC_F1     |                 |

|                 | 18        | TD1+       | DTA_VP023_P     | A47           | 27         | 34              |

|                 | 19        | TD1-       | DTA_VP023_N     | A46           | 28         | 33              |

|                 | 12        | TD2+       | DTA_VP022_P     | B49           | 23         | 38              |

|                 | 13        | TD2-       | DTA_VP022_N     | B48           | 24         | 37              |

| 5               | 5         | SCL        | SCL_pad<9>      | H2            | 4          |                 |

|                 | 4         | SDA        | SDA_pad<9>      | H1            | 4          |                 |

|                 | 7         | SCL2       | SCL_pad<10>     | H4            | 4          |                 |

|                 | 9         | SDA2       | SDA_pad<10>     | H3            | 4          |                 |

|                 | 3         | Tx_Disable | GPIO_pad<5>     | B11           |            |                 |

Table 11: Connections for the second set of VTTx optical transmitters reading out the two tiles close to the 'short' edge of the module. The common connections are given in Table 9.

| Optical tra | ansmit | ter (VTTx_N) | Signal name or  | PCIe or SCA_2 | Hashard Jacks | Foodthy         |

|-------------|--------|--------------|-----------------|---------------|---------------|-----------------|

| Number      | Pin    | Name         | SCA_2 input pad | pin           | Hybrid pin    | Feedthrough pin |

|             |        |              | A               |               | HSC_B1        |                 |

|             | 18     | TD+          | DTA_VP213_N     | A43           | 23            | 38              |

|             | 19     | TD-          | DTA_VP213_P     | A42           | 24            | 37              |

|             | 12     | TD2+         | DTA_VP223_N     | B45           | 27            | 34              |

|             | 13     | TD2-         | DTA_VP223_P     | B44           | 28            | 33              |

| 6           | 5      | SCL          | SCL_pad<1>      | C2            |               |                 |

|             | 4      | SDA          | SDA_pad<1>      | C1            |               |                 |

|             | 7      | SCL2         | SCL_pad<2>      | D2            |               |                 |

|             | 9      | SDA2         | SDA_pad<2>      | D1            |               |                 |

|             | 3      | Tx_Disable   | GPIO_pad<1>     | A13           | HSC_B1        |                 |

|             | 18     | TD+          | DTA_VP203_N     | A39           | 15            | 46              |

|             | 19     | TD-          | DTA_VP203_P     | A38           | 16            | 45              |

|             | 12     | TD2+         | DTA_VP212_N     | B41           | 19            | 42              |

|             | 13     | TD2-         | DTA_VP212_P     | B40           | 20            | 41              |

| 7           | 5      | SCL          | SCL_pad<3>      | E2            |               | ·               |

|             | 4      | SDA          | SDA_pad<3>      | E1            | 1             |                 |

|             | 7      | SCL2         | SCL_pad<4>      | D3            |               |                 |

|             | 9      | SDA2         | SDA_pad<4>      | C3            |               |                 |

|             | 3      | Tx_Disable   | GPIO_pad<2>     | B12           | HSC_B1        |                 |

|             | 18     | TD+          | DTA_VP201_N     | A35           | 7             | 54              |

|             | 19     | TD-          | DTA_VP201_P     | A34           | 8             | 53              |

|             | 12     | TD2+         | DTA_VP202_N     | B37           | 11            | 50              |

|             | 13     | TD2-         | DTA_VP202_P     | B36           | 12            | 49              |

| 8           | 5      | SCL          | SCL_pad<5>      | F2            |               |                 |

|             | 4      | SDA          | SDA_pad<5>      | F1            |               |                 |

|             | 7      | SCL2         | SCL_pad<6>      | F3            |               |                 |

|             | 9      | SDA2         | SDA_pad<6>      | E3            |               |                 |

|             | 3      | Tx_Disable   | GPIO_pad<3>     | A12           | HSC_F2 / HS   | C_B1            |

|             | 18     | TD+          | DTA_VP303_P     | B19           | 19            | 42              |

|             | 19     | TD-          | DTA_VP303_N     | B18           | 20            | 41              |

|             | 12     | TD2+         | DTA_VP200_N     | A21           | 3             | 58              |

|             | 13     | TD2-         | DTA_VP200_P     | A20           | 4             | 57              |

| 9           | 5      | SCL          | SCL_pad<7>      | G2            |               |                 |

|             | 4      | SDA          | SDA_pad<7>      | G1            | ]             |                 |

|             | 7      | SCL2         | SCL_pad<8>      | G4            |               |                 |

|             | 9      | SDA2         | SDA_pad<8>      | G3            |               |                 |

|             | 3      | Tx_Disable   | GPIO_pad<4>     | C11           | HSC_F2        |                 |

|             | 18     | TD+          | DTA_VP323_P     | B15           | 27            | 34              |

|             | 19     | TD-          | DTA_VP323_N     | B14           | 28            | 33              |

|             | 12     | TD2+         | DTA_VP313_P     | A17           | 23            | 38              |

|             | 13     | TD2-         | DTA_VP313_N     | A16           | 24            | 37              |

| 10          | 5      | SCL          | SCL_pad<9>      | H2            |               |                 |

|             | 4      | SDA          | SDA_pad<9>      | H1            |               |                 |

|             | 7      | SCL2         | SCL_pad<10>     | H4            |               |                 |

|             | 9      | SDA2         | SDA_pad<10>     | Н3            |               |                 |

|             | 3      | Tx_Disable   | GPIO_pad<5>     | B11           |               |                 |

# 5 The GBLD implementation

The GBLD [15-17] is designed as a laser driver and is one of the components on the VTRx and VTTx modules [7-9]. In addition, they are used as stand-alone differential line drivers on the OPB and the on the hybrid to drive the control link signals between the VTRx transceivers on the OPB and the GBTx ASICs [10-12] on the front-end hybrids.

They require configuration via I<sup>2</sup>C and a reset provided by the GBT-SCA [13-14]. The GBLDs are configured to be enabled and to come up in the default low-power mode. The connections of the two GBLDs on the OPB are given in Table 12.

Table 12: Connections for the two GBLD ASICs driving the signals between the VTRx on the OPB and the GBTx on the hybrid. The components are labelled \_FH or \_BH depending on if they are driving signals for the front or back hybrid.

| GBLD_FH, GBLD_BH |      |                 | SCA_2, SCA_1 |     |

|------------------|------|-----------------|--------------|-----|

| Pin              | Name |                 | Name         | Pin |

| 5                | SCL  | Pull-up to VDDc | SCL_pad<14>  | L3  |

| 6                | SDA  | Pull-up to VDDc | SDA_pad<14>  | L2  |

|         |      | VTRx_FH, VTRx_BH |     |    |

|---------|------|------------------|-----|----|

|         |      | Name             | Pin |    |

| 9       | DIN- |                  | RD- | 13 |

| 10 DIN+ |      | RD+              | 12  |    |

|    |       |                  | Connector pir       | 1         |          |

|----|-------|------------------|---------------------|-----------|----------|

|    |       |                  | Name                | HSC_F2/B2 | PCIe     |

| 20 | MODB+ |                  | N/C                 |           |          |

| 21 | MODA+ | CTLE circuit and | CTRL_DN_FH_P, _BH_P | 46        | B22, B70 |

| 22 | MODA- | AC coupling      | CTRL_DN_FH_N, _BH_N | 45        | B23, B71 |

| 23 | MODB- |                  | N/C                 |           |          |

|            |        |            | Power connections                                                  |

|------------|--------|------------|--------------------------------------------------------------------|

| 1          | RST    | Active low | LOGIC_RESET (SCA_1 GPIO and button)                                |

| 14         | I2C_A2 |            | $N/C$ to give the same $I^2C$ address as a VTT <sub>V</sub> (0v7E) |

| 15         | I2C_A3 |            | N/C to give the same $I^2C$ address as a VTTx (0x7E)               |

| 4          | DIS    |            | Pull-down to GND                                                   |

| 13         | HIMODE |            | Pull-down to GND                                                   |

| 18         | IBIAS  |            | 560 Ohm resistor to V_OPB_LINK1/2                                  |

| 7,12       | VDDc   | Decoupling | Net for I <sup>2</sup> C pull-up                                   |

| 2,8,11,17  | GND    |            | GND                                                                |

| 3,16,19,24 | VDD    | Decoupling | 2.5 V supply from DCDC_LINK1/2                                     |

# 6 **GBT-SCA** and **GBTx** implementation

The connections to the GBT-SCA [13,14] are partially defined from the tables of connections to the other components, since the connections to the GPIO, ADC channel or I<sup>2</sup>C bus are shown in those tables. This section defines the connections to the other pins and the connections between the GBTx [10-12] and the GBT-SCA. The connections for the two GBT-SCAs on the OPB are given in Table 13 and Table 14 lists the connections to the GBTx. The non-connected inputs are pulled with 10 k $\Omega$  to VDD and GND for the positive and negative inputs, respectively. The non-connected outputs are left floating. These are all labelled N/C in the table.

Table 13: Connections to the two GBT-SCA ASICs on the OPB, omitting the GPIO, ADC, I<sup>2</sup>C and power connections.

| Pin name(s)                                                                                 | Pin #                                                          | Connection                    | Comment                                                                                         |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------|

| GPIO_EXTCLK                                                                                 | A14                                                            | N/C                           | External clock for GPIO sampling, not used                                                      |

| auxPortSDA,<br>auxPortSCL, auxPortEn                                                        | H12, J12, K12                                                  | N/C (pull-up)                 | Aux serial control port, used for testing and daisy chaining SCAs                               |

| SPI bus pads                                                                                | B14, C14, D14,<br>C12, D12, E12,<br>F12, C13, D13,<br>E13, E14 | N/C                           | SPI bus not used                                                                                |

| TX_SD_AUX,<br>TX_SD_AUX_N,<br>RX_SD_AUX,<br>RX_SD_AUX_N,<br>LINK_CLK_AUX_N,<br>LINK_CLK_AUX | F13, F14, G13,<br>G14, H13, H14                                | N/C                           | Auxiliary GBTx-SCA link, not used                                                               |

| LINK_AUX_DISABLE                                                                            | L12                                                            | pull-up 4.7 k $\Omega$        | Disable auxiliary GBTx-SCA link                                                                 |

| TX_SD_N                                                                                     | J13                                                            | SCINN (GBTx<br>DINN16 (GBTx   | P13) for SCA_1<br>(G18) for SCA_2                                                               |

| TX_SD                                                                                       | J14                                                            | SCINP (GBTx H<br>DINP16 (GBTx | / _                                                                                             |

| RX_SD_N                                                                                     | L13                                                            | SCOUTN (GBT                   | Tx P3) for SCA_1<br>Tx H18) for SCA_2                                                           |

| RX_SD                                                                                       | L14                                                            | SCOUTP (GBT                   | x P4) for SCA_1<br>Tx J18) for SCA_2                                                            |

| LINK_CLK_N                                                                                  | K13                                                            | SCCLKN (GBT                   | Tx R6) for SCA_1<br>Tx L17) for SCA_2                                                           |

| LINK_CLK                                                                                    | K14                                                            | · ·                           | x P6) for SCA_1<br>Γx K17) for SCA_2                                                            |

| FuseProgramPulse                                                                            | M13                                                            | N/C                           | E-fuse for default register values not used                                                     |

| PWR3_3                                                                                      | G12                                                            | 11/C                          | for the SCA                                                                                     |

| RESET_B                                                                                     | M14                                                            | Power-on<br>reset             | Generated by 5kΩ/100nF RC on GBTx & SCA supply (DCDC_OPB_CTRL), push button or SCA_1 GPIO ch<6> |

| DAC_OUT<0-3>                                                                                | N3, N2, P3, P2                                                 | N/C                           | DACs not used                                                                                   |

| JTAG pads                                                                                   | P1, N1, M1, L1, K1                                             | N/C                           | JTAG not used                                                                                   |

| Pin name(s)                    | Pin #                 | Connection                                                                                      | Comment                                                                                                 |

|--------------------------------|-----------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| CLOCKDES<0-7>N/P               | Multiple              | N/C                                                                                             | Output clocks, not used                                                                                 |

| DCLKN/P<0-15, 17-39>           | Multiple              | N/C                                                                                             | E-links not used                                                                                        |

| DINN/P<0-15,17-39>             | Multiple              | N/C                                                                                             | E-links not used                                                                                        |

| DION/<0-15,17-39>              | Multiple              | N/C                                                                                             | E-links not used.                                                                                       |

| DCLKN/P<16>                    | L17, K17              | SCA_2 LINK_CLK(_n)                                                                              |                                                                                                         |

| DINN/P<16>                     | G18, F18              | SCA_2 TX_SD(_n)                                                                                 | Control link between GBTx and SCA_2                                                                     |

| DOUTN/P<16>                    | H1, J18               | SCA_2 RX_SD(_n)                                                                                 | Control link between OD1x and SEA_2                                                                     |

| DOUTN/F<10>                    | пі, ло                | SCA_2 KA_SD(_II)                                                                                | Configuration via I <sup>2</sup> C interface, used for USB                                              |

| CONFIGSELECT                   | K7                    | Switch to V <sub>DD</sub> /GND                                                                  | dongle programming and E-Fuse burning                                                                   |

| EFUSEPOWER                     | P14                   | Switch: 3.3 V supply and EFuse<br>connector pin 2 when burning<br>fuses, 1.5 V supply otherwise | For E-Fuse burning                                                                                      |

| EFUSEPROGRMPULSE               | P11                   | EFuse connector pin 4                                                                           | For E-Fuse burning                                                                                      |

| I2CADDRESS<0-3>                | L8, N6,<br>N7, P5     | N/C                                                                                             | Default address 0000001 is OK, set by internal pull-up/down resistors.                                  |

| LDRESET                        | J7                    | N/C                                                                                             | Not used                                                                                                |

| LDSCL                          | K8                    | VTRx OPB SCL (pin5)                                                                             | I <sup>2</sup> C bus for VTRx configuration, pulled up                                                  |

| LDSCA                          | H8                    | VTRx OPB SDA (pin 4)                                                                            | with 750 $\Omega$ to 1.5 V                                                                              |

|                                | N5, L7,               | Optional pull-up (4.7k) and                                                                     | Sets the transmission mode, expected mode                                                               |

| MODE<0-3>                      | L10, P10              | GND via resistors                                                                               | for VELO is 0010 (FEC Transceiver)                                                                      |

| REFCLKN/P                      | K1, L1                | N/C                                                                                             | Local reference clock not used                                                                          |

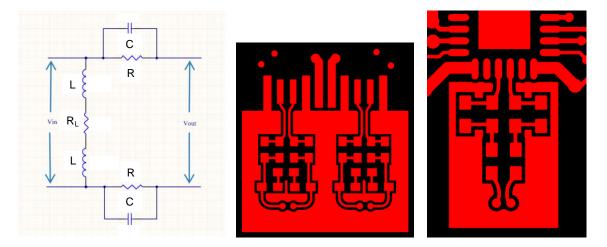

|                                | ,                     |                                                                                                 | Take reference clock from PLL or XOsc. GBT                                                              |