## Upgrade of the ATLAS Muon Drift Tube Front-end Electronics for HL-LHC Runs

#### X. Hu, University of Michigan On behalf of the ATLAS Muon Collaboration

### Outline

#### Introduction

- ATLAS MDT Detector

- MDT Electronics System

### Frontend Electronic System Upgrade

- ASD

- TDC

- Mezzanine Card

- CSM

- Integration Test Plan

- **Summary**

### Introduction

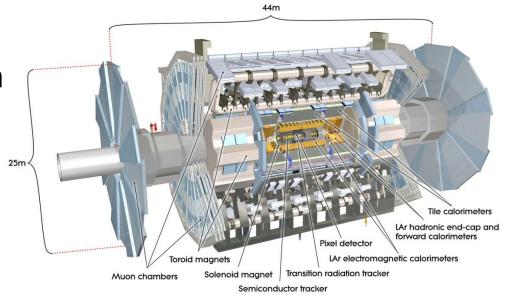

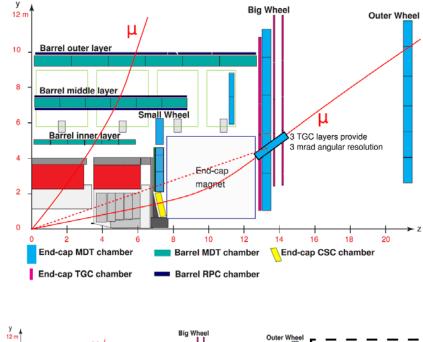

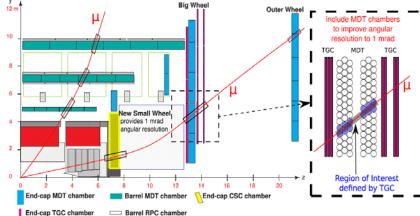

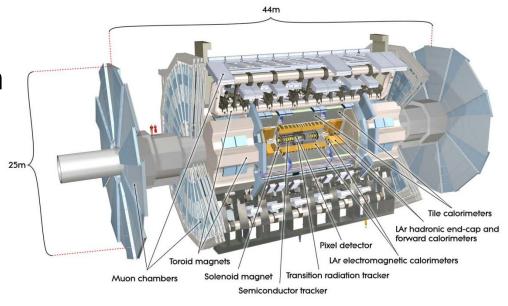

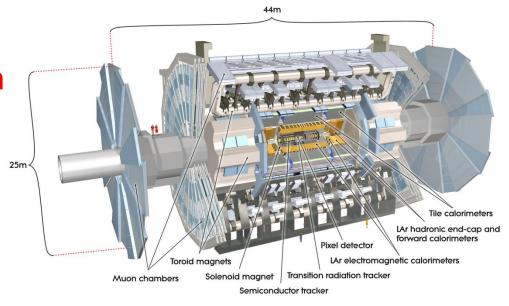

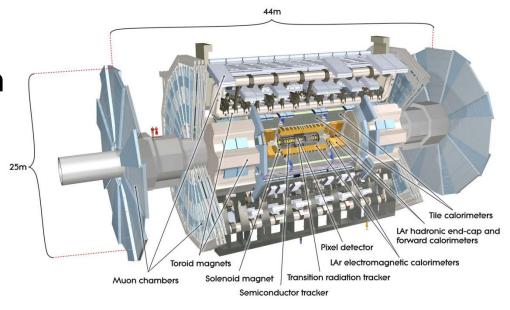

#### **ATLAS Muon Spectrometer**

- Muon triggering, identification & momentum measurement

- Resistive Plat Chambers (RPCs)/ Thin Gap Chambers (TGCs): primary trigger detectors

- Monitored Drift Tubes (MDTs)/ Cathode Strip Chambers (CSCs): precision trackers

#### MDT Detector Upgrade @ HL-LHC

- Improve Muon transverse momentum (pT) resolution at L0 triggering

- pT selectivity of tracks for the trigger will be improved by integrating MDT info into L0 triggering

- RPC and sMDT chambers will replace current MDT chambers (inner barrel) to allow for a 3-station RPC trigger

- Cope with high rates

- MDT readout electronics system must be upgraded

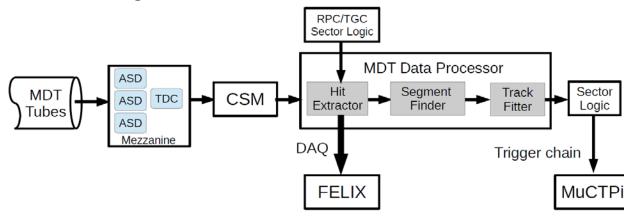

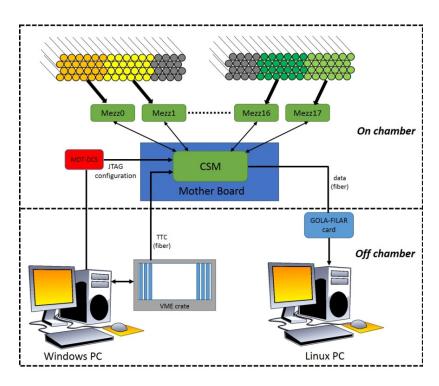

## **MDT Electronics System**

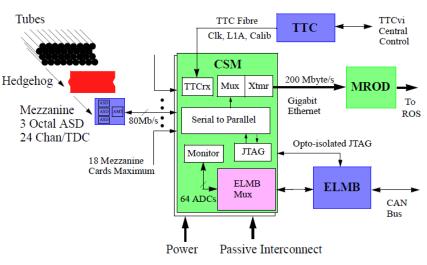

#### **MDT Elx @ Current System**

- MDT & Trigger. Chambers independently R/O

- MDT readout only on L1 trigger → lower bandwidth

- Trigger mode used at the Front-end

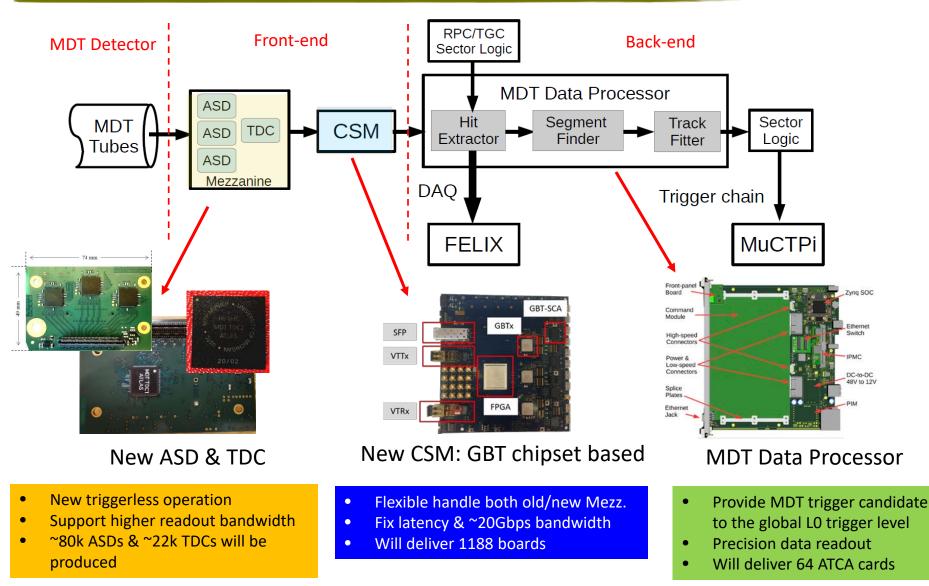

### **MDT Elx @ HL-LHC**

- MDT data "sharpen" trigger decision

- Find accurate pT using ROI seed from trigger chambers and confirm/reject trigger hypothesis

- Triggerless at FE and track fitting in the counting room → higher bandwidth

## MDT Electronics System @ HL-LHC

### Outline

#### Introduction

- ATLAS MDT Detector

- MDT Electronics System

#### Frontend Electronic System Upgrade

- ASD

- TDC

- Mezzanine Card

- CSM

- Integration Test Plan

- **Summary**

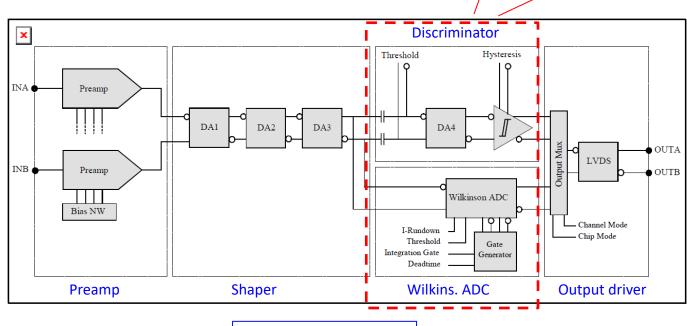

### **Amplifier-Shaper-Discriminator ASIC**

Discriminator

ADC

Leading Edge

Charge

#### **ASD** Design

- 8-Chs ASD: GF 130nm CMOS process (7.6 mm<sup>2</sup>)

- 4 key parts

- Pre-amplifier: charge-sensitive

- Shaper: differential amplification (DA1-DA3)

- o Wilkinson ADC & Discriminator

- o Output Driver

LVDS

Threshold

Trailing Edge

Optical photo of ASD ASIC

Diagram of one ASD Channel

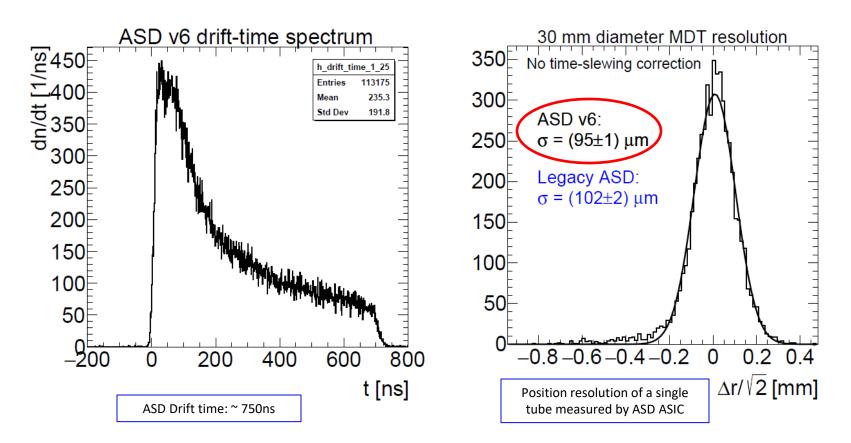

### **Amplifier-Shaper-Discriminator ASIC**

#### **ASD Project Status**

- Detailed studies performed and no design problems found

- Test of the ASD up to 1 Mrad and checked chip behaviors for current, peak time, pulse shape etc before and after the irradiation

- Also studied ASD performance at GIF++ with 150 GeV muon beam

## **Time-Digital-Converter ASIC**

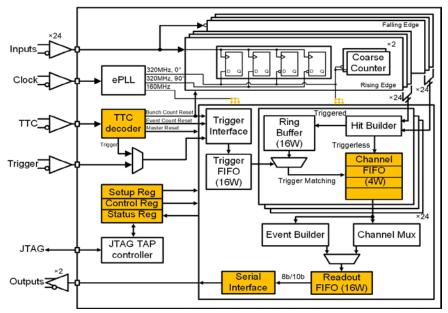

#### **D** TDC Design

- 24 CHs input, 2 CHs outputs (320Mbps)

- 4 key parts

- o ePLL (extended Phase-locked loop)

- Timing circuit: fine + coarse time (0.78ns bin)

- o TDC logic

- Trigger-less + Trigger mode

- New output protocol

- High speed interface

- o Interface: serial output, configuration, clocks...

| No. of channels             | 24                                                                |

|-----------------------------|-------------------------------------------------------------------|

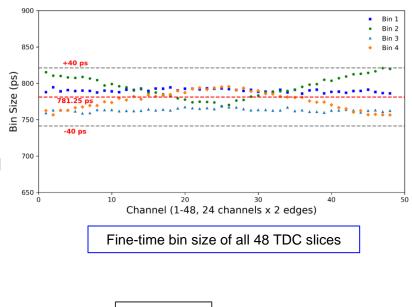

| Least time count            | 0.78 ns                                                           |

| Dynamic range               | 17 bits (102.4 µs)                                                |

| Integral non-linearity      | ±40 ps                                                            |

| Differential non-linearity  | ±40 ps                                                            |

| Double hit resolution       | <10 ns                                                            |

| Input clock frequency       | 40 MHz                                                            |

| Max. recommended hit rate   | 400 kHz per channel                                               |

| Edge/pair time measurements | Configurable                                                      |

| Output data rate            | Configurable: 80 Mbps one line, 160/320 Mbps two lines            |

| Triggerless/trigger modes   | Configurable                                                      |

| Triggerless: Latency        | <500 ns at 400 kHz per tube                                       |

| Trigger: Buffer sizes       | Hit buffer: 16/channel, channel FIFO: 4/channel, Readout FIFO: 16 |

| Channel enable/disable      | Yes                                                               |

| Input/Output signal         | SLVS                                                              |

| Radiation tolerance         | >20 kRad                                                          |

| Power consumption           | <360 mW                                                           |

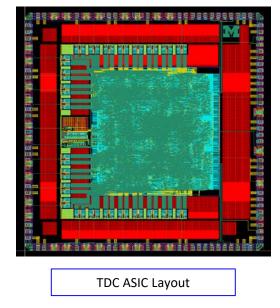

| Fabrication process         | TSMC 130 nm CMOS process                                          |

Diagram of TDC V2 with TMR implemented (yellow blocks)

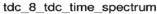

### **Time-Digital-Converter ASIC**

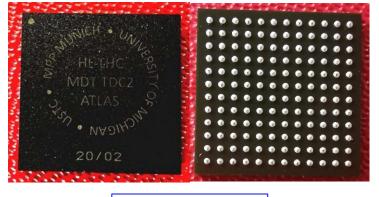

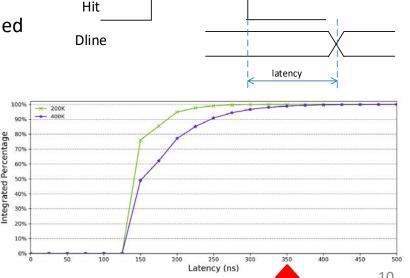

#### **TDC Project Status**

- Detailed studies performed and no design problems found

- Bin size for all 48 channels have been measured (24 0 channels  $\times$  rising and falling edges): variation < ±40ps

- Latency: For 400kHz hit rate, 99% of the data was read 0 out after 350ns

- Brief history of TDC development

- 2016: V0 designed and tested (GF 130nm) 0

- 2018: V1 submitted and tested (TSMC 130nm) Ο

- 2019/2020: V2 submitted and tested Ο

- Triple Modular Redundancy (TMR) added

Percentage

BGA 12\*12 package

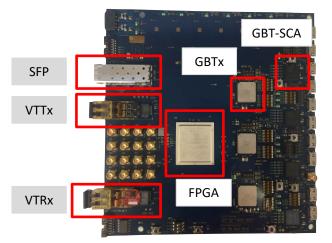

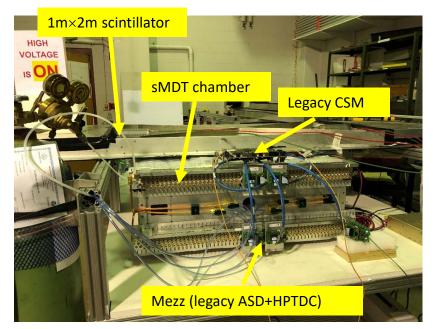

### **Mezzanine Card**

#### Design

- Compatibility

- dimensions and locations of the connectors (Faraday 0 cages, read-out hedgehog cards, and read-out cables)

- Pin assignment Ο

- Radiation tolerant

- All critical components must be radiaion tolerant Ο

- COTS LDO radiation tests have been scheduled 0

#### **Status**

- A few mezz. Prototype cards built:

- Multiple ASD+TDC combinations Ο

- Specification review in May. 2019

- Prelimiary design review in Mar. 2020

3 new ASDs + 1 FPGA TDC

3 legacy ASDs + 1 HPTDC (stacked for sMDT)

3D CAD model: 11 3 new ASDs + 1 new TDC V2

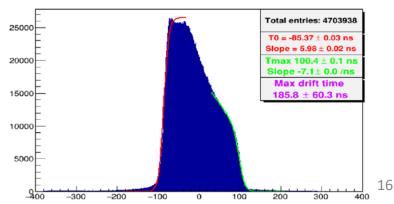

### **Chamber Service Module**

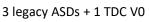

#### **CSM** Design

- Bandwidth: Input (36CHs \* 320Mbps); Output (uplink fiber 2\*10.24Gbps, downlink fiber 1\* 2.56Gbps)

- 4 key parts

FE

Mezz

FE

Mezz

FE

Mezz

ASD 🔁

ASD

ASD

ASD

ASD

ASD

9

3

Up to 18

Mezz.

- LpGBT \*2 (master-slave mode)

- o GBT-SCA: monitoring & configuration

High-

density

140

pin conn.

• Fan-out FPGA: receive "TTC" info and broadcast to all 18 Mezz.

18\*2CHs @ 320Mbps And/Or

18\*1CH @ 80Mbps

Data In

40MHz \* 18

Elink clocks

AVDD, DVDD, TEMP

(6\*18)

**CSM Monitoring**

Volt,Temp

ENC, Calib\* 18

JTAG Config.

Normal Elinks

LpGBT

320Mbps

80Mbps\*3

**GBT-SCA**

Fan-Out

**FPGA**

GPIO, I2C, JTAG

• VTRx+: optical module

10.24 Gbps \*2

VL+

(2 Tx

&

1 Rx)

Normal Elink

for

TTC

80Mbps\*1

Uplink

Gbps

Downlink

BE

Proc.

OMD.

**TDC Data**

Monitor info

40MHz clocks Config. & Ctrl

#### Photo of CSM prototype v1

LpGBT-CSM Functionality Block Diagram

### **Chamber Service Module**

#### **CSM Project Status**

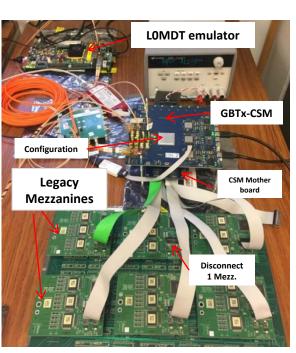

- Prototype v1 (GBTx-based): pass standalone & integration tests

- Specificaiton review in Dec. 2018

- Preliminary deisgn reivew in Mar. 2020

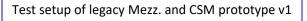

- Prototype v2 submitted in Jul. 2020

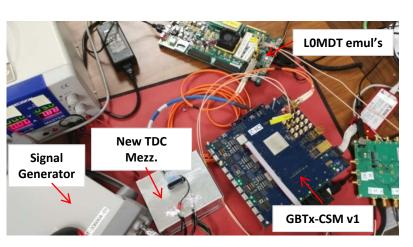

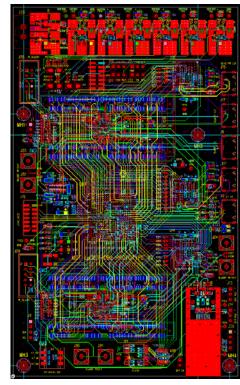

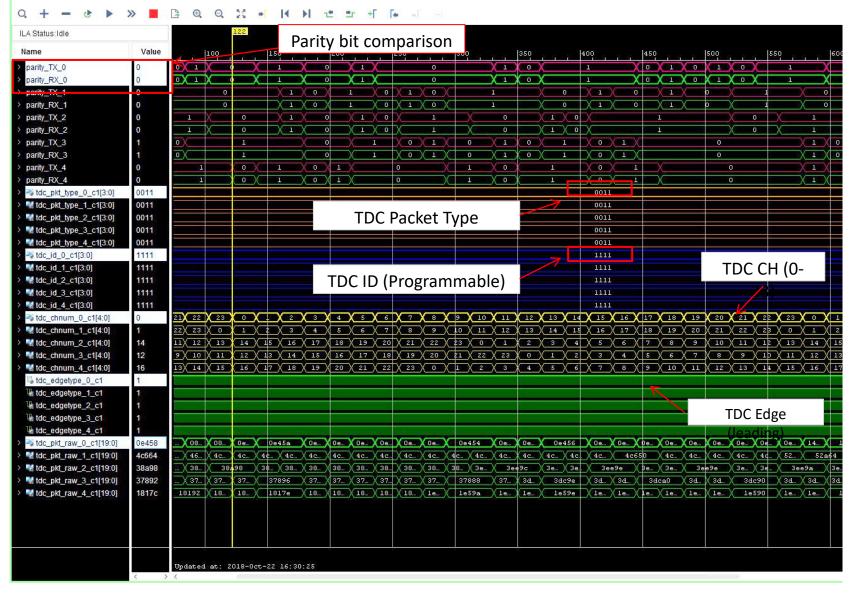

Test setup of new TDC Mezz. and CSM prototype v1

LpGBT-CSM v2 layout

#### Six legacy Mezzanines tested with New CSM v1

- Configuration done properly

- Data decoded successfully

#### Waveform - hw\_ila\_4

### Outline

#### □ Introduction

- ATLAS MDT Detector

- MDT Electronics System

### Frontend Electronic System Upgrade

- ASD

- TDC

- Mezzanine Card

- CSM

- Integration Test Plan

- **Summary**

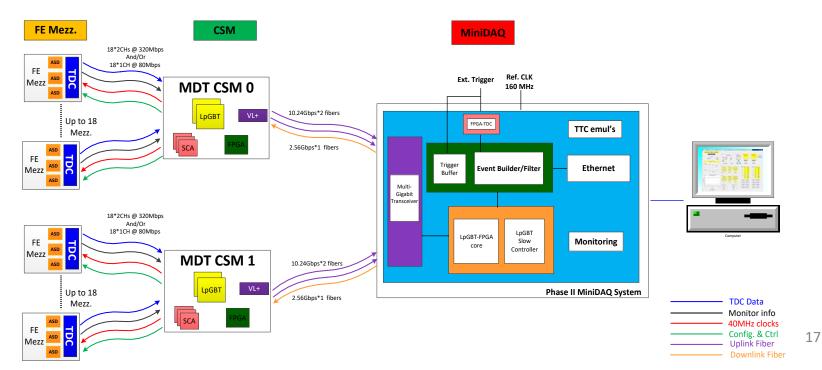

### **Integration Test Plan**

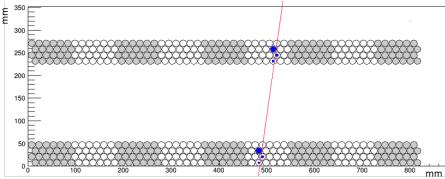

- Current activities -- sMDT cosmic ray test system

- Legacy electronics used, but will be replaced with new electronics later

### **Integration Test Plan**

- Goal: integrate different electronics components together and perform studies with/without sMDT/MDT chambers and LOMDT

- Plan to perform integration tests in several steps:

- ✓ ASD+TDC v1 (QFN package) with and without CSM v1

- ASD (QFN88) +TDC v2 (BGA)+CSM v2 with and without chambers

- o Develop miniDAQ system for integration tests

- ASD+TDC v2+CSM v2+L0MDT demonstrator

- Final versions of ASD, TDC and CSM with L0MDT v1

### Outline

#### □ Introduction

- ATLAS MDT Detector

- MDT Electronics System

### Frontend Electronic System Upgrade

- ASD

- TDC

- Mezzanine Card

- CSM

#### Integration Test Plan

**Summary**

### Summary

- To cope with high rates & improve pT momentum resolution, upgrade all MDT electronics system is required

- MDT FE upgrade projects have made lots of progress and passed major reviews (SPR, PDR/FDR)

- o ASD: in production run

- o TDC: close to final designs

- Mezzanine card prototype & CSM prototype v2: all final features

- Ongoing development on the frontend electronics integration

- MiniDAQ: sMDT/MDT chambers  $\rightarrow$  Mezz. card  $\rightarrow$  CSM  $\rightarrow$  L0MDT emulator (light version)

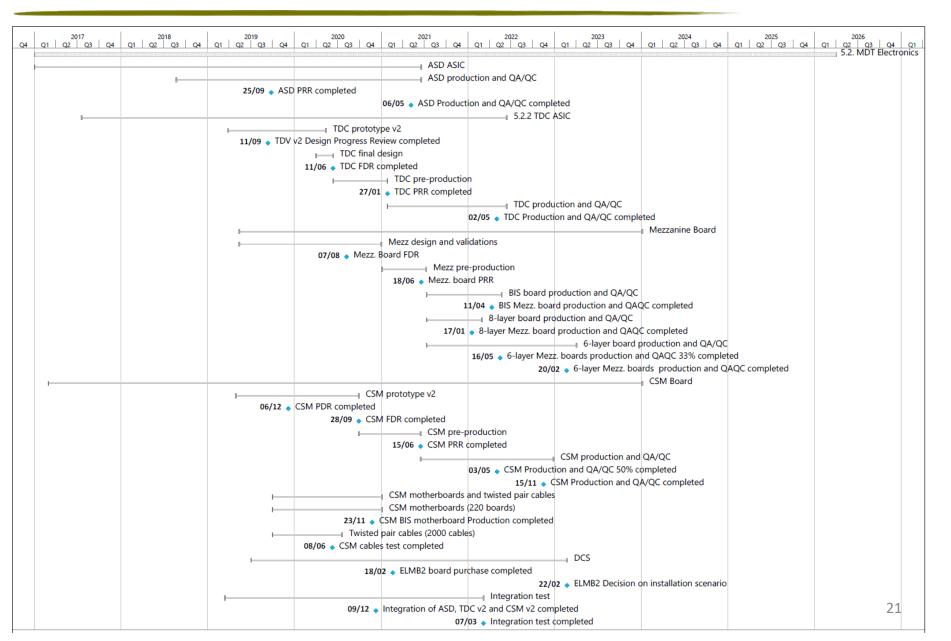

- General Schedules

- o ASD production done @ Q3.2021

- TDC production done @ Q3.2022

- o Mezz. card production done @ Q1. 2024

- o CSM production done @ Q1. 2024

# Thanks!

### **Schedules**