## Université de Savoie Laboratoire d'Annecy-Le-Vieux de Physique des Particules BP 110, 74941 Annecy-Le-Vieux Cedex, France

#### **THÈSE**

présentée pour obtenir le titre de

Docteur en Sciences Spécialité : Physique Experimentale & Instrumentation

par

#### **Xudong CAI**

## Contribution à l'élaboration et à la mise en oeuvre du système de déclenchement et d'acquisition de l'expérience L3 au LEP

Soutenue le 6 Octobre 1994 devant la Commission d'Examen

L. Massonnet (Président)

J. J. Blaising (Directeur de thèse)

O. Callot (Rapporteur)

P. Charpentier (Rapporteur)

A. DegréC. Dionisi

# Contribution to the trigger and data acquisition system of the L3 experiment at LEP

Xudong CAI

6 October 1994

Annecy, France

## Résume

Cette thèse est consacrée au système de déclenchement et d'acquisition de l'expérience L3 au LEP. Il est distribué à plusieurs niveaux, afin de déclencher, sélectionner, collecter et enregistrer les événements détectés par L3. Le système de déclenchement à trois niveaux permet de réduire un éventuel taux de déclenchement de premier niveau de 100 Hz à quelques Hz. Les systèmes de lecture et d'assemblage disposent de mémoires intermédiaires afin que seul la numérisation des données des détecteurs introduise du temps mort.

Dans cette thèse l'accent est mis sur le système de lecture du calorimètre hadronique, le système central d'assemblage et le filtre de troisième niveau.

Mots clefs: L3-Déclenchement-Acquisition-FASTBUS-Transputer

## **Abstract**

This thesis is devoted to the L3 trigger and data acquisition system of the L3 experiment at LEP. It is a large distributed system with multiple levels to trigger, collect and record events detected by the L3 detector. The three trigger levels are designed to reduce a possible first level trigger rate of 100 Hz to a few Hz. The readout and event building systems have intermediate buffering so that the only dead time is introduced during digitization of the detector signals.

The emphasis of this thesis is on the Hadron Calorimeter (one of the subdetectors) readout system, the L3 event building system and the upgraded level-3 trigger system. Both hardware and software are described.

Keywords: L3-Trigger-Data Acquisition-FASTBUS-Transputer

## **Contents**

| Ré | sume    | ;             |                                  | i   |

|----|---------|---------------|----------------------------------|-----|

| Al | ostrac  | :t            |                                  | i   |

| Co | ontent  | ts            |                                  | iii |

| Li | st of l | Figures       |                                  | vii |

| Li | st of ' | <b>Tables</b> |                                  | X   |

| In | trodu   | ction (F      | French)                          | 1   |

| 1  | Le I    | LEP et l      | 'expérience L3                   | 6   |

|    | 1.1     | Le LE         | P                                | 6   |

|    | 1.2     | Le Det        | tecteur L3                       | 7   |

|    |         | 1.2.1         | Introduction                     | 7   |

|    |         | 1.2.2         | Le détecteur central de trace    | 9   |

|    |         | 1.2.3         | Le Calorimètre Electromagnétique | 11  |

|    |         | 1.2.4         | Les Compteurs à Scintillation    | 12  |

|    |         | 1.2.5         | Le Calorimètre Hadronique        | 12  |

|    |         | 1.2.6         | Le Spectromètre à Muons          | 14  |

|    |         | 1.2.7         | Les Moniteurs de Luminosités     | 15  |

| In | trodu | ction   |                                      | 18         |

|----|-------|---------|--------------------------------------|------------|

| 1  | LEI   | and th  | ne L3 Experiment                     | 19         |

|    | 1.1   | The L   | EP                                   | 19         |

|    | 1.2   | The L   | 3 Detector                           | 20         |

|    |       | 1.2.1   | Introduction                         | 20         |

|    |       | 1.2.2   | The Central Track Detector           | 22         |

|    |       | 1.2.3   | The Electromagnetic Calorimeter      | 23         |

|    |       | 1.2.4   | The Scintillation Counters           | 24         |

|    |       | 1.2.5   | The Hadron Calorimeter               | 25         |

|    |       | 1.2.6   | The Muon Spectrometer                | 27         |

|    |       | 1.2.7   | The Luminosity Monitors              | 28         |

| 2  | 700 - | T a mus |                                      | 20         |

| 2  |       |         | gger and Data Acquisition System     | 30         |

|    | 2.1   |         | uction                               |            |

|    | 2.2   | The Fi  | irst Level Trigger System            | 31         |

|    |       | 2.2.1   | The Calorimeter Trigger              | 32         |

|    |       | 2.2.2   | The TEC Trigger                      | 33         |

|    |       | 2.2.3   | The Scintillator Trigger             | 33         |

|    |       | 2.2.4   | The Muon Trigger                     | 33         |

|    |       | 2.2.5   | The Level-1 Trigger Rates            | 34         |

|    | 2.3   | The Se  | econd Level Trigger System           | 35         |

|    | 2.4   | The Re  | eadout and Event Building Systems    | 38         |

|    | 2.5   | The Th  | hird Level Trigger System            | 38         |

|    | 2.6   | The Tr  | rigger Control Logic                 | 39         |

|    |       | 2.6.1   | Overview                             | . 39       |

|    |       | 262     | Timing of the Trigger and DAO System | <b>4</b> 1 |

| 3 | The | Hadron  | Calorimeter Data Acquisition System |   | 46  |

|---|-----|---------|-------------------------------------|---|-----|

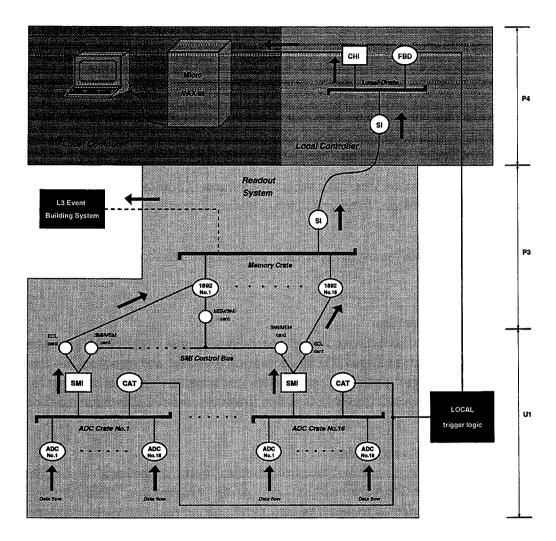

|   | 3.1 | Genera  | al Description                      |   | 46  |

|   |     | 3.1.1   | The System Requirements             |   | 46  |

|   | ÷   | 3.1.2   | System Structure                    |   | 47  |

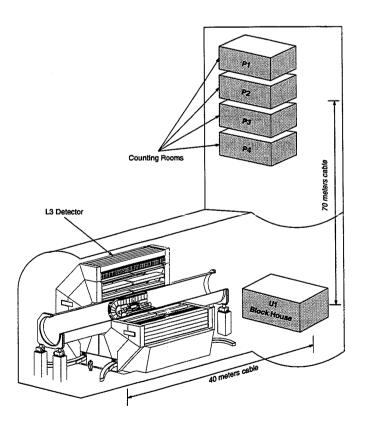

|   |     | 3.1.3   | System Location                     |   | 49  |

|   | 3.2 | Hardwa  | are                                 |   | 50  |

|   |     | 3.2.1   | Digitization                        |   | 50  |

|   |     | 3.2.2   | The Readout System                  |   | 51  |

|   |     | 3.2.3   | Local Controller                    |   | 55  |

|   |     | 3.2.4   | The Local Trigger Logic             |   | 56  |

|   | 3.3 | Softwa  | are                                 | • | 60  |

|   |     | 3.3.1   | Software Structure                  | • | 60  |

|   |     | 3.3.2   | The VAX Software                    | • | 62  |

|   |     | 3.3.3   | The CHI Software                    | • | 67  |

|   |     | 3.3.4   | The SMI Software                    | • | 73  |

|   |     | 3.3.5   | Data Format                         |   | 80  |

|   | 3.4 | System  | n Performance                       | • | 81  |

|   |     |         |                                     |   | 0.4 |

| 4 | The | Event I | Building System                     |   | 84  |

|   | 4.1 | Introdu | uction                              | • | 84  |

|   | 4.2 | System  | n Composition and Data Flow         | • | 86  |

|   | 4.3 | The L3  | 3 Event Structure                   |   | 88  |

|   | 4.4 | The Ev  | vent Building Software              | • | 90  |

|   | 4.5 | System  | m Configuration                     |   | 94  |

|   | 4.6 | The In  | nitialization Process               |   | 98  |

|   | 4.7 | The M   | Ionitoring Program                  |   | 100 |

|   | 4.8 | The Di  | iagnostic Tool                      |   | 103 |

|    | 4.9   | System Performance                | 104 |

|----|-------|-----------------------------------|-----|

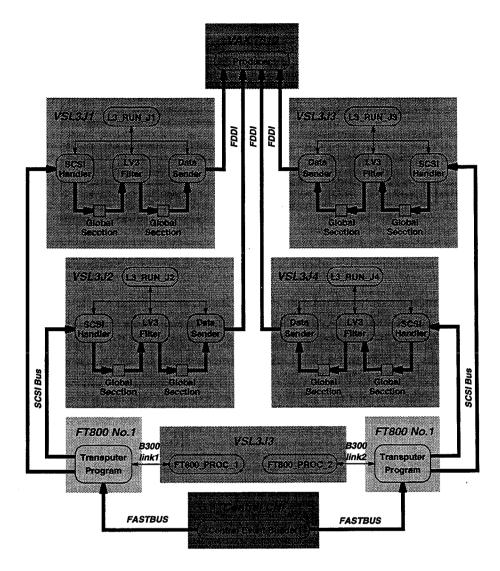

| 5  | The   | Third Level Trigger System        | 108 |

|    | 5.1   | Introduction                      | 108 |

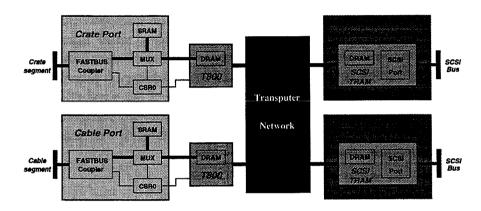

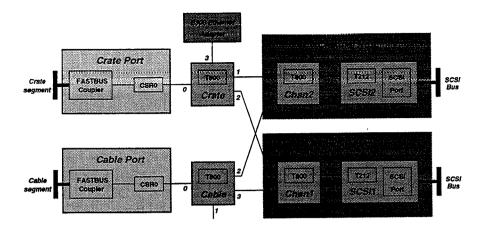

|    | 5.2   | The FASTBUS Interface FT800       | 110 |

|    | 5.3   | Software Structure                | 113 |

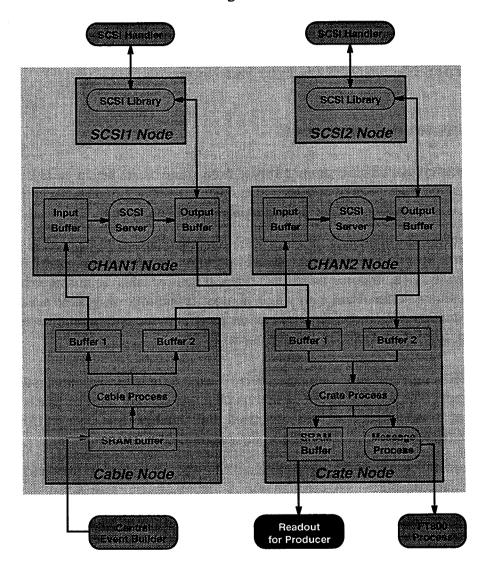

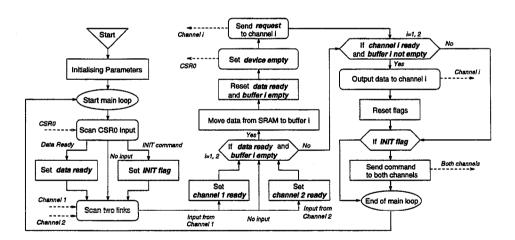

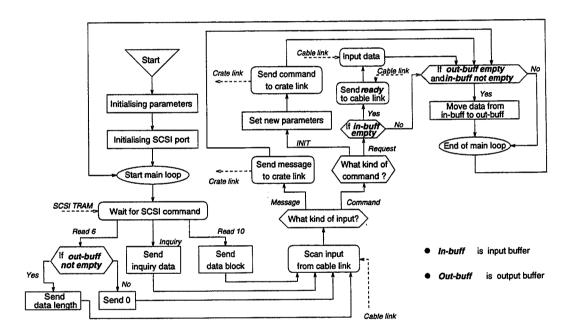

|    | 5.4   | The Transputer Software           | 115 |

|    | 5.5   | The SCSI Handler                  | 122 |

|    | 5.6   | System Performance                | 123 |

| Co | nclus | sions and Prospects               | 125 |

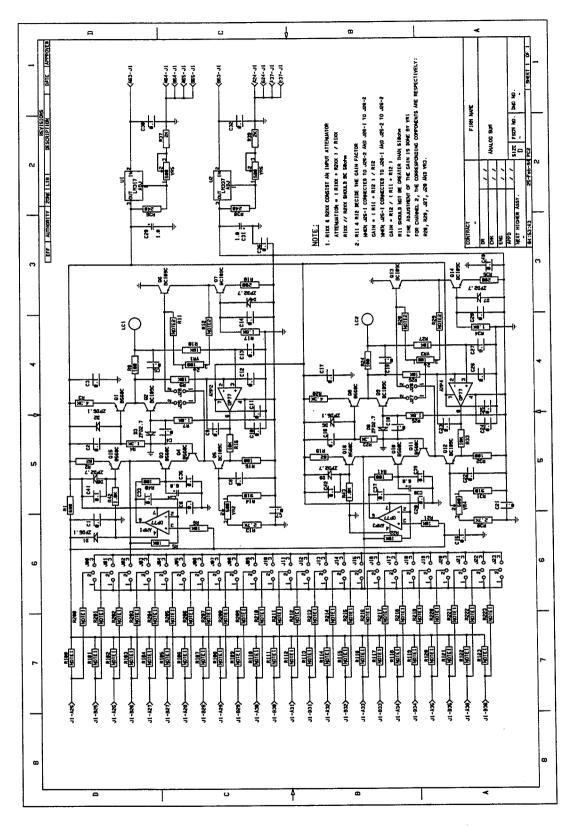

| A  | The   | Analog Sum Card                   | 126 |

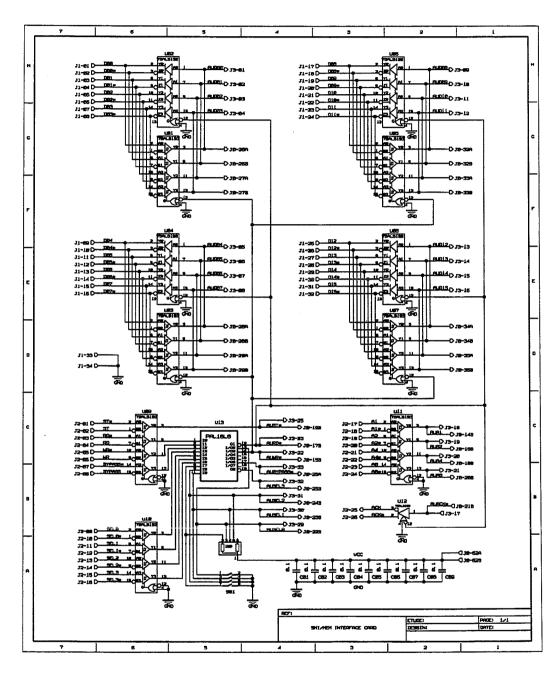

| В  | The   | Interfaces of the SMI Control Bus | 129 |

| Ac | know  | vledgements                       | 133 |

## **List of Figures**

| 1.1 | Le LEP                                          | 6  |

|-----|-------------------------------------------------|----|

| 1.2 | Shema du detecteur L3                           | 8  |

| 1.3 | Système de coordonnées utilisé dans L3          | 9  |

| 1.4 | Le détecteur central de trace                   | 10 |

| 1.5 | Le Calorimètre Electromagnétique                | 11 |

| 1.6 | Coupe de la partie interne du détecteur L3      | 12 |

| 1.7 | Module du calorimètre hadronique                | 13 |

| 1.8 | Vue globale du Spectromètre à Muon              | 14 |

| 1.9 | Shema d'un octant du système de chambres à muon | 15 |

| 1.1 | The map of LEP                                  | 19 |

| 1.2 | The perspective view of the L3 detector         | 21 |

| 1.3 | The L3 coordinate system                        | 22 |

| 1.4 | The central track detector                      | 23 |

| 1.5 | The electromagnetic calorimeter                 | 24 |

| 1.6 | The cutaway side view of inner L3 detector      | 25 |

| 1.7 | Assembly of the HCAL module                     | 26 |

| 1.8 | The overview of the muon spectrometer           | 27 |

| 1.9 | The end view of one muon octant                 | 28 |

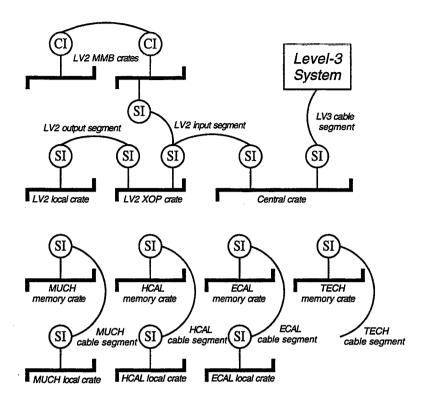

| 2.1 | The structure of the L3 trigger and DAQ system  | 31 |

| 2.2  | The level-1 trigger rates in fill No.1891             | 34  |

|------|-------------------------------------------------------|-----|

| 2.3  | The structure of the second level trigger system      | 36  |

| 2.4  | The block diagram of the trigger control logic        | 40  |

| 2.5  | The level-1 trigger timing                            | 42  |

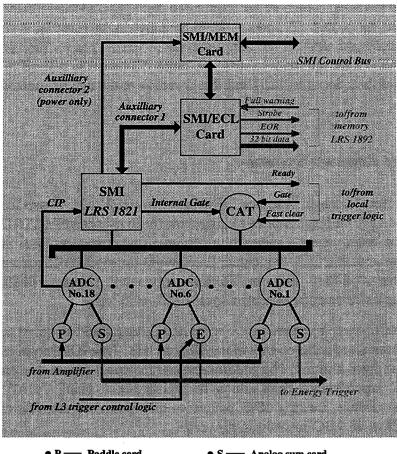

| 3.1  | The hadron calorimeter readout system                 | 48  |

| 3.2  | The locations of the L3 electronics                   | 49  |

| 3.3  | The organization of the SMI readout system            | 52  |

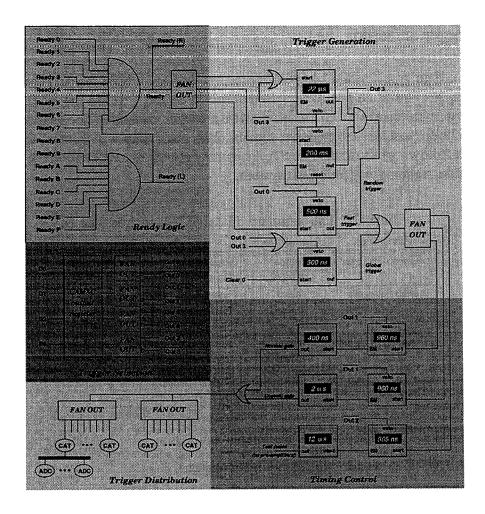

| 3.4  | The HCAL local trigger logic                          | 57  |

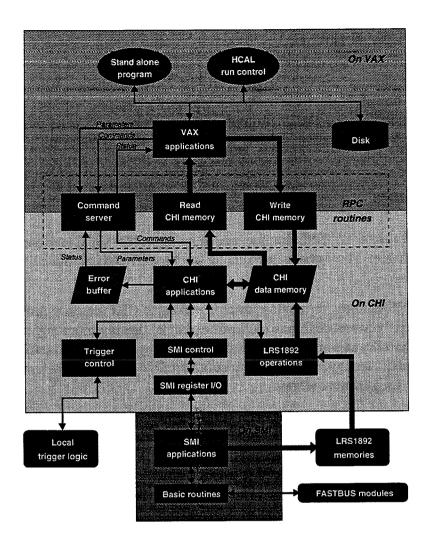

| 3.5  | The HCAL software structure                           | 61  |

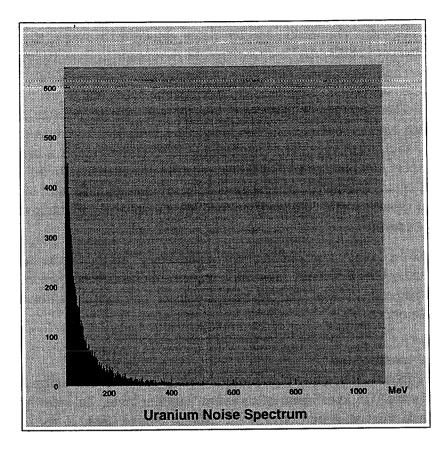

| 3.6  | The uranium noise spectrum                            | 65  |

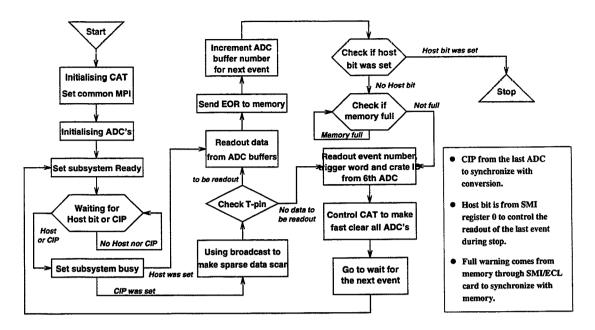

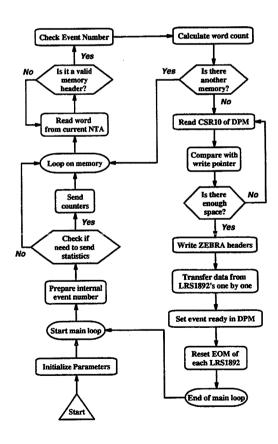

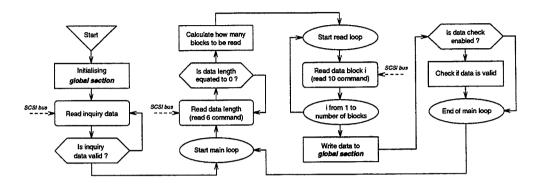

| 3.7  | The flow chart of the SMI data taking routine         | 79  |

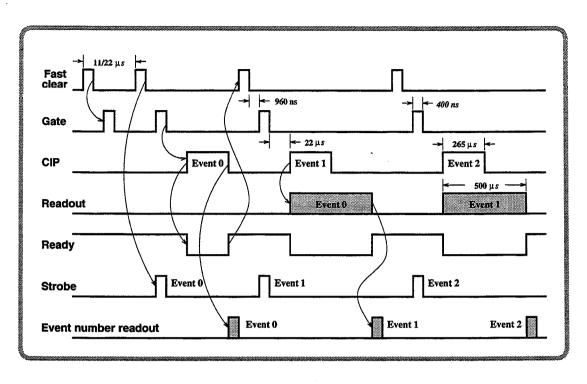

| 3.8  | The readout timing in the HCAL system                 | 80  |

| 3.9  | The HCAL data format in each memory                   | 81  |

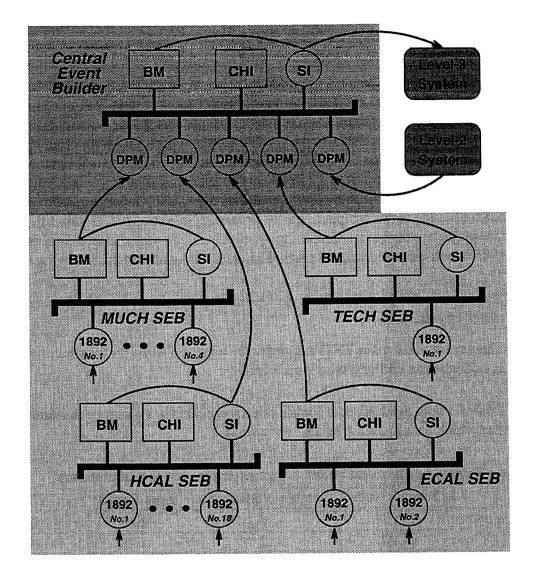

| 4.1  | The L3 event building system                          | 85  |

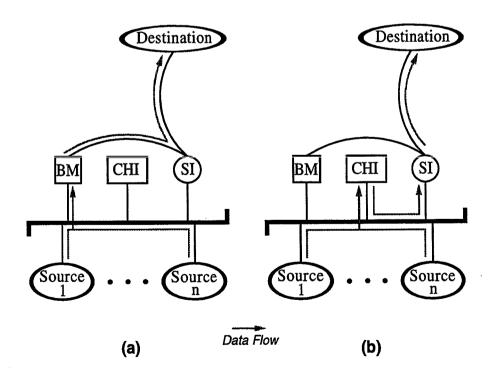

| 4.2  | The data flow in the event builder system             | 87  |

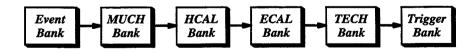

| 4.3  | The L3 data banks                                     | 88  |

| 4.4  | The organization of the subdetector bank              | 89  |

| 4.5  | The flow chart of the subdetector event builder       | 91  |

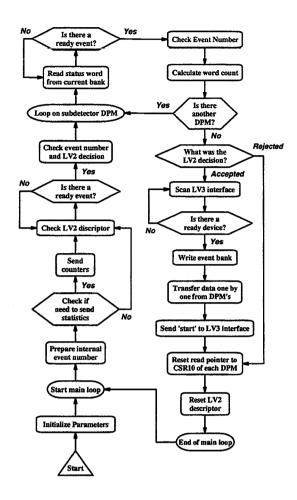

| 4.6  | The flow chart of the central event builder           | 92  |

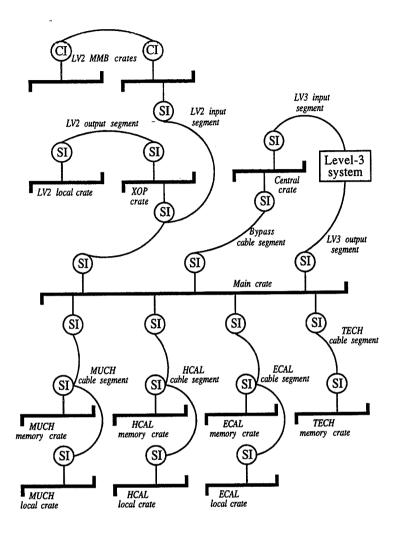

| 4.7  | The original configuration of the L3 FASTBUS segments | 95  |

| 4.8  | The new configuration of the L3 FASTBUS segments      | 96  |

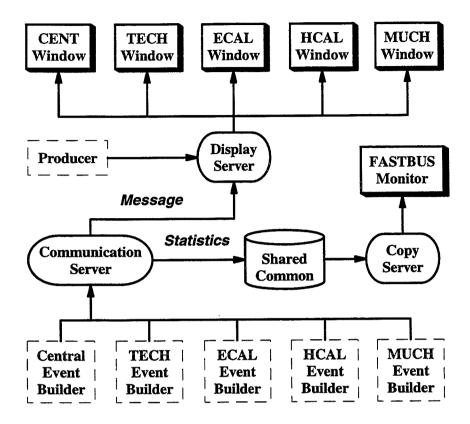

| 4.9  | The event building monitoring processes               | .01 |

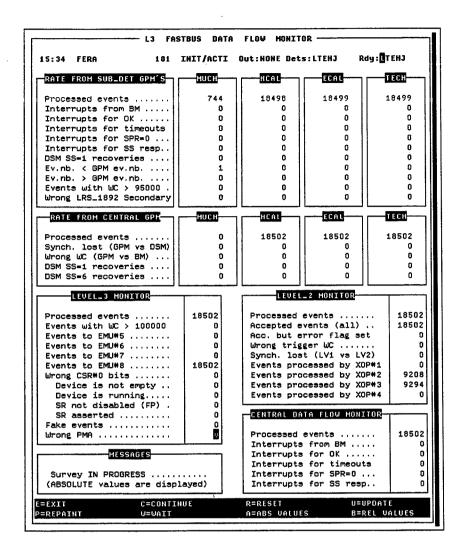

| 4.10 | The FASTBUS monitor display                           | 03  |

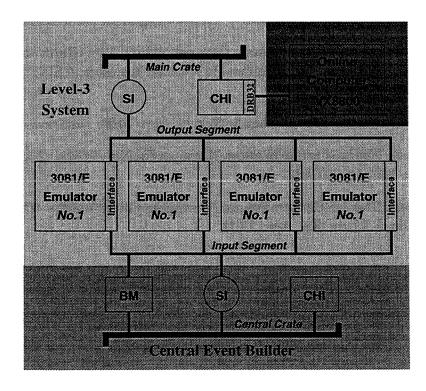

| 5.1  | The old level-3 trigger system                        | 108 |

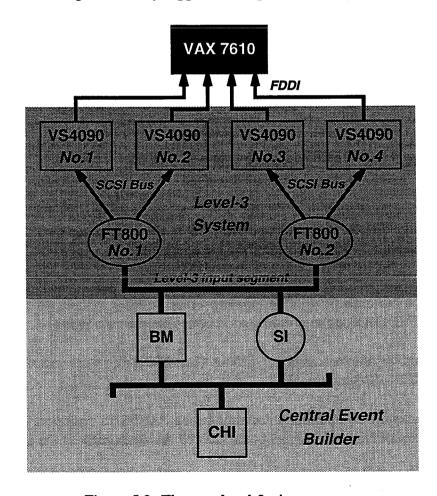

| 5.2  | The new level-3 trigger system                        | 109 |

| 5.3  | The block diagram of the FT800 interface              | 11  |

| 5.4         | The transputer network configuration                |

|-------------|-----------------------------------------------------|

| 5.5         | The structure of the level-3 trigger software       |

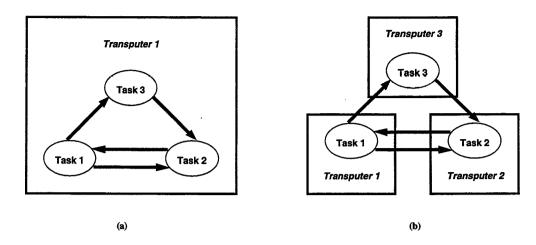

| 5.6         | The multiple tasks on the transputer network        |

| 5.7         | The FT800 software structure                        |

| 5.8         | The flow chart of the cable process                 |

| 5.9         | The flow chart of the SCSI server                   |

| 5.10        | The flow chart of the SCSI handler                  |

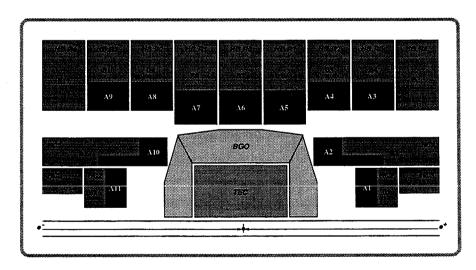

| <b>A.</b> 1 | The HCAL layers definded by the calorimeter trigger |

| A.2         | The circuit diagram of the analog sum card          |

| B.1         | The pin map of SMI 1821 I/O connector               |

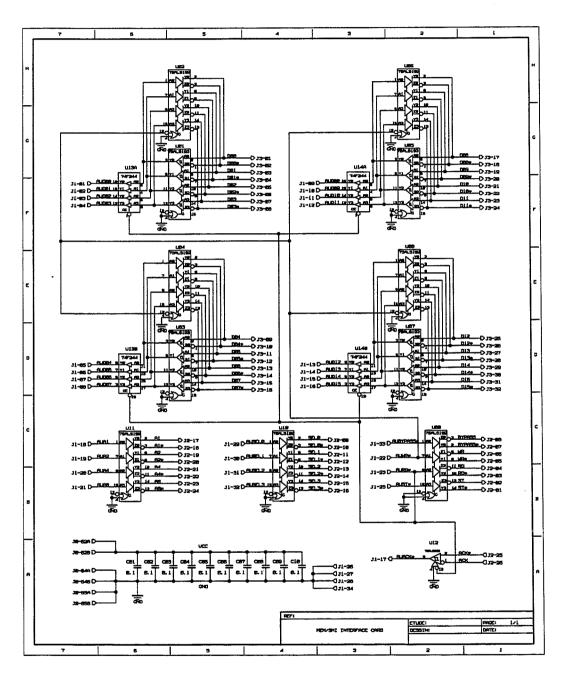

| B.2         | The schematic diagram of the SMI/MEM card           |

| B.3         | The schematic diagram of the MEM/SMI card           |

## **List of Tables**

| 1.1  | Principaux paramètres de LEP (Phase 1)                 | 7  |

|------|--------------------------------------------------------|----|

| 1.1  | The major parameters of LEP (Phase 1)                  | 20 |

| 2.1  | The typical level-1 trigger rates                      | 35 |

| 2.2  | The major subdetector readout systems                  | 38 |

| 2.3  | The signals from the trigger control logic             | 43 |

| 3.1  | The bit map of CSR10 of LRS1892                        | 54 |

| 3.2  | The summary of the HCAL trigger type                   | 58 |

| 3.3  | The commands defined by the command server             | 52 |

| 3.4  | The running parameters                                 | 63 |

| 3.5  | The CAMAC address word from FBD                        | 70 |

| 3.6  | The default value in the SMI microcode compiler        | 75 |

| 3.7  | The error codes during the FASTBUS operations          | 76 |

| 3.8  | The SMI readout routines                               | 77 |

| 3.9  | The bit map of the ADC word                            | 80 |

| 3.10 | The format of control words                            | 81 |

| 4.1  | The event buffer memories required by the subdetectors | 86 |

| 4.2  | The L3 data banks                                      | 89 |

| 4.3  | ZEBRA headers                                          | 89 |

| 4.4 | The event description bank                       |   | • | • | • | • | • | • | • | • | • | • | 90  |

|-----|--------------------------------------------------|---|---|---|---|---|---|---|---|---|---|---|-----|

| 4.5 | The L3 FASTBUS segments                          |   |   | • |   |   | • |   |   |   |   |   | 97  |

| 4.6 | The throughput of the event building system      | • |   |   |   |   |   |   | • |   | • | • | 105 |

| 5.1 | The CSR0 of the FT800 interface                  |   |   |   |   |   |   |   |   |   |   |   | 112 |

| 5.2 | The throughout of the new level-3 trigger system |   |   |   |   |   |   |   |   |   |   |   | 123 |

## **Introduction (French)**

La découverte en 1983 des bosons vecteurs  $Z^0$  et  $W^{\pm}$ , par les expériences UA1 at UA2 [1, 2, 3, 4] au CERN, a été une confirmation remarquable des prédictions du modèle electrofaible de Glashow, Salam et Weinberg [5, 6, 7, 8, 9].

Depuis 1989 le LEP (Large Electron Positron collider) produit des collisions  $e^+e^-$  qui permettent détudier les propriétés et des couplages du boson  $Z^0$ , grace à sa production directe, ainsi que la production de nouvelles particules. En attendant une augmentation de l'énergie des faisceaux pour atteindre la production de paires de W, plusieurs millions de  $Z^0$  ont déja été produits.

L'étude de la variation des sections efficaces en fonction de l'énergie dans le centre de masse pour chacun des canaux  $e^+e^- \rightarrow f^+f^-$  avec f=e,  $\mu$ ,  $\tau$ , q a permis de déterminer la masse  $m_Z$ , la largeur totale  $\Gamma_Z$ , les sections efficaces leptoniques, la section efficace hadronique au pic  $\sigma_{\rm had}^0$  ainsi que les différentes largeurs partielles  $\Gamma_{had}$ ,  $\Gamma_{ee}$ ,  $\Gamma_{\mu\mu}$ ,  $\Gamma_{\tau\tau}$  et par suite la largeur invisible  $\Gamma_{inv}$ .  $\Gamma_{inv}$  est la largeur partielle de désintégration en paires  $\nu\bar{\nu}$ . Les valeurs obtenues sont en très bon accord avec le modèle standard et montrent que le nombre de canaux de désintégration du  $Z^0$  est tel que l'Univers ne peut compter que trois types de neutrinos légers  $\nu_e$ ,  $\nu_\mu$ ,  $\nu_\tau$ .

Les mesures des assymétries angulaires avant-arrière de la charge des fermions produits dans les canaux  $e^+e^- \to f^+f^-$  (avec f=e,  $\mu$ ,  $\tau$ ) ainsi que la mesure de la polarisation des tau conduisent à la détermination de l'angle de mélange de Weinberg  $\sin^2\Theta_w$  qui est un des paramètres essentiels du modèle electrofaible.

Le  $Z^0$  se désintègre à 70% en une paire quark-antiquark. Il offre donc la possibilité de tester la chromodynamique quantique (CDQ), théorie de l'interaction forte incluse dans le modèle standard, et de mesurer à la masse du  $Z^0$  l'intensité du couplage quark-gluon  $\alpha_s(m_Z)$ .

Jusqu'à présent aucune particule supersymetrique ou composée n'a été mise en évidence dans la limite de masse cinématique permise. Le boson scalaire de Higgs, qui dans le modèle standard génère la masse des particules, n'a pas été observé, mais les résultats obtenus indiquent que sa masse devrait être supérieure à 65 Gev. Les désintégrations rares de Z, n'ont pas permis de mettre en évidence de nouvelles

#### interactions.

Avec les statistiques obtenus, et la mise en oeuvre de détecteurs de traces au silicium, la physique du quark b au LEP devient compétitive avec celle faite sur les autres machines. 20 désintégrations hadroniques ont lieu en paires  $b\bar{b}$  permettant d'étudier la spectroscopie des hadrons "beaux" et de mesurer le paramètre de mélange  $B^0$ - $\bar{B}^0$ . La mesure de la largeur partielle  $\Gamma_{b\bar{b}}$  du  $Z^0$  en paires  $b\bar{b}$  permet de déterminer le couplage du  $Z^0$  au quark b et de tester l'universalité du couplage des quarks. L'angle de mélange  $\sin^2\Theta_w$  du modèle électrofaible peut également être obtenu grace à la mesure des asymétries angulaires avant-arrière de la charge  $(A_{b\bar{b}})$  des paires  $b\bar{b}$ .

Le LEP est également un excellent collisioneur de photons, à l'énergie des paires de W les interactions photon-photon produiront la majeure partie des événements.

L'expérience L3 [10] est l'une des quatre expériences qui sont en fonctionnement depuis juillet 1989 auprès du collisioneur électron, positron du CERN. Elle a été optimisée pour la détection des électrons des photons et de muons. Le dispositif expérimental est constitué de plusieurs détecteurs disposés en couches cylindriques successives autour de l'axe du faisceau, ainsi que de deux bouchons situés aux extrémités du cylindre. En allant du point d'interaction vers l'extérieur on trouve:

- deux compteurs de luminosité en Germanate de Bismuth (BGO) mesurant la diffusion  $e^+e^- \rightarrow e^+e^-$  à petit angle 24.7  $mrad \le \theta \le 69.3 \ mrad$ .

- un détecteur de trace au silicium (SMD, Silicon Microvertex Detector) installé en 1993.

- un détecteur de trace et de vertex (TEC, Time Expansion Chamber) qui mesure la trajectoire, la charge et l'impulsion des traces chargées issues du point d'interaction.

- un calorimètre électromagnétique (ECAL) constitué de 10734 cristaux en BGO qui mesure l'énergie des électrons et des photons avec une résolution en énergie de 1.3% à E=45 GeV et 5% à E=100 MeV.

- un hodoscope de 30 compteurs à scintillation dont la bonne résolution en temps (< 1ns) permet de rejeter les muons cosmiques.

- un calorimètre hadronique (HCAL) constitué de quatre longueurs d'absorption d'uranium, instrumentées par des chambres proportionelles à fils. Il mesure l'énergie des hadrons avec une résolution de  $(55/\sqrt{E}+5)\%$

- un spectromètre à muons (MUCH) qui mesure l'impulsion des muons avec une précision de 2.5% à 45 GeV.

Tout cet appareillage est contenu dans un solénoide de 7800 t produisant un champ magnétique uniforme de 0.5 Tesla.

De 1989 à 1992 le LEP a fonctionné avec 4 paquets d'électrons et 4 paquets de positrons au rythme de 44982 croisements par seconde. Depuis septembre 1992 pour atteindre la luminosité nominale de  $1.5 \cdot 10^{31} cm^{-2}s^{-1}$  dans le LEP circulent 8 paquets d'électrons et 8 paquets de positrons (89964 croisements par seconde), qui entrent ainsi en collision toutes les  $11.116\mu sec$ . A chaque croisement des faisceaux le système de déclenchement et d'acquisition analyse les données produites, reconnait si une interaction  $e^+e^-$  s'est produite et décide de l'enregistrement de l'événement.

A lénergie du  $Z^0$ , lorsque la luminosité est de  $1.5 \ 10^{31} cm^{-2} s^{-1}$  le LEP produit  $0.45 \ Z^0$  par seconde, le système de déclenchement et d'acquisition doit sélectionner ces évènements parmi le bruit de fond produit par les interactions des faisceaux avec le gaz du tube à vide, les rayons cosmiques, l'électronique des détecteurs, l'activité de l'uranium du calorimètre hadronique.

Afin d'éffectuer cette sélection le système de déclenchement et d'acquisition est organisé en plusieurs niveaux:

- Le déclenchement de premier niveau utilise une logique cablée capable de prendre une décision en 11 μsec.

- Le déclenchement de deuxième niveau comporte 3 microprocesseurs.

- Le filtre de troisième niveau est constitué de 4 stations VAX.

- Le système d'acquisition central utilise le standard Fastbus.

Les deux premiers niveaux fonctionnent sur des données de faible résolution (10<sup>4</sup> canaux) obtenues par regroupement des capteurs. Le troisième niveau à accès à l'information complète (10<sup>5</sup> canaux de haute résolution).

A chaque croisement des faisceaux le système déclenche la numérisation des données résumées. Celles ci sont mémorisées dans les mémoires du niveau-2 pendant que le niveau-1 analyse l'événement. Si la décision est négative, l'électronique est remise à zéro. Si la décision est positive, les données principales sont numérisées, l'événement est construit au niveau de chaque détecteur et le niveau-2 est activé (temps de calcul  $\sim 2$  ms). Si la décision du niveau-2 est positive, les données principales, des détecteurs et les données résumées sont assemblées, l'événement est structuré, puis envoyé à l'une des stations VAX du niveau-3 (temps de calcul  $\sim 100$  ms).

Si la réponse du niveau-3 est positive l'événement est transféré dans une mémoire de la VAX7610. Un programme lit ces événements et les écrit sur bande ou les transfère vers les disques du centre de calcul de L3.

De 1989 à 1993 le système d'acquisition de L3 a permis de recueillir un total de plus de 1.5 millions de  $Z^0$ .

Le travail presenté dans ce mémoire est destiné à décrire l'architecture ainsi que les performances actuelles du système d'acquisition. En effet depuis 1989 le système a déja subi différentes améliorations.

Le premier chapitre est consacré à la description du dispositif expérimental de L3.

Le second chapitre décrit le système de déclenchement et d'acquistion.

Entre 1988 et 1990 j'ai participé a la conception et à la réalisation du système d'acquisition du calorimètre hadronique. Le troisième chapitre, présente donc l'aspect conceptuel et fonctionnel de l'acquisition de ce détecteur, la synchronisation et l'assemblage d'un événement lorsque le système est utilisé pour la calibration du calorimètre.

Le quatrième chapitre est consacré à la synchronisation et à l'assemblage des données provenants des différents détecteurs. ainsi qu'a la connection au filtre de troisième niveau.

Le dernier chapitre est consacré au filtre de troisième niveau qui a été modifié en 1993. Il décrit également les performances du système, et introduit les dévelopements en cours de réalisation.

## Reference

- [1] UA1 Collaboration, G.Arnison, et al.. Experimental Observation of Isolated Large Transverse Energy Electrons with Associated Missing Energy at  $\sqrt{s}$  = 540 GeV. Physics Letters B 122, pages 103–116, 1983.

- [2] UA1 Collaboration, G.Arnison, et al.. Experimental Observation of Lepton Pairs of Invariant Mass around 95 GeV/c<sup>2</sup> at the CERN SPS Collider. Physics Letters B 126, pages 398–410, 1983.

- [3] UA2 Collaboration, P.Bagnaia, et al.. Evidence for  $Z^o \rightarrow e^+e^-$  at the CERN  $p\bar{p}$  Collider. Physics Letters **B** 129, pages 130–140, 1983.

- [4] UA2 Collaboration, R.Ansari, et al.. Measurement of the Standard Model Parameters from a Antiquark pairs. Physics Letters B 186, pages 440–451, 1987.

- [5] S.L.Glashow. Partial-Symmetries of Weak Interactions. *Nuclear Physics* 22, pages 579–588, 1961.

- [6] S.L.Glashow, J.Ilipoulos, and L.Maiani. Weak Interactions with Lepton-Hadron Symmetry. *Physical Review D* 2, No. 7, pages 1285–1292, 1970.

- [7] S. Weinberg. A Model of Leptons. Physical Review Letters 19, No. 21, pages 1264–1266, 1967.

- [8] A.Salam and J.C.Ward. Electromagnetic and Weak Interactions. *Physics Letters* 13, No. 2, pages 168–171, 1964.

- [9] A.Salam. Elementary Particle Theory. Almquist and Wiksell, Sockolm, 1968.

- [10] L3 Collaboration, B.Adeva, et al.. The Construction of the L3 Experiment. Nuclear Instruments and Methods in Physics Research A 289, pages 35–102, 1990.

## Chapitre 1

## Le LEP et l'expérience L3

## 1.1 Le LEP

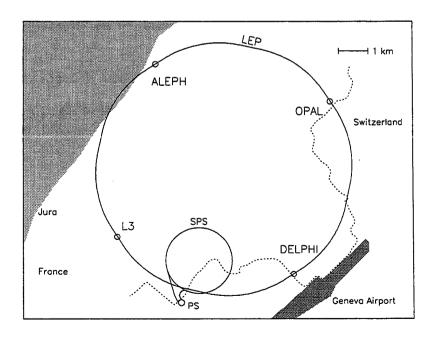

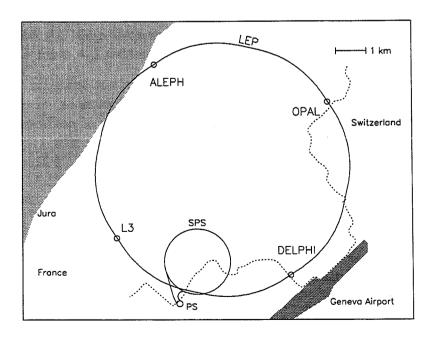

Le collisioneur Electron Positron (LEP) [1, 2] est installé dans un tunnel circulaire ayant une circonférence de 26.66 km. Le tunnel est creusé dans la molasse à une profondeur moyenne de 100m, entre les montagnes du Jura et le lac Leman, à la frontière Franco-Suisse (Figure 1.1).

Figure 1.1: Le LEP

Les électrons et les positons circulent en sens opposé dans un tube a vide. Plus de 3000 aimants dipolaires courbent les particules le long de leurs trajectoires circulaires et environ 2000 quadrupoles focalisent le faisceau. Aux points de collision la dimension du faisceau est de 200  $\mu m$  suivant la direction horizontale et de 10  $\mu m$  dans la direction verticale. Le construction du LEP prévoie plusieurs phases correspondant à un accroissement de l'énergie des faisceaux. La première phase d'exploitation de LEP a commencé en 1989. La table 1.1 présente quelques paramètres de LEP pour cette première phase.

Table 1.1: Principaux paramètres de LEP (Phase 1)

| Circonférence                   | 26658.883 m                         |

|---------------------------------|-------------------------------------|

| Rayon de courbure des dipoles   | 3096.175 m                          |

| Section horizontale du faisceau | $200 \ \mu m$                       |

| Section verticale du faisceau   | $10 \mu m$                          |

| Fréquence de révolution         | 11245 Hz                            |

| Nombre de paquets par faisceau  | 4/8                                 |

| Nombre de points de collision   | 4                                   |

| Nombre de cavités RF            | 128                                 |

| Frequence RF                    | 352.20904 MHz                       |

| Energy à l'injection            | 20 Gev                              |

| Energie maximum                 | $\approx 60 \text{ Gev}$            |

| Luminosity (3 mA par faisceau)  | $1.6 \times 10^{31} cm^{-2} s^{-1}$ |

Les deux faisceaux peuvent entrer en collision en 8 points disposés symétriquement le long de l'anneau du LEP. Quatre d'entre eux sont utilisés par des expériences appelées L3, ALEPH, OPAL et DELPHI. Celles-ci se trouvent respectivements situées aux points No. 2, 4, 6 et 8.

Les électrons et les positons sont groupés en *paquets* et accélerés de 20 GeV (énergie d'injection) à 45 GeV en 15 minutes environ. De 1989 à 1992 le LEP a fonctionné avec 4 paquets d'électrons et 4 paquets de positons, chaque paquet ayant une longueur d'environ 15 mm suivant la direction des faisceux. Depuis Octobre 1992 le nombre des paquets délectrons et de positons a été augmenté à 8 afin d'accroitre la luminosité de LEP.

## 1.2 Le Detecteur L3

#### 1.2.1 Introduction

Le détecteur L3 [3, 4] est le plus grand des quatre détecteurs en fonctionnement aupres du LEP. Il permet de mesurer l'impulsion et l'angle des muons, des

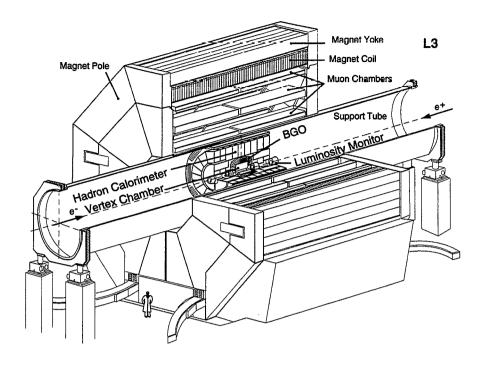

Figure 1.2: Shema du detecteur L3

électrons, et des photons, la position du vertex de l'interaction ainsi que l'energie des jets de hadrons. La Figure 1.2 représente le détecteur L3.

Le détecteur est installé à l'interieur d'un aimant, ses divers éléments sont positionnés à l'aide d'un tube d'acier de 4.45 m de diamètre et de 32 m de long. L'aimant solenoidal, de forme octoganale (16 m de diamètre et 12 m de long) est constitué de 6700 tonnes d'acier et d'une bobine en aluminium d'un poids de 1100 tonnes. Lorsque le courant est de 30338 A le champ magnétique atteint 0.5 T. A partir de la ligne de faisceau les principaux éléments du détecteur sont:

- Le détecteur central de trace.

- Le calorimètre électromagnetique.

- Les compteurs à scintillation.

- Le calorimètre hadronique.

- Le spectromètre à muon.

- Les moniteurs de luminosité.

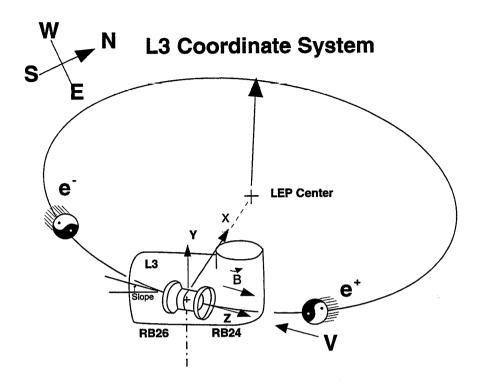

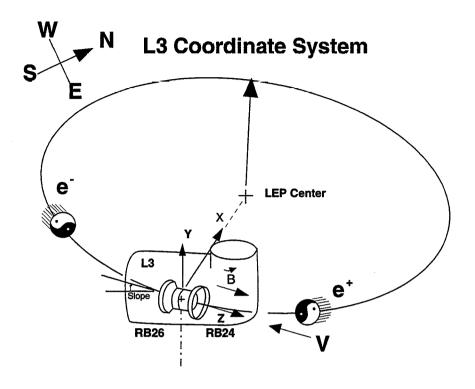

La Figure 1.3 indique le système de coordonnées utilisé dans L3.

Figure 1.3: Système de coordonnées utilisé dans L3

#### 1.2.2 Le détecteur central de trace

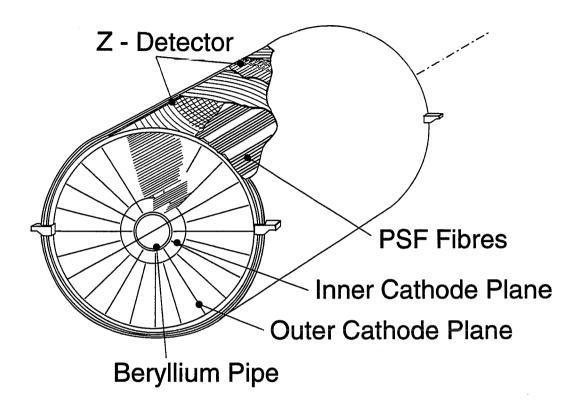

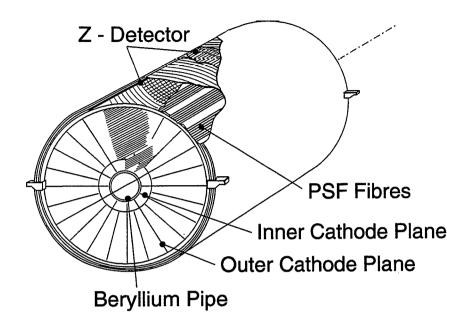

Le détecteur central de trace [5], shematisé sur la Figure 1.4, est constitué d'une chambre à dérive *Time Expension CHamber (TECH)* à faible vitesse de dérive,  $6 \mu m/ns$ , et d'une chambre proportionelle, chambre-Z, permettant de:

- mesurer avec précision la position et l'angle des traces des particules chargées.

- mesurer l'impulsion transverse et identifier la charge des particules jusqu'à une impulsion de 50 GeV /c.

- reconstruire le point d'impact et l'angle des particules chargées à la face d'entrée du calorimètre électromagnétique.

- déterminer la multiplicité des traces provenant du vertex au niveau du système de déclenchement.

- reconstruire la position du point d'interaction ainsi que les vertex secondaires des particules ayant une durée de vie supérieure à  $10^{-13}s$ .

La TECH comprend deux cylindres concentriques. La chambre intérieure est constituées de 12 secteurs équipés de 8 fils chacun, la chambre extérieure étant composé

Figure 1.4: Le détecteur central de trace

de 24 secteurs incluant 54 fils. Deux types de fils sont utilisés, les fils d'anodes et les fils de division de charge, ils déterminent respectivement la cordonnée  $\phi$  et la coordonnée selon l'axe Z. De chaque coté de la région d'amplification des groupes de fils de grille permettent de résoudre l'ambiguité gauche droite. Le mélange gazeux permettant d'obtenir une vitesse de dérive lente est constitué de 80%  $CO_2$  et de 20%  $C_4H_{10}$ , il est utilisé à une pression de 1.2 bar. Les signaux des anodes sont numérisés par des convertiseurs analogiques digitaux FADC. Pour une trace de grand  $P_T$  (45 GeV) les 62 fils de la TECH permettent d'obtenir une résolution simple de 60  $\mu m$  en moyenne.

Un ruban de 143 fibres scintillantes en plastic (PSF) paralèlle à l'axe du faisceau est utilisé pour la calibration de la vitesse de dérive de la TECH.

Sur la surface extérieure de la TECH la chambre-Z est constitué de deux chambres proportionelles cylindriques, à lecture par la cathode. Elle permettent une mesure plus précise de la coordonnée Z suivant l'axe du faisceau. La chambre Z fonctionne avec un mélange gazeux composé de 80% d'Argon et de 20% de  $CO_2$ . La chambre Z a une résolution simple comprise entre  $300~\mu m$  et 1 mm suivant l'angle polaire de la trace.

## 1.2.3 Le Calorimètre Electromagnétique

Le calorimètre électromagnétique (ECAL) [6] entoure le détecteur central de traces, il permet de mesurer l'énergie et l'angle des photons et des électrons produits lors des collisions  $e^+e^-$ . Il est constitué d'environ 11000 cristaux de BGO (Oxyde de Germanate Bismuth,  $Bi_4Ge_3O_{12}$ ) Figure 1.5. Le BGO est particulièrement bien adapté à la construction d'un calorimètre compact, car il a une faible longueur de radiation, une grande longueur d'interaction et des propriétés chimiques stables. De plus le BGO a une bonne résolution en énergie, (4% à E=200 MeV et 1.3% à E=45 GeV [7]) et une excellente linéarité. Chaque cristal est un tronc de pyramide ayant une section d'entrée de  $2 \times 2cm^2$  et une section de sortie de  $3 \times 3cm^2$ . Sa longueur et de 24 cm, soit 22 longueurs de radiations. Deux photodiodes associées à une électronique linéaire détectent la lumière scintillante du BGO.

Figure 1.5: Le Calorimètre Electromagnétique

Le calorimètre électromagnétique est composé d'un tonneau (EB) et de deux bouchons (EC) précedés de chambres à dérive (FTC). Le tonneau est constitué de 7680 cristaux, organisés en 48 anneaux de 160 cristaux, couvrant une région angulaire ente 42° et 138°. Le tonneau est mécaniquement divisé en deux demi tonneau symmétriquement par rapport à l'axe  $\theta = 90^\circ$ , ceci a permis de calibrer chacun des cristaux dans un faisceau d'électrons. Les deux bouchons étendent la couverture angulaire jusqu'à 12° et 168°, chacun contient 1536 cristaux, il furent installés durant l'arrêt hivernal 1990-1991 du LEP.

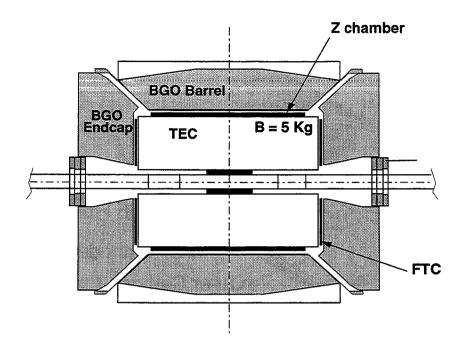

## 1.2.4 Les Compteurs à Scintillation

Les compteurs à scintillation [8, 9] sont situés entre les calorimètres électromagnétique et hadronique (Figure 1.6). Les compteurs du tonneau couvrent une région angulaire allant de 34° à 146° par rapport à la direction du faisceau. Ils sont utilisés dans un déclenchement de multiplicité permettant de sélectionner les événements hadroniques et pour distinguer les di-muons des muons cosmiques en mesurant la différence de temps de vol entre des compteurs opposés. Celle-ci est de 6ns pour les muons cosmique et zéro pour les paires de muon.

Les 30 compteurs, constitués de 1 cm de scintillateur plastique, sont courbés afin de s'adapter à la forme du tonneau du calorimètre hadronique Chaque compteur est équipé d'un photomultiplicateur à chaque extrémité. Le temps et l'amplitude du signal sont analysés à l'aide de convertisseurs digitaux TDC et ADC.

Figure 1.6: Coupe de la partie interne du détecteur L3

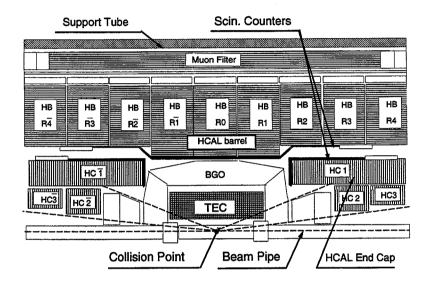

## 1.2.5 Le Calorimètre Hadronique

A l'extérieur du calorimètre électromagnétique, après les scintillateurs, se trouve le calorimètre hadronique (HCAL) [10, 11], Figure 1.6. Il permet de mesurer l'énergie des hadrons provenants des interactions  $e^+e^-$  en mesurant, avec l'aide du BGO, l'energie totale. Il agit également comme un filtre à muon.

Le HCAL contient trois parties: Le tonneau (HB), les bouchons (HC) et le filtre

à muon (MF). Le tonneau est divisé en 9 anneaux de 16 modules chacun. Le rayon intérieur est de 885 mm pour les trois anneaux centraux et de 979 mm pour les six autres. Il couvre une région angulaire allant de 35° à 145° suivant la direction  $\theta$ .

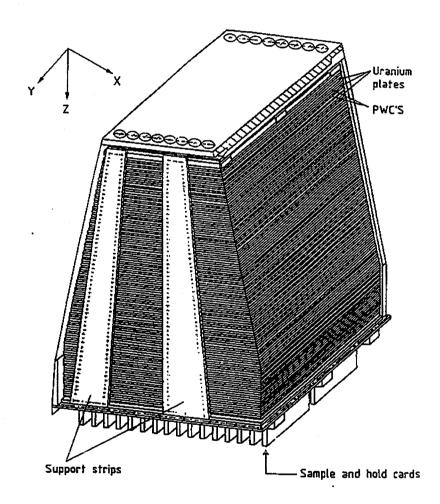

Figure 1.7: Module du calorimètre hadronique

Les modules sont constitués d'empilements de plaques d'absorbeur en uranium appauvri et de chambres proportionnelles. La Figure 1.7 montre un module. Les plans de chambre sont organisés afin que les fils d'un plan soient perpendiculaires aux fils du plan suivant. Les chambres ayant les fils parallèles à la direction du faisceau sont appelées chambres P(hi), les autres sont appelées chambres T(heta). Le mélange gazeux est constitué de 80% d'Argon et de 20%  $CO_2$ , il donne un gain tres élevé ( $\approx 10^4$  à une tension de 1.6 kV). La résolution totale en energie est de 10% pour des désintégrations hadroniques au  $Z^0$ .

Chaque bouchon est constitué de trois anneaux (HC1, HC2 et HC3 Figure 1.6), chaque anneau est divisé en deux parties afin de faciliter l'installation. Les modules

des bouchons ont une structure semblable à ceux du tonneau, mais il ont des tailles différentes et comportent moins de plans de chambre. Les deux bouchons étendent la couverture angulaire du HCAL entre 5.5° et 174.5°. Les signaux recuillis par les fils d'anode sont amplifiés et numérisés à l'aide de convertiseurs analogiques digitaux Fastbus.

Grace à la densité de l'uranium, l'ensemble des deux calorimètres (ECAL et HCAL) fournissent environ 6 à 7 longueur d'absorbtion. Le filtre à muons est installé sur la face interne du tube support ajoutant environ 1 longueur d'absorbtion supplémentaire. Il améliore l'efficacité de détection des muons en réduisant la pénétration des muons venant de la désintégration des pions. Le filtre à muons est constitué de 8 octants, chacun d'eux étant composé de six plaques de 1 cm de laiton séparés par des plans de chambres proportionelles. Les chambres utilisent le même mélange gazeux que le tonneau du HCAL et fonctionnent à une tension de 1.8 kV.

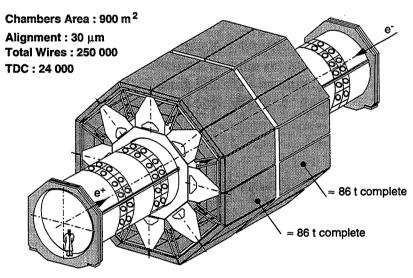

## 1.2.6 Le Spectromètre à Muons

Le système de chambres à muons [12, 13] est installé à l'extérieur du tube support. Il est composé de deux roues, chacune étant constituée de huit modules appelés octants. La Figure 1.8 donne une vue globale du Spectromètre à Muons.

Figure 1.8: Vue globale du Spectromètre à Muon

Figure 1.9: Shema d'un octant du système de chambres à muon

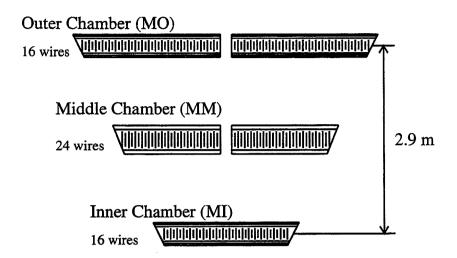

Chaque octant (Figure 1.9) est constitué de 5 chambres (P) à dérive: une chambre interne (MI), deux chambres intermédiaires (MM) et deux chambres externes (MO). Elles mesurent les coordonnées des traces dans le plan de déflexion.

Chacune des chambres MI et MO est couverte par 2 chambres-Z dont les fils sont disposés perpendiculairement à la direction du faisceau afin de mesurer la coordonnée suivant l'axe Z. Les signaux des chambres P et Z sont envoyés vers des discriminateurs et des TDC Fastbus permettant de mesurer les temps de dérive, par rapport au signal de référence généré lors du croisemenent des faisceaux.

Le système de chambres à muon est destiné à mesurer l'impulsion des muons avec une precision d'environ 2.5% à 45 GeV. Le mélange gazeux est constitué de 61.5% d'Argon et de 38.5% Ethane pour les chambres-P, de 91.5% Argon et 8.5% de Methane pour les chambres-Z. La région angulaire couverte est  $36^{\circ} \le \theta \le 144^{\circ}$ . Elle sera étendue dans les régions avant et arrière en 1994 et 1995.

#### 1.2.7 Les Moniteurs de Luminosités

Les deux moniteurs de luminosité [14, 15] sont installés symmétriquement de part et d'autre du point d'interraction à une distance  $z=\pm 2765mm$ , Figure 1.2. Ils permettent de calculer la luminosité du faisceau avec une précision de l'ordre de 1% en mesurant la diffusion élastique  $e^+e^- \rightarrow e^+e^-$  (Bhabha) à petit angle. Chaque moniteur couvre une région angulaire comprise entre 24.7 mrad et 69.3 mrad. Il est

composé d'un calorimètre électromagnétique en BGO et d'un ensemble de chambres proportionelles placé devant le BGO.

Celles-ci ont été remplacé en 1993 par des détecteurs de traces au silicium permettant d'avoir une meilleure définition du volume fiduciel.

## Reference

- [1] **LEP Design Report (Vol. II): The LEP Main Ring.** European Organization for Nuclear Research (CERN), CERN-LEP 84-01, June 1984.

- [2] I.Wilson and H.Henke. The LEP Main Ring Accelerating Structure. European Organization for Nuclear Research (CERN), LEP Division, CERN 89-09, November 1989.

- [3] L3 Collaboration, B.Adeva, et al.. The Construction of the L3 Experiment. Nuclear Instruments and Methods in Physics Research A 289, pages 35–102, 1990.

- [4] L3 Collaboration. Letter of Intent. European Organization for Nuclear Research (CERN), CERN/LEPC 82-5, March 1982.

- [5] D.N.Ren. The L3 Vertex Chamber Development and Infrastructure. PhD thesis, Swiss Federal Institute of Technology (ETH), Zurich, 1990.

- [6] L3 Collaboration, F.Ferroni, et al.. The L3 BGO Electromagnetic Calorimeter at LEP. Nuclear Physics B 23A, pages 100–106, 1991.

- [7] Jorg Wenninger Measure de paramètres électrofaibles du  $Z^0$  avec la réaction  $e^+e^- \rightarrow e^+e^-(\gamma)$ . PhD thesis, Université de Genéve. Geneve, 1992.

- [8] U.Uwer. Aufbau und Eichung der Szintillationszaehler des L3-Experimentes. Diploma thesis. Rheinisch-Westfälische Technische Hochschule (RWTH), Aachen, 1990.

- [9] U.Uwer. The L3 scintillation counter system. L3 Collaboration, L3 Note 1400, March 1991.

- [10] L3 Collaboration, A.Arefrev, et al.. Proportional Chambers for the Hadron Calorimeter of the L3 Experiment. Nuclear Instruments and Methods in Physics Research A 275, pages 71–80, 1989.

- [11] L3 Collaboration. **Hadron Calorimetry in the L3 Detector**. Nuclear Instruments and Methods in Physics Research A 302, pages 53–62, 1991.

- [12] L3 Collaboration, B.Adeva, et al.. Muon Detector in the L3 Experiment at LEP. Nuclear Instruments and Methods in Physics Research A 277, pages 187–193, 1989.

- [13] Y.Peng. The Muon Spectrometer of the L3 Detector at LEP. PhD thesis, University of Amsterdam, 1988.

- [14] H.Meinhard. Precise Measurement of the Luminosity at LEP. In J.R.Sanford, editor, 26th International Conference on High-energy Physics, Dallas, Augest 1992.

- [15] F.Linde. Luminosity Measurement at LEP. In K.Bos and B. van Eijl, editors, Workshop on detector and event simulation in high energy physics Monte Carlo 91, Amsterdam, April 1991.

## Introduction

The study of the constituents of matter and the fundamental interactions requires higher and higher particle energy. Most of current searches in elementary particle physics are based on experiments of collision between high energy particles (electrons, protons, and their anti-particles). The *Large Electron Positron* collider (LEP) which started to operate in August 1989 provides a unique solution for studying the electromagnetic and weak interactions because the initial state is well defined.

L3 is one of the four experiments installed on the LEP which is situated at CERN (European Organization for Nuclear Research). The L3 experiment was designed to have an excellent energy resolution measuring electrons, muons and photons. Due to the fast colliding rate of the LEP, a large number of detector cells generate a large amount of data so that its data acquisition system becomes very important. A fast but flexible trigger system is also required to select the interesting events from among the various sources of background.

This thesis describes the trigger and data acquisition system of the *L3 experiment*. There are five chapters. The *LEP collider* and the *L3 detector* are introduced in the first one. The structure of the L3 trigger and data acquisition system is described in the second chapter. Then the other three chapters explain in detail the author's contributions respectively on the *Hadron Calorimeter readout system*, the *L3 event building system* and the *third level trigger system*.

# **Chapter 1**

# LEP and the L3 Experiment

# 1.1 The LEP

The Large Electron Positron (LEP) collider [1, 2] is built in a tunnel of 26.66 km circumference. The tunnel runs about 100 meters deep under the plain between the Jura mountains and the Geneva lake at the border of France and Switzerland (see Figure 1.1).

Figure 1.1: The map of LEP

Electrons and positrons circulate in opposite directions inside a beam pipe. More than 3000 bending dipoles hold the particles on their circular orbits, and over 2000 quadrupoles focus the beam. In each interaction points, the beam dimension is  $200~\mu m$  in the horizontal direction and  $10~\mu m$  in the vertical direction. The construction of LEP is planned to evolve through several phases corresponding to increasing beam energy. The first phase of LEP has been operating since 1989. Table 1.1 exhibits some parameters of LEP in the first phase.

Table 1.1: The major parameters of LEP (Phase 1)

| Circumference                       | 26658.883 m                         |

|-------------------------------------|-------------------------------------|

| Dipole bending radius               | 3096.175 m                          |

| Horizontal rms beam radius          | $200 \ \mu m$                       |

| Vertical rms beam radius            | $10 \mu m$                          |

| Revolution frequency                | 11245 Hz                            |

| Number of bunches per beam          | 4/8                                 |

| Number of interaction points        | 4                                   |

| Number of RF cavities               | 128                                 |

| RF frequency                        | 352.20904 MHz                       |

| Injection energy                    | 20 Gev                              |

| Maximum beam energy                 | $\approx$ 60 Gev                    |

| Peak luminosity (3 mA beam current) | $1.6 \times 10^{31} cm^{-2} s^{-1}$ |

The two beams cross each other at 8 places symmetrically distributed along the LEP ring, where 4 of them are used for the experiments named L3, ALEPH, OPAL and DELPHI. They are respectively located in the point No.2, 4, 6 and 8.

Electrons and positrons are grouped in *bunches* and accelerated in the LEP from 20 GeV (at the injection time) to 45 GeV within about 15 minutes. At the beginning, LEP was running with 4 bunches of electrons and 4 bunches of positrons, where each bunch has a length of about 15 mm in the beam running direction. To improve the luminosity, the number of bunches was increased to 8 in October 1992.

## 1.2 The L3 Detector

#### 1.2.1 Introduction

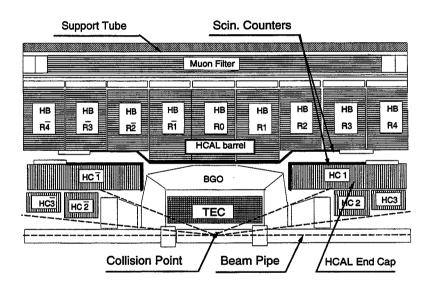

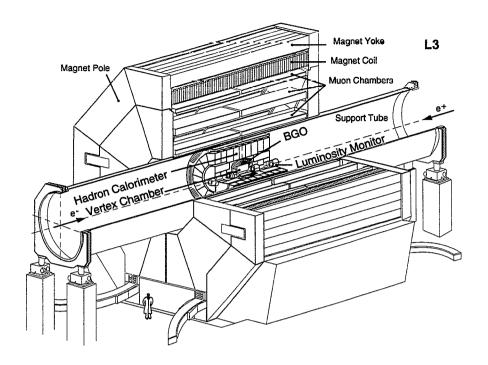

The L3 detector [3, 4] is the largest of the four detectors at LEP, it was designed as a general purpose detector to measure both momentum and direction of muons, electrons and photons with high resolution as well as the vertices and the energy flow of hadronic jets. Figure 1.2 gives a schematic view of the L3 detector.

Figure 1.2: The perspective view of the L3 detector

The entire detector resides inside a magnet and is supported by a steel tube with 4.45 m inner diameter and 32 m long. The octagonal solenoid magnet (16 m diameter and 12 m long) consists of a 6700 tons yoke of low carbon steel and a huge aluminum coil weighing about 1100 tons. When the current is 30338 A, the magnetic field is 0.5 Tesla. Starting from the beam line the major components of the L3 detector are:

- The central track detector.

- The electromagnetic calorimeter.

- The scintillation counters.

- The hadron calorimeter.

- The muon spectrometer.

- The luminosity monitors.

Figure 1.3 shows the coordinate system of the L3 detector corresponding to the LEP ring.

Figure 1.3: The L3 coordinate system

#### 1.2.2 The Central Track Detector

The central track detector [5], as shown in Figure 1.4, consists of a **Time Expansion Chamber** (TEC, TECH) with low drift time velocity 6  $\mu$ m/ns and a proportional Z-Chamber, it was designed with the following goals:

- Measure precisely the direction and the location of charged particle tracks.

- Measure the transverse momentum and the sign of the charge for particles with momentum up to 50 GeV/c.

- Reconstruct the impact point and the direction for charged particles at the entrance of the *electromagnetic calorimeter*.

- Determine the track multiplicity originating from the interaction region at the trigger level.

- Find the interaction point and secondary vertices for particles with lifetime greater than  $10^{-13}s$ .

The TEC is composed of two concentric cylinders. The inner TEC consists of 12 sectors with 8 wires each and the outer TEC has 24 sectors with 54 wires each. Two

Figure 1.4: The central track detector

types of wires, sense anode wires and charge division wires, determine respectively the  $\phi$  and the Z coordinates. Additionally, groups of five grid wires on each side of the amplification region are used to solve the left-right ambiguity. The gas mixture of 80%  $CO_2$  and 20%  $C_4H_{10}$  is used at a pressure of 1.2 bar. The sense wire signals are digitized with analog digital converters (FADC). For a high PT track (45 GeV) the 62 wires provide a single track resolution of 60  $\mu m$  in average.

A plastic scintillating fiber (PSF) ribbon, with 143 fibers running along the beam direction, are used for the calibration of the TEC.

On the outer shell of the TEC, the Z detector is composed of two cylindrical proportional chambers with cathode strip readout. It provides a more precise measurement of the position along the beam direction. The Z chamber is operated with a gas mixture of 80% Argon and 20%  $CO_2$ . The Z-chamber has a single track resolution ranging from 300  $\mu m$  to 1 mm following the polar angle of the track.

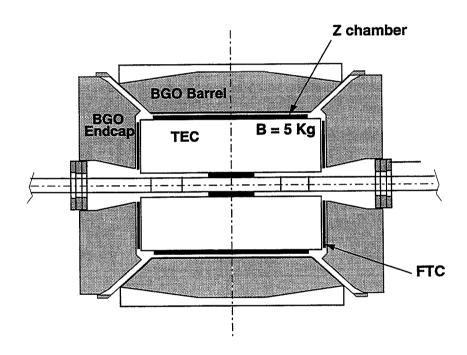

# 1.2.3 The Electromagnetic Calorimeter

The *Electromagnetic Calorimeter* (ECAL, BGO) [6] surrounds the central track detector to measure the energy and the position of photons and electrons produced by the  $e^+e^-$  interactions. It is made up of about 11000 BGO (Bismuth Germanate

Figure 1.5: The electromagnetic calorimeter

Oxide,  $Bi_4Ge_3O_{12}$ ) crystals, see Figure 1.5. BGO is a particularly attractive material to build a compact calorimeter, for its short radiation length for photons and electrons, large nuclear interaction length and stable chemical properties. Furthermore, BGO has very good intrinsic energy resolution (about 4% at 200 MeV and 1.3% at 45 GeV [7]) and excellent linearity. Each crystal is a truncated pyramid with a cross-section of  $2 \times 2cm^2$  at the inner end and  $3 \times 3cm^2$  at the outer end. Its length is 24 cm, corresponding to 22 radiation lengths. Two silicon photodiodes and associated linear electronics detect the scintillation light produced by each BGO crystal.

The electromagnetic calorimeter is composed of a cylindrical barrel (EB), two endcaps (EC) with tracking chambers (FTC) in front. The barrel is made of 7680 BGO crystals, arranged in 48 rings of 160 crystals each, which covers the polar angular region from 42° to 138°. The barrel is mechanically divided into two half-barrels symmetrically around  $\theta = 90^\circ$ , it allowed the calibration of each crystal in a direct electron beam. The two endcaps extend the polar angular coverage to 12° and 168° and contain 1536 crystals in each. The endcaps were installed during 1990-1991 LEP shutdown.

#### **1.2.4** The Scintillation Counters

The scintillation counters [8, 9] are located between the electromagnetic and hadronic calorimeters (Figure 1.6). They are used to build a multiplicity trigger for

hadronic events and to discriminate di-muon events from cosmic muon by measuring the time-of-flight difference between opposite scintillation counters. The time difference is 6 nsec for cosmic ray background and zero for the muon pairs.

The 30 counters, made of 1 cm thick plastic scintillator are bent to suit the shape of the hadron calorimeter barrel. Each counter has one phototube at each end. The time and the amplitude are read out by high precision TDC and ADC. The counters cover the polar angular region from 34° to 146° with respect to the beam line.

Figure 1.6: The cutaway side view of inner L3 detector

#### 1.2.5 The Hadron Calorimeter

Surrounding the ECAL is the *Hadron Calorimeter* (HCAL) [10, 11], see Figure 1.6. It measures the energy of hadrons emerging from the  $e^+e^-$  interactions by the total absorption technique, together with BGO crystals. It acts also as a muon filter.

The HCAL contains three parts: the barrel part (HB), the forward-backward part (endcaps, HC) and the muon filter part (MF). The HB part is split into 9 ring with 16 modules in each ring. The inner radius is 885 mm for the central three rings (long modules) and 979 mm for the other six rings (short modules). It covers a range of  $35^{\circ}$  to  $145^{\circ}$  in the  $\theta$  direction.

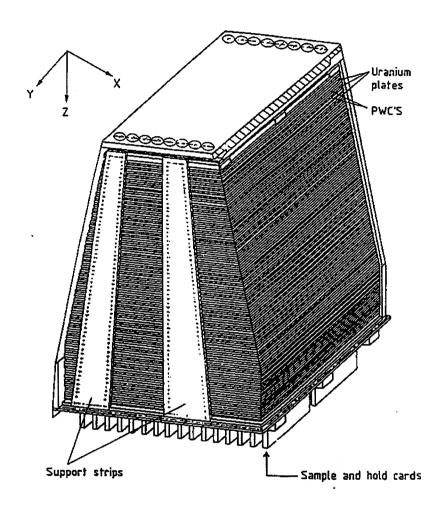

The modules are constructed with depleted uranium absorber plates sandwiched alternatively with layers of proportional chambers. Figure 1.7 shows a HB module.

The chamber layers in each module are arranged so that the orientation of the wires in one chamber layer are perpendicular to those in the next chamber layer. The chambers with wires along the beam direction are called P(hi) chambers, while the other chambers are called T(heta) chambers. The working gas is a mixture of 80% Argon and 20%  $CO_2$ , it has a very large gain coefficient ( $\approx 10^4$  under the 1.6 kV working voltage). The total energy resolution is 10% for hadronic decays of  $Z^0$ .

Figure 1.7: Assembly of the HCAL module

Each endcap consists of three rings (HC1, HC2 and HC3, see Figure 1.6), each ring is divided into two half rings to provide easy installation. The modules of the endcaps have a similar structure to the barrel modules but with smaller size and less chamber layers. Both endcaps together extend the angular coverage to a span of 5.5° to 174.5°.

Due to the high density of the uranium, the combined calorimeters (ECAL and HCAL) provide about 6-7 nuclear absorption length. The muon filter is mounted

on the inside wall of the support tube and adds 1.03 absorption length to the barrel HCAL. It increases the muon detection efficiency by reducing punch-through. The muon filter contains 8 identical octants, each made of six 1 cm thick brass absorber plates interleaved with five layers of proportional chambers and followed by five 1.5 cm thick absorber plate matching the circular shape of the support tube. The chambers use the same gas mixture as the HCAL barrel under 1.8 kV working voltage.

The FASTBUS digitizers are used to produce the data from all of the three HCAL parts.

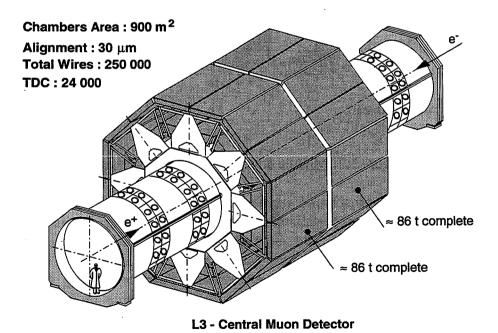

#### 1.2.6 The Muon Spectrometer

The *Muon Chambers* (MUCH) [12, 13] is located outside of the support tube. It is divided into two wheels, each composed of eight modules called octants. Figure 1.8 gives an overview of the whole muon spectrometer.

L3 - Central Muon Detector

Figure 1.8: The overview of the muon spectrometer

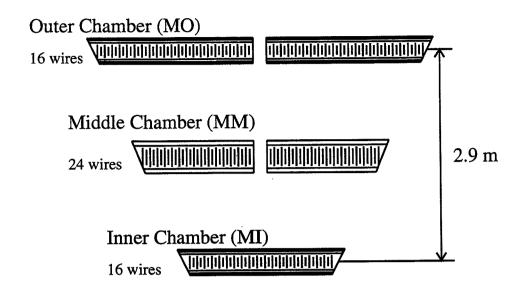

Each octant (see Figure 1.9) is composed of five Precision (P) drift chambers: one inner chamber (MI), two middle chambers (MM) and two outer chambers (MO). They measure the track coordinates in the bending plane. In addition, each of the MI and MO chambers is covered by 2 Z-chambers (respectively called II, IM on MI chamber and OO, OM on MO chamber) with wires perpendicular to the beam direction to measure the Z coordinate. The signals from P and Z chambers are sent to discriminators and FASTBUS time digitizers allowing to measure the drift time in comparison with the beam crossing signal.

Figure 1.9: The end view of one muon octant

The MUCH is designed to measure muon momenta with a momentum precision of about 2.5% at 45 GeV. The gas mixture is 61.5% Argon and 38.5% Ethane in the P-chambers, and 91.5% Argon and 8.5% Methane in the Z-chambers. The angular coverage is  $36^{\circ} \leq \theta \leq 144^{\circ}$ . It will be extended in the forward-backward region in 1994 and 1995.

#### 1.2.7 The Luminosity Monitors

The two luminosity monitors [14, 15], situated symmetrically on each side of the interaction point, at  $z=\pm 2765mm$ , are shown in Figure 1.2. They provide beam luminosity information with about 1% precision by using small angle  $e^+e^- \rightarrow e^+e^-$  (Bhabha) scattering events. Each monitor is composed of a cylindrical BGO electromagnetic detector and a set of proportional chambers.

In 1993 the chambers were replaced by silicon detectors allowing to have a better definition of the fiducial volume. Each monitor covers the forward or backward polar angle between 24.7 *mrad* and 69.3 *mrad*.

#### Reference

[1] **LEP Design Report (Vol. II): The LEP Main Ring.** European Organization for Nuclear Research (CERN), CERN-LEP 84-01, June 1984.

- [2] I.Wilson and H.Henke. The LEP Main Ring Accelerating Structure. European Organization for Nuclear Research (CERN), LEP Division, CERN 89-09, November 1989.

- [3] L3 Collaboration, B.Adeva, et al.. The Construction of the L3 Experiment. Nuclear Instruments and Methods in Physics Research A 289, pages 35-102, 1990.

- [4] L3 Collaboration. Letter of Intent. European Organization for Nuclear Research (CERN), CERN/LEPC 82-5, March 1982.

- [5] D.N.Ren. The L3 Vertex Chamber Development and Infrastructure. PhD thesis, Swiss Federal Institute of Technology (ETH), Zurich, 1990.

- [6] L3 Collaboration, F.Ferroni, et al.. The L3 BGO Electromagnetic Calorimeter at LEP. Nuclear Physics, B 23A, pages 100–106, 1991.

- [7] Jorg Wenninger Measure de paramètres électrofaibles du  $Z^0$  avec la réaction  $e^+e^- \rightarrow e^+e^-(\gamma)$ . PhD thesis, Université de Genéve. Geneve, 1992.

- [8] U.Uwer. Aufbau und Eichung der Szintillationszaehler des L3-Experimentes. Diploma thesis. Rheinisch-Westfälische Technische Hochschule (RWTH), Aachen, 1990.

- [9] U.Uwer. The L3 scintillation counter system. L3 Collaboration, L3 Note 1400, March 1991.

- [10] L3 Collaboration, A.Arefrev, et al.. Proportional Chambers for the Hadron Calorimeter of the L3 Experiment. Nuclear Instruments and Methods in Physics Research A 275, pages 71–80, 1989.

- [11] L3 Collaboration. **Hadron Calorimetry in the L3 Detector**. *Nuclear Instruments and Methods in Physics Research A* **302**, pages 53–62, 1991.

- [12] L3 Collaboration, B.Adeva, et al.. Muon Detector in the L3 Experiment at LEP. Nuclear Instruments and Methods in Physics Research A 277, pages 187–193, 1989.

- [13] Y.Peng. The Muon Spectrometer of the L3 Detector at LEP. PhD thesis, University of Amsterdam, 1988.

- [14] H.Meinhard. Precise Measurement of the Luminosity at LEP. In J.R.Sanford, editor, 26th International Conference on High-energy Physics, Dallas, August 1992.

- [15] F.Linde. Luminosity Measurement at LEP. In K.Bos and B. van Eijl, editors, Workshop on detector and event simulation in high energy physics Monte Carlo 91, Amsterdam, April 1991.

# Chapter 2

# The L3 Trigger and Data Acquisition System

## 2.1 Introduction

The aims of the L3 Trigger and Data Acquisition (DAQ) system [1, 2, 3, 4, 5] are to select and record the events which have particles coming from the  $e^+e^-$  interaction vertex.

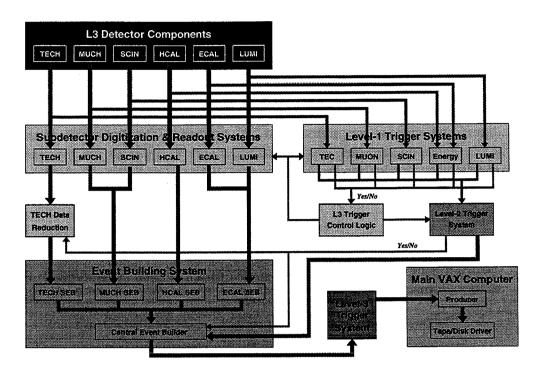

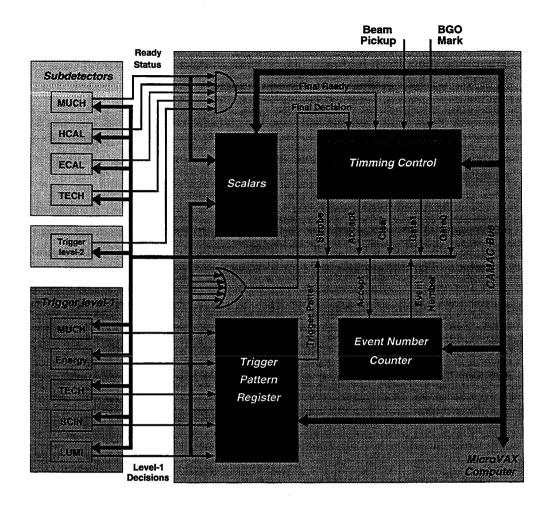

The system is achieved by three levels of trigger for the event selection, four subdetector DAQ systems for the signal digitization and the data readout as well as a two level event building system for the data collection. To insure good efficiency, each trigger level has redundant selection criteria which are combined in a logical OR to make the decision. The system is shown in Figure 2.1.

The detector signals provide two data streams. The coarse data are used by the level-1 and level-2 trigger systems to select events. The level-1 trigger decision is made within  $11.1/22.2~\mu sec$  which is the time between two beam crossings. The precise data are produced by the subdetector DAQ systems only when the event is selected by the first level trigger. By design the only deadtime in the system is introduced during the digitization and readout of the precise data which need at least  $500~\mu sec$  per event. The second level trigger system collects the trigger data and uses them to reject the background event which accepted by the level-1 trigger.

At the event building stage, the main data stream and the trigger data stream are integrated by the event builders according to the level-2 trigger selection. The events accepted by the second level trigger are sent to the third level trigger system for the final selection. The level-3 trigger selection is based on the online reconstruction by using the precise data. The selected events are transferred to the online VAX computer

Figure 2.1: The structure of the L3 trigger and DAQ system

for data monitoring and storage.

In order to synchronize different parts of the system, a trigger control logic provides the synchronization signals as well as the event number which is used to assemble the data from the different subdetectors and the trigger system at the event building level.

The different parts of the L3 trigger and data acquisition system are briefly described in the following sections.

# 2.2 The First Level Trigger System

In the first level, there are five subtriggers based on the signals from the calorimeters, the luminosity monitors, the TEC chambers, the scintillation counters and the muon spectrometer respectively. They use the coarse trigger data from the detector to make the decision at each beam crossing. Since the LEP collision rate is 45/90 kHz, the level-1 trigger decisions have to be made within  $22.2/11.1 \, \mu sec$ . Both the trigger raw data and the decisions are sent to the *level-2 trigger system*.

#### 2.2.1 The Calorimeter Trigger

The *calorimeter trigger* [6, 7] is designed to select events with energy in the electromagnetic and hadronic calorimeters as well as in the luminosity monitors, it is also called the *energy trigger*. The analog sum signals from BGO crystals of both ECAL barrel and endcaps are grouped into 512 channels. The *luminosity monitors* provide 32 signals. In the same way, the HCAL analog sum signals are grouped into 384 channels. The signals from the 928 channels, in total, are digitized and converted into energy depositions. An event is selected if one of the following conditions is fulfilled.

#### • Total energy trigger:

The following thresholds are used for the energy coming from different layers of the calorimeters.

- 1. Total energy from all calorimeters layers is larger than 20 GeV.

- 2. Total energy from barrel of BGO and Hadronic layers is more than 15 GeV.

- 3. Total energy from both barrel and end cap BGO is above 20 GeV.

- 4. Total energy from barrel BGO is not less than 10 GeV.

#### • Cluster trigger :

The trigger cells from the different detector layers (ECAL and HCAL) in the same  $\theta$  and  $\phi$  coordinates are defined as a **cluster**. The cluster trigger condition is that the sum of energy in one cluster is above 7 GeV. The TEC trigger information allows to use a lower threshold (3 GeV).

#### • Hit counting trigger:

At least two trigger cells have recorded energy with more than 5 GeV.

#### • Single photon trigger:

The energy of a BGO cluster is bigger than 80% of the total energy from the whole electromagnetic calorimeter.

#### • Luminosity trigger:

More than 15 GeV in both luminosity monitors or one monitor energy above 25 GeV and the other not less than 5 GeV.

#### • Single tag trigger:

The energy from one of the luminosity monitors is above 30 GeV. It is used to monitor the luminosity trigger efficiency.

The *calorimeter trigger* is implemented with CAMAC modules. It uses the Fast Encoding and Readout ADC (FERA) to digitize the analog sum signals from the calorimeters and the small angle luminosity monitors.

#### 2.2.2 The TEC Trigger

The **TEC trigger** [8] is used to select events with charged particle tracks. It is used as a backup trigger for dimuon and **energy trigger** and allows to trigger on two photon events. The decision is obtained in the following steps.

- 1. Digitize the analog wire signals (14  $\times$  24) of the outer TEC to produce a hit pattern in the projection normal to the beam axis ( $R_{\phi}$ ).

- 2. Search for tracks from the hit pattern

- 3. Make the trigger decision based on the total number of tracks and the total number of coplanar pairs of tracks.

The system is based on the FASTBUS standard.

## 2.2.3 The Scintillator Trigger

The scintillator trigger [9, 10] is based on the signals from the 30 scintillation counters. It is used to select high multiplicity events. The multiplicity trigger requires a coincidence of 5 out of 16 scintillator pairs. Its information is also used by the muon trigger. The system is implemented in both FASTBUS and CAMAC standards.

# 2.2.4 The Muon Trigger

The muon trigger [11, 12, 13, 14] selects events with at least one particle which penetrates the muon chambers. It uses the trigger cells information from the muon chambers and searches for tracks pointing to the interaction region with  $P_T > 1$  GeV. The total rate is about 10 Hz. After requiring at least one scintillator counter, it goes down to about 1 Hz, mainly coming from the cosmic rays. There are three subtriggers:

#### • Single muon trigger:

This trigger defines a muon track as a coincidence of 2 out of 3 P-chamber layers in  $R_{\theta}$  plane and as a coincidence of 3 out of 4 Z-chamber layers in  $R_z$  plane. At least one octant should have a track identified in both the  $R_{\theta}$  and  $R_z$  planes. The trigger effective in the region  $44^{\circ} \le \theta \le 136^{\circ}$ .

#### • Dimuon trigger:

The trigger defines a muon track as a coincidence of any two layers in the  $R_{\phi}$  plane. At least two octants should have a track identified and the second track

should be in one of the five opposite octants in relation to the first track. The angular coverage of this trigger is  $36^{\circ} \le \theta \le 144^{\circ}$ .

#### • Small angle muon trigger:

A muon track is defined, in this case, by a hit in MI chamber in the  $R_{\phi}$  plane and a hit in II or IM chamber in the  $R_z$  plane. Furthermore, if a track is found in the forward half (+z) of the detector, another should be found in the backward half (-z). The angular region  $24^{\circ} \le \theta \le 156^{\circ}$  is covered.

The *muon trigger* is composed of over 100 CAMAC modules and some FAST-BUS modules located in the MUCH readout system.

#### 2.2.5 The Level-1 Trigger Rates

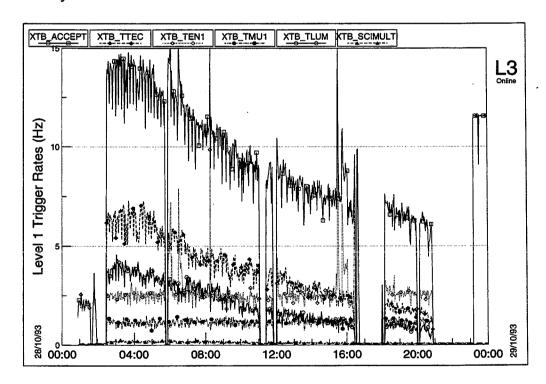

Figure 2.2 displays the trigger rates versus time in Fill No.1891 which was a high luminosity fill in 1993. The fill was started at about 2:30 and ended at about 21:00.

Figure 2.2: The level-1 trigger rates in fill No.1891

XTB\_TTEC, XTB\_TEN, XTB\_TMU, XTB\_LUM and XTB\_SCIMULT in the firgue indicate respectively the *TEC trigger*, the *energy trigger*, the *muon trigger*, the *luminosity trigger* and the *scintillator multiplicity trigger*. The XTB\_ACCEPT is the total rate accepted by the level-1 trigger. It is shown clearly that the *luminosity trigger*

and **TEC trigger** rates are correlated with the beam luminosity which decreases with time, but the **energy trigger**, **muon trigger** and **scintillator trigger** are mainly coming from the electronic noise and cosmic ray respectively which are constant in the whole fill.

Table 2.1 lists the typical level-1 trigger rates (in average) from different triggers [15]. The total output rate is about 10 Hz.

Group trigger Rate

TEC trigger 4.0 Hz

Energy trigger 2.5 Hz

(Luminosity trigger) 2.5 Hz

Muon trigger 0.9 Hz

Scintillator Trigger 0.1 Hz

Total rate 10.0 Hz

Table 2.1: The typical level-1 trigger rates

# 2.3 The Second Level Trigger System

The second level trigger [16] has two functions; collection of the coarse trigger data coming from the first level and rejection of background events selected by the level-1 trigger. The selection algorithm is based on the trigger data and the level-1 trigger decision. To preserve the first level trigger redundancy, the second level algorithms analyze the following categories of single level-1 trigger events which represent 87% of the first level selected events [16].

- The *energy algorithm* is based on the precise energy estimation and rejects events with energy less than the level-2 threshold.

- The *TEC algorithm* rejects electronic noise, beam gas or events with tracks not coming from the interaction point.

- The *muon algorithm* rejects muon events with a small number of hits in vertex chambers and without scintillator counters in time.

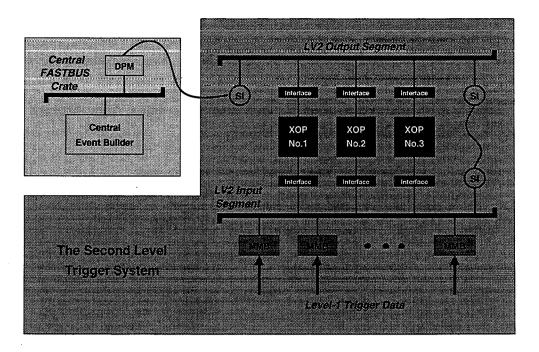

The system [17] is implemented in FASTBUS standard and is shown in Figure 2.3. It is composed of three XOP (bit-slice microprocessors) processing farms [18]. A dedicated XOP/FASTBUS interface has been realized to fully integrate FASTBUS into XOP. Three XOP processors work in a round robin mode. Each one is connected to both input and output FASTBUS segments and acts as a FASTBUS master to take care of the latter three steps in a four steps sequence.

Figure 2.3: The structure of the second level trigger system

#### 1. Trigger data memorization

The trigger data are simultaneously sent to the first level processors and the second level Multiport Multievent input Buffer (MMB) memories. This prevents dead time induced by data transfer between the first and second level. All data (2.5K - 16bit words) from the front end trigger digitizers are stored in parallel to the 48 ECL input port in 12 MMB FASTBUS cards within about 10  $\mu sec$ . At each beam crossing, the data are overwritten unless a good candidate is identified by *the first level trigger*.

#### 2. Trigger event building

The MMB acts as an eight events deep FIFO (First In First Out) memory to allow the asynchronous processor operation at high speed. Its real simultaneous random read/write access at a normal value of 60 nsec per word on the ECL port and 125 nsec per word on the FASTBUS port, provides the decoupling between data storage and trigger event building.

The trigger event building consists of the following steps.

- Reading the data words of all MMB ports associated to the same beam crossing.

- Normalizing data with the same energy unit.

- Suppressing some non significant bits.

- Recording data.

• Building one structured block managed by pointers, named DPM block.

It has to deal with the fact that several ports mix data from several subdetectors in a non ordered sequence. After typically 360  $\mu sec$ , the trigger data block is assembled, data are ordered and normalized.

#### 3. Data processing

XOP is made of 16 bits integer arithmetic ECL processors, implemented in an internal multibus parallel structure and controlled by 192 bits microcode instructions. Parallelism covers arithmetic operations, data address calculation, data access, loop control, condition checking and next instruction evaluation. Due to parallelism and pipelining, the overall performance is in fact much more higher than the cycle time of 100 *nsec* would indicate. XOP provides a speed factor around 40 versus 68000 processors as well as good micro instruction field extension facilities. Microcode is the price to pay to reach these performances.

Processing consists of applying specific algorithms to identify background candidates according to the first level trigger classification and making a decision. The processing time depends strongly on the first level trigger type. Latency time is always less than  $5 \, msec$ .

#### 4. Transfer data to the central event builder

As soon as a decision is made, XOP arbitrates for a mastership of the FASTBUS output segment, and writes trigger data and results into the Dual Port Memory (DPM) acting as the input buffer of the *central event builder*.

Since there is a time dispersion of several milliseconds introduced by the different event processing time, one disturbs the event ordering produced by the first level. As the *central event builder* operates on the various buffer memories according to the original first level sequence, it is mandatory to recover that sequence at the DPM order.

A DPM is partitioned by software in 64 events. The six less significant bits of the event number define the DPM addresses in which the event is stored. A flag associated to each event controls alternatively write access by XOP processors and read access by the central event builder.

The second level trigger was designed to accept up to 500 Hz of input rate. It processes only single or combinations of single level-1 trigger with scintillation counters. At the  $Z^0$  peak, its global reduction is about 50%. More than 99.95% of selection efficiencies are achieved.

# 2.4 The Readout and Event Building Systems

The data from each subdetector come to its front end electronics. The four subdetectors (TECH, ECAL, HCAL and MUCH) use different systems to make digitization and readout according to the detector properties, see [19, 20, 21, 22, 23]. Some of the characteristics of the subdetector DAQ systems are listed in Table 2.2.

Detector Number of Digitizer Data Size System Name Channels Standard Device Resolution Raw Reduced **TECH** 2000 Flash ADC 2 Mbytes VME  $1024 \times 6$  bits 5 Kbytes **ECAL** 12000 VME ADC 12 bits 80 Kbytes 8 Kbytes HCAL 30000 120 Kbytes 4 Kbytes **FASTBUS** ADC 12 bits **MUCH** 21000 **FASTBUS** TDC 10 bits 2 Kbytes 2 Kbytes

Table 2.2: The major subdetector readout systems

Each subdetector system can be operated in two modes. Firstly, it should be able to perform the subdetector calibrations and system debugging independently from other branches. This is called a *local mode*. Secondly, in order to be embedded into the main L3 DAQ stream, the system is operated as a branch of the whole DAQ system and is running in parallel with other branches. This is called a *global mode*. In the *global mode*, the data from each subdetector branch are stored in the FASTBUS event buffers at the event building level. Since the auther has been working on the HCAL readout system, the HCAL system will be described in detail in the next chapter.

The L3 event building system [2] consists of two stages, the subdetector event builders and the central event builder. Each of the four subdetector event builders merges the corresponding subdetector data from the buffers into a logical unit and sends it to the central event builder. The central event builder completes the final combination of the event and checks the level-2 decision. The good events are sent to the third level trigger system to make further selection. The system will be described in detail in Chapter 4.

# 2.5 The Third Level Trigger System

The third level trigger [24] rejects the background events selected by the level-1 and the level-2 using the precise data from the subdetectors. Several algorithms are used to analyze the events.

• The energy algorithm reconstructs energy in the electromagnetic and hadronic calorimeters. As the calculations are based on the fine digitization, the thresholds

can be more precisely defined than in level-2.

- The **muon algorithm** requires a muon track to have a scintillator hit with a time of  $\pm 10$  nsec with respect to the beam crossing.

- The **TEC algorithm** reconstructs the TEC tracks by using the  $R_z$  trigger data to check if the tracks originate from the vertex. It checks also whether the tracks in the  $\phi$  coordinate are correlated with some energy deposit or with hits in the scintillation counters.

The system is fully embedded in the DAQ tree and is based on several powerful processors. It consists of three parts, the input interface, the processor units and the output interface. The output data are sent to a *data producer* which stores events in a memory buffer on the main computer. The buffer is controlled by a Memory Buffer Manager (MBM) software package [25] (developed by CERN ECP division). From this buffer, all events are recorded and selected events are dispatched to monitoring programs.

The third level trigger system accepts up to 20 Hz as input rate without introducing any additional dead time to the system. It provides a reduction of about 50% of the input rate. The system is described in detail in Chapter 5.

# 2.6 The Trigger Control Logic

#### 2.6.1 Overview

The *trigger control logic* [26] makes the synchronization of the different triggers and subdetector components of the DAQ system with the LEP beam. It provides the following functions.

- Provide timing signals for starting level-1 trigger processors and data acquisition modules of the subdetectors.

- Make a final level-1 trigger decision to accept or abort an event.

- Distribute event information to subdetector readout systems if the event is accepted.

- Monitor different background and trigger rates, system lifetime etc. to check the running status of the whole DAQ system.

Figure 2.4: The block diagram of the trigger control logic

The *trigger control logic* is completely implemented by CAMAC modules. The CAMAC bus is only used for system initialization and monitoring. The timing logic is hardwired using either ECL or NIM standards. The schematics of the *trigger control logic* is shown in Figure 2.4.

The *trigger control logic* is fully computer controlled. A program running on a MicroVAX computer provides the link between the *L3 run control* and the *trigger control logic*. Parameters and commands received from the *L3 run control* are passed through CAMAC bus to hardware. To monitor the running status of the trigger and DAQ system, different trigger rates and important single rates are recorded and constantly monitored. The program provides direct operator access through a terminal. There it displays all trigger control parameters and scaler readout. It also accepts keyboard inputs to change all parameters and to select different display items. Thirty selected trigger rates are written every 100 seconds to a disk file and presented on graphic display as a past history.

#### 2.6.2 Timing of the Trigger and DAQ System

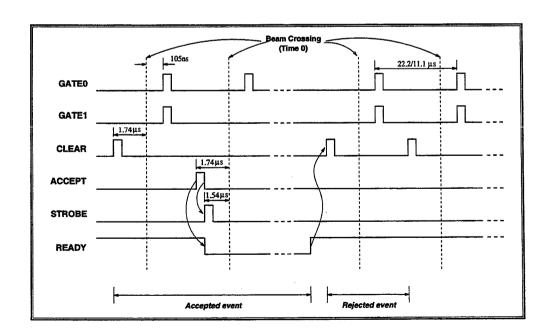

The positron bunch passing by a beam pickup device induces a very narrow signal which is discriminated by a tunnel diode discriminator. All other timing signals of the system are derived from this signal. The absolute time zero of the system is defined as the time when the beam bunch passes the interaction point.

The discriminated beam crossing signal which appears at the discriminator output at +75 nsec is available for different trigger and DAQ components in both ungated and gated forms. The ungated one comes every 22.2/11.1  $\mu$ sec (4 × 4 bunches/8 × 8 bunches) as long as there are beams, it is called GATE0. The gated one is disabled when DAQ system is busy and is called GATE1.