# Characterization and Modeling of Gigarad-TID-Induced Drain Leakage Current of 28-nm Bulk MOSFETs

Chun-Min Zhang<sup>®</sup>, Student Member, IEEE, Farzan Jazaeri<sup>®</sup>, Member, IEEE, Giulio Borghello<sup>®</sup>,

Federico Faccio<sup>®</sup>, Serena Mattiazzo<sup>®</sup>, Andrea Baschirotto, *Fellow, IEEE*, and Christian Enz<sup>®</sup>, *Senior Member, IEEE*

Abstract-This paper characterizes and models the effects of total ionizing dose (TID) up to 1 Grad(SiO<sub>2</sub>) on the drain leakage current of *n*MOSFETs fabricated with a commercial 28-nm bulk CMOS process. Experimental comparisons among individual *n*MOSFETs of various sizes provide insight into the TID-induced lateral parasitic devices, which contribute the most to the significant increase up to four orders of magnitude in the drain leakage current. We introduce a semiempirical physicsbased approach using only three parameters to model the parallel parasitic and total drain leakage current as a function of TID. Taking into account the gate independence of the drain leakage current at high TID levels, we model the lateral parasitic device as a gateless charge-controlled device by using the simplified chargebased Enz-Krummenaker-Vittoz (EKV) MOSFET model. This approach enables us to extract the equivalent density of trapped charges related to the shallow trench isolation oxides. The adopted simplified EKV MOSFET model indicates the weak inversion operation of the lateral parasitic devices.

*Index Terms*—28-nm bulk MOSFETs, charge controlled, drain leakage current, gateless, parasitic device, parasitic leakage current, physics-based modeling, shallow trench isolation (STI), total ionizing dose (TID), trapped charges, weak inversion.

### I. INTRODUCTION

THE forthcoming High-Luminosity Large Hadron Collider (HL-LHC) at CERN is anticipated to experience an

Manuscript received October 16, 2018; revised October 20, 2018; accepted October 22, 2018. Date of publication October 26, 2018; date of current version January 17, 2019. This work was supported in part by the Swiss National Science Foundation (SNSF) through the GigaradMOST Project under grant number 200021\_160185 and in part by the Istituto Nazionale di Fisica Nucleare (INFN) through the ScalTech28 project. (*Corresponding author: Chun-Min Zhang.*)

C.-M. Zhang, F. Jazaeri, and C. Enz are with the Integrated Circuits Laboratory, École Polytechnique Fédérale de Lausanne, 2002 Neuchâtel, Switzerland (e-mail: chunmin.zhang@epfl.ch; farzan.jazaeri@epfl.ch; christian.enz@epfl.ch).

G. Borghello is with the Experimental Physics Department, CERN, 1211 Geneva, Switzerland, and also with DPIA, University of Udine, 33100 Udine, Italy (e-mail: giulio.borghello@cern.ch).

F. Faccio is with the Experimental Physics Department, CERN, 1211 Geneva, Switzerland (e-mail: federico.faccio@cern.ch).

S. Mattiazzo is with the Department of Physics and Astronomy, University of Padova, and also with INFN Padova, 35131 Padova, Italy (e-mail: serena.mattiazzo@dei.unipd.it).

A. Baschirotto is with the Microelectronic Group, University of Milano-Bicocca, and also with INFN Milano-Bicocca, 20126 Milano, Italy (e-mail: andrea.baschirotto@unimib.it).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TNS.2018.2878105

unprecedented radiation level up to 1 Grad(SiO<sub>2</sub>) of total ionizing dose (TID) and  $10^{16}$  neutrons/cm<sup>2</sup> of hadron fluence over 10 years of operation [1]. To ensure long-term reliable performance, the HL-LHC will require highly improved tracking systems with higher bandwidth and more radiationtolerant front-end (FE) electronics [2], [3]. The aggressive downscaling of CMOS technologies brings a higher operation speed and an extended circuit functionality [4], [5]. Moreover, the introduced ultrascaled gate oxides suppress the relevant TID-induced charge buildup and reduce the susceptibility to TID effects [6], [7]. However, at ultrahigh TID levels, effects on parasitic oxides, such as shallow trench isolation (STI) oxides and spacer oxides, often dominate the radiation response of nanoscale CMOS technologies [8], [9]. With the perspective of using ultrascaled CMOS technologies in the future radiation-tolerant tracking systems, we have been characterizing the radiation tolerance of a commercial 28-nm bulk CMOS process up to 1 Grad(SiO<sub>2</sub>) of TID [10], [11] and modeling the observed effects for supporting radiation-tolerant circuit designs [12]. Static measurements on our 28-nm bulk MOSFETs demonstrate an improved radiation tolerance at the switched-on region, whereas most of the irradiated *n*-type MOSFETs undergo a significant increase in the drain leakage current [10], [11]. To characterize these effects, we have introduced the simplified charge-based Enz-Krummenaker-Vittoz (EKV) MOSFET model in [12] to describe the largeand small-signal characteristics. We are currently developing physics-based models of TID effects on bulk MOSFETs that can ultimately be implemented into the BSIM6 compact model for the design of radiation-tolerant circuits. Among all the various effects of TID on bulk MOSFETs, the significant increase of the drain leakage current observed for *n*-type MOSFETs is certainly the most important to model. Most of the other effects such as threshold voltage shift can be compensated by proper circuit biasing techniques. This paper, therefore, focuses on modeling the TID-induced drain leakage current by means of a gateless charge-controlled model similar to the simplified charge-based EKV MOSFET model.

The significant increase in the drain leakage current is mainly attributed to the radiation-induced charge trapping in relatively thick STI oxides. For an *n*MOSFET, trapped holes in STI oxides can invert the *p*-type substrate along the STI sidewalls and open two parallel parasitic leakage paths [13]–[16].

0018-9499 © 2018 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

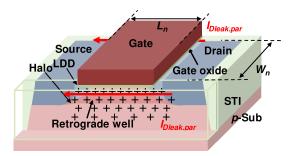

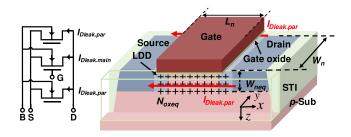

Fig. 1. 3-dimensional (3-D) schematic of an irradiated *n*MOSFET illustrating the formation of two lateral parasitic devices. The main *n*MOSFET is surrounded by the STI structure, as shown in light green. The front face of the STI structure is represented by the light-green frame to make the channel doping profile and the STI-related trapped-charge (+ markers) distribution visible.

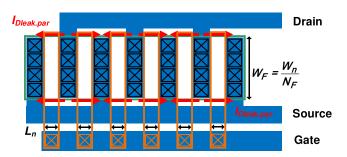

This allows two parallel leakage components to flow from drain to source, even when the main *n*MOSFET is switched off, as shown in Fig. 1. The situation becomes even worse for a multifinger *n*MOSFET because the total parasitic drain-to-source leakage current scales with the number of fingers [17], as shown in Fig. 2. This radiation-induced leakage current questions the main advantage of nanoscale CMOS technologies, i.e., low power consumption [18]. In contrast, for a *p*MOSFET, trapped holes in STI oxides tend to accumulate electrons at the surface of the *n*-type substrate and prevent the formation of *p*-type channels. Therefore, the drain leakage current of the irradiated *p*MOSFETs is not an issue, as shown in [11].

This paper characterizes and models, in detail, the effects of TID up to 1 Grad(SiO<sub>2</sub>) on the drain leakage current of nMOSFETs. To the best of our knowledge, no publication has been devoted from the perspective of both experiment and modeling to the impact of such high TID levels on the drain leakage current of this commercial 28-nm bulk CMOS process. We propose a semiempirical physics-based approach with only three parameters to model the parallel parasitic and total drain leakage current as a function of TID. The lateral parasitic device has been investigated using TCAD device simulations [19]-[21], compact models [22], or a combination of these two approaches [16], [23]. However, these models involve complex device structures and intensive analytical computations. We aim at a simpler approach for evaluating the TID-induced drain leakage current. Taking into account the gate independence of the drain leakage current at high TID levels, we propose modeling the lateral parasitic device as a gateless charge-controlled device by using the simplified charge-based EKV MOSFET model.

## **II. EXPERIMENTAL DETAILS**

Test chips with a matrix of individual MOSFETs were fabricated with a commercial 28-nm bulk CMOS technology, which allows the width per finger  $W_F$  from 100 nm to 3  $\mu$ m and the length  $L_n$  from 30 nm to 1  $\mu$ m. We explore standard single-finger and multifinger *n*MOSFETs of various sizes for identifying the dominant components of drain leakage current at different TID levels and the favorable device geometry for radiation-tolerant applications. Each chip has only one

Fig. 2. Layout of an irradiated multifinger *n*MOSFET illustrating the scaling property of the total parallel parasitic drain-to-source leakage current with two times the number of fingers. The total width of the multifinger *n*MOSFET  $W_n$  is the width per finger  $W_F$  times the number of fingers  $N_F$ .

transistor of each size. However, a brief comparison of the same size of transistors on different chips demonstrates the repeatability of our measurement results. Enclosed-layout transistors are often used for isolating the effects of TID on STI oxides [8], [9]. However, the strict design rules of this commercial 28-nm bulk CMOS process exclude such special structures.

Chips were irradiated at CERN's in-house 10-keV X-ray irradiation system (Seifert RP149) at room temperature (300 K). Reference [8] shows that the conducting bias condition  $V_{GB} = V_{DS} = V_{DD}$  is the real worst bias case for commercial 65-nm bulk nMOSFETs from the same foundry, where  $V_{GB}$  is the gate-to-bulk voltage,  $V_{DS}$  is the drainto-source voltage, and  $V_{DD}$  is the nominal voltage supply. This is different from the historical worst bias case, i.e., the switched-on bias condition  $V_{GB} = V_{DD}$  and  $V_{DS} = 0$  [24]. Nevertheless, these two bias conditions induce no big difference in the drain leakage current of our 28-nm bulk MOS-FETs [25]. Moreover, in most analog circuits and particularly the analog FE electronics, MOSFETs are biased in saturation with a nonzero  $V_{DS}$  except the switches working at a zero  $V_{DS}$ . To reproduce as closely as possible the realistic bias condition, we used the conducting bias condition.

Single-finger and multifinger nMOSFETs were irradiated up to 1  $Grad(SiO_2)$  with steps of 0, 0.5, 1, 5, 10, 50, 100, 200, 400, 600, 800, and 1000 Mrad at a dose rate of 8.82 and 10 Mrad/h(SiO<sub>2</sub>), respectively. These two dose rates are quite similar and make no big difference in terms of TID effects on our 28-nm bulk MOSFETs. Immediately after each TID step, static measurements were performed with the Keithley 4200-SCS Parameter Analyzer. As oxidetrapped charges anneal with time [26], we chose a voltage step of 25 mV as a suitable compromise between limiting the measurement duration and providing a sufficient measurement resolution. Reference [11] shows the relatively slow oxidetrapped charge annealing at room temperature for our 28-nm bulk MOSFETs. This allows us to neglect the annealing effects that happened during less than one hour of measurements. More measurement details can be found in [10] and [11].

## III. CHARACTERIZATION OF THE DRAIN LEAKAGE CURRENT

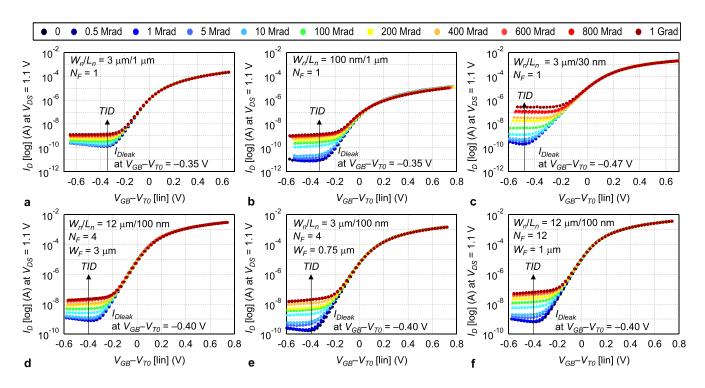

Fig. 3 plots the drain current  $I_D$  of single-finger (a-c) and multifinger (d-f) *n*MOSFETs measured in saturation

Fig. 3. Drain current  $I_D$  of single-finger (a)–(c) and multifinger (d)–(f) *n*MOSFETs measured in saturation ( $V_{DS} = 1.1$  V) versus overdrive voltage  $V_{GB} - V_{T0}$  with respect to the TID.  $V_{T0}$  is the threshold voltage extracted as the intercept of the linear extrapolation at the maximum slope of  $\sqrt{I_D} - V_{GB}$  curves at the  $V_{GB}$  axis. The vertical arrow lines point out the location where the drain leakage current  $I_{Dleak}$  is extracted.

$(V_{DS} = 1.1 \text{ V})$  versus the overdrive voltage  $V_{GB} - V_{T0}$  with respect to TID up to 1 Grad(SiO<sub>2</sub>), where the threshold voltage  $V_{T0}$  is extracted as the intercept of the linear extrapolation at the maximum slope of  $\sqrt{I_D}$ - $V_{GB}$  curves at the  $V_{GB}$  axis. Both single-finger and multifinger *n*MOSFETs demonstrate a substantial increase in the drain leakage current.

Furthermore, the drain leakage current of single-finger *n*MOSFETs presents a width independence and a length dependence. At high TID levels, single-finger *n*MOSFETs of the same length ( $L_n = 1 \mu$ m), as shown in Fig. 3(a) and (b), exhibit a close amount of drain leakage current. However, those of the same width ( $W_n = 3 \mu$ m) but different lengths, as shown in Fig. 3(a) and (c), display different values of drain leakage current. This width independence and length dependence jointly indicate the dominant contribution of the lateral parasitic devices.

In addition to the gate length dependence, the drain leakage current is also proportional to the number of fingers. At high TID levels, multifinger *n*MOSFETs of the same gate length and the same number of fingers ( $L_n = 100 \ \mu \text{m}$  and  $N_F = 4$ ), as shown in Fig. 3(d) and (e), present almost the same amount of drain leakage current. However, those of the same device geometry ( $W_n/L_n = 12 \ \mu \text{m}/100 \text{ nm}$ ), as shown in Fig. 3(d) and (f), have the drain leakage current proportional to the number of fingers. This scalability with the number of fingers confirms the primary contribution of the lateral parasitic devices.

Even though the increase in the drain leakage current slows down at relatively high TID levels, we do not see the rebound effects of interface-trapped charges [13]. For the tested 28-nm bulk *n*MOSFETs, trapped holes in STI oxides, therefore, play a more important role than charges trapped at silicon/STI interfaces.

# IV. MODELING OF THE DRAIN LEAKAGE CURRENT

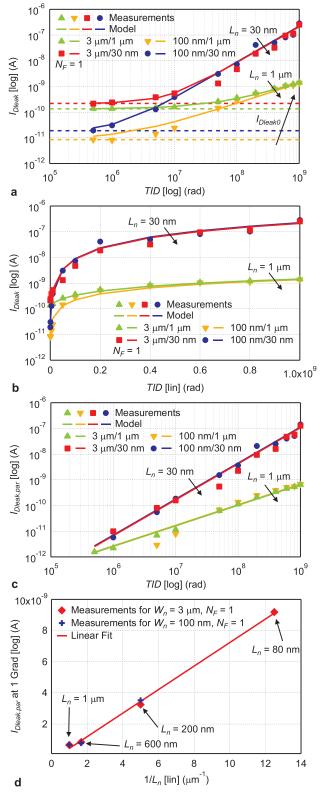

This paper mainly studies single-finger *n*MOSFETs at the four corners of the  $W_n$  versus  $L_n$  plot, the multifinger *n*MOSFET with  $W_n = 3 \ \mu m$  and  $N_F = 4$ , and those with  $W_n = 12 \ \mu m$  and  $N_F = 4, 6, 8$ , and 12. The total drain leakage current  $I_{Dleak}$  is extracted at a constant  $V_{GB} - V_{T0}$ from the transfer characteristics. Figs. 4(a) and 5(a) plot the extracted I<sub>Dleak</sub> of single-finger and multifinger nMOSFETs as closed markers, respectively. The tested *n*MOSFETs of the same gate length and the same number of fingers exhibit a close amount of  $I_{Dleak}$ . This confirms the width independence, the length dependence, and the dependence on the number of fingers, demonstrating the main contribution of the lateral parasitic devices. The log-lin plots with closed markers in Figs. 4(b) and 5(b) show that the significant increase in IDleak mostly happens before 200 Mrad of TID. Afterward, the increase tends to slow down. This might be due to the saturation effect of STI-related trapped charges [27].

$I_{Dleak}$  comes from the main *n*MOSFET ( $I_{Dleak.main}$ ) and the lateral parasitic devices ( $2N_F I_{Dleak.par}$ )

$$I_{Dleak} = I_{Dleak.main} + 2N_F I_{Dleak.par}.$$

(1)

The drain leakage current of the main *n*MOSFET  $I_{Dleak.main}$  is mainly composed of the drain-to-gate tunneling current, the gate-induced drain leakage current, and the subthreshold current [28]. These leakage components are as a function of the threshold voltage  $V_{TO}$ , which is among the most

10<sup>-7</sup> Measurements Model 10<sup>-8</sup> I<sub>Dleak</sub> [log] (A) From up to down N<sub>F</sub> =12, 8, 6, and um/100 nm 10<sup>-9</sup> Dleak = 3 μm/100 nm, N<sub>F</sub> = 4 -10 10  $10^{6}$  $10^{8}$ 10<sup>9</sup> 10 10 TID [log] (rad) а 10 10<sup>-8</sup> I<sub>Dleak</sub> [log] (A) Measurements 10 -Model -  $W_n/L_n = 3 \,\mu m/100 \,nm$  and  $N_F = 4$  $W_n/L_n = 12 \ \mu m/100 \ nm$  $N_F = 4$   $\checkmark$  $N_{\rm F} = 6$ 10<sup>-10</sup> 0.2 0.4 0.6 0.8 0 1.0x10<sup>9</sup> b TID [lin] (rad) 10<sup>-6</sup> Measurements Model 10 I<sub>Dleak.par</sub> [log] (A) 10<sup>-8</sup> 10<sup>-9</sup>  $L_n = 100 \text{ nm}$ 10<sup>-10</sup> 10<sup>-11</sup> 10<sup>-12</sup> 10<sup>6</sup> 10<sup>7</sup> 10<sup>8</sup> 10<sup>9</sup> 10<sup>5</sup> С TID [log] (rad) 70x10<sup>-9</sup>  $W_n/L_n = 12 \ \mu m/100 \ nm$ 60 Markers: Measurements Lines: Asymptotes I<sub>Dleak</sub>-I<sub>Dleak0</sub> [lin] (A) 50 Grad 600 Mrad 40 400 Mrad 30 200 Mrad 20 100 Mrad 10 50 Mrad 0 6 8 0 2 4 10 12 d N<sub>F</sub> [lin] (-)

Fig. 4. Model validation of the total drain leakage current  $I_{Dleak}$  of singlefinger *n*MOSFETs in (a) log–log scale and (b) log–lin scale versus the TID. (c) Model validation of the average parasitic drain-to-source leakage current  $I_{Dleak,par}$  versus *TID*. (d) Average parasitic drain-to-source leakage current at 1 Grad of TID versus  $L_n$ .

TID-sensitive device parameters. Plotting  $I_D$  versus  $V_{GB}-V_{T0}$  isolates the effects of the TID-induced  $V_{T0}$  shift.  $I_{Dleak}$  extracted at a constant  $V_{GB} - V_{T0}$  with respect to TID therefore has almost the same contribution from the main *n*MOSFET.

Fig. 5. Model validation of the total drain leakage current  $I_{Dleak}$  of multifinger *n*MOSFETs in (a) log–log scale and (b) log–lin scale versus the TID. (c) Model validation of the average parasitic drain-to-source leakage current  $I_{Dleak,par}$  versus *TID*. (d) Total parasitic leakage current  $I_{Dleak} - I_{Dleak0}$  of multifinger *n*MOSFETs of the same size versus the number of fingers  $N_F$ .

In addition, the substantial increase in  $I_{Dleak}$  is mostly the contribution of the lateral devices, which allows us to assume a constant  $I_{Dleak.main}$ , as confirmed by the plateau at low TID levels (< ~ 1 Mrad) in Figs. 4(a) and 5(a). Prior to

$W_n/L_n$ TID<sub>crit</sub> (Mrad) I<sub>Dleakθ</sub> (A)  $1.34 \times 10^{-10}$ 58.6 3 μm/1 μm 0.8 100 nm/1 µm  $8.47 \times 10^{-12}$ 0.8 1.78  $2.17 \times 10^{-10}$ 3 µm/30 nm 1.4 7.35  $1.\overline{90} \times 10^{-11}$ 100 nm/30 nm 1.24 1.4 -10 3 µm/100 nm  $1.65 \times 10^{-1}$ 0.9 4.10 4  $7.84 \times 10^{-10}$ 22.4 12 µm/100 nm 4 0.9 -10 12 µm/100 nm  $7.37 \times 10^{-1}$ 0.9 12.3 6 -10  $12 \,\mu m / 100 \,nm$  $6.37 \times 10^{-1}$ 8.95

8

12

12 µm/100 nm

TABLE I MODEL PARAMETERS FOR THE DRAIN-TO-SOURCE LEAKAGE CURRENT

irradiation, neither the oxide-trapped charge density from the semiconductor processing nor the fringing field from the gate bias is high enough to induce the parasitic leakage paths in parallel with the main channel or a total parasitic drain-tosource leakage current comparable to IDleak.main [29]. This allows us to neglect the parallel parasitic drain-to-source leakage current before irradiation.

$6.42 \times 10^{-10}$

Therefore, the preirradiation drain leakage current  $I_{Dleak0}$ , as plotted by dashed lines in Figs. 4(a) and 5(a), measures I<sub>Dleak.main</sub>. Solving (1) gives the average parasitic drain-tosource leakage current I<sub>Dleak.par</sub>

$$I_{Dleak.par} = \frac{I_{Dleak} - I_{Dleak0}}{2N_F}.$$

(2)

0.9

0.9

5.29

Closed markers in Figs. 4(c) and 5(c) exhibit a significant increase in I<sub>Dleak.par</sub>. Moreover, the lateral parasitic devices in parallel with the main *n*MOSFETs of the same gate length have almost the same contribution to I<sub>Dleak</sub>. I<sub>Dleak,par</sub> of longchannel parasitic devices is actually linearly dependent on  $1/L_n$ , as shown in Fig. 4(d). The shortest gate length  $L_n =$ 30 nm falls beyond the linear fit due to short-channel effects. The linearity in Fig. 5(d) evidences the scaling property of the total parasitic drain-to-source leakage current with the number of fingers.

Considering the constant I<sub>Dleak.main</sub> at all TID steps and the linear relation between I<sub>Dleak</sub> and TID in log-log scale at high TID levels, as shown in Figs. 4(a) and 5(a), we propose a simple semiempirical physics-based model for the total drain leakage current IDleak

$$I_{Dleak} = I_{Dleak0} \left[ 1 + \left( \frac{TID}{TID_{crit}} \right)^k \right]$$

(3)

where  $TID_{crit}$  is the critical total dose at which the lateral parasitic devices contribute the same amount of current as the main nMOSFET and k is the slope of the log-log plot at relatively high TID levels calculated by  $(\log_{10} I_{Dleak2,par} \log_{10} I_{Dleak1.par} / (\log_{10} TID_2 - \log_{10} TID_1)$  with two sets of data  $I_{Dleak1,par}(TID_1)$  and  $I_{Dleak2,par}(TID_2)$ . Solving (2) and (3) produces the model for the parallel parasitic drain-to-source leakage current I<sub>Dleak.par</sub>

$$I_{Dleak,par} = \frac{I_{Dleak0}}{2N_F} \left(\frac{TID}{TID_{crit}}\right)^k.$$

(4)

Fitting (3) with measurement results determines the values of  $TID_{crit}$  and k. Together with  $I_{Dleak0}$ , model parameters are listed in Table I. The power k is the same for *n*MOSFETs

Equivalent circuit of an irradiated nMOSFET with two gate-Fig. 6. independent lateral parasitic devices (left) and 3-D schematic of the irradiated *n*MOSFET with two parallel parasitic leakage paths formed by uniformly distributed trapped charges related to STI oxides (right).

of the same length, whereas the preirradiation drain leakage current I<sub>Dleak0</sub> and the critical total dose TID<sub>crit</sub> depend on the device geometry and the number of fingers. Model results are plotted as solid lines in Figs. 4 and 5. Using only three parameters, the proposed semiempirical physics-based model demonstrates a good agreement with measurement results. This efficiency makes it a practical method of evaluating the parallel parasitic and total drain leakage current with respect to TID. *TID<sub>crit</sub>* indicates the TID level, above which the lateral parasitic devices contribute the most to the total drain leakage current  $I_{Dleak}$ . Recent measurements show the independence of the parallel parasitic drain-to-source leakage current I<sub>Dleak.par</sub> on the applied  $V_{DS}$  during irradiation. This demonstrates the promising use of this model in accurately predicting the drain leakage current of *n*MOSFETs working across the whole range of  $V_{DS}$  from zero to  $V_{DD}$ . By extracting the corresponding values of three model parameters, we can apply this model easily to alternative CMOS technologies.

# V. MODELING THE LATERAL PARASITIC DEVICE AS A GATELESS CHARGE-CONTROLLED DEVICE

# A. Equivalent Structure for the Lateral Parasitic Device

At high TID levels, the drain current at low values of overdrive voltage is independent of the gate bias, as shown in Fig. 3. This weak or negligible gate control is the one distinctive feature of the lateral parasitic device. It is the STI-related trapped charges that modify the surface potential of the edge channel and control the mobile charge density of the lateral parasitic device. This motivates us to model the lateral parasitic device as a gateless charge-controlled device, as shown by the equivalent circuit in Fig. 6. Since this lateral parasitic device has no gate control and is fully controlled by STI-related trapped charges, we name it as *n-Q*FET.

The applied bias and the dynamic charge movement during irradiation make the electrical condition inside the device complex. This results in a nonuniform charge buildup related to STI oxides [19], [20]. Moreover, the complex channel doping engineering has been widely used in modern CMOS technologies, including the retrograde well for preventing the latch-up effect, the threshold voltage adjustment by ion implant at the surface, the lightly doped drain for suppressing the hot carrier degradation, and the halo implant for inhibiting the punch through effect [30]. This leads to a nonuniform doping profile [16], [19], as illustrated in Fig. 1. Both aspects

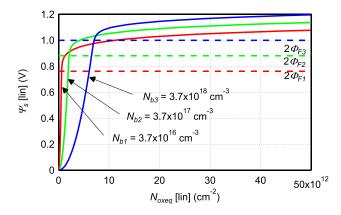

Fig. 7. Surface potential  $\Psi_s$  versus the equivalent density of STI-related trapped charges per unit area  $N_{oxeq}$ .

influence the electrical characteristics of the lateral parasitic n-QFET.

To simplify the modeling task, we introduce an equivalent structure for the lateral parasitic *n*-*Q*FET, as illustrated in Fig. 6. It has a uniform channel doping concentration ( $N_b$ ) that is the same as the main channel. It also has an equivalent STI-related trapped-charge density  $Q_{oxeq} = qN_{oxeq}$  that models the complex charge distribution

$$Q_{oxeq} = \frac{\int_0^{W_{n,par}} \int_0^{L_{n,par}} Q_{ox}(x, y) dx dy}{W_{neq} L_{neq}}$$

(5)

where  $Q_{ox}(x, y)$  is the local STI-related trapped-charge density,  $W_{n.par}$  is the local width,  $L_{n.par}$  is the local length,  $W_{neq}$ is the equivalent channel width, and  $L_{neq}$  is the equivalent channel length. The equivalent STI-related trapped-charge density  $Q_{oxeq}$  is uniform over a certain width  $W_{neq}$  and a certain length  $L_{neq}$ .  $I_{Dleak.par}$  is assumed above the bottom of source and drain extensions. It is then straightforward to assume  $L_{neq}$  equal to the gate length of the main channel  $L_n$  and  $W_{neq}$  equal to the junction depth of source and drain extensions  $X_j$ , where  $L_n$  and  $X_j$  are the two known parameters.

#### B. Utilization of the Simplified EKV MOSFET Model

The simplified EKV MOSFET model is able to fully describe large- and small-signal characteristics over a wide range of bias from weak via moderate to strong inversion with only four parameters, i.e., the slope factor *n*, the specific current  $I_{spec}$ , the velocity saturation (VS) parameter  $\lambda_c$ , and the threshold voltage  $V_{T0}$ . References [12], [31], and [32] have verified the applicability of this model for this commercial 28-nm bulk CMOS process. Since the gateless charge-controlled concept involves no gate voltage or gate oxide capacitance, we need to modify the simplified EKV MOSFET model for the lateral parasitic *n-Q*FET.

Solving Gauss's law and Poisson's equation gives the relation between the local silicon charge density  $Q_{si}$  and the surface potential  $\Psi_s$

$$Q_{si} = -\Gamma_{b.par} \sqrt{U_T} \sqrt{\exp \frac{-2\Phi_F - V_{ch}}{U_T}} \left(\exp \frac{\Psi_s}{U_T} - 1\right) + \frac{\Psi_s}{U_T}$$

(6)

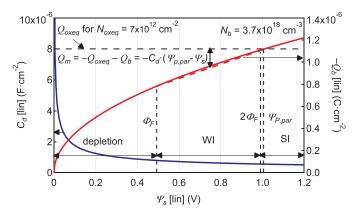

Fig. 8. Linearization of the mobile charge density  $Q_m$  with respect to the surface potential  $\Psi_s$ .

where  $\Gamma_{b,par} = \sqrt{2q\epsilon_{si}N_b}$  is defined as the substrate modulation factor, q is the elementary charge,  $\epsilon_{si}$  is the silicon permittivity,  $U_T = kT/q$  is the thermal voltage, k is Boltzmann's constant, T is the temperature,  $\Phi_F = U_T \ln(N_b/n_i)$  is the Fermi potential,  $n_i$  is the intrinsic carrier concentration,  $V_{ch}$ is the channel voltage equal to  $V_S$  at source and  $V_D$  at drain, and  $V_S$  and  $V_D$  are the source and drain voltages, respectively. Note that in [33], the substrate modulation factor is defined as  $\Gamma_b = \sqrt{2q\epsilon_{si}N_b}/C_{ox}$  that links  $\Gamma_{b,par}$  by  $\Gamma_{b,par} = \Gamma_bC_{ox}$ , where  $C_{ox}$  is the gate oxide capacitance.

The charge neutrality condition provides the key bridge between STI-related trapped-charge density and total silicon charge density

$$Q_{oxeq} = -Q_{si}.\tag{7}$$

Solving (6) and (7) gives the link between  $Q_{oxeq}$  and  $\Psi_s$ . Fig. 7 shows that for a higher channel doping concentration, a higher STI-related trapped-charge density is needed to switch on the lateral parasitic *n*-*Q*FET. Since  $N_b = 3.7 \times 10^{18} \text{ cm}^{-3}$ and  $\Phi_F = 0.5 V$  for our 28-nm bulk *n*MOSFETs,  $N_{oxeq}$ needs to be higher than  $4.94 \times 10^{12} \text{ cm}^{-2}$  to bias the lateral parasitic *n*-*Q*FET in weak inversion ( $\Phi_F < \Psi_s < 2\Phi_F$ ) and  $7.06 \times 10^{12} \text{ cm}^{-2}$  in strong inversion ( $\Psi_s \ge 2\Phi_F$ ). Therefore, we expect that advanced bulk CMOS technologies, which have a higher channel doping concentration, can withstand a much higher TID before having enough STI-related trapped charges to switch on the lateral parasitic *n*-*Q*FET.

The charge-sheet approximation gives the expression of depletion charge density  $Q_b = -\Gamma_{b,par}\sqrt{\Psi_s}$ . The differentiation of  $Q_b$  versus  $\Psi_s$  gives the depletion capacitance  $C_d = \Gamma_{b,par}/(2\sqrt{\Psi_s})$ . As shown in Fig. 8,  $C_d$  slightly depends on  $\Psi_s$  in inversion operation. This enables us to linearize the depletion charge density  $Q_b$ , as shown by the approximated red dashed line in Fig. 8. The length of the vertical doublearrowheaded line in Fig. 8 represents the mobile charge density  $Q_m = -Q_{oxeq} - Q_b$  that can be linearized in inversion region as

$$Q_m = -C_d(\Psi_{P,par} - \Psi_s) \tag{8}$$

where  $\Psi_{P,par}$  is the pinch-off potential. Once  $\Psi_s$  reaches  $\Psi_{P,par}$ ,  $Q_m$  becomes 0 and  $Q_b$  equals to  $-Q_{oxeq}$ , which gives the expression of  $\Psi_{P,par}$ :  $\Psi_{P,par} = Q_{oxeq}^2 / \Gamma_{b,par}^2$ . Note that in

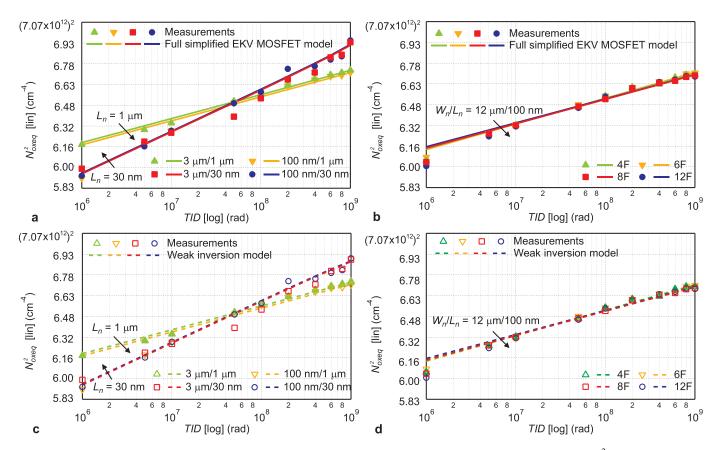

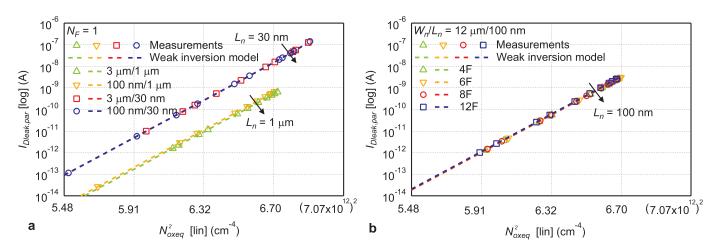

Fig. 9. Square of the extracted (markers) and modeled (lines) equivalent density of STI-related trapped charges per unit area  $N_{oxeq}^2$  versus the TID in lin–log scale for (a) and (c) single-finger and (b) and (d) multifinger *n*MOSFETs. (a) and (b) correspond to the full simplified EKV MOSFET model, whereas (c) and (d) correspond to the weak inversion approximation.

[33], the slope factor *n* is defined as  $n = 1 + \Gamma_b/(2\sqrt{\Psi_s})$  that links the depletion capacitance  $C_d$  by  $C_d = C_{ox}(n-1)$ . Subtracting  $Q_b$  from  $Q_{si}$  gives the expression of  $Q_m$

$$Q_m = -\Gamma_{b,par}\sqrt{U_T} \times \left[\sqrt{\exp\frac{-2\Phi_F - V_{ch}}{U_T}\left(\exp\frac{\Psi_s}{U_T} - 1\right) + \frac{\Psi_s}{U_T}} - \sqrt{\frac{\Psi_s}{U_T}}\right].$$

(9)

Under the flatband condition,  $\Psi_s$  and  $Q_m$  equal to zero. Combining (8) and (9) and following the steps from [31, eqs. (3.40)–(3.48)] with the redefined parameters, we obtain the charge-voltage relation

$$v_{p,par} - v_{s,d} = 2q_{s,d} + \ln q_{s,d} \tag{10}$$

where  $q_s = Q_{iS}/Q_{spec.par}$  is the normalized mobile charge density at source,  $q_d = Q_{iD}/Q_{spec.par}$  is the normalized mobile charge density at drain,  $Q_{iS}$  and  $Q_{iD}$  are the mobile charge densities at source and drain, respectively,  $Q_{spec.par} = -2C_dU_T$ is the specific charge,  $v_{p.par} = V_{P.par}/U_T$  is the normalized pinch-off voltage,  $V_{P.par} = Q_{oxeq}^2/\Gamma_{b.par}^2 - 2\Phi_F - (\ln 2)U_T$  is the pinch-off voltage,  $v_s = V_S/U_T$  is the normalized channel voltage at source, and  $v_d = V_D/U_T$  is the normalized channel voltage at drain.

Adopting the drift-diffusion model  $I_D = -\mu_n (W_{neq}/L_n)$  $\int_{V_S}^{V_D} Q_m dV_{ch}$ , we obtain the charge-current relation

$$i_{f,r} = q_{s,d}^2 + q_{s,d} \tag{11}$$

where  $i_f = I_F/I_{spec.par}$  is the normalized forward current,  $i_r = I_R/I_{spec.par}$  is the normalized reverse current,  $I_F$  and  $I_R$ are the forward and reverse currents, respectively,  $I_{spec.par} = 2\mu_n C_d U_T^2 W_{neq}/L_n$  is the specific current, and  $\mu_n$  is the lowfield electron mobility that is assumed equal to that of the main *n*MOSFET. The parallel parasitic drain-to-source leakage current  $I_{Dleak.par}$  is the difference between the forward current  $I_F$  and the reverse current  $I_R$ . Since the reverse current  $I_R$ is negligible in saturation, combining (10) and (11) and neglecting  $I_R$  leads to the current–voltage relation

$$v_{p,par} - v_s = \sqrt{1 + 4i_{dleak,par}} + \ln\left(\sqrt{1 + 4i_{dleak,par}} - 1\right) - (1 + \ln 2)$$

(12)

where  $i_{dleak,par} = I_{Dleak,par}/I_{spec,par}$  is the normalized parasitic leakage current. Taking into account the VS effect, the current–voltage relation for short-channel parasitic n-QFETs becomes [34]

$$v_{p,par} - v_s$$

$$= \sqrt{(1 + \lambda_c i_{dleak,par})^2 + 4i_{dleak,par}}$$

$$+ \ln[\sqrt{(1 + \lambda_c i_{dleak,par})^2 + 4i_{dleak,par}} - 1] - (1 + \ln 2)$$

(13)

where  $\lambda_c = L_{sat}/L_n$  is the VS parameter and  $L_{sat}$  corresponds to the section of the channel where the carrier drift velocity saturates.  $L_{sat}$  is assumed equal to that of the main *n*MOSFET.

Fig. 10. Extracted and modeled parasitic drain-to-source leakage current  $I_{Dleak,par}$  of (a) single-finger and (b) multifinger *n*MOSFETs versus the square of the density of STI-related trapped charges  $N_{oxeq}^2$ .

The proposed charge-controlled concept is similar to the work of Zebrev *et al.* [35]. However, the work of Zebrev *et al.* [35] focuses on the interdevice parasitic leakage current underneath the STI oxide between the *n*-well of a *p*MOSFET and the source/drain of the nearby *n*MOSFET, whereas our work focuses on the intradevice parasitic leakage current along the STI sidewalls in parallel with the main *n*-type channel. Moreover, the work of Zebrev *et al.* [35] is limited to the linear operation and validated at low TID levels (krad), whereas our approach is able to cover the parallel parasitic drain-to-source leakage current from linear to saturation and extends to rather high TID levels up to 1 Grad.

# C. Extraction of the Equivalent Density of STI-Related Trapped Charges

Solving (2) with (12) or (13), we extract the equivalent density of STI-related trapped charges  $N_{oxeq}$  from measurement results. Combining (4) with (12) or (13), we obtain the  $N_{oxeq}$ predicted by the proposed models. The square of the extracted and modeled  $N_{oxeq}$  are plotted as closed markers and solid lines in Fig. 9(a) and (b), respectively. Model results are in a good agreement with the extraction. The lateral parasitic n-QFETs of the same length have the same amount of STIrelated trapped charges, which is consistent with their close amount of parallel parasitic drain-to-source leakage current.

#### D. Weak Inversion Approximation

As mentioned in Section V-B,  $N_{oxeq}$  needs to be higher than  $7.06 \times 10^{12}$  cm<sup>-2</sup> for  $\Psi_s$  to be higher than  $2\Phi_F$  and to bias the parasitic *n*-*Q*FET in strong inversion. However, as shown in Fig. 9(a) and (b), the highest value of  $N_{oxeq}$  is around  $6.95 \times 10^{12}$  cm<sup>-2</sup>. This meets our intuition that even after 1 Grad(SiO<sub>2</sub>) of TID, the lateral parasitic *n*-*Q*FET still works in weak inversion and might eventually enter the moderate inversion. Therefore, we consider only the weak inversion operation for an approximated solution to the equivalent density of STI-related trapped charges.

Now, we focus on the logarithmic term of (10):  $v_{p,par} - v_s = \ln q_s$ . Substituting the normalized variables with

the absolute values brings back to the original expression:  $Q_m/(-2C_dU_T) = \exp[(V_{P,par} - V_{ch})/U_T]$ . Introducing it into the drift-diffusion model gives

$$I_{Dleak.par} = \frac{2\mu_n C_d U_T W_{neq}}{L_n} \int_{V_S}^{V_D} \exp \frac{V_{P.par} - V_{ch}}{U_T} dV_{ch}.$$

(14)

Solving the integral gives the parallel parasitic drain-to-source leakage current in weak inversion *I*<sub>Dleak.par</sub>

$$I_{Dleak.par} = I_{spec.par} \left( \exp \frac{V_{P.par} - V_S}{U_T} - \exp \frac{V_{P.par} - V_D}{U_T} \right).$$

(15)

Since  $V_D > V_{P,par}$  in saturation,  $I_{Dleak,par}$  is finally modeled as

$$I_{Dleak.par} = I_{spec.par} \exp \frac{V_{P.par} - V_S}{U_T}.$$

(16)

Combining (4) and (16), replacing  $V_{P,par}$  with  $Q_{oxeq}^2/\Gamma_{b,par}^2 - 2\Phi_F - (\ln 2)U_T$ , and including the VS parameter  $\lambda_c$ , we obtain the approximated solution for STI-related trapped-charge density

$$Q_{oxeq}^{2} = \Gamma_{b,par}^{2} U_{T} \times \left[ \ln\left(\frac{(2+\lambda_{c})I_{Dleak0}}{2I_{spec,par}}\right) + k\ln\left(\frac{TID}{TID_{crit}}\right) + \frac{2\Phi_{F}}{U_{T}} + \ln 2 \right].$$

(17)

Setting  $\lambda_c$  to zero leads to the long-channel model.

The square of the extracted and modeled  $N_{oxeq}$  using the weak inversion approximation are plotted as open markers and dashed lines in Fig. 9(c) and (d), respectively. The weak inversion approximation presents almost the same results as the full simplified EKV MOSFET model, except the slight mismatch at ultrahigh TID levels where the lateral parasitic *n*-*Q*FET approaches the moderate inversion. In addition, the straight lines fit the relation of  $Q_{oxeq}^2 \propto k \ln(TID/TID_{crit})$  in (17). The weak inversion model is, therefore, a very good approximation for the parallel parasitic drain-to-source leakage current.

Replacing all defined terms in (16) with the full expressions provides a direct link between the parallel parasitic drainto-source leakage current  $I_{Dleak,par}$  and the channel doping concentration  $N_b$

$$I_{Dleak,par} \propto \exp \frac{Q_{oxeq}^2}{2q\epsilon_{si}N_bU_T}.$$

(18)

The parallel parasitic drain-to-source leakage current  $I_{Dleak.par}$  increases exponentially with the square of STI-related trappedcharge density  $Q_{oxeq}^2$ , as shown by the straight lines in the log–lin plots in Fig. 10. For a higher channel doping concentration  $N_b$ , the lateral parasitic *n-Q*FET needs a higher  $Q_{oxeq}$  to reach the same amount of  $I_{Dleak.par}$ . Advanced CMOS technologies with a higher channel doping concentration are, therefore, advantageous in terms of radiation-induced static power consumption.

#### VI. CONCLUSION

This paper characterizes and models the effects of TID up to 1 Grad(SiO<sub>2</sub>) on the drain leakage current of *n*MOSFETs fabricated with a commercial 28-nm bulk CMOS process. Static measurements demonstrate a significant increase up to four orders of magnitude in the drain leakage current. At high TID levels, the drain leakage current is independent of the width but dependent on the length and the number of fingers, indicating the dominant contribution of the TID-induced lateral parasitic devices.

We model the parallel parasitic and total drain leakage current as a function of TID with a semiempirical physicsbased approach. Using only three parameters, model results have a good agreement with measurements. One of those three parameters is the critical total dose that is defined as the TID, above which the parallel parasitic drain-to-source leakage current dominates the total drain leakage current. This model provides a practical way of predicting the parallel parasitic drain-to-source leakage current.

Owing to the gate independence of the drain leakage current at high TID levels, we model the lateral parasitic device as a gateless device that is fully controlled by STI-related trapped charges. The simplified charge-based EKV MOSFET model indicates that even at 1 Grad, the STI-related trapped-charge density is not high enough to bias the lateral parasitic device in strong inversion. The weak inversion approximation gives a direct link between the STI-related trapped-charge density and the parallel parasitic drain-to-source leakage current, indicating the advantage of a higher channel doping concentration in terms of radiation-induced static power consumption.

## ACKNOWLEDGMENT

The authors would like to thank Dr. A. Pezzotta from ICLAB of EPFL for his support. They would also like to thank H. D. Koch from the Experimental Physics Department, CERN and University of Mons, for the great help with the measurements.

#### REFERENCES

"Technical design report for the ATLAS inner tracker pixel detector," ATLAS Collaboration, Tech. Rep. CERN-LHCC-2017-021, ATLAS-TDR-030, 2017.

- [2] K. Einsweiler and L. Pontecorvo, "ATLAS phase-II upgrade scoping document," CERN, Geneva, Switzerland, Tech. Rep. CERN-LHCC-2015-019, 2015.

- [3] J. Butler *et al.*, "CMS phase II upgrade scope document," CERN, Geneva, Switzerland, Tech. Rep. CERN-LHCC-2015-020, 2015.

- [4] P. E. Dodd, M. R. Shaneyfelt, J. R. Schwank, and J. A. Felix, "Current and future challenges in radiation effects on CMOS electronics," *IEEE Trans. Nucl. Sci.*, vol. 57, no. 4, pp. 1747–1763, Aug. 2010.

- [5] F. Ellinger, M. Claus, M. Schröter, and C. Carta, "Review of advanced and Beyond CMOS FET technologies for radio frequency circuit design," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Oct. 2011, pp. 347–351.

- [6] J. M. Benedetto, H. E. Boesch, F. B. McLean, and J. P. Mize, "Hole removal in thin-gate MOSFETs by tunneling," *IEEE Trans. Nucl. Sci.*, vol. 32, no. 6, pp. 3916–3920, Dec. 1985.

- [7] D. M. Fleetwood, "Evolution of total ionizing dose effects in MOS devices with Moore's law scaling," *IEEE Trans. Nucl. Sci.*, vol. 65, no. 8, pp. 1465–1481, Aug. 2018.

- [8] F. Faccio, S. Michelis, D. Cornale, A. Paccagnella, and S. Gerardin, "Radiation-induced short channel (RISCE) and narrow channel (RINCE) effects in 65 and 130 nm MOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 62, no. 6, pp. 2933–2940, Dec. 2015.

- [9] F. Faccio et al., "Influence of LDD spacers and H<sup>+</sup> transport on the total-ionizing-dose response of 65-nm MOSFETs irradiated to ultrahigh doses," *IEEE Trans. Nucl. Sci.*, vol. 65, no. 1, pp. 164–174, Jan. 2018.

- [10] A. Pezzotta *et al.*, "Impact of GigaRad ionizing dose on 28 nm bulk MOSFETs for future HL-LHC," in *Proc. 46th Eur. Solid-State Device Res. Conf. (ESSDERC)*, Sep. 2016, pp. 146–149.

- [11] C. M. Zhang *et al.*, "Characterization of GigaRad total ionizing dose and annealing effects on 28-nm bulk MOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 64, no. 10, pp. 2639–2647, Oct. 2017.

- [12] C.-M. Zhang *et al.*, "Total ionizing dose effects on analog performance of 28 nm bulk MOSFETs," in *Proc. 47th Eur. Solid-State Device Res. Conf. (ESSDERC)*, Sep. 2017, pp. 30–33.

- [13] F. Faccio and G. Cervelli, "Radiation-induced edge effects in deep submicron CMOS transistors," *IEEE Trans. Nucl. Sci.*, vol. 52, no. 6, pp. 2413–2420, Dec. 2005.

- [14] M. Gaillardin, V. Goiffon, S. Girard, M. Martinez, P. Magnan, and P. Paillet, "Enhanced radiation-induced narrow channel effects in commercial 0.18 μm bulk technology," *IEEE Trans. Nucl. Sci.*, vol. 58, no. 6, pp. 2807–2815, Dec. 2011.

- [15] M. Gaillardin *et al.*, "Investigations on the vulnerability of advanced CMOS technologies to MGy dose environments," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 4, pp. 2590–2597, Aug. 2013.

- [16] M. L. McLain, H. J. Barnaby, and G. Schlenvogt, "Effects of channel implant variation on radiation-induced edge leakage currents in n-channel MOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 64, no. 8, pp. 2235–2241, Aug. 2017.

- [17] L. Ratti, L. Gaioni, M. Manghisoni, V. Re, and G. Traversi, "TIDinduced degradation in static and noise behavior of Sub-100 nm multifinger bulk NMOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 58, no. 3, pp. 776–784, Jun. 2011.

- [18] K. Choi et al., "The past, present and future of high-k/metal gates," ECS Trans., vol. 53, no. 3, pp. 17–26, 2013.

- [19] I. S. Esqueda, J. H. Barnaby, and M. L. Alles, "Two-dimensional methodology for modeling radiation-induced off-state leakage in CMOS technologies," *IEEE Trans. Nucl. Sci.*, vol. 52, no. 6, pp. 2259–2264, Dec. 2005.

- [20] M. Turowski, A. Raman, and R. D. Schrimpf, "Nonuniform total-doseinduced charge distribution in shallow-trench isolation oxides," *IEEE Trans. Nucl. Sci.*, vol. 51, no. 6, pp. 3166–3171, Dec. 2004.

- [21] A. H. Johnston, R. T. Swimm, G. R. Allen, and T. F. Miyahira, "Total dose effects in CMOS trench isolation regions," *IEEE Trans. Nucl. Sci.*, vol. 56, no. 4, pp. 1941–1949, Aug. 2009.

- [22] G. I. Zebrev and M. S. Gorbunov, "Modeling of radiation-induced leakage and low dose-rate effects in thick edge isolation of modern MOSFETs," *IEEE Trans. Nucl. Sci.*, vol. 56, no. 4, pp. 2230–2236, Aug. 2009.

- [23] H. J. Barnaby, M. L. McLain, I. S. Esqueda, and X. J. Chen, "Modeling ionizing radiation effects in solid state materials and CMOS devices," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 56, no. 8, pp. 1870–1883, Aug. 2009.

- [24] P. V. Dressendorfer, J. M. Soden, J. J. Harrington, and T. V. Nordstrom, "The effects of test conditions on MOS radiation-hardness results," *IEEE Trans. Nucl. Sci.*, vol. 28, no. 6, pp. 4281–4287, Dec. 1981.

- [25] C.-M. Zhang, F. Jazaeri, G. Borghello, S. Mattiazzo, A. Baschirotto, and C. Enz, "Bias dependence of total ionizing dose effects on 28 nm Bulk MOSFETs," in *Proc. IEEE Nucl. Sci. Symp. (NSS)*, Nov. 2018.

- [26] G. F. Derbenwick and H. H. Sander, "CMOS hardness prediction for low-dose-rate environments," *IEEE Trans. Nucl. Sci.*, vol. 24, no. 6, pp. 2244–2247, Dec. 1977.

- [27] J. R. Schwank, P. S. Winokur, P. J. McWhorter, F. W. Sexton, P. V. Dressendorfer, and D. C. Turpin, "Physical mechanisms contributing to device 'rebound," *IEEE Trans. Nucl. Sci.*, vol. NS-31, no. 6, pp. 1434–1438, Dec. 1984.

- [28] K. Roy, S. Mukhopadhyay, and H. Mahmoodi-Meimand, "Leakage current mechanisms and leakage reduction techniques in deepsubmicrometer CMOS circuits," *Proc. IEEE*, vol. 91, no. 2, pp. 305–327, Feb. 2003.

- [29] I. S. Esqueda, H. J. Barnaby, K. E. Holbert, F. El-Mamouni, and R. D. Schrimpf, "Modeling of ionizing radiation-induced degradation in multiple gate field effect transistors," in *Proc. Eur. Conf. Radiat. Effects Compon. Syst.*, Sep. 2009, pp. 2–6.

- [30] S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*. Hoboken, NJ, USA: Wiley, 2007.

- [31] C. Enz, F. Chicco, and A. Pezzotta, "Nanoscale MOSFET modeling: Part 1: The simplified EKV model for the design of low-power analog circuits," *IEEE Solid-State Circuits Mag.*, vol. 9, no. 3, pp. 26–35, 2017.

- [32] C. Enz, F. Chicco, and A. Pezzotta, "Nanoscale MOSFET modeling: Part 2: Using the inversion coefficient as the primary design parameter," *IEEE Solid-State Circuits Mag.*, vol. 9, no. 4, pp. 73–81, 2017.

- [33] C. C. Enz and E. A. Vittoz, Charge-Based MOS Transistor Modeling: The EKV Model for Low-Power and RF IC Design. Hoboken, NJ, USA: Wiley, 2006.

- [34] A. Mangla, M.-A. Chalkiadaki, F. Fadhuile, T. Taris, Y. Deval, and C. C. Enz, "Design Methodology for ultra low-power analog circuits using next generation BSIM6 MOSFET compact model," *Microelectron. J.*, vol. 44, no. 7, pp. 570–575, 2013.

- [35] G. I. Zebrev, V. V. Orlov, M. S. Gorbunov, and M. G. Drosdetsky, "Physics-based modeling of TID induced global static leakage in different CMOS circuits," *Microelectron. Rel.*, vol. 84, pp. 181–186, May 2018.