# The DUNE Far Detector Interim Design Report Volume 2: Single-Phase Module

Deep Underground Neutrino Experiment (DUNE)

FERMILAB-DESIGN-2018-02

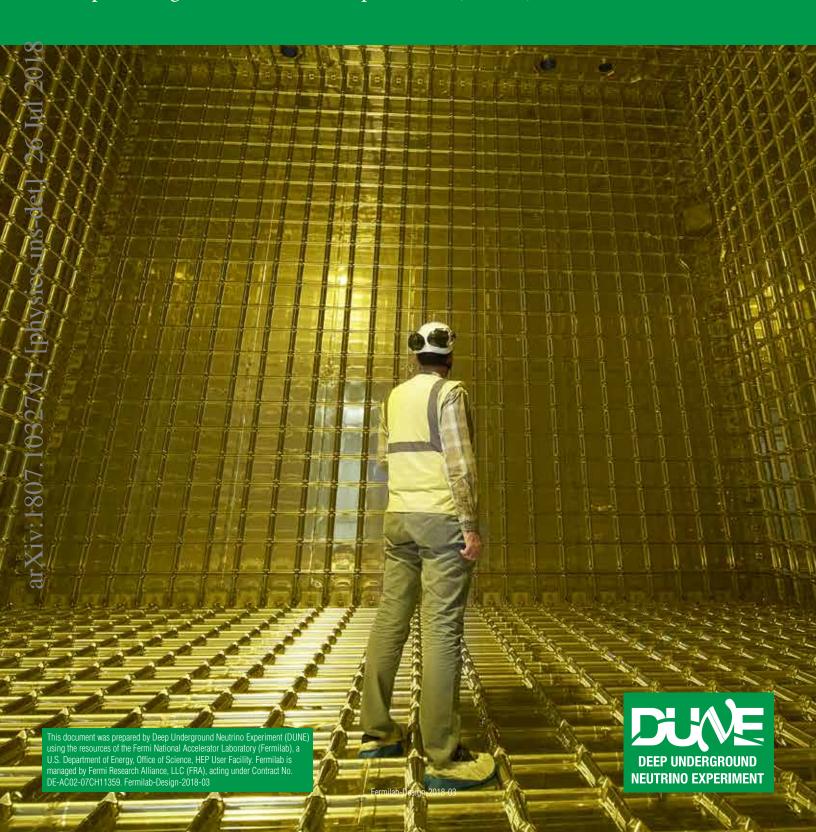

Cover design: Diana Brandonisio, Fermilab Creative Services, July 2018

Cover photo: "Inside ProtoDUNE" by Maximilien Brice, ©CERN, November 2017

#### Authors

```

B. Abi, 125 R. Acciarri, 54 M. A. Acero, 8 M. Adamowski, 54 C. Adams, 62 D. Adams, 15 P. Adamson, 54 M. Adinolfi, 14

Z. Ahmad, <sup>165</sup> C. H. Albright, <sup>54</sup> L. Aliaga Soplin, <sup>54</sup> T. Alion, <sup>152</sup> S. Alonso Monsalve, <sup>20</sup> M. Alrashed, <sup>89</sup> C. Alt, <sup>47</sup>

J. Anderson, K. Anderson, A. Andrews, M. P. Andrews, A. Andrews, M. Andrews, A. Andrews, A

J. Anthony, <sup>27</sup> M. Antonello, <sup>58</sup> M. Antonova, <sup>68</sup> S. Antusch, <sup>10</sup> A. Aranda Fernandez, <sup>34</sup> A. Ariga, <sup>11</sup> T. Ariga, <sup>11</sup>

D. Aristizabal Sierra, <sup>154</sup> E. Arrieta Diaz, <sup>150</sup> J. Asaadi, <sup>157</sup> M. Ascencio, <sup>135</sup> D. Asner, <sup>15</sup> M. S. Athar, <sup>1</sup> M. Auger, <sup>11</sup>

A. Aurisano, <sup>32</sup> V. Aushev, <sup>94</sup> D. Autiero, <sup>79</sup> F. Azfar, <sup>125</sup> A. Back, <sup>82</sup> H. Back, <sup>126</sup> J. Back, <sup>170</sup> C. Backhouse, <sup>100</sup>

P. Baesso, <sup>14</sup> L. Bagby, <sup>54</sup> X. Bai, <sup>147</sup> M. Baird, <sup>167</sup> B. Balantekin, <sup>173</sup> S. Balasubramanian, <sup>175</sup> B. Baller, <sup>54</sup> P. Ballett, <sup>46</sup>

L. Balleyguier, <sup>79</sup> B. Bambah, <sup>66</sup> H. Band, <sup>175</sup> M. Bansal, <sup>129</sup> S. Bansal, <sup>129</sup> G. Barenboim, <sup>68</sup> G. J. Barker, <sup>170</sup>

C. Barnes, <sup>108</sup> G. Barr, <sup>125</sup> J. Barranco Monarca, <sup>60</sup> N. Barros, <sup>132</sup> J. Barrow, <sup>155</sup> A. Bashyal, <sup>123</sup> V. Basque, <sup>105</sup>

M. Bass, <sup>15</sup> F. Bay, <sup>160</sup> K. Bays, <sup>26</sup> J. L. Bazo, <sup>135</sup> J. F. Beacom, <sup>122</sup> E. Bechetoille, <sup>79</sup> B. R. Behera, <sup>129</sup> L. Bellantoni, <sup>54</sup>

G. Bellettini, <sup>133</sup> V. Bellini, <sup>28</sup> O. Beltramello, <sup>20</sup> D. Belver, <sup>21</sup> N. Benekos, <sup>20</sup> P. A. Benetti, <sup>130</sup> A. Bercellie, <sup>139</sup>

E. Berman, <sup>54</sup> P. Bernardini, <sup>164</sup> R. Berner, <sup>11</sup> H.-G. Berns, <sup>23</sup> R. H. Bernstein, <sup>54</sup> S. Bertolucci, <sup>74</sup> M. Betancourt, <sup>54</sup>

V. Bhatnagar, ^{129} M. Bhat<br/>tacharjee, ^{71} B. Bhuyan, ^{71} S. Biagi,<br/> ^{96} J. Bian, ^{24} K. Biery, ^{54} B. Bilki,<br/> ^{81} M. Bishai, ^{15}

A. Bitadze, <sup>105</sup> T. Blackburn, <sup>152</sup> A. Blake, <sup>97</sup> B. Blanco Siffert, <sup>51</sup> F. Blaszczyk, <sup>13</sup> E. Blaufuss, <sup>106</sup> G. C. Blazey, <sup>113</sup>

M. Blennow, <sup>88</sup> E. Blucher, <sup>30</sup> V. Bocean, <sup>54</sup> F. Boffelli, <sup>130</sup> J. Boissevain, <sup>101</sup> S. Bolognesi, <sup>19</sup> T. Bolton, <sup>89</sup>

M. Bonesini,<sup>73</sup> T. Boone,<sup>36</sup> A. Booth,<sup>152</sup> C. Booth,<sup>143</sup> S. Bordoni,<sup>20</sup> A. Borkum,<sup>152</sup> T. Boschi,<sup>46</sup> P. Bour,<sup>39</sup>

B. Bourguille, <sup>67</sup> S. B. Boyd, <sup>170</sup> D. Boyden, <sup>113</sup> J. Bracinik, <sup>12</sup> D. Brailsford, <sup>97</sup> A. Brandt, <sup>157</sup> J. Bremer, <sup>20</sup>

S. J. Brice, <sup>54</sup> C. Bromberg, <sup>109</sup> G. Brooijmans, <sup>37</sup> J. Brooke, <sup>14</sup> G. Brown, <sup>157</sup> N. Buchanan, <sup>36</sup> H. Budd, <sup>139</sup>

P. C. de Holanda, <sup>49</sup> T. Cai, <sup>139</sup> D. Caiulo, <sup>79</sup> P. Calafiura, <sup>98</sup> A. Calatayud, <sup>135</sup> J. Calcutt, <sup>109</sup> C. Callahan, <sup>132</sup>

E. Calligarich, <sup>130</sup> E. Calvo, <sup>21</sup> L. Camilleri, <sup>37</sup> A. Caminata, <sup>56</sup> M. Campanelli, <sup>100</sup> G. Cancelo, <sup>54</sup> K. Cankocak, <sup>81</sup>

C. Cantini, <sup>47</sup> D. Caratelli, <sup>54</sup> B. Carlus, <sup>79</sup> M. Carneiro, <sup>123</sup> I. Caro Terrazas, <sup>36</sup> T. J. Carroll, <sup>158</sup> M. P. Carvallo, <sup>151</sup>

M. Cascella, <sup>100</sup> C. Castromonte, <sup>114</sup> E. Catano-Mur, <sup>82</sup> M. Cavalli-Sforza, <sup>67</sup> F. Cavanna, <sup>54</sup> E. Cazzato, <sup>10</sup>

S. Centro, <sup>128</sup> G. Cerati, <sup>54</sup> A. Cervelli, <sup>74</sup> A. Cervera Villanueva, <sup>68</sup> T. Cervi, <sup>130</sup> M. Chalifour, <sup>20</sup> A. Chappuis, <sup>95</sup>

A. Chatterjee, <sup>157</sup> S. Chattopadhyay, <sup>54</sup> S. Chattopadhyay, <sup>165</sup> J. Chaves, <sup>132</sup> H. Chen, <sup>15</sup> M.-C. Chen, <sup>24</sup>

S. Chen, <sup>159</sup> D. Cherdack, <sup>36</sup> C.-Y. Chi, <sup>37</sup> S. Childress, <sup>54</sup> K. Cho, <sup>92</sup> S. Choubey, <sup>61</sup> B. C. Choudhary, <sup>43</sup>

A. Christensen, <sup>36</sup> D. Christian, <sup>54</sup> G. Christodoulou, <sup>99</sup> C.-A. Christofferson, <sup>147</sup> E. Church, <sup>126</sup> P. Clarke, <sup>48</sup>

T. E. Coan, <sup>150</sup> A. Cocco, <sup>115</sup> G. H. Collin, <sup>107</sup> E. Conley, <sup>45</sup> J. M. Conrad, <sup>107</sup> M. Convery, <sup>140</sup> R. Corey, <sup>147</sup>

L. Corwin, <sup>147</sup> P. Cotte, <sup>19</sup> L. Cremonesi, <sup>100</sup> J. I. Crespo-Anadón, <sup>37</sup> J. Creus Prats, <sup>20</sup> E. Cristaldo, <sup>163</sup> P. Crivelli, <sup>47</sup>

D. Cronin-Hennessy, <sup>112</sup> C. Crowley, <sup>54</sup> C. Cuesta, <sup>21</sup> A. Curioni, <sup>73</sup> D. Cussans, <sup>14</sup> M. Dabrowski, <sup>15</sup> D. Dale, <sup>76</sup>

H. Da Motta, <sup>18</sup> T. Davenne, <sup>141</sup> E. Davenport, <sup>157</sup> G. S. Davies, <sup>78</sup> J. Davies, <sup>152</sup> S. Davini, <sup>56</sup> J. Dawson, <sup>4</sup> K. De, <sup>157</sup>

M. P. Decowski, <sup>119</sup> P. Dedin Neto, <sup>49</sup> I. de Icaza Astiz, <sup>152</sup> A. Delbart, <sup>19</sup> D. Delepine, <sup>60</sup> M. Delgado, <sup>3</sup> A. Dell, <sup>20</sup>

J. de Mello Neto, <sup>51</sup> D. DeMuth, <sup>166</sup> Z. Deng, <sup>159</sup> S. Dennis, <sup>99</sup> C. Densham, <sup>141</sup> I. De Bonis, <sup>95</sup> A. De Gouvêa, <sup>120</sup>

P. De Jong, <sup>119</sup> P. De Lurgio, <sup>5</sup> S. De Rijck, <sup>158</sup> A. De Roeck, <sup>20</sup> J. J. de Vries, <sup>27</sup> R. Dharmapalan, <sup>5</sup> N. Dhingra, <sup>129</sup>

M. Diamantopoulou, F. Diaz, 135 J. S. Díaz, 78 G. Diaz Bautista, 139 P. Ding, 54 C. Distefano, 96 M. Diwan, 15

S. Di Domizio, <sup>56</sup> L. Di Giulio, <sup>20</sup> S. Di Luise, <sup>67</sup> Z. Djurcic, <sup>5</sup> F. Doizon, <sup>79</sup> N. Dokania, <sup>151</sup> M. J. Dolinski, <sup>44</sup>

R. Dong, <sup>81</sup> J. dos Anjos, <sup>18</sup> D. Douglas, <sup>109</sup> G. Drake, <sup>5</sup> D. Duchesneau, <sup>95</sup> K. Duffy, <sup>54</sup> B. Dung, <sup>158</sup> D. Dutta, <sup>61</sup>

M. Duvernois, <sup>173</sup> H. Duyang, <sup>145</sup> O. Dvornikov, <sup>63</sup> D. A. Dwyer, <sup>98</sup> S. Dye, <sup>63</sup> A. S. Dyshkant, <sup>113</sup> S. Dytman, <sup>134</sup>

M. Eads, <sup>113</sup> B. Eberly, <sup>140</sup> D. Edmunds, <sup>109</sup> J. Eisch, <sup>82</sup> A. Elagin, <sup>30</sup> S. Elliott, <sup>101</sup> W. Ellsworth, <sup>64</sup> M. Elnimr, <sup>24</sup> S. Emery, <sup>19</sup> S. Eno, <sup>106</sup> A. Ereditato, <sup>11</sup> C. O. Escobar, <sup>54</sup> L. Escudero Sanchez, <sup>27</sup> J. J. Evans, <sup>105</sup> A. Ezeribe, <sup>143</sup>

K. Fahey, <sup>54</sup> A. Falcone, <sup>157</sup> L. Falk, <sup>152</sup> A. Farbin, <sup>157</sup> C. Farnese, <sup>128</sup> Y. Farzan, <sup>75</sup> M. Fasoli, <sup>73</sup> A. Fava, <sup>54</sup> J. Felix, <sup>60</sup>

E. Fernandez-Martinez, <sup>104</sup> P. Fernandez Menendez, <sup>68</sup> F. Ferraro, <sup>56</sup> F. Feyzi, <sup>54</sup> L. Fields, <sup>54</sup> A. Filkins, <sup>172</sup>

F. Filthaut, <sup>119</sup> A. Finch, <sup>97</sup> O. Fischer, <sup>10</sup> M. Fitton, <sup>141</sup> R. Fitzpatrick, <sup>108</sup> W. Flanagan, <sup>41</sup> B. T. Fleming, <sup>175</sup>

R. Flight, <sup>139</sup> T. Forest, <sup>76</sup> J. Fowler, <sup>45</sup> W. Fox, <sup>78</sup> J. Franc, <sup>39</sup> K. Francis, <sup>113</sup> P. Franchini, <sup>170</sup> D. Franco, <sup>175</sup>

J. Freeman,<sup>54</sup> J. Freestone,<sup>105</sup> J. Fried,<sup>15</sup> A. Friedland,<sup>140</sup> S. Fuess,<sup>54</sup> I. Furic,<sup>55</sup> A. Furmanski,<sup>105</sup> A. M. Gago,<sup>135</sup>

H. Gallagher, <sup>161</sup> A. Gallego-Ros, <sup>21</sup> V. Galymov, <sup>79</sup> E. Gamberini, <sup>20</sup> S. Gambetta, <sup>20</sup> T. Gamble, <sup>143</sup> R. Gandhi, <sup>61</sup>

R. Gandrajula, <sup>109</sup> S. Gao, <sup>15</sup> D. Garcia-Gamez, <sup>105</sup> S. Gardiner, <sup>23</sup> D. Gastler, <sup>13</sup> J. Gehrlein, <sup>104</sup> B. Gelli, <sup>49</sup> A. Gendotti, <sup>47</sup> Z. Ghorbani-Moghaddam, <sup>23</sup> A. Ghosh, <sup>154</sup> D. Gibin, <sup>128</sup> I. Gil-Botella, <sup>21</sup> C. Girerd, <sup>79</sup> A. K. Giri, <sup>72</sup>

S. Glavin, <sup>132</sup> D. Goeldi, <sup>11</sup> O. Gogota, <sup>94</sup> M. Gold, <sup>117</sup> S. Gollapinni, <sup>155</sup> K. Gollwitzer, <sup>54</sup> R. A. Gomes, <sup>57</sup> L. Gomez, <sup>142</sup>

L. V. Gomez Bermeo, <sup>142</sup> J. J. Gomez Cadenas, <sup>68</sup> H. Gong, <sup>159</sup> F. Gonnella, <sup>12</sup> J. A. Gonzalez-Cuevas, <sup>163</sup>

M. Goodman,<sup>5</sup> O. Goodwin,<sup>105</sup> D. Gorbunov,<sup>80</sup> S. Goswami,<sup>127</sup> E. Goudzovski,<sup>12</sup> C. Grace,<sup>98</sup> N. Graf,<sup>134</sup>

N. Graf, <sup>140</sup> M. Graham, <sup>140</sup> E. Gramellini, <sup>175</sup> R. Gran, <sup>111</sup> A. Grant, <sup>42</sup> C. Grant, <sup>13</sup> N. Grant, <sup>170</sup> V. Greco, <sup>28</sup>

S. Green, <sup>27</sup> H. Greenlee, <sup>54</sup> L. Greenler, <sup>173</sup> M. Greenwood, <sup>123</sup> J. Greer, <sup>14</sup> W. C. Griffith, <sup>152</sup> M. Groh, <sup>78</sup>

```

J. Grudzinski, K. Grzelak, G. Guanghua, E. Guardincerri, V. Guarino, G. P. Guedes, R. Guenette, Caracteria, R. Guenette, G. Guardincerri, E. Guardincerri, V. Guarino, G. P. Guedes, R. Guenette, G. Guanghua, R. Guardincerri, R. A. Guglielmi, <sup>128</sup> B. Guo, <sup>145</sup> S. Gupta, <sup>84</sup> V. Gupta, <sup>71</sup> K. K. Guthikonda, <sup>91</sup> R. Gutierrez, <sup>3</sup> P. Guzowski, <sup>105</sup> M. M. Guzzo,<sup>49</sup> A. Habig,<sup>111</sup> R. W. Hackenburg,<sup>15</sup> A. Hackenburg,<sup>175</sup> B. Hackett,<sup>63</sup> H. Hadavand,<sup>157</sup> R. Haenni, <sup>11</sup> A. Hahn, <sup>54</sup> J. Haigh, <sup>170</sup> T. Haines, <sup>101</sup> J. Haiston, <sup>147</sup> T. Hamernik, <sup>54</sup> P. Hamilton, <sup>153</sup> J. Han, <sup>134</sup> T. Handler, <sup>155</sup> S. Hans, <sup>15</sup> D. A. Harris, <sup>54</sup> J. Hartnell, <sup>152</sup> T. Hasegawa, <sup>87</sup> R. Hatcher, <sup>54</sup> A. Hatzikoutelis, <sup>155</sup> S. Hays,<sup>54</sup> E. Hazen,<sup>13</sup> M. Headley,<sup>148</sup> A. Heavey,<sup>54</sup> K. Heegerv,<sup>175</sup> J. Heise,<sup>148</sup> K. Hennessy,<sup>99</sup> S. Henry,<sup>139</sup> A. Hernandez, J. Hernandez-Garcia, 104 K. Herner, 4 V Hewes, 2 J. Hignight, 109 A. Higuera, 4 T. Hill, 76 S. Hillier, <sup>12</sup> A. Himmel, <sup>54</sup> C. Hohl, <sup>10</sup> A. Holin, <sup>100</sup> E. Hoppe, <sup>126</sup> S. Horikawa, <sup>47</sup> G. Horton-Smith, <sup>89</sup> M. Hostert, <sup>46</sup> A. Hourlier, <sup>107</sup> B. Howard, <sup>78</sup> R. Howell, <sup>139</sup> J. Huang, <sup>158</sup> J. Hugon, <sup>102</sup> P. Hurh, <sup>54</sup> J. Hylen, <sup>54</sup> R. Illingworth, <sup>54</sup> J. Insler, <sup>44</sup> G. Introzzi, <sup>130</sup> A. Ioannisian, <sup>176</sup> A. Izmaylov, <sup>68</sup> D. E. Jaffe, <sup>15</sup> C. James, <sup>54</sup> E. James, <sup>54</sup> C.-H. Jang, <sup>31</sup> F. Jediny, <sup>39</sup> Y. S. Jeong, <sup>6</sup> A. Jhingan, <sup>129</sup> W. Ji, <sup>15</sup> A. Jipa, <sup>16</sup> S. Jiménez, <sup>21</sup> C. Johnson, <sup>36</sup> M. Johnson, <sup>54</sup> R. Johnson, <sup>32</sup> J. Johnstone, <sup>54</sup> B. Jones, <sup>157</sup> S. Jones, <sup>100</sup> J. Joshi, <sup>15</sup> H. Jostlein, <sup>54</sup> C. K. Jung, <sup>151</sup> T. Junk, <sup>54</sup> A. Kaboth, <sup>141</sup> I. Kadenko, <sup>94</sup> F. Kamiya, <sup>52</sup> Y. Kamyshkov, <sup>155</sup> G. Karagiorgi, <sup>37</sup> D. Karasavvas, <sup>7</sup> Y. Karyotakis, <sup>95</sup> S. Kasai, <sup>93</sup> S. Kasetti, <sup>102</sup> K. Kaur, <sup>129</sup> B. Kayser, <sup>54</sup> N. Kazaryan, <sup>176</sup> E. Kearns, <sup>13</sup> P. Keener, <sup>132</sup> E. Kemp, <sup>49</sup> C. Kendziora,<sup>54</sup> W. Ketchum,<sup>54</sup> S. H. Kettell,<sup>15</sup> M. Khabibullin,<sup>80</sup> A. Khotjantsev,<sup>80</sup> D. Kim,<sup>20</sup> B. Kirby,<sup>15</sup> M. Kirby, <sup>54</sup> J. Klein, <sup>132</sup> Y.-J. Ko, <sup>31</sup> T. Kobilarcik, <sup>54</sup> B. Kocaman, <sup>160</sup> L. W. Koerner, <sup>64</sup> S. Kohn, <sup>22</sup> G. Koizumi, <sup>54</sup> P. Koller, <sup>11</sup> A. Kopylov, <sup>80</sup> M. Kordosky, <sup>172</sup> L. Kormos, <sup>97</sup> T. Kosc, <sup>79</sup> U. Kose, <sup>20</sup> V. A. Kostelecký, <sup>78</sup> K. Kothekar, <sup>14</sup> M. Kramer, <sup>22</sup> F. Krennrich, <sup>82</sup> I. Kreslo, <sup>11</sup> K. Kriesel, <sup>173</sup> W. Kropp, <sup>24</sup> Y. Kudenko, <sup>80</sup> V. A. Kudryavtsev, <sup>143</sup> S. Kulagin, <sup>80</sup> J. Kumar, <sup>63</sup> L. Kumar, <sup>129</sup> A. Kumar, <sup>129</sup> S. Kumbhare, <sup>157</sup> C. Kuruppu, <sup>145</sup> V. Kus, <sup>39</sup> T. Kutter, <sup>102</sup> R.  $LaZur,^{36}$  K.  $Lande,^{132}$  C.  $Lane,^{44}$  K.  $Lang,^{158}$  T.  $Langford,^{175}$  F.  $Lanni,^{15}$  P.  $Lasorak,^{152}$  D.  $Last,^{132}$ C. Lastoria, <sup>21</sup> A. Laundrie, <sup>173</sup> I. Lazanu, <sup>16</sup> T. Le, <sup>161</sup> J. Learned, <sup>63</sup> P. Lebrun, <sup>54</sup> D. Lee, <sup>101</sup> G. Lehmann Miotto, <sup>20</sup> M. A. Leigui de Oliveira, <sup>52</sup> Q. Li, <sup>54</sup> S. Li, <sup>15</sup> S. W. Li, <sup>140</sup> X. Li, <sup>151</sup> Y. Li, <sup>15</sup> Z. Li, <sup>45</sup> H.-Y. Liao, <sup>89</sup> S.-K. Lin, <sup>36</sup> C-J. S. Lin, 98 R. Linehan, 140 V. Linhart, 39 J. Link, 167 Z. Liptak, 35 D. Lissauer, 15 L. Littenberg, 15 B. Littlejohn, 69 J. Liu, <sup>146</sup> T. Liu, <sup>150</sup> L. LoMonaco, <sup>28</sup> J. M. LoSecco, <sup>121</sup> S. Lockwitz, <sup>54</sup> N. Lockyer, <sup>54</sup> T. Loew, <sup>98</sup> M. Lokajicek, <sup>17</sup> K. Long, 77 K. Loo, 86 J. P. Lopez, 35 D. Lorca, 11 T. Lord, 170 M. Losada, W. C. Louis, 101 M. Luethi, 11 K.-B. Luk, 22 T. Lundin, <sup>54</sup> X. Luo, <sup>175</sup> N. Lurkin, <sup>12</sup> T. Lux, <sup>67</sup> V. P. Luzio, <sup>52</sup> J. Lykken, <sup>54</sup> J. Maalampi, <sup>86</sup> R. MacLellan, <sup>146</sup> A. A. Machado, <sup>52</sup> P. Machado, <sup>54</sup> C. T. Macias, <sup>78</sup> J. Macier, <sup>54</sup> P. Madigan, <sup>22</sup> S. Magill, <sup>5</sup> G. Mahler, <sup>15</sup> K. Mahn, <sup>109</sup> M. Malek, <sup>143</sup> J. A. Maloney, <sup>40</sup> F. Mammoliti, <sup>62</sup> S. K. Mandal, <sup>43</sup> G. Mandrioli, <sup>74</sup> L. Manenti, <sup>100</sup> S. Manly, <sup>139</sup> A. Mann, <sup>161</sup> A. Marchionni, <sup>54</sup> W. Marciano, <sup>15</sup> S. Marcocci, <sup>54</sup> D. Marfatia, <sup>63</sup> C. Mariani, <sup>167</sup> J. Maricic, <sup>63</sup> F. Marinho, <sup>162</sup> A. D. Marino, <sup>35</sup> M. Marshak, <sup>112</sup> C. Marshall, <sup>98</sup> J. Marshall, <sup>27</sup> J. Marteau, <sup>79</sup> J. Martin-Albo, <sup>125</sup> D. Martinez, <sup>69</sup> N. Martinez, <sup>137</sup> H. Martinez, <sup>142</sup> K. Mason, <sup>161</sup> A. Mastbaum, <sup>30</sup> M. Masud, <sup>68</sup> H. Mathez, <sup>79</sup> S. Matsuno, <sup>63</sup> J. Matthews, <sup>102</sup> C. Mauger, <sup>132</sup> N. Mauri, <sup>74</sup> K. Mavrokoridis, <sup>99</sup> R. Mazza, <sup>73</sup> A. Mazzacane, <sup>54</sup> E. Mazzucato, <sup>19</sup> N. McCauley, <sup>99</sup> E. McCluskey, <sup>54</sup> N. McConkey, <sup>143</sup> K. McDonald, <sup>136</sup> K. S. McFarland, <sup>139</sup> C. McGivern, <sup>54</sup> A. McGowan, <sup>139</sup> C. McGrew, <sup>151</sup> R. McKeown, <sup>172</sup> A. McNab, <sup>105</sup> D. McNulty, <sup>76</sup> R. McTaggart, <sup>149</sup> V. Meddage, <sup>89</sup> A. Mefodiev, <sup>80</sup> P. Mehta, <sup>85</sup> D. Mei, <sup>146</sup> O. Mena, <sup>68</sup> S. Menary, <sup>177</sup> H. Mendez, <sup>137</sup> D. P. Mendez, <sup>152</sup> A. Menegolli,  $^{130}$  G. Meng,  $^{128}$  M. Messier,  $^{78}$  W. Metcalf,  $^{102}$  M. Mewes,  $^{78}$  H. Meyer,  $^{171}$  T. Miao,  $^{54}$  J. Migenda,  $^{143}$  R. Milincic,  $^{63}$  J. Miller,  $^{154}$  W. Miller,  $^{112}$  J. Mills,  $^{161}$  C. Milne,  $^{76}$  O. Mineev,  $^{80}$  O. Miranda,  $^{33}$  C. S. Mishra,  $^{54}$ S. R. Mishra, <sup>145</sup> A. Mislivec, <sup>112</sup> B. Mitrica, <sup>65</sup> D. Mladenov, <sup>20</sup> I. Mocioiu, <sup>131</sup> K. Moffat, <sup>46</sup> N. Moggi, <sup>74</sup> R. Mohanta, <sup>66</sup> N. Mokhov,<sup>54</sup> J. Molina,<sup>163</sup> L. Molina Bueno,<sup>47</sup> A. Montanari,<sup>74</sup> C. Montanari,<sup>130</sup> D. Montanari,<sup>54</sup> L. Montano Zetina, <sup>33</sup> J. Moon, <sup>107</sup> M. Mooney, <sup>36</sup> C. Moore, <sup>54</sup> D. Moreno, <sup>3</sup> B. Morgan, <sup>170</sup> G. F. Moroni, <sup>54</sup> C. Morris, <sup>64</sup> W. Morse, <sup>15</sup> C. Mossey, <sup>54</sup> C. A. Moura, <sup>52</sup> J. Mousseau, <sup>108</sup> L. Mualem, <sup>26</sup> M. Muether, <sup>171</sup> S. Mufson, <sup>78</sup> F. Muheim, <sup>48</sup> H. Muramatsu, <sup>112</sup> S. Murphy, <sup>47</sup> J. Musser, <sup>78</sup> J. Nachtman, <sup>81</sup> M. Nalbandyan, <sup>176</sup> R. Nandakumar, <sup>141</sup> D. Naples, <sup>134</sup> S. Narita, <sup>83</sup> G. Navarro, <sup>3</sup> J. Navarro, <sup>8</sup> D. Navas-Nicolás, <sup>21</sup> N. Nayak, <sup>24</sup> M. Nebot-Guinot, <sup>48</sup> M. Needham, <sup>48</sup> K. Negishi, <sup>83</sup> J. Nelson, <sup>172</sup> M. Nessi, <sup>20</sup> D. Newbold, <sup>14</sup> M. Newcomer, <sup>132</sup> R. Nichol, <sup>100</sup> T. C. Nicholls, <sup>141</sup> E. Niner, <sup>54</sup> A. Norman, <sup>54</sup> B. Norris, <sup>54</sup> J. Norris, <sup>76</sup> P. Novella, <sup>68</sup> E. Nowak, <sup>20</sup> J. Nowak, <sup>97</sup> M. S. Nunes, <sup>49</sup> H. O'Keeffe, <sup>97</sup> M. Oberling, <sup>5</sup> A. Olivares Del Campo, <sup>46</sup> A. Olivier, <sup>139</sup> Y. Onel, <sup>81</sup> Y. Onishchuk, <sup>94</sup> T. Ovsjannikova, <sup>80</sup> S. Ozturk, <sup>20</sup> L. Pagani, <sup>23</sup> S. Pakvasa, <sup>63</sup> O. Palamara, <sup>54</sup> J. Paley, <sup>54</sup> M. Pallavicini, <sup>56</sup> C. Palomares,<sup>21</sup> J. Palomino,<sup>151</sup> E. Pantic,<sup>23</sup> A. Paolo,<sup>64</sup> V. Paolone,<sup>134</sup> V. Papadimitriou,<sup>54</sup> R. Papaleo,<sup>96</sup> S. Paramesvaran, <sup>14</sup> J. Park, <sup>167</sup> S. Parke, <sup>54</sup> Z. Parsa, <sup>15</sup> S. Pascoli, <sup>46</sup> J. Pasternak, <sup>77</sup> J. Pater, <sup>105</sup> L. Patrizii, <sup>74</sup> R. B. Patterson, <sup>26</sup> S. J. Patton, <sup>98</sup> T. Patzak, <sup>4</sup> A. Paudel, <sup>89</sup> B. Paulos, <sup>173</sup> L. Paulucci, <sup>52</sup> Z. Pavlovic, <sup>54</sup> G. Pawloski, <sup>112</sup> P. Payam, <sup>75</sup> D. Payne, <sup>99</sup> V. Pec, <sup>143</sup> S. J. M. Peeters, <sup>152</sup> E. Pennacchio, <sup>79</sup> A. Penzo, <sup>81</sup> G. N. Perdue, <sup>54</sup> O. l. G. Peres, <sup>49</sup> L. Periale, <sup>47</sup> K. Petridis, <sup>14</sup> G. Petrillo, <sup>140</sup> R. Petti, <sup>145</sup> P. Picchi, <sup>130</sup> L. Pickering, <sup>109</sup> F. Pietropaolo, <sup>128</sup> J. Pillow, <sup>170</sup> P. Plonski, <sup>169</sup> R. Plunkett, <sup>54</sup> R. Poling, <sup>112</sup> X. Pons, <sup>20</sup> N. Poonthottathil, <sup>82</sup>

```

M. Popovic, <sup>54</sup> R. Pordes, <sup>54</sup> S. Pordes, <sup>54</sup> M. Potekhin, <sup>15</sup> R. Potenza, <sup>28</sup> B. Potukuchi, <sup>84</sup> S. Poudel, <sup>64</sup> J. Pozimski, <sup>77</sup>

M. Pozzato, <sup>74</sup> T. Prakasj, <sup>98</sup> R. Preece, <sup>141</sup> O. Prokofiev, <sup>54</sup> N. Pruthi, <sup>129</sup> P. Przewlocki, <sup>116</sup> F. Psihas, <sup>78</sup> D. Pugnre, <sup>79</sup>

D. Pushka, <sup>54</sup> K. Qi, <sup>151</sup> X. Qian, <sup>15</sup> J. L. Raaf, <sup>54</sup> R. Raboanary, <sup>2</sup> V. Radeka, <sup>15</sup> J. Rademacker, <sup>14</sup> V. Radescu, <sup>20</sup>

B. Radics,<sup>47</sup> A. Radovic,<sup>172</sup> A. Rafique,<sup>89</sup> M. Rajaoalisoa,<sup>2</sup> I. Rakhno,<sup>54</sup> H. T. Rakotondramanana,<sup>2</sup>

L. Rakotondravohitra, Y. A. Ramachers, R. A. Rameika, M. A. Ramirez Delgado, U. Ramsey, 101

B. J. Ramson,<sup>54</sup> A. Rappoldi, <sup>130</sup> G. L. Raselli, <sup>130</sup> P. Ratoff, <sup>97</sup> S. Ravat, <sup>20</sup> O. Ravinez, <sup>114</sup> H. Razafinime, <sup>2</sup>

B. Rebel, <sup>54</sup> D. Redondo, <sup>21</sup> C. Regenfus, <sup>47</sup> M. Reggiani-Guzzo, <sup>49</sup> T. Rehak, <sup>44</sup> J. Reichenbacher, <sup>147</sup> D. Reitzner, <sup>54</sup>

M. H. Reno, <sup>81</sup> A. Renshaw, <sup>64</sup> S. Rescia, <sup>15</sup> F. Resnati, <sup>20</sup> A. Reynolds, <sup>125</sup> G. Riccobene, <sup>96</sup> L. C. J. Rice, <sup>113</sup>

K. Rielage, <sup>101</sup> K. Riesselmann, <sup>54</sup> Y. - A. Rigaut, <sup>47</sup> D. Rivera, <sup>132</sup> L. Rochester, <sup>140</sup> M. Roda, <sup>99</sup> P. Rodrigues, <sup>125</sup> M. J. Rodriguez Alonso, <sup>20</sup> B. Roe, <sup>108</sup> A. J. Roeth, <sup>45</sup> R. M. Roser, <sup>54</sup> M. Ross-Lonergan, <sup>46</sup> M. Rossella, <sup>130</sup> J. Rout, <sup>85</sup>

S. Roy, <sup>61</sup> A. Rubbia, <sup>47</sup> C. Rubbia, <sup>59</sup> R. Rucinski, <sup>54</sup> B. Russell, <sup>175</sup> J. Russell, <sup>140</sup> D. Ruterbories, <sup>139</sup> M. R. Vagins, <sup>90</sup>

R. Saakyan, <sup>100</sup> N. Sahu, <sup>72</sup> P. Sala, <sup>110</sup> G. Salukvadze, <sup>20</sup> N. Samios, <sup>15</sup> F. Sanchez, <sup>67</sup> M. C. Sanchez, <sup>82</sup> C. Sandoval, <sup>3</sup>

B. Sands, <sup>136</sup> S. U. Sankar, <sup>70</sup> S. Santana, <sup>137</sup> L. M. Santos, <sup>49</sup> G. Santucci, <sup>151</sup> N. Saoulidou, <sup>7</sup> P. Sapienza, <sup>96</sup> C. Sarasty, <sup>32</sup> I. Sarcevic, <sup>6</sup> G. Savage, <sup>54</sup> A. Scaramelli, <sup>130</sup> A. Scarpelli, <sup>4</sup> T. Schaffer, <sup>111</sup> H. Schellman, <sup>123</sup> P. Schlabach, <sup>54</sup> C. M. Schloesser, <sup>47</sup> D. W. Schmitz, <sup>30</sup> J. Schneps, <sup>161</sup> K. Scholberg, <sup>45</sup> A. Schukraft, <sup>54</sup> E. Segreto, <sup>49</sup>

S. Sehrawat, <sup>61</sup> J. Sensenig, <sup>132</sup> I. Seong, <sup>24</sup> J. A. Sepulveda-Quiroz, <sup>82</sup> A. Sergi, <sup>12</sup> F. Sergiampietri, <sup>151</sup> D. Sessumes, <sup>157</sup>

K. Sexton, <sup>15</sup> L. Sexton-Kennedy, <sup>54</sup> D. Sgalaberna, <sup>20</sup> M. H. Shaevitz, <sup>37</sup> S. Shafaq, <sup>85</sup> J. S. Shahi, <sup>129</sup> S. Shahsavarani, <sup>157</sup> P. Shanahan, <sup>54</sup> H. R. Sharma, <sup>84</sup> R. Sharma, <sup>15</sup> R. K. Sharma, <sup>138</sup> T. Shaw, <sup>54</sup> S. Shin, <sup>30</sup>

I. Shoemaker, <sup>146</sup> D. Shooltz, <sup>109</sup> R. Shrock, <sup>151</sup> N. Simos, <sup>15</sup> J. Sinclair, <sup>11</sup> G. Sinev, <sup>45</sup> V. Singh, <sup>9</sup> J. Singh, <sup>103</sup> J. Singh, <sup>103</sup> I. Singh, <sup>129</sup> J. Singh, <sup>129</sup> R. Sipos, <sup>20</sup> F. W. Sippach, <sup>37</sup> G. Sirri, <sup>74</sup> K. Siyeon, <sup>31</sup> D. Smargianaki, <sup>151</sup> A. Smith, <sup>27</sup> A. Smith, <sup>45</sup> E. Smith, <sup>78</sup> P. Smith, <sup>78</sup> J. Smolik, <sup>39</sup> M. Smy, <sup>24</sup> E. L. Snider, <sup>54</sup> P. Snopok, <sup>69</sup> J. Sobczyk, <sup>174</sup>

H. Sobel, <sup>24</sup> M. Soderberg, <sup>153</sup> C. J. Solano Salinas, <sup>114</sup> N. Solomey, <sup>171</sup> W. Sondheim, <sup>101</sup> M. Sorel, <sup>68</sup> J. A. Soto-Oton, <sup>21</sup>

A. Sousa, <sup>32</sup> K. Soustruznik, <sup>29</sup> F. Spagliardi, <sup>125</sup> M. Spanu, <sup>130</sup> J. Spitz, <sup>108</sup> N. J. C. Spooner, <sup>143</sup> R. Staley, <sup>12</sup>

M. Stancari, <sup>54</sup> L. Stanco, <sup>128</sup> A. Stefanik, <sup>54</sup> H. M. Steiner, <sup>98</sup> J. Stewart, <sup>15</sup> J. Stock, <sup>147</sup> F. Stocker, <sup>20</sup> S. Stoica, <sup>65</sup>

J. Stone, <sup>13</sup> J. Strait, <sup>54</sup> M. Strait, <sup>112</sup> T. Strauss, <sup>54</sup> S. Striganov, <sup>54</sup> A. Stuart, <sup>34</sup> G. Sullivan, <sup>106</sup> M. Sultana, <sup>139</sup>

Y. Sun, <sup>63</sup> A. Surdo, <sup>164</sup> V. Susic, <sup>10</sup> L. Suter, <sup>54</sup> C. M. Sutera, <sup>28</sup> R. Svoboda, <sup>23</sup> B. Szczerbinska, <sup>156</sup> A. M. Szelc, <sup>105</sup> S. Söldner-Rembold, <sup>105</sup> N. Tagg, <sup>124</sup> R. Talaga, <sup>5</sup> H. Tanaka, <sup>140</sup> B. Tapia Oregui, <sup>158</sup> S. Tariq, <sup>54</sup> E. Tatar, <sup>76</sup>

R. Tayloe, <sup>78</sup> M. Tenti, <sup>74</sup> K. Terao, <sup>140</sup> C. A. Ternes, <sup>68</sup> F. Terranova, <sup>73</sup> G. Testera, <sup>56</sup> A. Thea, <sup>141</sup> L. F. Thompson, <sup>143</sup>

J. Thompson, <sup>143</sup> C. Thorn, <sup>15</sup> A. Timilsina, <sup>15</sup> S. C. Timm, <sup>54</sup> J. Todd, <sup>32</sup> A. Tonazzo, <sup>4</sup> T. Tope, <sup>54</sup> D. Torbunov, <sup>112</sup>

M. Torti, <sup>73</sup> M. Tórtola, <sup>68</sup> F. Tortorici, <sup>28</sup> M. Toups, <sup>54</sup> C. Touramanis, <sup>99</sup> J. Trevor, <sup>26</sup> M. Tripathi, <sup>23</sup> W. Tromeur, <sup>79</sup>

I. Tropin, <sup>54</sup> W. H. Trzaska, <sup>86</sup> Y.-T. Tsai, <sup>140</sup> K. V. Tsang, <sup>140</sup> A. Tsaris, <sup>54</sup> S. Tufanli, <sup>175</sup> C. Tull, <sup>98</sup> J. Turner, <sup>46</sup> M. Tzanov, <sup>102</sup> E. Tziaferi, <sup>7</sup> Y. Uchida, <sup>77</sup> J. Urheim, <sup>78</sup> T. Usher, <sup>140</sup> G. A. Valdiviesso, <sup>50</sup> E. Valencia, <sup>172</sup> L. Valerio, <sup>54</sup>

Z. Vallari, <sup>151</sup> J. W. F. Valle, <sup>68</sup> R. Van Berg, <sup>132</sup> R. Van de Water, <sup>101</sup> F. Varanini, <sup>128</sup> G. Varner, <sup>63</sup> J. Vasel, <sup>78</sup>

G. Vasseur, <sup>19</sup> K. Vaziri, <sup>54</sup> G. Velev, <sup>54</sup> S. Ventura, <sup>128</sup> A. Verdugo, <sup>21</sup> M. Vermeulen, <sup>119</sup> E. Vernon, <sup>15</sup> M. Verzocchi, <sup>54</sup> T. Viant, <sup>47</sup> C. Vignoli, <sup>58</sup> S. Vihonen, <sup>86</sup> C. Vilela, <sup>151</sup> B. Viren, <sup>15</sup> P. Vokac, <sup>39</sup> T. Vrba, <sup>39</sup> T. Wachala, <sup>118</sup> D. Wahl, <sup>173</sup>

M. Wallbank, <sup>32</sup> H. Wang, <sup>25</sup> J. Wang, <sup>23</sup> T.-C. Wang, <sup>46</sup> B. Wang, <sup>150</sup> Y. Wang, <sup>151</sup> Z. Wang, <sup>159</sup> K. Warburton, <sup>82</sup>

D. Warner, <sup>36</sup> M. O. Wascko, <sup>77</sup> D. Waters, <sup>100</sup> A. Watson, <sup>12</sup> A. Weber, <sup>125</sup>, <sup>141</sup> M. Weber, <sup>11</sup> H. Wei, <sup>15</sup> W. Wei, <sup>146</sup> A. Weinstein, <sup>82</sup> D. Wenman, <sup>173</sup> M. Wetstein, <sup>82</sup> M. While, <sup>147</sup> A. White, <sup>157</sup> L. H. Whitehead, <sup>20</sup> D. Whittington, <sup>153</sup>

K. Wierman, <sup>126</sup> M. Wilking, <sup>151</sup> C. Wilkinson, <sup>11</sup> J. Willhite, <sup>54</sup> Z. Williams, <sup>157</sup> R. J. Wilson, <sup>36</sup> P. Wilson, <sup>54</sup> P. Wittich, <sup>38</sup> J. Wolcott, <sup>161</sup> T. Wongjirad, <sup>161</sup> K. Wood, <sup>151</sup> L. Wood, <sup>126</sup> E. Worcester, <sup>15</sup> M. Worcester, <sup>15</sup>

S. Wu, <sup>47</sup> W. Wu, <sup>54</sup> W. Xu, <sup>146</sup> C. Yanagisawa, <sup>151</sup> S. Yang, <sup>32</sup> T. Yang, <sup>54</sup> G. Yang, <sup>151</sup> J. Ye, <sup>150</sup> M. Yeh, <sup>15</sup>

N. Yershov, <sup>80</sup> K. Yonehara, <sup>54</sup> L. Yoshimura, <sup>163</sup> B. Yu, <sup>15</sup> J. Yu, <sup>157</sup> J. Zalesak, <sup>17</sup> L. Zambelli, <sup>95</sup> B. Zamorano, <sup>152</sup> A. Zani, <sup>20</sup> K. Zaremba, <sup>169</sup> L. Zazueta, <sup>172</sup> G. P. Zeller, <sup>54</sup> J. Zennamo, <sup>54</sup> C. Zhang, <sup>15</sup> C. Zhang, <sup>146</sup> M. Zhao, <sup>15</sup>

Y.-L. Zhou, <sup>46</sup> G. Zhu, <sup>122</sup> E. D. Zimmerman, <sup>35</sup> M. Zito, <sup>19</sup> S. Zucchelli, <sup>74</sup> J. Zuklin, <sup>17</sup> V. Zutshi, <sup>113</sup> and R. Zwaska <sup>54</sup>

(The DUNE Collaboration)

```

<sup>1</sup>Aligarh Muslim University, Department of Physics, Aligarh-202002, India

<sup>2</sup>University of Antananarivo, BP 566, Antananarivo 101, Madagascar

<sup>3</sup>Universidad Antonio Nariño, Cra 3 Este No 47A-15, Bogota, Colombia

<sup>4</sup>APC, AstroParticule et Cosmologie, Universit Paris Diderot, CNRS/IN2P3, CEA/lrfu, Observatoire de Paris, Sorbonne Paris Cit, 10, rue Alice Domon et Lonie Duquet, 75205 Paris Cedex 13, France

<sup>5</sup>Argonne National Laboratory, Argonne, IL 60439, USA

<sup>6</sup>University of Arizona, 1118 E. Fourth Street Tucson, AZ 85721, USA

<sup>7</sup>University of Athens, University Campus, Zografou GR 157 84, Greece

<sup>8</sup>Universidad del Atlantico, Carrera 30 Nmero 8- 49 Puerto Colombia - Atlntico, Colombia

<sup>9</sup>Banaras Hindu University, Department of Physics, Varanasi - 221 005, India

```

<sup>10</sup>University of Basel, Klingelbergstrasse 82, CH-4056 Basel, Switzerland

<sup>11</sup>University of Bern, Sidlerstrasse 5, CH-3012 Bern, Switzerland

<sup>12</sup>University of Birmingham, Edgbaston, Birmingham B15 2TT, United Kingdom

<sup>13</sup>Boston University, Boston, MA 02215, USA

<sup>14</sup> University of Bristol, H. H. Wills Physics Laboratory, Tyndall Avenue Bristol BS8 1TL, United Kingdom

<sup>15</sup> Brookhaven National Laboratory, Upton, NY 11973, USA

<sup>16</sup>University of Bucharest, Faculty of Physics, Bucharest, Romania

<sup>17</sup>Institute of Physics, Czech Academy of Sciences, Na Slovance 2, 182 21 Praha 8, Czech Republic

<sup>18</sup>Centro Brasileiro de Pesquisas Físicas, Rio de Janeiro, RJ 22290-180, Brazil

<sup>19</sup>CEA/Saclay, IRFU (Institut de Recherche sur les Lois Fondamentales de l'Univers), F-91191 Gif-sur-Yvette CEDEX, France

<sup>20</sup>CERN, European Organization for Nuclear Research 1211 Geneve 23, Switzerland, CERN

<sup>21</sup> CIEMAT, Centro de Investigaciones Energéticas, Medioambientales

y Tecnológicas, Av. Complutense, 40, E-28040 Madrid, Spain <sup>22</sup> University of California (Berkeley), Berkeley, CA 94720, USA

<sup>23</sup> University of California (Davis), Davis, CA 95616, USA

<sup>24</sup> University of California (Irvine), Irvine, CA 92697, USA

<sup>25</sup>University of California (Los Angeles), Los Angeles, CA 90095, USA

<sup>26</sup>California Institute of Technology, Pasadena, CA 91125, USA

<sup>27</sup>University of Cambridge, JJ Thomson Avenue, Cambridge CB3 0HE, United Kingdom

<sup>28</sup> University of Catania, INFN Sezione di Catania, Via Santa Sofia 64, I-95123 Catania, Italy

<sup>29</sup>Institute of Particle and Nuclear Physics of the Faculty of Mathematics and Physics of the

Charles University in Prague, V Holešovičkách 747/2, 180 00 Praha 8-Libeň, Czech Republic

<sup>30</sup> University of Chicago, Chicago, IL 60637, USA

<sup>31</sup>Chung-Ang University, Dongjak-Gu, Seoul 06974, South Korea

<sup>32</sup> University of Cincinnati, Cincinnati, OH 45221, USA

<sup>33</sup>Cinvestav, Apdo. Postal 14-740, 07000 Ciudad de Mexico, Mexico

<sup>34</sup> Universidad de Colima, 340 Colonia Villa San Sebastian Colima, Colima, Mexico

<sup>35</sup>University of Colorado (Boulder), Boulder, CO 80309, USA

<sup>36</sup>Colorado State University, Fort Collins, CO 80523, USA

<sup>37</sup>Columbia University, New York, NY 10027, USA

<sup>38</sup>Cornell University, Ithaca, NY 14853, USA

<sup>39</sup>Czech Technical University in Prague, Břehová 78/7, 115 19 Prague 1, Czech Republic

<sup>40</sup>Dakota State University, Madison, SD 57042, USA

<sup>41</sup>University of Dallas, Irving, TX 75062-4736, USA

<sup>42</sup>Daresbury Laboratory, Daresbury Warrington, Cheshire WA4 4AD, United Kingdom

<sup>43</sup>University of Delhi. Department of Physics and Astrophysics, Delhi 110007, India

<sup>44</sup>Drexel University, Philadelphia, PA 19104, USA

<sup>45</sup>Duke University, Durham, NC 27708, USA

<sup>46</sup>University of Durham, South Road, Durham DH1 3LE, United Kingdom

<sup>47</sup>ETH Zurich, Institute for Particle Physics, Zurich, Switzerland

<sup>48</sup> University of Edinburgh, Edinburgh EH8 9YL, UK, United Kingdom

<sup>49</sup>Universidade Estadual de Campinas, Campinas - SP, 13083-970, Brazil

<sup>50</sup>Universidade Federal de Alfenas, Poços de Caldas - MG, 37715-400, Brazil

<sup>51</sup>Universidade Federal do Rio de Janeiro, Rio de Janeiro - RJ, 21941-901, Brazil

<sup>52</sup>Universidade Federal do ABC, Santo André, SP 09210-580, Brazil

<sup>53</sup>UEFS/DFIS - State University of Feira de Santana, Feira de Santana - BA, 44036-900, Brazil

<sup>54</sup>Fermi National Accelerator Laboratory, Batavia, IL 60510, USA

<sup>55</sup>University of Florida, PO Box 118440 Gainesville, FL 32611-8440, USA

<sup>6</sup>University of Genova, 16126 Genova GE, Italy

<sup>57</sup>Universidade Federal de Goias, Goiania, GO 74690-900, Brazil

<sup>58</sup>Laboratori Nazionali del Gran Sasso, I-67010 Assergi, AQ, Italy

<sup>59</sup>Gran Sasso Science Institute, Viale Francesco Crispi 7, L'Aquila, Italy

<sup>60</sup>Universidad de Guanajuato, Gto., C.P. 37000, Mexico

<sup>61</sup>Harish-Chandra Research Institute, Jhunsi, Allahabad 211 019, India

<sup>62</sup>Harvard University, 17 Oxford St. Cambridge, MA 02138, USA

<sup>63</sup>University of Hawaii, Honolulu, HI 96822, USA

<sup>64</sup> University of Houston, Houston, TX 77204, USA

<sup>65</sup>Horia Hulubei National Institute of Physiscs and Nuclear Engineering, Strada Reactorului 30, Măgurele, Romania

<sup>66</sup>University of Hyderabad, Gachibowli, Hyderabad - 500 046, India

<sup>67</sup>Institut de Fisica d'Altes Energies (IFAE), Campus UAB, Facultat Ciences Nord, 08193 Bellaterra, Barcelona, Spain

<sup>68</sup>Instituto de Fisica Corpuscular, Catedratico Jose Beltran, 2 E-46980 Paterna (Valencia), Spain

<sup>69</sup>Illinois Institute of Technology, Chicago, IL 60616, USA

<sup>70</sup>Indian Institute of Technology Bombay, Department of Physics Mumbai 400 076, India

<sup>1</sup>Indian Institute of Technology Guwahati, Guwahati, 781 039, India

```

```

<sup>72</sup>Indian Institute of Technology Hyderabad, Hyderabad, 502285, India

<sup>73</sup>Sezione INFN Milano Bicocca and University of Milano Bicocca, Milano, Italy

<sup>74</sup>INFN Universit degli Studi di Bologna, 40127 Bologna BO, Italy

<sup>75</sup>Institute for Research in Fundamental Sciences (IPM), Farmanieh St. Tehran, 19538-33511, Iran

<sup>76</sup>Idaho State University, Department of Physics, Pocatello, ID 83209, USA

<sup>77</sup>Imperial College of Science Technology & Medicine, Blackett

Laboratory Prince Consort Road, London SW7 2BZ, United Kingdom

78 Indiana University, Bloomington, IN 47405, USA

79 Institut de Physique Nucleaire de Lyon (IPNL), Rue E. Fermi 4 69622 Villeurbanne, France

<sup>80</sup>Institute for Nuclear Research of the Russian Academy of Sciences (INR

RAS), 60th October Anniversary Prosp. 7a Moscow, 117312, Russia

<sup>81</sup>University of Iowa, Department of Physics and Astronomy 203 Van Allen Hall Iowa City, IA 52242, USA

82 Iowa State University, Ames, Iowa 50011, USA

<sup>83</sup>Iwate University, Morioka, Iwate 020-8551, Japan

<sup>84</sup> University of Jammu, Physics Department, JAMMU-180006, India

<sup>85</sup> Jawaharlal Nehru University, Jawaharlal Nehru University, New Delhi 110067, India

<sup>86</sup>University of Jyvaskyla, P.O. Box 35, FI-40014, Finland

<sup>87</sup>High Energy Accelerator Research Organization (KEK), Ibaraki, 305-0801, Japan

<sup>88</sup>KTH Royal Institute of Technology, Roslagstullsbacken 21, SE-106 91 Stockholm, Sweden

<sup>89</sup>Kansas State University, Manhattan, KS 66506, USA

<sup>90</sup>Kavli Institute for the Physics and Mathematics of the Universe (WPI), Kashiwa, Chiba 277-8583, Japan

<sup>91</sup>Department of Physics, K L E F, Green Fields, Guntur - 522 502, AP, India

<sup>92</sup>Korea Institute for Science and Technology Information, Daejeon, 34141, South Korea

<sup>93</sup>National Institute of Technology, Kure College, Hiroshima, 737-8506, Japan

<sup>94</sup>Kyiv National University, 64, 01601 Kyiv, Ukraine

<sup>95</sup>Laboratoire d'Annecy-le-Vieux de Physique des Particules, CNRS/IN2P3

and Université Savoie Mont Blanc, 74941 Annecy-le-Vieux, France

96 INFN - Laboratori Nazionali del Sud (LNS), Via S. Sofia 62, 95123 Catania, Italy

<sup>97</sup>Lancaster University, Bailrigg, Lancaster LA1 4YB, United Kingdom

<sup>98</sup>Lawrence Berkeley National Laboratory, Berkeley, CA 94720, USA

<sup>99</sup>University of Liverpool, L69 7ZE, Liverpool, United Kingdom

<sup>100</sup>University College London, London, WC1E 6BT, United Kingdom

<sup>101</sup>Los Alamos National Laboratory, Los Alamos, NM 87545, USA

<sup>102</sup>Louisiana State University, Baton Rouge, LA 70803, USA

<sup>103</sup>University of Lucknow, Lucknow 226007, Uttar Pradesh, India

<sup>104</sup>Madrid Autonoma University. Ciudad Universitaria de Cantoblanco 28049 Madrid, Spain

<sup>105</sup>University of Manchester, Oxford Road, Manchester M13 9PL, United Kingdom

<sup>106</sup>University of Maryland, College Park, MD 20742, USA

<sup>107</sup>Massachusetts Institute of Technology, Cambridge, MA 02139, USA

<sup>108</sup>University of Michigan, Ann Arbor, MI 48109, USA

<sup>109</sup>Michigan State University, East Lansing, MI 48824, USA

<sup>110</sup>INFN Milano, INFN Sezione di Milano, I-20133 Milano, Italy

<sup>111</sup>University of Minnesota (Duluth), Duluth, MN 55812, USA

<sup>112</sup>University of Minnesota (Twin Cities), Minneapolis, MN 55455, USA

<sup>113</sup>Northern Illinois University, Department of Physics, DeKalb, Illinois 60115, USA

<sup>114</sup>Universidad Nacional de Ingeniería, Av. Tupac Amaru 210, Lima 25, Peru

<sup>115</sup>Istituto Nazionale di Fisica Nucleare - Sezione di Napoli, Complesso Universitario di Monte S. Angelo, I-80126 Napoli, Italy

<sup>116</sup>National Centre for Nuclear Research, A. Soltana 7, 05 400 Otwock, Poland

<sup>117</sup>University of New Mexico, 1919 Lomas Blvd. N.E. Albuquerque, NM 87131, USA

<sup>118</sup>H. Niewodniczanski Institute of Nuclear Physics, Polish Academy of Sciences, Cracow, Poland

<sup>119</sup>Nikhef National Institute of Subatomic Physics, Science Park, Amsterdam, Netherlands

<sup>120</sup>Northwestern University, Evanston, Il 60208, USA

<sup>121</sup>University of Notre Dame, Notre Dame, IN 46556, USA

<sup>122</sup>Ohio State University, 191 W. Woodruff Ave. Columbus, OH 43210, USA

<sup>123</sup>Oregon State University, Corvallis, OR 97331, USA

<sup>124</sup>Otterbein University, One South Grove Street Westerville, OH 43081, USA

<sup>125</sup>University of Oxford, Oxford, OX1 3RH, United Kingdom

<sup>126</sup>Pacific Northwest National Laboratory, Richland, WA 99352, USA

<sup>127</sup>Physical Research Laboratory, Ahmedabad 380 009, India

<sup>128</sup> University of Padova, Dip. Fisica e Astronomia G. Galilei and INFN Sezione di Padova, I-35131 Padova, Italy

<sup>129</sup>Panjab University, Chandigarh, 160014 U.T., India

<sup>130</sup>University of Pavia, INFN Sezione di Pavia, I-27100 Pavia, Italy

<sup>131</sup>Pennsylvania State University, University Park, PA 16802, USA

<sup>132</sup>University of Pennsylvania, Philadelphia, PA 19104, USA

```

```

<sup>133</sup> University di Pisa, Theor. Division; Largo B. Pontecorvo 3, Ed. B-C, I-56127 Pisa, Italy

<sup>134</sup> University of Pittsburgh, Pittsburgh, PA 15260, USA

<sup>135</sup>Pontificia Universidad Católica del Perú, Apartado 1761, Lima, Peru

<sup>136</sup>Princeton University, Princeton, New Jersey 08544, USA

<sup>137</sup>University of Puerto Rico, Mayaguez, 00681, USA

<sup>138</sup>Punjab Agricultural University, Department of Math. Stat. & Physics, Ludhiana 141004, India

<sup>139</sup>University of Rochester, Rochester, NY 14627, USA

<sup>140</sup>SLAC National Acceleratory Laboratory, Menlo Park, CA 94025, USA

<sup>141</sup>STFC Rutherford Appleton Laboratory, OX11 0QX Harwell Campus, Didcot, United Kingdom

<sup>142</sup> University Sergio Arboleda, Cll 74 -14 -14, 11022 Bogotá, Colombia

<sup>143</sup>University of Sheffield, Department of Physics and Astronomy, Sheffield S3 7RH, United Kingdom

<sup>144</sup>University of Sofia, 5 James Bourchier Blvd., Sofia, Bulgaria

<sup>145</sup>University of South Carolina, Columbia, SC 29208, USA

<sup>146</sup>University of South Dakota, Vermillion, SD 57069, USA

<sup>147</sup>South Dakota School of Mines and Technology, Rapid City, SD 57701, USA

<sup>148</sup>South Dakota Science And Technology Authority, Lead, SD 57754, USA

<sup>149</sup>South Dakota State University, Brookings, SD 57007, USA

<sup>150</sup>Southern Methodist University, Dallas, TX 75275, USA

<sup>151</sup>Stony Brook University, Stony Brook, New York 11794, USA

<sup>152</sup>University of Sussex, Brighton, BN1 9RH, United Kingdom

<sup>153</sup>Syracuse University, Syracuse, NY 13244, USA

<sup>154</sup>Universidad Tecnica Federico Santa Maria, Department de Fisica, Casino 110-V, Valparaiso, Chile

<sup>155</sup>University of Tennessee at Knoxville, TN, 37996, USA

<sup>156</sup>Texas A&M University (Corpus Christi), Corpus Christi, TX 78412, USA

<sup>157</sup>University of Texas (Arlington), Arlington, TX 76019, USA

<sup>158</sup> University of Texas (Austin), Austin, TX 78712, USA

<sup>159</sup>Tsinghua University, Haidian District, Beijing 100084, China

<sup>160</sup>TUBITAK Space Technologies Research Institute, TR-06800, Ankara, Turkey

<sup>161</sup> Tufts University, Medford, MA 02155, USA

<sup>162</sup>Universidade Federal de São Carlos, Araras - SP, 13604-900, Brazil

<sup>163</sup>Universidade Nacional de Asuncion, 585540/2 Interno 1068 CC: 910, Asunción, Paraguay

<sup>164</sup> Università del Salento - INFN, Via Provinciale per Arnesano, 73100 - Lecce , Italy

<sup>165</sup> Variable Energy Cyclotron Centre, 1/AF, Bidhannagar Kolkata - 700 064 West Bengal, India

<sup>66</sup> Valley City State University, Valley City, ND 58072, USA

<sup>167</sup> Virginia Tech, Blacksburg, VA 24060, USA

<sup>168</sup> University of Warsaw, Faculty of Physics ul. Pasteura 5 02-093 Warsaw, Poland

<sup>169</sup>Warsaw University of Technology, Nowowiejska 15/19, 00-665 Warszawa Poland, Poland

<sup>170</sup>University of Warwick, Coventry CV4 7AL, United Kingdom

<sup>171</sup>Wichita State University, Physics Division, Wichita, KS 67260, USA

<sup>172</sup>William and Mary, Williamsburg, VA 23187, USA

<sup>173</sup>University of Wisconsin (Madison), Madison, WI 53706, USA

<sup>174</sup>Wroclaw University, Plac Maxa Borna 9, 50-204 Wroclaw, Poland

<sup>175</sup>Yale University, New Haven, CT 06520, USA

<sup>176</sup> Yerevan Institute for Theoretical Physics and Modeling, Halabian Str. 34, Yerevan 0036, Armenia

<sup>177</sup>York University, Physics and Astronomy Department, 4700 Keele St. Toronto M3J 1P3, Canada

```

# **Contents**

| Cc  | Contents            |          |                                                    |    |  |

|-----|---------------------|----------|----------------------------------------------------|----|--|

| Lis | List of Figures vii |          |                                                    |    |  |

| Lis | st of               | Tables   |                                                    | X  |  |

| 1   | Desi                | _        | tivation and Overview                              | 2  |  |

|     | 1.1                 | Introdu  | ction to the DUNE Single-Phase Far Detector Design | 2  |  |

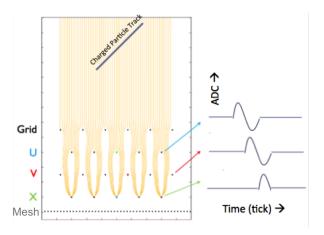

|     | 1.2                 | Single-  | Phase LArTPC Operational Principle                 | 2  |  |

|     | 1.3                 | Motiva   | tion of Single-Phase LArTPC Design at DUNE         | 3  |  |

|     | 1.4                 | Overvie  | ew of the Single-Phase Design                      | 4  |  |

|     | 1.5                 | Detecto  | or Systems                                         | 4  |  |

|     |                     | 1.5.1    | Anode Plane Assemblies                             | 6  |  |

|     |                     | 1.5.2    | TPC Electronics                                    | 6  |  |

|     |                     | 1.5.3    | CPA, Field Cage and High Voltage                   | 6  |  |

|     |                     | 1.5.4    | Photon Detection                                   | 6  |  |

|     |                     | 1.5.5    | Data Acquisition                                   | 7  |  |

|     |                     | 1.5.6    | Cryogenic Instrumentation and Slow Controls        | 7  |  |

|     | 1.6                 | Technic  | cal Coordination                                   | 7  |  |

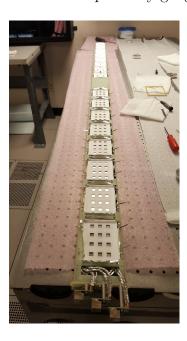

| 2   | Ano                 |          | ne Assemblies                                      | 8  |  |

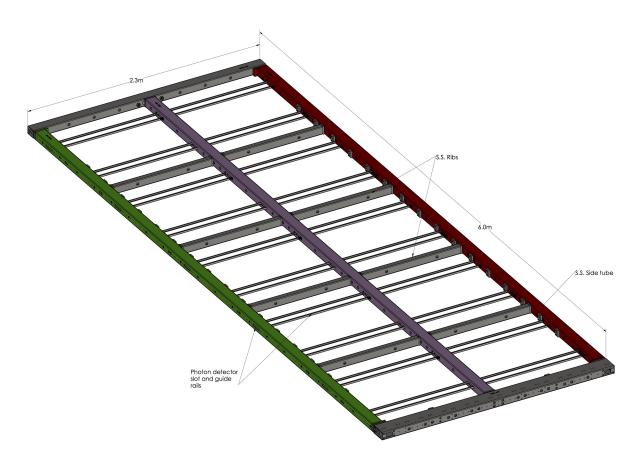

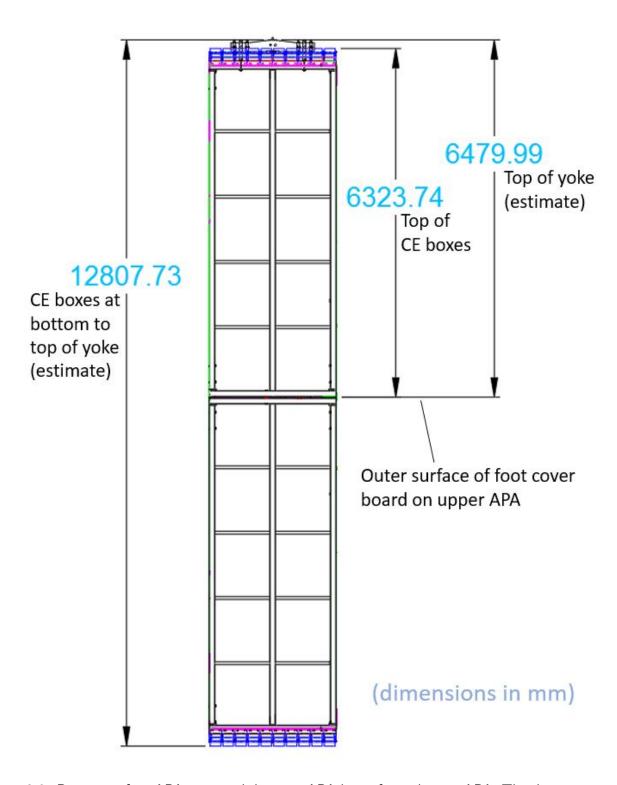

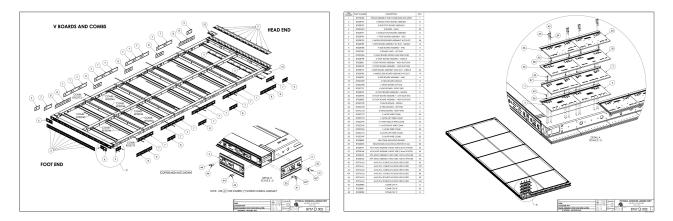

|     | 2.1                 | Anode    | Plane Assembly (APA) Overview                      | 8  |  |

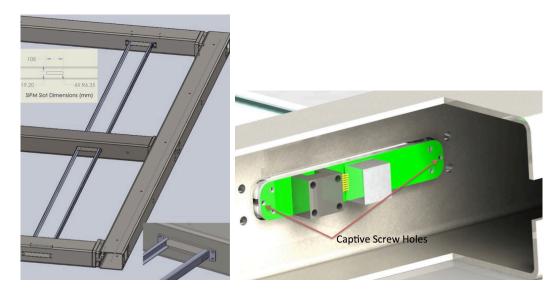

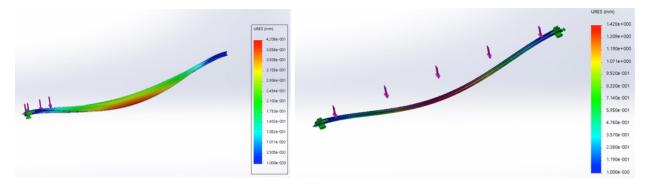

|     | 2.2                 | Design   |                                                    | 11 |  |

|     |                     | 2.2.1    | APA Overview and Key Design Parameters             | 11 |  |

|     |                     | 2.2.2    | APA Frames                                         | 14 |  |

|     |                     | 2.2.3    | Grounding Mesh                                     | 16 |  |

|     |                     | 2.2.4    | Wires                                              | 19 |  |

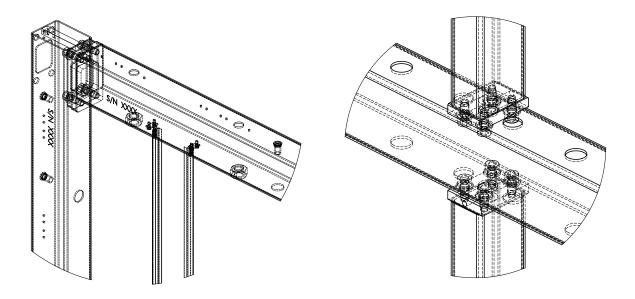

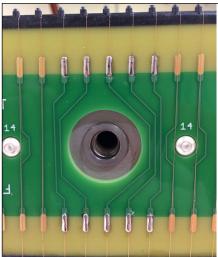

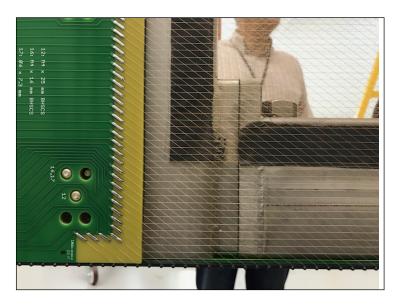

|     |                     | 2.2.5    | Wire Boards and Anchoring Elements                 | 19 |  |

|     | 2.3                 | Interfac | ces                                                | 24 |  |

|     |                     | 2.3.1    | TPC Cold Electronics                               | 24 |  |

|     |                     | 2.3.2    | Photon Detection System                            | 25 |  |

|     |                     | 2.3.3    | APA-to-APA Connections and Cable Routing           | 26 |  |

|     | 2.4                 | Produc   | tion and Assembly                                  | 26 |  |

|     |                     | 2.4.1    | Facility Plans                                     |    |  |

|     |                     | 2.4.2    | Assembly Procedures and Tooling                    |    |  |

|     |                     | 2.4.3    | Material Supply                                    |    |  |

|   |      | 2.4.4    | Planned Improvements to Production Process                            | 32  |

|---|------|----------|-----------------------------------------------------------------------|-----|

|   |      | 2.4.5    | Quality Assurance and Quality Control in APA Production               | 34  |

|   | 2.5  | Integra  | ation and Installation                                                | 36  |

|   |      | 2.5.1    | Transport and Handling                                                | 36  |

|   |      | 2.5.2    | APA-to-CPA Assembly and Installation in the Cryostat                  | 37  |

|   |      | 2.5.3    | Quality Assurance and Quality Control in Integration and Installation | 37  |

|   | 2.6  | Safety   |                                                                       | 41  |

|   | 2.7  | Organi   | zation and Management                                                 | 41  |

|   |      | 2.7.1    | APA Consortium Organization                                           |     |

|   |      | 2.7.2    | Planning Assumptions                                                  | 42  |

|   |      | 2.7.3    | WBS and Responsibilities                                              |     |

|   |      | 2.7.4    | High-level Milestones and Schedule                                    |     |

|   |      |          |                                                                       |     |

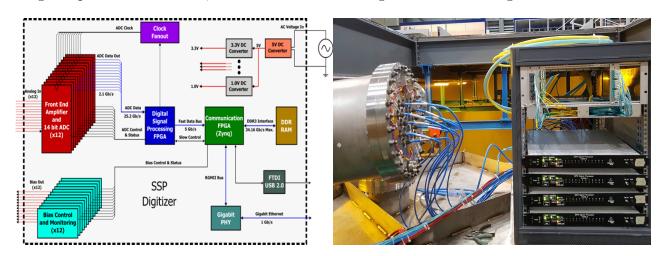

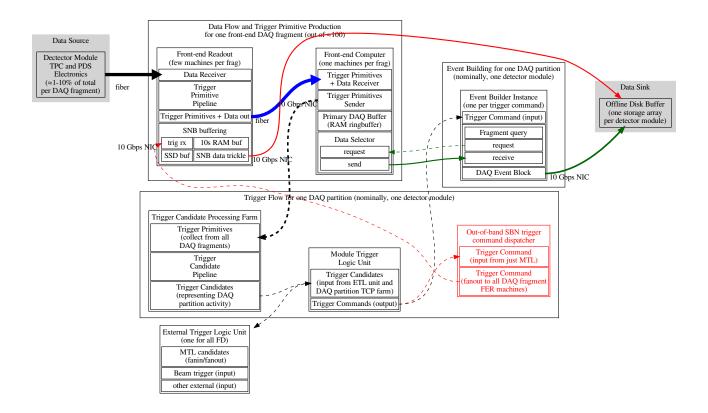

| 3 | TPC  | C Electi | ronics                                                                | 44  |

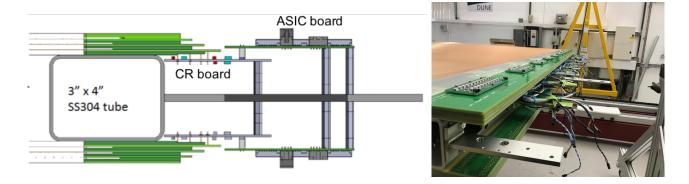

|   | 3.1  | TPC E    | Electronics (CE) System Overview                                      | 44  |

|   |      | 3.1.1    | Introduction                                                          | 44  |

|   |      | 3.1.2    | System Description, Scope and Current Status                          | 45  |

|   |      | 3.1.3    | System Requirements                                                   | 48  |

|   | 3.2  | System   | n Design                                                              | 49  |

|   |      | 3.2.1    | Grounding and Shielding                                               | 49  |

|   |      | 3.2.2    | Connections from Wire to Front-End                                    | 50  |

|   |      | 3.2.3    | Front-End Mother Board (FEMB)                                         | 51  |

|   |      | 3.2.4    | Additional FEMB/ASIC Designs                                          | 58  |

|   |      | 3.2.5    | Cold Electronics Feedthroughs and Cold Cables                         |     |

|   |      | 3.2.6    | Warm Interface Electronics                                            | 63  |

|   |      | 3.2.7    | External Power and Supplies                                           | 65  |

|   | 3.3  | Produc   | ction and Assembly                                                    |     |

|   | 3.4  |          | ces                                                                   |     |

|   |      | 3.4.1    | Overview                                                              | 68  |

|   |      | 3.4.2    | APAs                                                                  |     |

|   |      | 3.4.3    | DAQ                                                                   | 69  |

|   | 3.5  | Quality  | y Assurance                                                           |     |

|   |      | 3.5.1    | Initial Design Validation                                             |     |

|   |      | 3.5.2    | Integrated Test Facilities                                            | 71  |

|   | 3.6  | Quality  | y Control                                                             |     |

|   | 3.7  | •        | ation, Integration, and Commissioning                                 |     |

|   |      | 3.7.1    | Installation and Integration with APAs                                |     |

|   |      | 3.7.2    | Commissioning and Calibration                                         |     |

|   | 3.8  | Safety   | <u> </u>                                                              |     |

|   | 3.9  | ,        | ization and Management                                                |     |

|   |      | 3.9.1    | Single-Phase TPC Electronics Consortium Organization                  |     |

|   |      | 3.9.2    | Planning Assumptions                                                  |     |

|   |      | 3.9.3    | WBS and Responsibilities                                              |     |

|   |      | 3.9.4    | Timeline and Key Milestones                                           |     |

|   |      |          |                                                                       | . • |

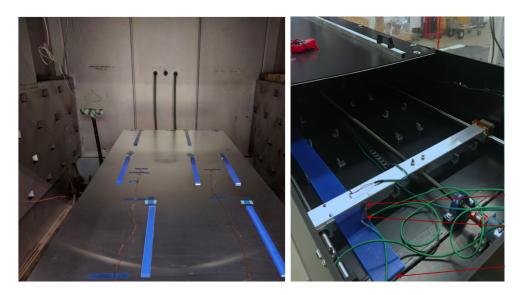

| 4 | High | ı Volta  | ge System                                                             | 86  |

|   | 4.1  | High V   | Oltage System Overview                                                | 86  |

|   |                                               | 4.1.1 I                                                                                                                                                          | ntroduction                                                                                                                                                                                               | 86                                                                                                    |

|---|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|   |                                               | 4.1.2                                                                                                                                                            | Design Requirements                                                                                                                                                                                       | 88                                                                                                    |

|   |                                               | 4.1.3                                                                                                                                                            | cope                                                                                                                                                                                                      | 91                                                                                                    |

|   | 4.2                                           | HV Syste                                                                                                                                                         | em Design                                                                                                                                                                                                 | 92                                                                                                    |

|   |                                               | 4.2.1 H                                                                                                                                                          | ligh Voltage Power Supply and Feedthrough                                                                                                                                                                 | 92                                                                                                    |

|   |                                               |                                                                                                                                                                  | Cathode Plane Assembly (CPA)                                                                                                                                                                              |                                                                                                       |

|   |                                               |                                                                                                                                                                  | ield Cages                                                                                                                                                                                                |                                                                                                       |

|   |                                               |                                                                                                                                                                  | Electrical Interconnections                                                                                                                                                                               |                                                                                                       |

|   | 4.3                                           |                                                                                                                                                                  | on and Assembly $\ldots\ldots\ldots\ldots$                                                                                                                                                                |                                                                                                       |

|   |                                               |                                                                                                                                                                  | Power Supplies and Feedthroughs                                                                                                                                                                           |                                                                                                       |

|   |                                               |                                                                                                                                                                  | Cathode Plane Assemblies                                                                                                                                                                                  |                                                                                                       |

|   |                                               |                                                                                                                                                                  | ield Cages                                                                                                                                                                                                |                                                                                                       |

|   |                                               |                                                                                                                                                                  | Electrical Interconnections                                                                                                                                                                               |                                                                                                       |

|   | 4.4                                           | Installati                                                                                                                                                       | on, Integration and Commissioning $\ldots\ldots\ldots\ldots\ldots$                                                                                                                                        | .11                                                                                                   |

|   |                                               |                                                                                                                                                                  | -ransport and Handling $\dots\dots\dots\dots$ 1                                                                                                                                                           |                                                                                                       |

|   |                                               |                                                                                                                                                                  | nstallation and Integration $\dots\dots\dots\dots\dots$                                                                                                                                                   |                                                                                                       |

|   |                                               |                                                                                                                                                                  | nterfaces                                                                                                                                                                                                 |                                                                                                       |

|   | 4.5                                           |                                                                                                                                                                  | Control (QC)                                                                                                                                                                                              |                                                                                                       |

|   | 4.6                                           | •                                                                                                                                                                |                                                                                                                                                                                                           |                                                                                                       |

|   | 4.7                                           | •                                                                                                                                                                | tion and Management                                                                                                                                                                                       |                                                                                                       |

|   |                                               | _                                                                                                                                                                | IV System Consortium Organization                                                                                                                                                                         |                                                                                                       |

|   |                                               |                                                                                                                                                                  | Planning Assumptions                                                                                                                                                                                      |                                                                                                       |

|   |                                               |                                                                                                                                                                  | ligh-level Cost and Schedule                                                                                                                                                                              |                                                                                                       |

|   |                                               |                                                                                                                                                                  | 8                                                                                                                                                                                                         |                                                                                                       |

|   |                                               |                                                                                                                                                                  |                                                                                                                                                                                                           |                                                                                                       |

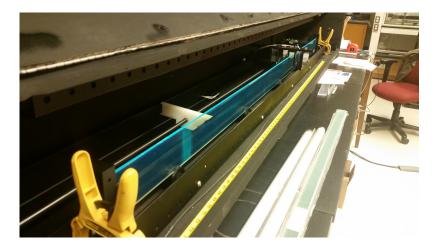

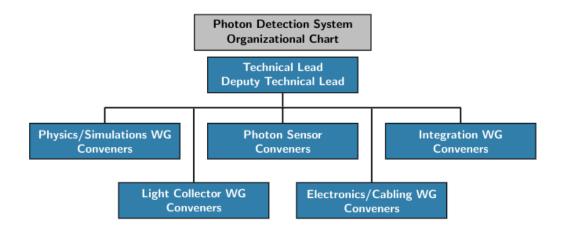

| 5 | Pho                                           |                                                                                                                                                                  |                                                                                                                                                                                                           | 20                                                                                                    |

| 5 | <b>Pho</b> 5.1                                | Photon I                                                                                                                                                         | Detection System (PDS) Overview                                                                                                                                                                           | .20                                                                                                   |

| 5 |                                               | Photon I<br>5.1.1 I                                                                                                                                              | Detection System (PDS) Overview                                                                                                                                                                           | .20<br>.20                                                                                            |

| 5 |                                               | Photon I 5.1.1 I 5.1.2                                                                                                                                           | Detection System (PDS) Overview       1         ntroduction       1         Design Considerations       1                                                                                                 | .20<br>.20<br>.21                                                                                     |

| 5 | 5.1                                           | Photon I 5.1.1 I 5.1.2 I 5.1.3 I                                                                                                                                 | Detection System (PDS) Overview       1         Introduction       1         Design Considerations       1         Development and Evaluation Plans       1                                               | .20<br>.20<br>.21<br>.27                                                                              |

| 5 | <ul><li>5.1</li><li>5.2</li></ul>             | Photon I<br>5.1.1 I<br>5.1.2 I<br>5.1.3 I<br>Photon I                                                                                                            | Detection System (PDS) Overview       1         ntroduction       1         Design Considerations       1         Development and Evaluation Plans       1         Detector Efficiency Simulation       1 | .20<br>.20<br>.21<br>.27                                                                              |

| 5 | 5.1                                           | Photon I<br>5.1.1 I<br>5.1.2 I<br>5.1.3 I<br>Photon I<br>Photon I                                                                                                | Detection System (PDS) Overview                                                                                                                                                                           | .20<br>.20<br>.21<br>.27<br>.28                                                                       |

| 5 | <ul><li>5.1</li><li>5.2</li></ul>             | Photon I<br>5.1.1 I<br>5.1.2 I<br>5.1.3 I<br>Photon I<br>Photon I<br>5.3.1 F                                                                                     | Detection System (PDS) Overview                                                                                                                                                                           | .20<br>.20<br>.21<br>.27<br>.28<br>.31                                                                |

| 5 | <ul><li>5.1</li><li>5.2</li></ul>             | Photon I<br>5.1.1 I<br>5.1.2 I<br>5.1.3 I<br>Photon I<br>Photon I<br>5.3.1 F<br>5.3.2 F                                                                          | Detection System (PDS) Overview                                                                                                                                                                           | .20<br>.21<br>.27<br>.28<br>.31<br>.31                                                                |

| 5 | <ul><li>5.1</li><li>5.2</li></ul>             | Photon I 5.1.1 I 5.1.2 I 5.1.3 I Photon I 5.3.1 F 5.3.2 F 5.3.3 F                                                                                                | Detection System (PDS) Overview                                                                                                                                                                           | .20<br>.20<br>.21<br>.27<br>.28<br>.31<br>.31<br>.37                                                  |

| 5 | <ul><li>5.1</li><li>5.2</li></ul>             | Photon I 5.1.1 I 5.1.2 E 5.1.3 E Photon I 5.3.1 F 5.3.2 F 5.3.3 F 5.3.4                                                                                          | Detection System (PDS) Overview                                                                                                                                                                           | .20<br>.20<br>.21<br>.27<br>.28<br>.31<br>.31<br>.37                                                  |

| 5 | <ul><li>5.1</li><li>5.2</li></ul>             | Photon I 5.1.1 I 5.1.2 E 5.1.3 E Photon I 5.3.1 F 5.3.2 F 5.3.3 F 5.3.4 F 5.3.5 S 5.3.5                                                                          | Detection System (PDS) Overview                                                                                                                                                                           | .20<br>.20<br>.21<br>.27<br>.28<br>.31<br>.31<br>.37<br>.38<br>.39                                    |

| 5 | <ul><li>5.1</li><li>5.2</li></ul>             | Photon I 5.1.1 I 5.1.2 E 5.1.3 E Photon I 5.3.1 F 5.3.2 F 5.3.3 F 5.3.4 F 5.3.5 S 5.3.5                                                                          | Detection System (PDS) Overview                                                                                                                                                                           | .20<br>.20<br>.21<br>.27<br>.28<br>.31<br>.31<br>.37<br>.38<br>.39                                    |

| 5 | <ul><li>5.1</li><li>5.2</li></ul>             | Photon I 5.1.1 I 5.1.2 E 5.1.3 E Photon I 5.3.1 F 5.3.2 F 5.3.3 F 5.3.4 F 5.3.5 E Producti                                                                       | Detection System (PDS) Overview                                                                                                                                                                           | .20<br>.20<br>.21<br>.27<br>.28<br>.31<br>.31<br>.37<br>.38<br>.39<br>.40                             |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Photon I 5.1.1 I 5.1.2 E 5.1.3 E Photon I 5.3.1 F 5.3.2 F 5.3.3 F 5.3.4 A 5.3.5 S 5.3.6 E Producti 5.4.1 F                                                       | Detection System (PDS) Overview                                                                                                                                                                           | .20<br>.20<br>.21<br>.27<br>.28<br>.31<br>.37<br>.38<br>.39<br>.40<br>.44<br>.47                      |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Photon I 5.1.1 I 5.1.2 E 5.1.3 E Photon I 5.3.1 F 5.3.2 F 5.3.3 F 5.3.4 A 5.3.5 S 5.3.6 E Producti 5.4.1 F                                                       | Detection System (PDS) Overview                                                                                                                                                                           | .20<br>.20<br>.21<br>.27<br>.28<br>.31<br>.37<br>.38<br>.39<br>.40<br>.44<br>.47                      |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Photon I 5.1.1 I 5.1.2 E 5.1.3 E Photon I F.3.1 F 5.3.2 F 5.3.3 F 5.3.4 E 5.3.5 S 5.3.6 E Producti 5.4.1 F 5.4.2 F                                               | Detection System (PDS) Overview                                                                                                                                                                           | .20<br>.20<br>.21<br>.27<br>.28<br>.31<br>.37<br>.38<br>.39<br>.40<br>.44<br>.47                      |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Photon I 5.1.1 I 5.1.2 E 5.1.3 E Photon I 5.3.1 F 5.3.2 F 5.3.3 F 5.3.4 A 5.3.5 S 5.3.6 E Producti 5.4.1 F 5.4.2 F 5.4.3 I                                       | Detection System (PDS) Overview                                                                                                                                                                           | .20<br>.20<br>.21<br>.27<br>.28<br>.31<br>.37<br>.38<br>.39<br>.40<br>.44<br>.47<br>.47               |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Photon I 5.1.1 I 5.1.2 I 5.1.3 I Photon I 5.3.1 F 5.3.2 F 5.3.3 F 5.3.4 A 5.3.5 S 5.3.6 E Producti 5.4.1 F 5.4.2 F 5.4.3 I 5.4.4 A 5.4.4                         | Detection System (PDS) Overview Introduction                                                                                                                                                              | .20<br>.20<br>.21<br>.27<br>.28<br>.31<br>.37<br>.38<br>.39<br>.40<br>.47<br>.47<br>.51<br>.52        |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Photon I 5.1.1 I 5.1.2 I 5.1.3 I Photon I 5.3.1 F 5.3.2 F 5.3.3 F 5.3.4 F 5.3.5 S 5.3.6 E Producti 5.4.1 F 5.4.2 F 5.4.2 F 5.4.3 I 5.4.4 F 5.4.5 C               | Detection System (PDS) Overview Introduction                                                                                                                                                              | .20<br>.20<br>.21<br>.27<br>.28<br>.31<br>.37<br>.38<br>.40<br>.47<br>.47<br>.51<br>.52               |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Photon I 5.1.1 I 5.1.2 I 5.1.3 I Photon I 5.3.1 F 5.3.2 F 5.3.3 F 5.3.4 F 5.3.5 S 5.3.6 E Producti 5.4.1 F 5.4.2 F 5.4.3 I 5.4.4 F 5.4.5 G 5.4.6 F 5.4.7 F 5.4.7 | Detection System (PDS) Overview                                                                                                                                                                           | .20<br>.20<br>.21<br>.27<br>.28<br>.31<br>.37<br>.38<br>.39<br>.40<br>.47<br>.51<br>.52<br>.52<br>.53 |

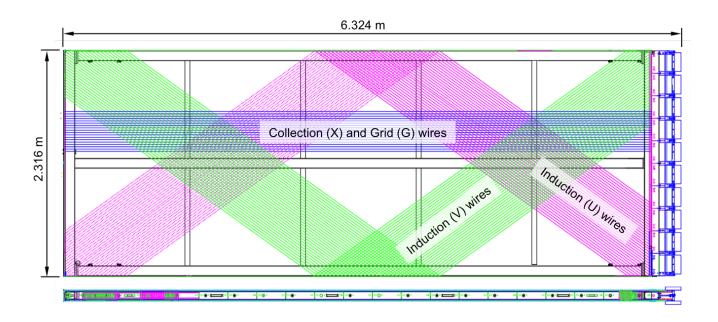

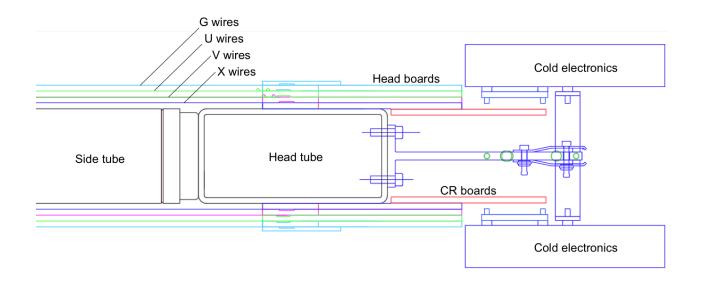

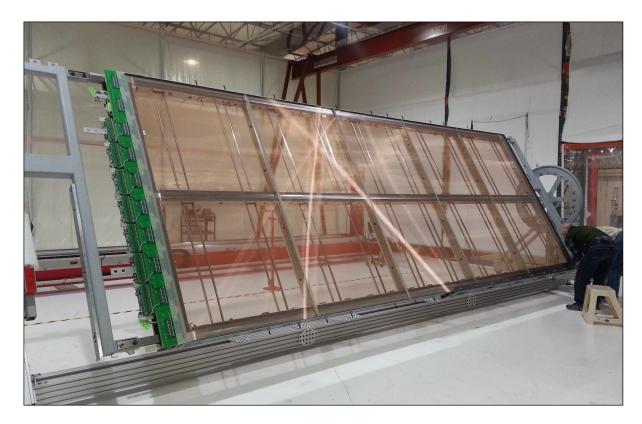

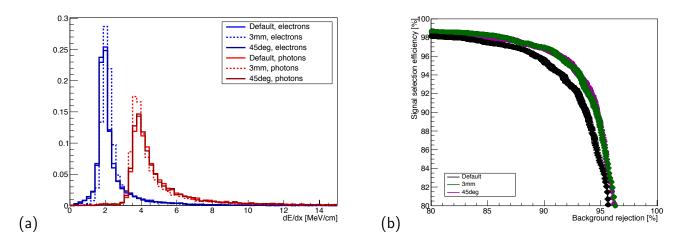

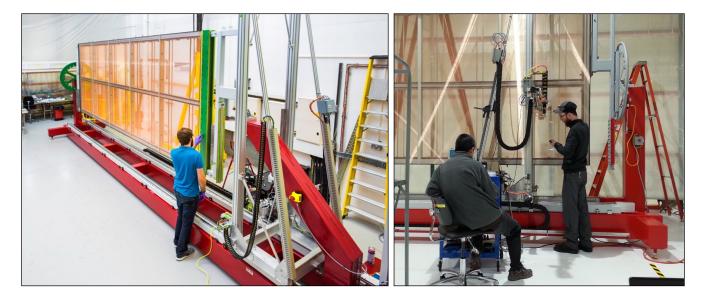

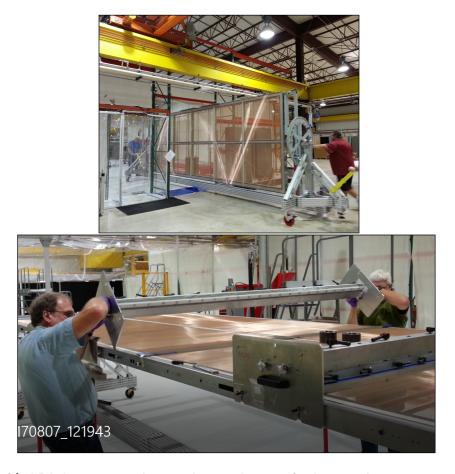

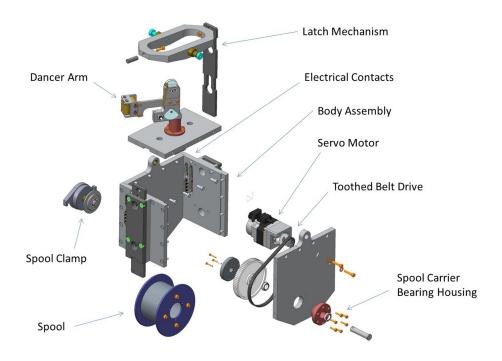

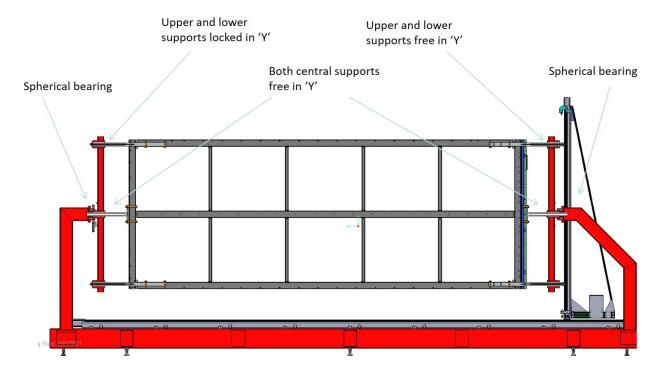

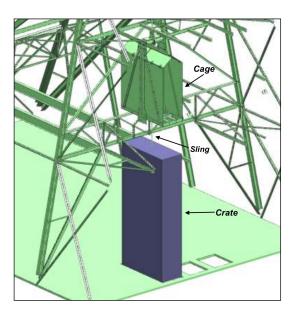

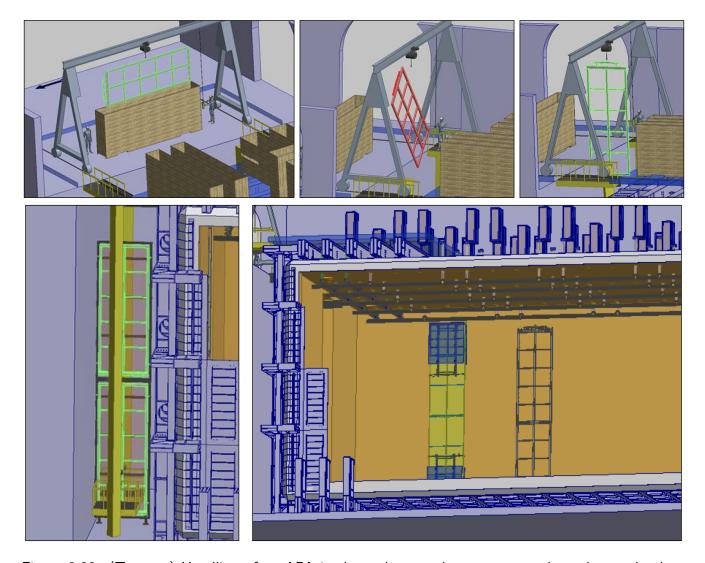

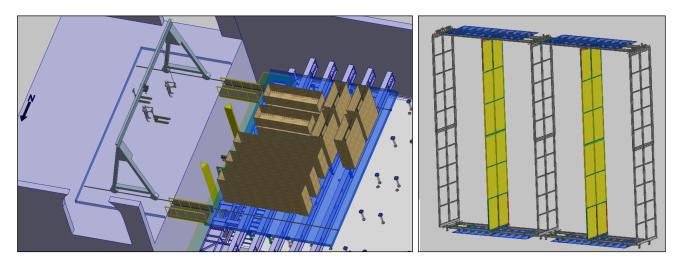

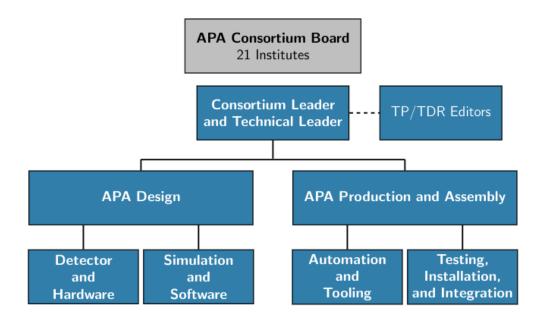

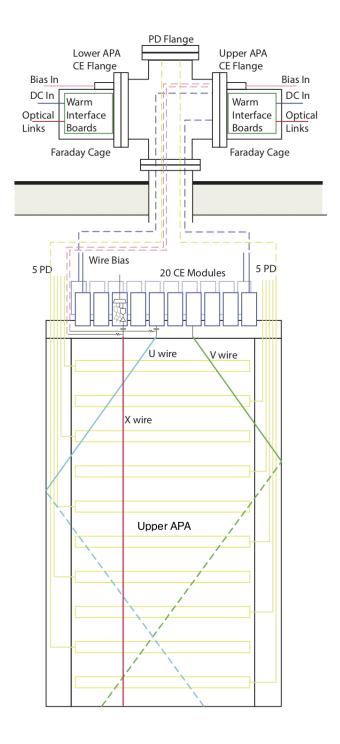

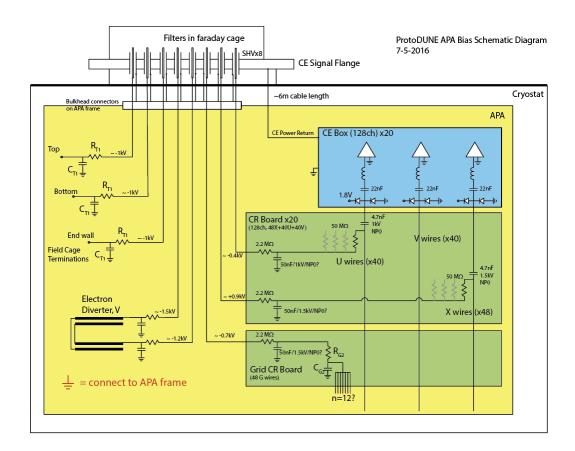

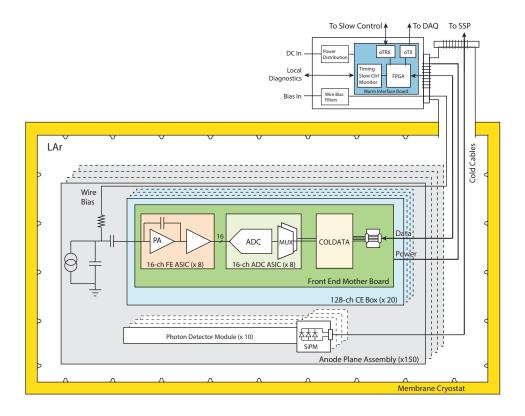

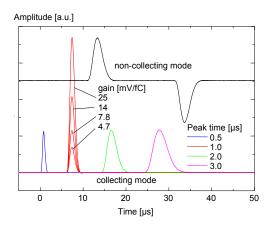

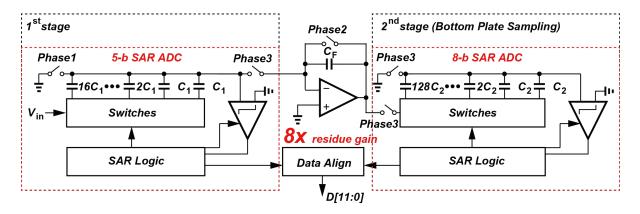

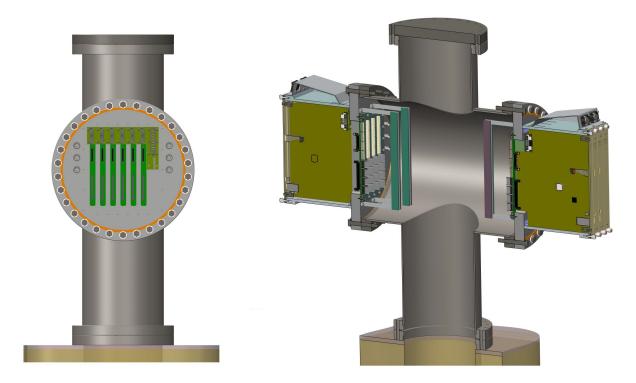

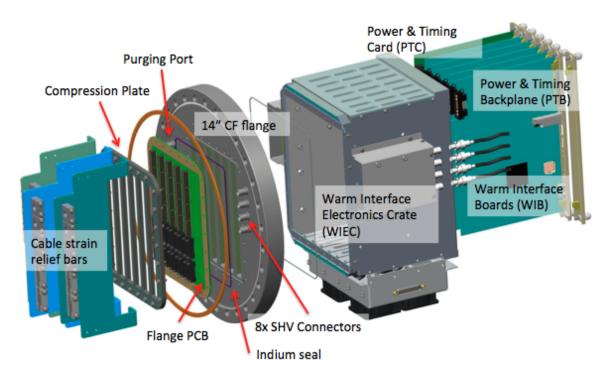

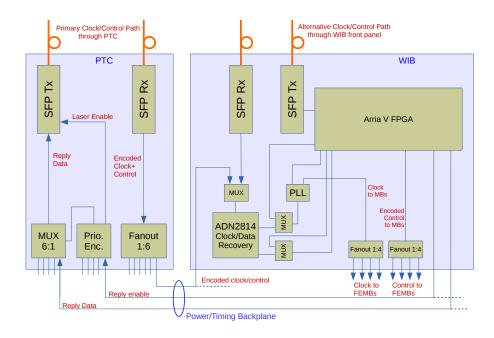

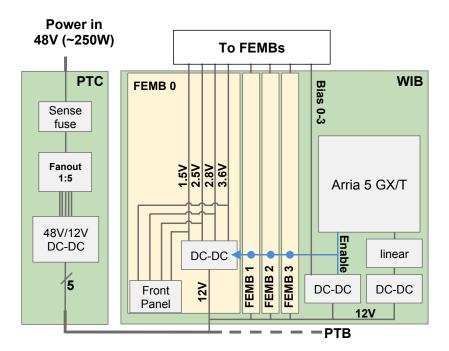

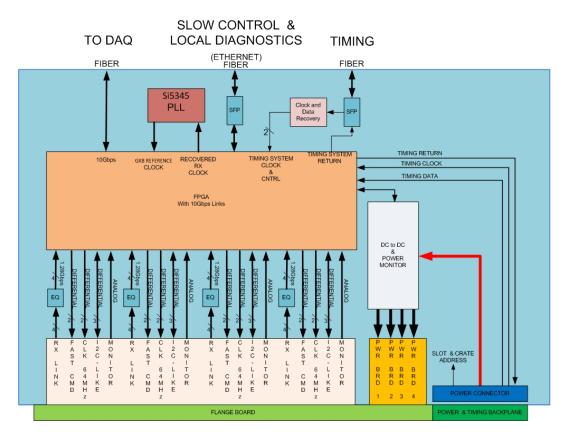

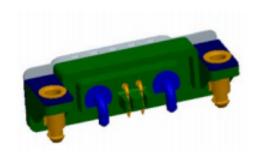

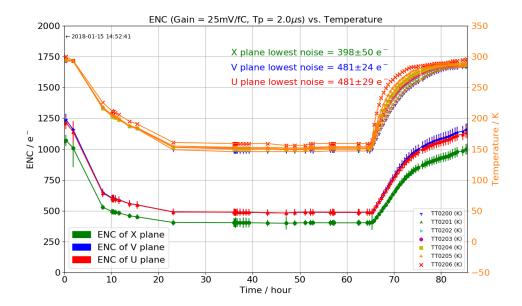

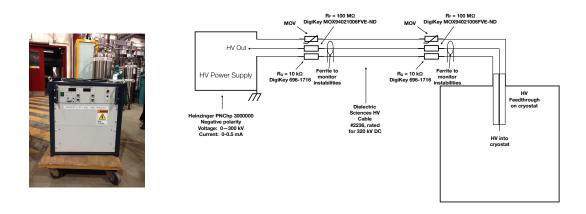

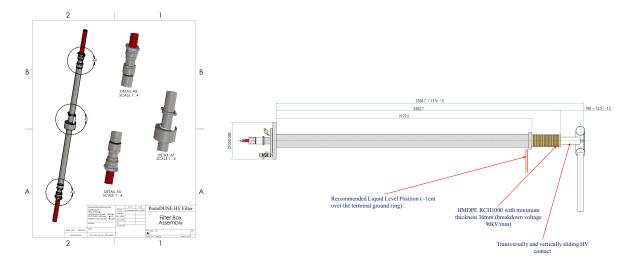

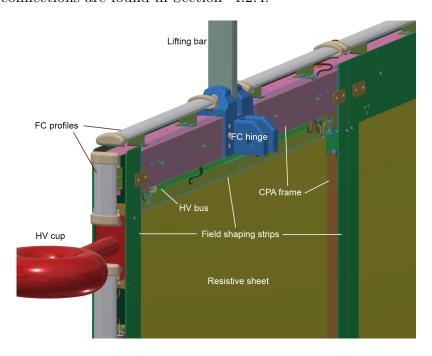

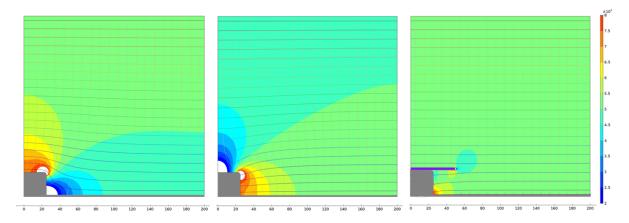

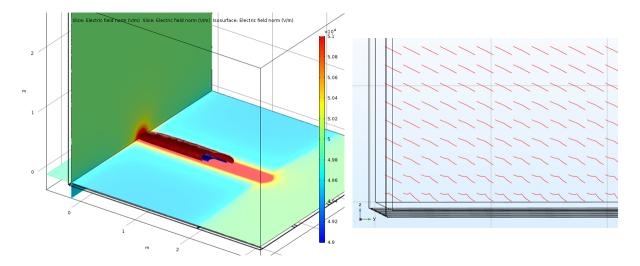

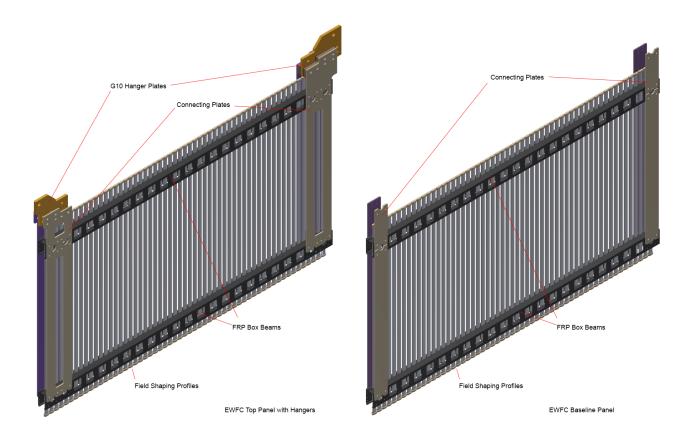

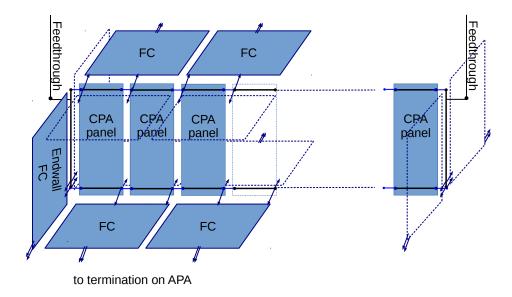

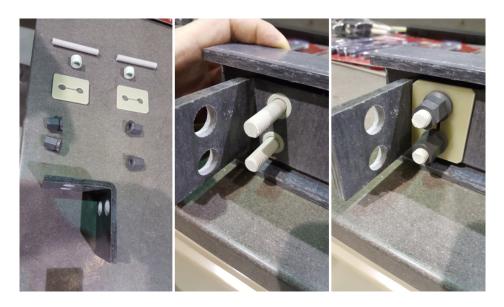

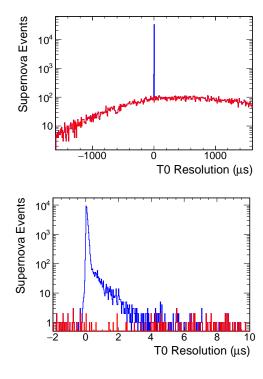

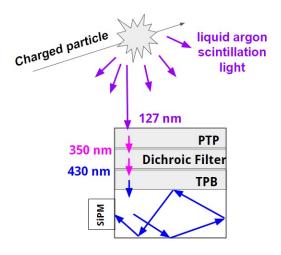

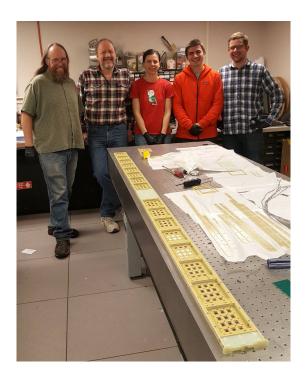

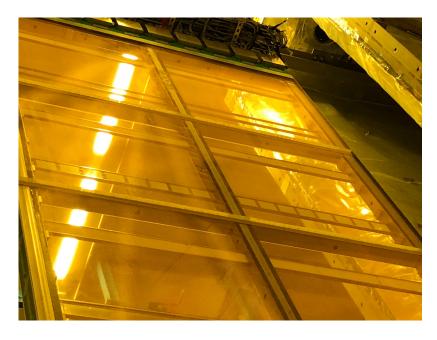

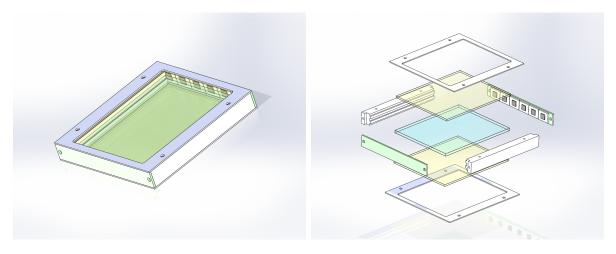

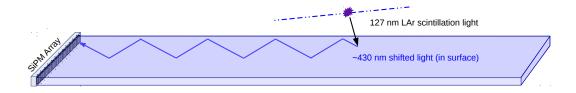

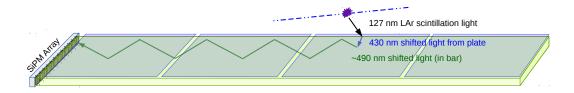

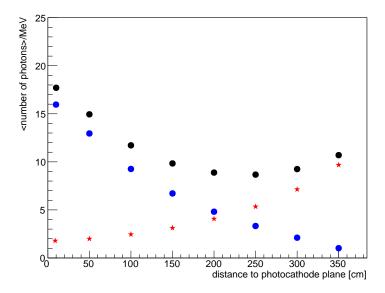

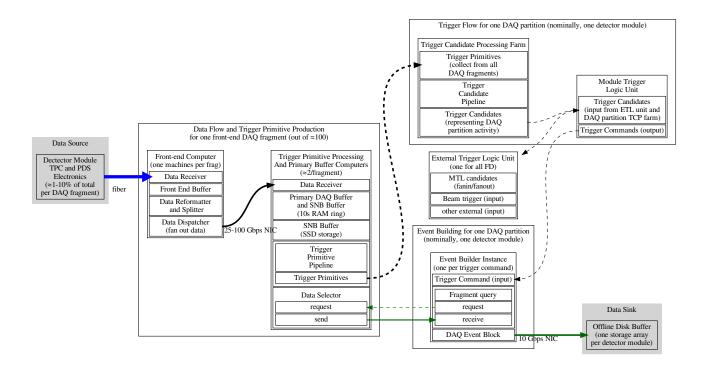

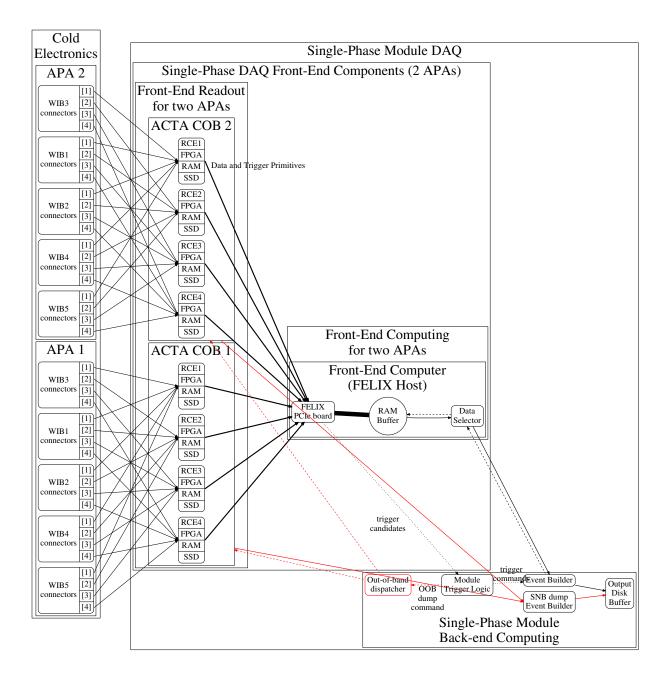

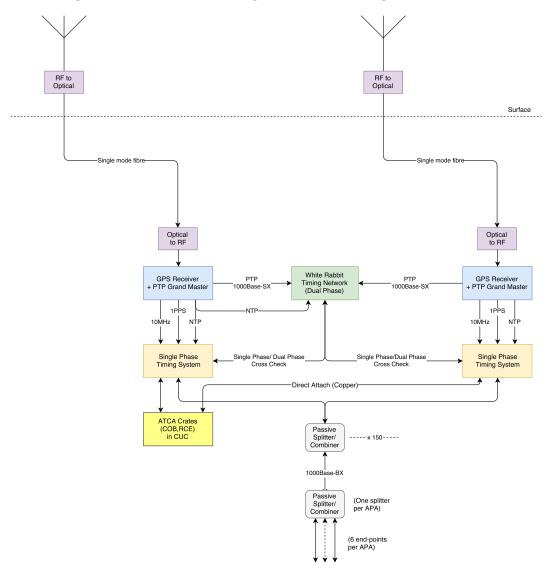

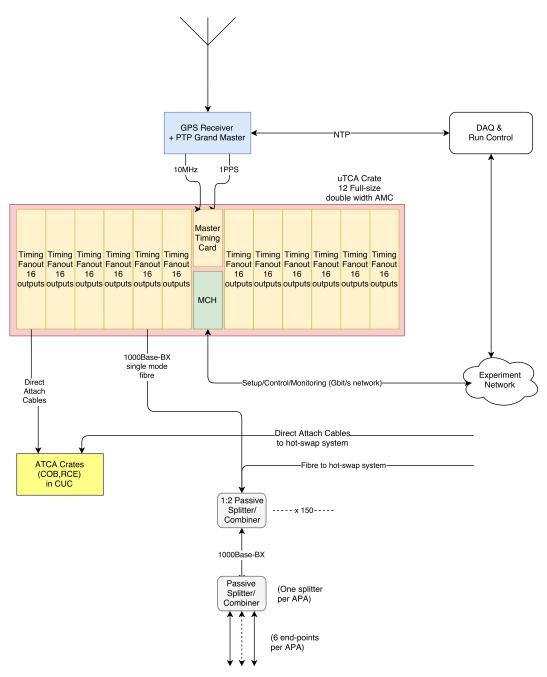

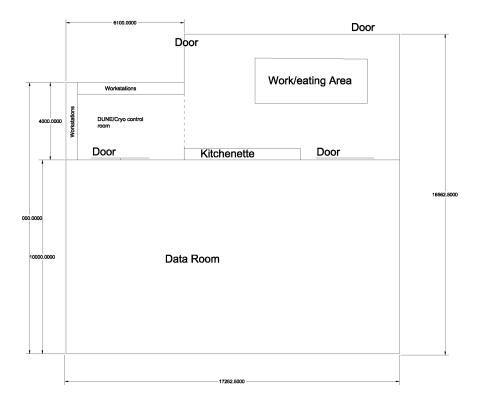

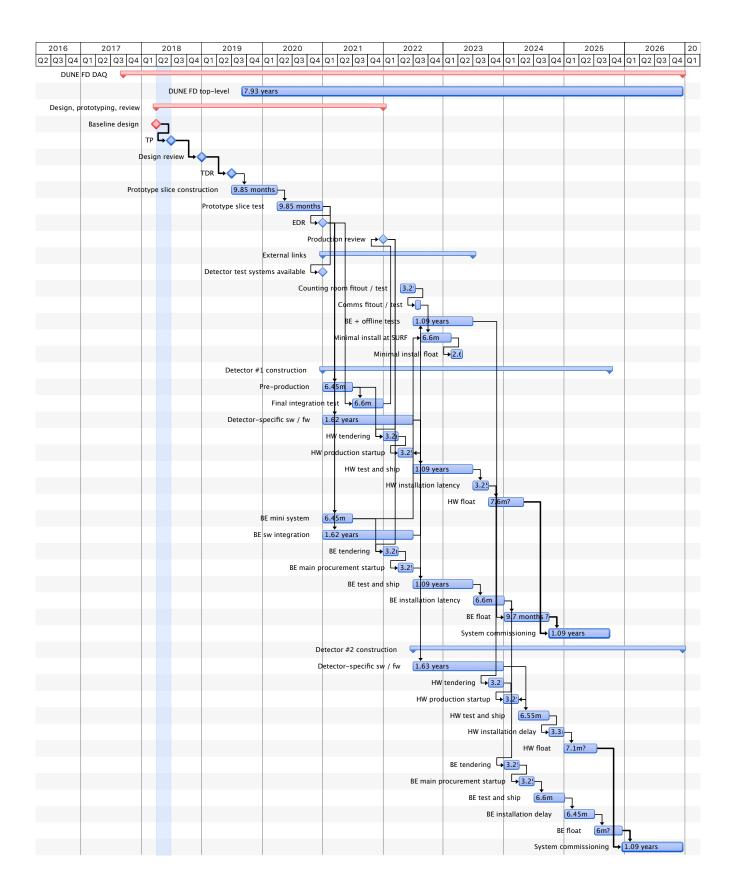

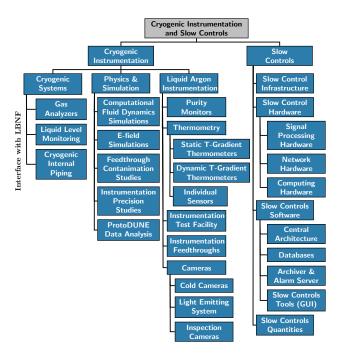

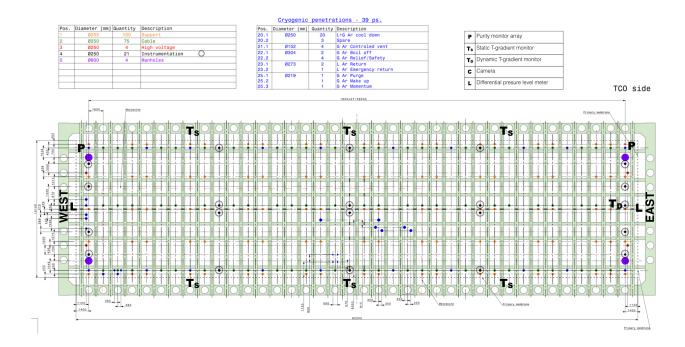

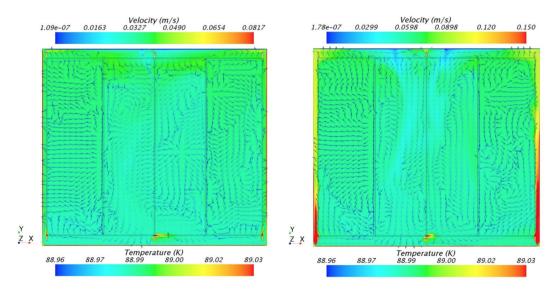

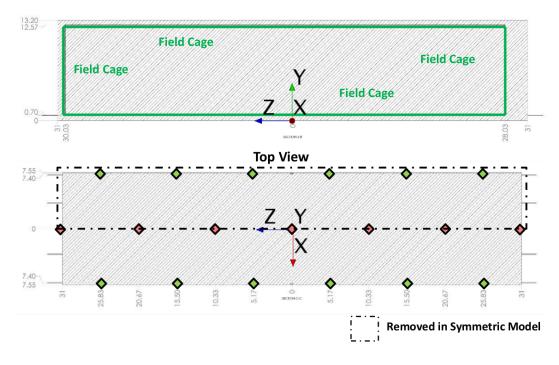

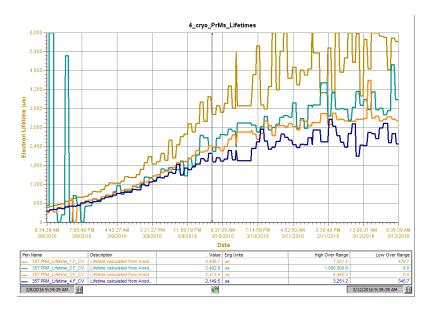

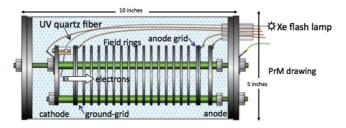

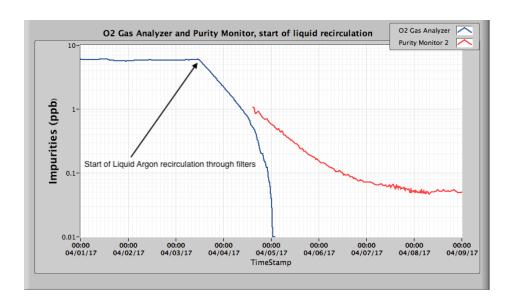

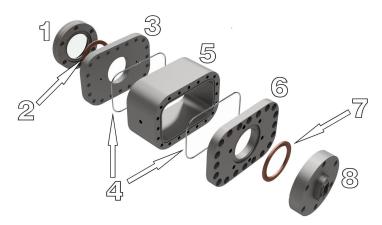

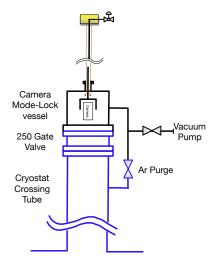

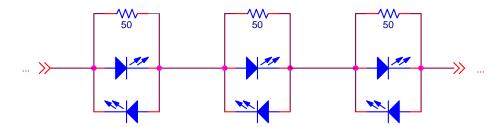

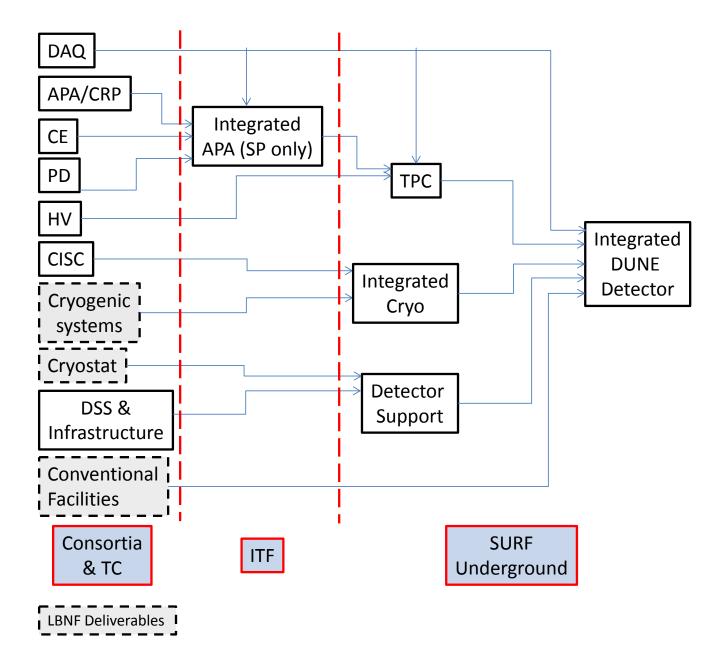

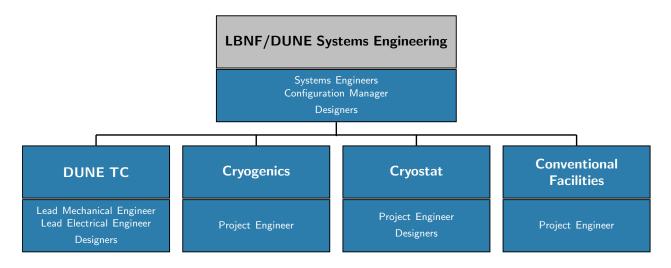

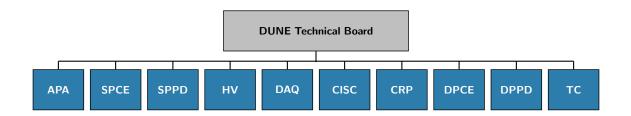

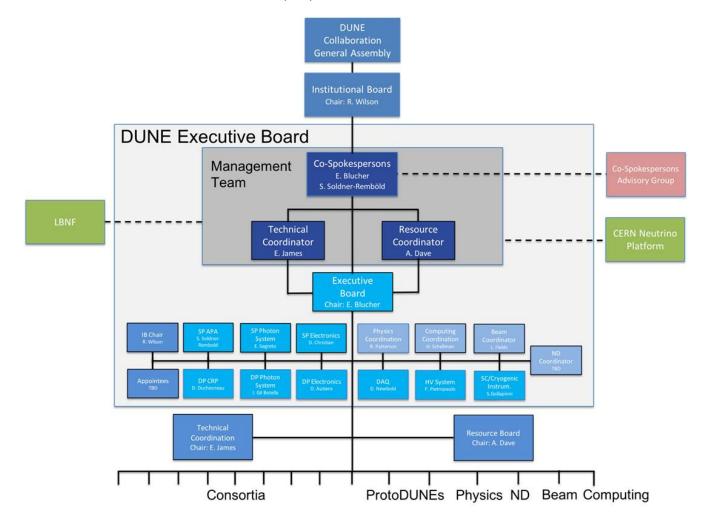

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Photon I 5.1.1 I 5.1.2 I 5.1.3 I Photon I 5.3.1 F 5.3.2 F 5.3.3 F 5.3.4 F 5.3.5 S 5.3.6 E Producti 5.4.1 F 5.4.2 F 5.4.3 I 5.4.4 F 5.4.5 G 5.4.6 F 5.4.7 F 5.4.7 | Detection System (PDS) Overview                                                                                                                                                                           | .20<br>.20<br>.21<br>.27<br>.28<br>.31<br>.37<br>.38<br>.39<br>.40<br>.47<br>.51<br>.52<br>.52<br>.53 |