#### **OPEN ACCESS**

## Production and integration of the ATLAS Insertable B-Layer

To cite this article: B. Abbott et al 2018 JINST 13 T05008

View the article online for updates and enhancements.

PUBLISHED BY IOP PUBLISHING FOR SISSA MEDIALAB

RECEIVED: *March 6, 2018* ACCEPTED: *April 26, 2018* PUBLISHED: *May 16, 2018*

# Production and integration of the ATLAS Insertable B-Layer

# ATLAS EXPERIMENT

### The ATLAS IBL collaboration

*E-mail:* allan.clark@cern.ch

ABSTRACT: During the shutdown of the CERN Large Hadron Collider in 2013-2014, an additional pixel layer was installed between the existing Pixel detector of the ATLAS experiment and a new, smaller radius beam pipe. The motivation for this new pixel layer, the Insertable B-Layer (IBL), was to maintain or improve the robustness and performance of the ATLAS tracking system, given the higher instantaneous and integrated luminosities realised following the shutdown. Because of the extreme radiation and collision rate environment, several new radiation-tolerant sensor and electronic technologies were utilised for this layer. This paper reports on the IBL construction and integration prior to its operation in the ATLAS detector.

KEYWORDS: Large detector systems for particle and astroparticle physics; Particle tracking detectors (Solid-state detectors)

ArXiv ePrint: 1803.00844

## Contents

| 1 | Intr | oductio  | n                                                           | 2  |

|---|------|----------|-------------------------------------------------------------|----|

| 2 | Dete | ector ov | erview and physics motivations                              | 3  |

|   | 2.1  | Layout   | toverview                                                   | 3  |

|   | 2.2  | System   | 1 overview                                                  | 7  |

|   | 2.3  | Trackin  | ng and flavour tagging performance                          | 8  |

| 3 | Mod  | lules    |                                                             | 11 |

|   | 3.1  | Sensor   | 'S                                                          | 12 |

|   |      | 3.1.1    | Planar design                                               | 12 |

|   |      | 3.1.2    | 3D design                                                   | 13 |

|   |      | 3.1.3    | Sensor production and quality assessment                    | 14 |

|   | 3.2  | On-det   | tector electronics                                          | 16 |

|   |      | 3.2.1    | The FE-I4 front-end chip                                    | 16 |

|   |      | 3.2.2    | FE-I4B production and quality assessment                    | 17 |

|   | 3.3  | Modul    | e assembly                                                  | 18 |

|   |      | 3.3.1    | Hybridisation of the FE-I4B chip and the sensor             | 18 |

|   |      | 3.3.2    | Module flex hybrid                                          | 20 |

|   |      | 3.3.3    | Final module assembly                                       | 21 |

|   | 3.4  | Modul    | e performance and quality assurance                         | 22 |

|   |      | 3.4.1    | Module I-V characteristics                                  | 23 |

|   |      | 3.4.2    | Module time-walk and threshold tuning                       | 25 |

|   |      | 3.4.3    | Module ToT-to-charge calibration                            | 28 |

|   |      | 3.4.4    | Module electronic noise                                     | 28 |

|   |      | 3.4.5    | Module bump-bond connectivity and individual pixel failures | 29 |

|   | 3.5  | Modul    | e production and yield                                      | 30 |

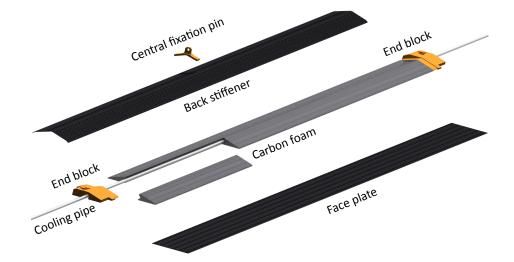

| 4 | Stav | e comp   | onents                                                      | 33 |

|   | 4.1  | The ba   | ire stave                                                   | 33 |

|   |      | 4.1.1    | Bare stave material                                         | 34 |

|   |      | 4.1.2    | Bare stave quality control and production                   | 34 |

|   | 4.2  | Stave f  |                                                             | 36 |

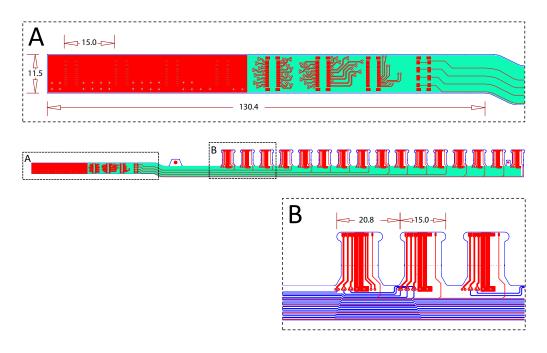

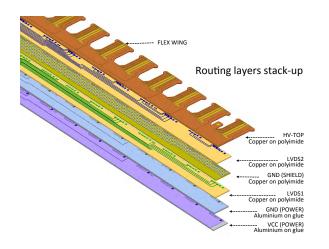

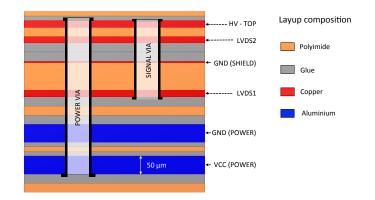

|   |      | 4.2.1    | Stave flex layout                                           | 37 |

|   |      | 4.2.2    | The process flow                                            | 39 |

|   |      | 4.2.3    | Quality control and production                              | 40 |

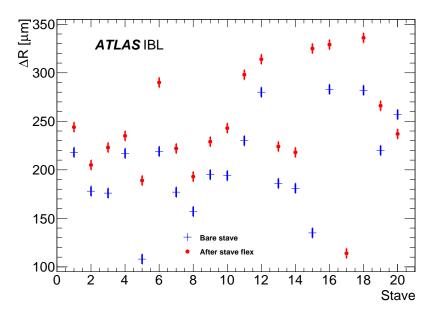

|   | 4.3  | Bare st  | tave and stave flex assembly                                | 41 |

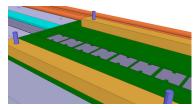

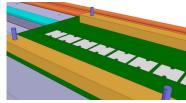

|   |      | 4.3.1    | Stave flex gluing                                           | 41 |

|   |      | 4.3.2    | Quality control of stave assembly components                | 41 |

| 5 | Stav | e loading and quality assurance                                    | 42 |

|---|------|--------------------------------------------------------------------|----|

|   | 5.1  | Stave loading and rework                                           | 42 |

|   | 5.2  | Quality assurance of the stave assemblies                          | 44 |

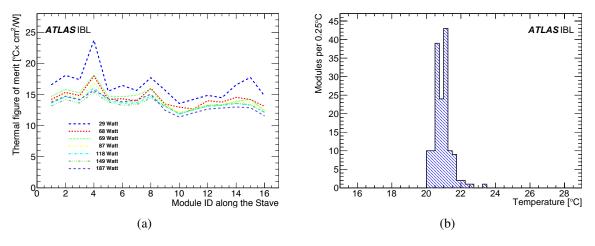

|   |      | 5.2.1 Stave cooling performance                                    | 44 |

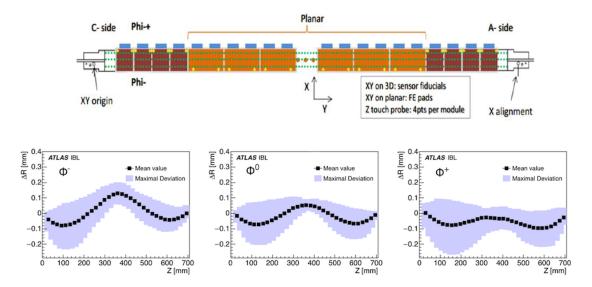

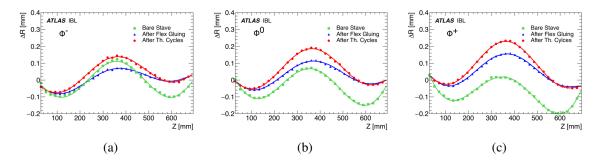

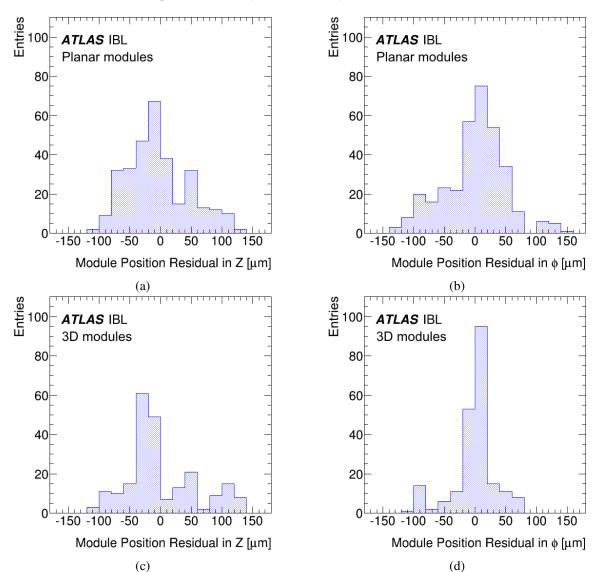

|   |      | 5.2.2 Metrology survey                                             | 46 |

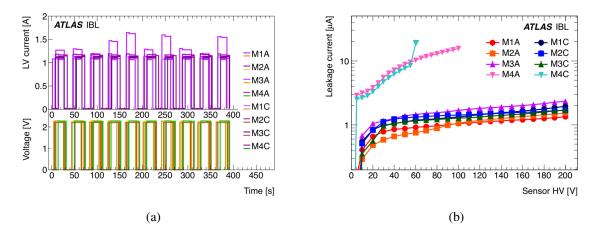

|   |      | 5.2.3 Functional qualification                                     | 47 |

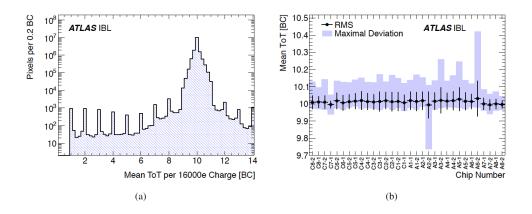

|   |      | 5.2.4 Stave calibration                                            | 49 |

|   |      | 5.2.5 Source scans                                                 | 52 |

|   |      | 5.2.6 Pixel defects                                                | 54 |

|   | 5.3  | Stave ranking and layout assignment                                | 55 |

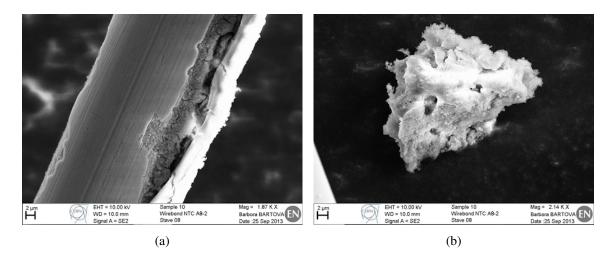

|   | 5.4  | Wire bond corrosion                                                | 56 |

|   |      | 5.4.1 Investigations of the Al wire corrosion process              | 59 |

| 6 | Off- | detector electronics and services                                  | 61 |

|   | 6.1  | Off-detector electrical cabling                                    | 61 |

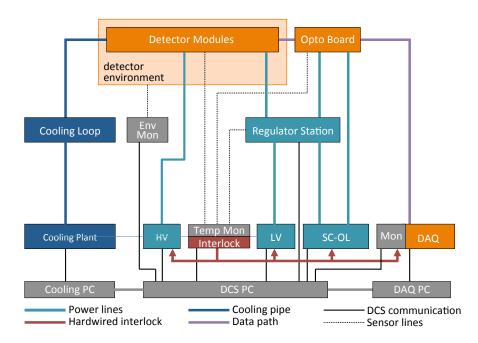

|   | 6.2  | The detector control, interlock and power supply systems           | 62 |

|   |      | 6.2.1 The DCS and interlock systems                                | 62 |

|   |      | 6.2.2 The IBL power supplies                                       | 64 |

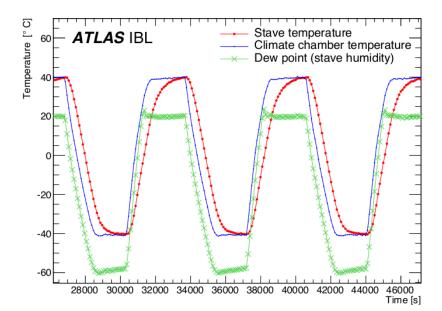

|   |      | 6.2.3 Temperature and humidity monitoring                          | 64 |

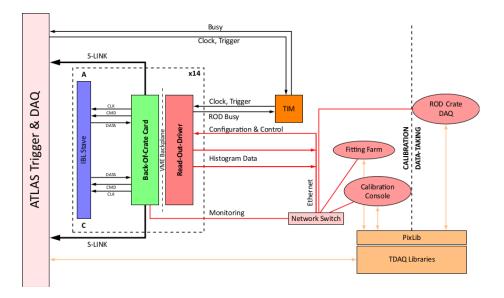

|   | 6.3  | Data Acquisition System (DAQ)                                      | 65 |

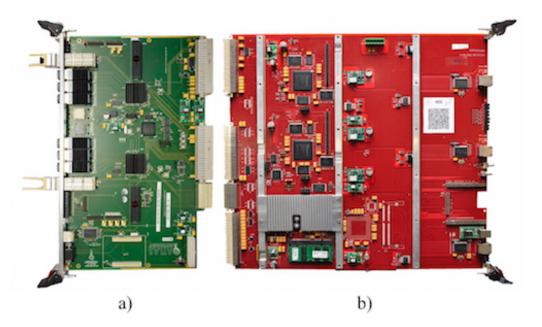

|   |      | 6.3.1 Optical link                                                 | 65 |

|   |      | 6.3.2 Off-detector read-out electronics (ROD/BOC)                  | 66 |

| 7 | Inte | rfaces and integration                                             | 67 |

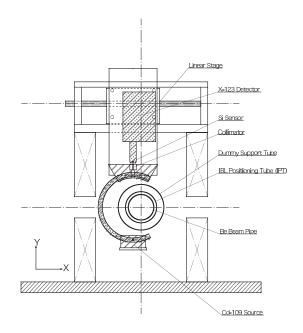

|   | 7.1  | The beryllium beam pipe                                            | 68 |

|   | 7.2  | The inner mechanical structure of IBL and its external envelope    | 69 |

|   | 7.3  | Surface integration and installation                               | 71 |

|   | 7.4  | Electrical tests after stave integration                           | 72 |

|   | 7.5  | CO <sub>2</sub> cooling system                                     | 74 |

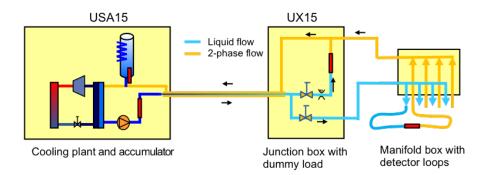

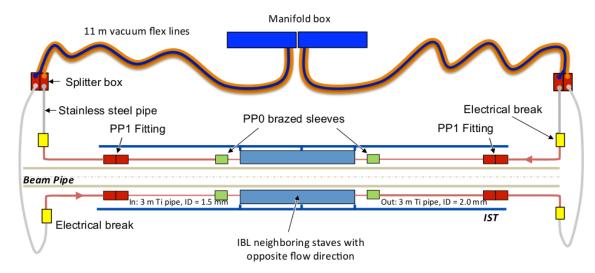

|   |      | 7.5.1 Cooling system operation                                     | 75 |

|   |      | 7.5.2 Redundant system                                             | 75 |

|   |      | 7.5.3 Detector distribution                                        | 76 |

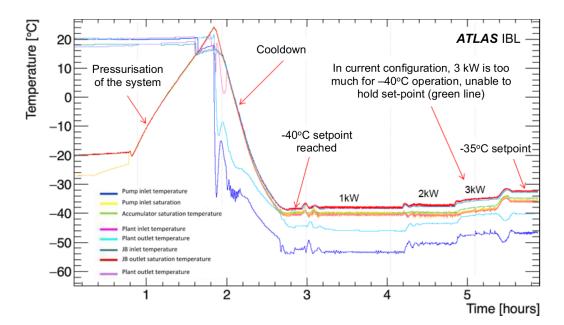

|   |      | 7.5.4 Commissioning                                                | 77 |

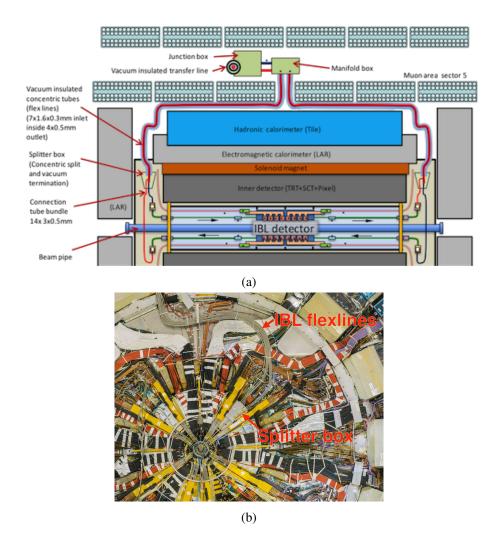

|   | 7.6  | On-detector cooling branch and interfaces                          | 78 |

|   |      | 7.6.1 Fittings outside the IBL volume                              | 78 |

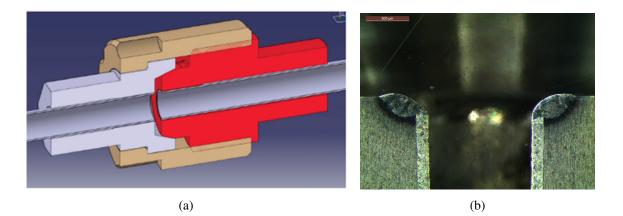

|   |      | 7.6.2 The cooling line electrical break                            | 79 |

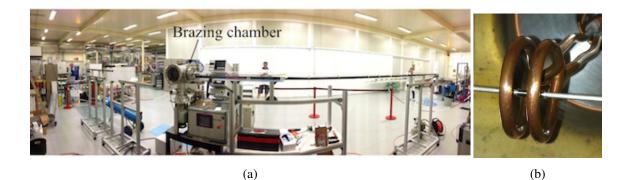

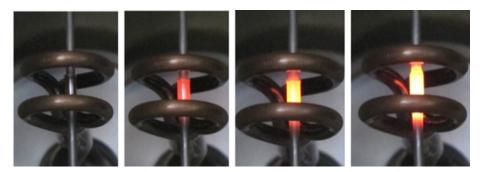

|   |      | 7.6.3 The brazing junction of the stave inside the detector volume | 80 |

| 8 | Fina | ll remarks and conclusion                                          | 81 |

|   | 8.1  | The IBL challenges                                                 | 81 |

|   | 8.2  | IBL in ATLAS                                                       | 83 |

|   | 8.3  | Conclusion                                                         | 84 |

#### 1 Introduction

The ATLAS [1] general purpose detector is used for the study of proton-proton (pp) and heavy-ion collisions at the CERN Large Hadron Collider (LHC) [2]. It successfully collected data at pp collision energies of 7 and 8 TeV in the period of 2010-2012, known as Run 1. Following an LHC shutdown in 2013-2014 (LS1), it has collected data since 2015 at a pp collision energy of 13 TeV (the so-called Run 2).

The ATLAS inner tracking detector (ID) [1, 3] provides charged particle tracking with high efficiency in the pseudorapidity<sup>1</sup> range of  $|\eta| < 2.5$ . With increasing radial distance from the interaction region, it consists of silicon pixel and micro-strip detectors, followed by a transition radiation tracker (TRT) detector, all surrounded by a superconducting solenoid providing a 2 T magnetic field.

The original ATLAS pixel detector [4, 5], referred to in this paper as the Pixel detector, was the innermost part of the ID during Run 1. It consists of three barrel layers (named the B-Layer, Layer 1 and Layer 2 with increasing radius) and three disks on each side of the interaction region, to guarantee at least three space points over the full tracking  $|\eta|$  range. It was designed to operate for the Phase-I period of the LHC, that is with a peak luminosity of  $1 \times 10^{34} \text{ cm}^{-2} \text{s}^{-1}$  and an integrated luminosity of approximately  $340 \text{ fb}^{-1}$  corresponding to a TID of up to  $50 \text{ MRad}^2$  and a fluence of up to  $1 \times 10^{15} \text{ n}_{eq}/\text{cm}^2 \text{ NIEL}$ . However, for luminosities exceeding  $2 \times 10^{34} \text{ cm}^{-2} \text{s}^{-1}$ , which are now expected during the Phase-I operation, the read-out efficiency of the Pixel layers will deteriorate.

This paper describes the construction and surface integration of an additional pixel layer, the Insertable B-Layer (IBL) [6], installed during the LS1 shutdown between the B-Layer and a new smaller radius beam pipe. The main motivations of the IBL were to maintain the full ID tracking performance and robustness during Phase-I operation, despite read-out bandwidth limitations of the Pixel layers (in particular the B-Layer) at the expected Phase-I peak luminosity, and accumulated radiation damage to the silicon sensors and front-end electronics. The IBL is designed to operate until the end of Phase-I, when a full tracker upgrade is planned [7] for high luminosity LHC (HL-LHC) operation from approximately 2025.

The IBL is a small detector that was constructed on a short timescale using the results from sensor, electronic and mechanical R&D programs, to operate over an extended period in a hostile environment. The emphasis was to construct the detector on time, while identifying and understanding the various production and quality assurance (QA) issues with the R&D groups and industrial partners. Some choices during the IBL construction were consequently influenced by the schedule.

<sup>&</sup>lt;sup>1</sup>ATLAS uses a right-handed coordinate system with its origin at the nominal interaction point (IP) in the centre of the detector and the *z*-axis along the beam pipe. The *x*-axis points from the IP to the centre of the LHC ring, and the *y*-axis points upward. Cylindrical coordinates  $(r, \phi)$  are used in the transverse plane,  $\phi$  being the azimuthal angle around the *z*-axis. The pseudorapidity is defined in terms of the polar angle  $\theta$  as  $\eta = -\ln \tan(\theta/2)$ . An ATLAS convention refers to the (-z) side of the detector as the C-side, and the (+z) side of the detector as the A-side.

<sup>&</sup>lt;sup>2</sup>The Total Ionising Dose (TID) in silicon is a measure of the radiation dose for the front-end electronics. For silicon sensors, a more relevant measure of the radiation dose is the non-ionising energy loss (NIEL), normally expressed as the equivalent damage of a fluence of 1 MeV neutrons ( $n_{eq}/cm^2$ ).

The procurement, QA and assembly of the different IBL components into loaded staves were undertaken at the participating institutes. The staves were then transported to CERN, where the final IBL integration and testing was made before installation in the ATLAS experiment.

The motivations and performance of the IBL are briefly described in section 2 together with a brief introduction to the detector layout and the electronic system design. Section 3 describes the production and QA of the individual pixel module components (the sensors, front-end electronics, and module hybrids). This is followed by a discussion of the module assembly and tests to ensure the required electrical and mechanical quality of the modules. The technical specification and fabrication of local support staves and their associated electrical services are discussed in section 4. In section 5 the loading of accepted pixel modules on the staves is described, together with a discussion of the module and stave QA at successive steps in the loading process. Section 6 briefly describes the off-detector services, including the detector control, interlock and power supply systems, and the data acquisition. The integration of the staves and their services around the beam pipe is presented in section 7. Finally, section 8 lists the most critical aspects of the IBL project, together with a short summary of the IBL status following its successful installation in ATLAS.

#### **2** Detector overview and physics motivations

#### 2.1 Layout overview

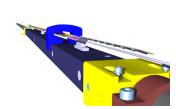

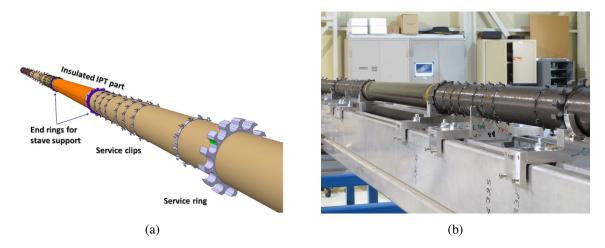

The IBL is a new layer of pixel sensors designed to fit between the B-Layer of the existing Pixel detector and a new beam pipe of reduced inner radius of 23.5 mm. It consists of 14 carbon composite staves, providing full azimuthal ( $\phi$ ) hermeticity for high transverse momentum ( $p_T > 1$  GeV) particles and longitudinal coverage up to  $|\eta|$  of 3. Each stave supports 20 pixel sensor modules together with their electrical services and a cooling pipe. Each module is constructed from a pixel sensor (section 3.1) with each pixel of nominal size  $250 \times 50 \,\mu\text{m}^2$  electrically bonded (section 3.3.1) to a channel of a read-out chip (the FE-I4B chip described below and in section 3.2). The IBL volume contains the staves and the services in the space between an inner support tube (IST) fixed on the Pixel structure and an inner positioning tube (IPT) with an inner radius of 29 mm. A key feature is that independent radial volumes are installed, allowing for the removal of the beam pipe with respect to the IBL package, or the IBL and beam pipe with respect to the Pixel package.

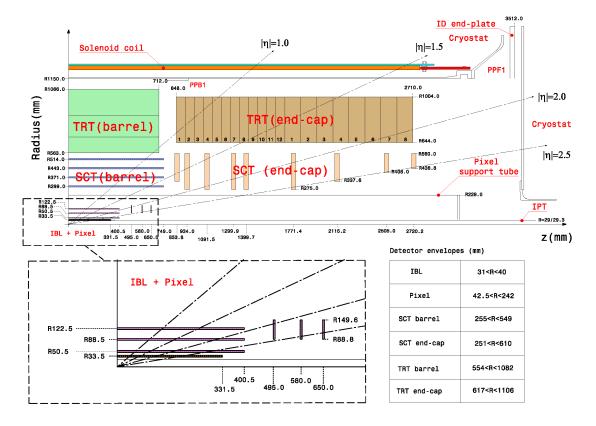

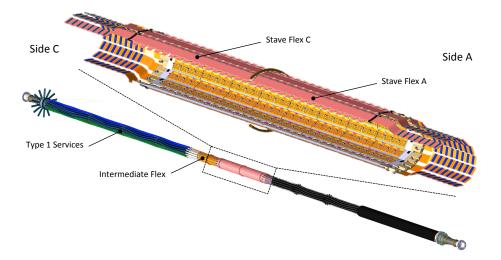

The ATLAS ID, including the IBL detector and its envelope, is shown in figure 1. The 3-dimensional structure of the IBL detector with its services is shown in figure 2.

The main IBL layout parameters are summarised in table 1 and a comparison between the technical characteristics of the IBL and the Pixel detector is shown in table 2. With a mean sensor radius of 33.5 mm (compared with 50.5 mm for the Pixel B-Layer), the IBL sensors and front-end electronics must cope with a much higher hit rate and radiation doses of  $5 \times 10^{15} n_{eq}/cm^2$  NIEL and 250 MRad TID during Phase-I operation. To address these requirements, a new front-end read-out chip, the FE-I4B [8], was developed in 130 nm CMOS technology satisfying the ATLAS requirements of radiation tolerance and read-out efficiency at high luminosity. In addition, the FE-I4B chip has a substantially larger active area compared to the FE-I3 front-end chip [4] of the Pixel detector, and a cell size reduced to  $250 \times 50 \,\mu\text{m}^2$  from  $400 \times 50 \,\mu\text{m}^2$ , the shorter side being in the transverse plane. The smaller layer radius and the reduced pixel cell length are crucial parameters in defining the performance improvement of the ID, in particular the track-extrapolation resolution.

**Figure 1.** The layout of the ATLAS inner tracking detector, including the additional IBL detector layer. The inner positioning tube (IPT) supports the IBL staves and separates them from the beam pipe.

**Figure 2.** Longitudinal view of the IBL detector and its services. The insert shows an enlarged 3-dimensional view of the detector with its modules arranged cylindrically around the beam pipe.

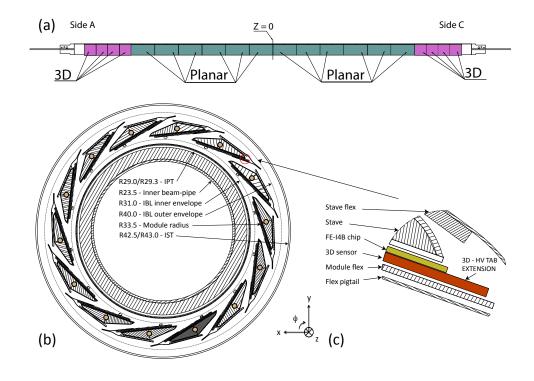

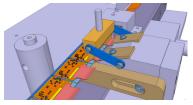

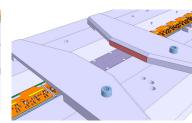

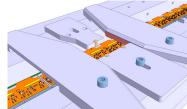

The IBL stave configuration is shown in figure 3. Two module types [9] are installed on each stave. A total of 12 double-chip planar n-in-n sensors similar to those equipping the Pixel detector, each bump-bonded to two FE-I4B read-out chips, populate the central stave region. Four single-chip

Table 1. Main layout parameters for the IBL detector.

| Item                                                  | Value                |

|-------------------------------------------------------|----------------------|

| Number of staves                                      | 14                   |

| Number of physical modules per stave                  | 20 (12 planar, 8 3D) |

| Number of FEs per stave                               | 32                   |

| Coverage in $\eta$ , no vertex spread                 | $ \eta  < 3.0$       |

| Coverage in $\eta$ , $2\sigma$ (122 mm) vertex spread | $ \eta  < 2.58$      |

| Active $ z $ stave length (mm)                        | 330.15               |

| Stave tilt in $\phi$ (degree)                         | 14                   |

| Overlap in $\phi$ (degree)                            | 1.82                 |

| Center of the sensor radius (mm)                      | 33.5                 |

**Figure 3.** IBL detector layout: (a) Longitudinal layout of planar and 3D modules on a stave. (b) An  $r - \phi$  section showing the beam pipe, the inner positioning tube (IPT), the staves of the IBL detector and the inner support tube (IST), as viewed from the C-side. (c) An expanded  $r - \phi$  view of the corner of a 3D module fixed to the stave.

3D sensors, adopted for the first time in a collider tracking detector and each bump-bonded to one FE-I4B chip, populate each end of the stave. The staves are mounted with the sensors facing the beam pipe and are inclined in azimuth by 14° to achieve an overlap of the active area. This tilt also compensates for the Lorentz angle of drifting charges in the case of planar sensors, and the effect

of partial column inefficiency for normal incidence tracks in the case of 3D sensors. Owing to space constraints, the sensors are not shingled along the stave (in z). To minimise the dead region, modules are glued on the stave with a physical gap of 200 µm.

| Technical characteristic                | Pixel                         | IBL             |

|-----------------------------------------|-------------------------------|-----------------|

| Active surface (m <sup>2</sup> )        | 1.73                          | 0.15            |

| Number of channels (x 10 <sup>6</sup> ) | 80.36                         | 12.04           |

| Pixel size (µm <sup>2</sup> )           | 50×400                        | 50×250          |

| Pixel array (columns $\times$ rows)     | 160×18                        | 336×80          |

| Front-end chip size (mm <sup>2</sup> )  | 7.6×10.8                      | 20.2×19.0       |

| Active surface fraction (%)             | 74                            | 89              |

| Analog current (µA/pixel)               | 26                            | 10              |

| Digital current (µA/pixel)              | 17                            | 10              |

| Analog voltage (V)                      | 1.6                           | 1.4             |

| Digital voltage (V)                     | 2.0                           | 1.2             |

| Data out transmission (MBit/s)          | 40-160                        | 160             |

| Sensor type                             | planar                        | planar / 3D     |

| Sensor thickness (µm)                   | 250                           | 200 / 230       |

| Layer thickness (% X <sub>0</sub> )     | 2.8                           | 1.88            |

| Cooling fluid                           | C <sub>3</sub> F <sub>8</sub> | CO <sub>2</sub> |

Table 2. Comparison of the main characteristics of the Pixel and IBL detectors.

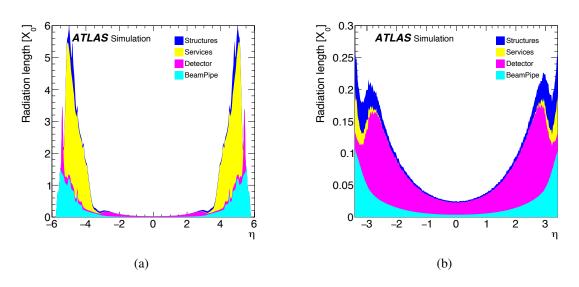

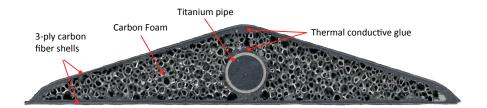

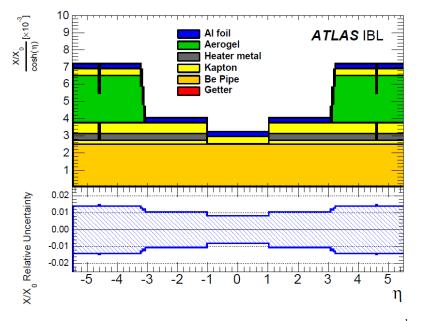

Minimising the material budget is very important for the optimisation of the tracking and vertex performance. The IBL radiation length, averaged over azimuth and taking into account the stave tilt and the overlap between staves, is estimated to be  $1.88\% X_0$  for tracks produced perpendicular to the beam axis at z = 0. This is ~30 % less than that of the Pixel B-Layer.<sup>3</sup> The reduced thickness was achieved by using more advanced technologies as discussed in the following sections. These include: a new low-mass module design; local support structures (staves) made of low density, thermally conductive carbon foam; the use of CO<sub>2</sub> evaporative cooling, which is more efficient in terms of mass flow and pipe size; and electrical power services using aluminium conductors. Table 3 reports the main contributions to the IBL material budget. Figure 4 shows the material traversed by a straight track originating in z = 0 as a function of  $\eta$ , smeared over the azimuthal angle.

<sup>&</sup>lt;sup>3</sup>The as-built IBL radiation length was evaluated using the ATLAS geometry model, as discussed in the IBL TDR [6]. The difference with respect to the value reported in the IBL TDR is mainly due to an initial underestimation of the module material and the addition of the IPT. A recent description of the ATLAS ID material and its comparison with Run 2 collision data is now available [10].

**Table 3.** IBL material budget as a fraction of  $X_0$ , averaged over the azimuthal angle  $\phi$  for straight tracks produced perpendicular to the beam axis at z = 0, as implemented in the ATLAS geometry model. The beam pipe material is excluded from the IBL total.

| Item      | Value (% $X_0$ ) |

|-----------|------------------|

| Beam pipe | 0.32             |

| IPT       | 0.12             |

| Module    | 0.76             |

| Stave     | 0.60             |

| Services  | 0.19             |

| IST       | 0.21             |

| IBL total | 1.88             |

**Figure 4.** Material budget of the IBL detector as a fraction of  $X_0$ , as implemented in the ATLAS geometry model using straight tracks originating from the nominal beam line at z = 0. Different components are shown: beam pipe, detector (IBL staves, modules, inner positioning tube (IPT)), services (cooling and cables) and structures (stave rings, end-blocks, sealing ring area, inner support tube (IST)). (a) Dependence on  $\eta$ , averaged over  $\phi$ . (b) A zoomed view of the central  $|\eta|$  region where precise tracking ( $|\eta| < 2.5$ ) is performed.

#### 2.2 System overview

The IBL electronic system includes the FE-I4B read-out chip, the off-detector read-out boards (the read-out driver (ROD) [11] and the back-of-crate board (BOC) [12, 13]), the detector control system (DCS) [14], the electronics and sensor power supplies, and all of their associated electrical and optical services. The data acquisition (DAQ) [15] controls the transfer of data to and from the off-detector read-out boards, while the DCS controls the electrical and environmental monitoring of the detector as well as the power distribution to the pixel sensors and FE-I4B chips.

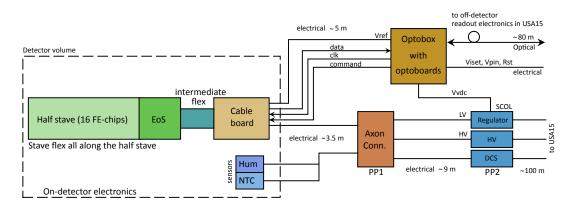

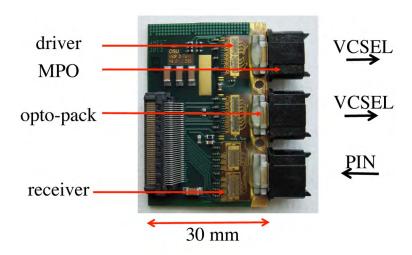

The electrical service design was driven by physical space constraints, especially in the inner region where all services and connectors must fit into the narrow IBL envelope over a length of approximately 3 m, and by the conflicting requirements of material budget, radiation hardness and electrical performance. Optical transmission is excluded in the IBL envelope because of the high radiation level. Figure 5 shows a block diagram of electrical services for one half-stave (the services are symmetrical, at each end of a stave). Each module of a given half-stave is connected electrically by a stave flex to an end-of-stave (EoS) card. The stave flex transfers the data from the half-stave, as well as control signals from the DAQ and DCS, and the power distribution. In the EoS region the detector services are connected via intermediate flexes to a cable board. The cable board connects the flexes to ~3 m-long extensions (Type 1 cables) that reach the ID end-plate where the first Patch Panel (PP1) is located to allow for electrical and optical connections to the external services after installation in ATLAS. A second break of the electrical services occurs at another Patch Panel (PP2) on the detector periphery that is accessible during a short shut-down.

**Figure 5.** Block diagram of on-detector and off-detector electrical services for one half-stave of the IBL detector. The on-detector front-end read-out and services are described in sections 3 and 4. The off-detector services (Type 1 cables) reaching the PP1 patch panel and opto-box are described in section 6.

Details of the FE-I4B chip and the module flex hybrid that connect a module to the stave flex are described in section 3, while those of the stave flexes are described in section 4. The off-detector electronics and power-supplies, as well as the electrical and optical services, are described in section 6.

#### 2.3 Tracking and flavour tagging performance

The ATLAS ID provides charged particle tracking with high efficiency in the  $|\eta| < 2.5$  range over the full azimuthal range. The pixel layers are crucial for the reconstruction of charged particles trajectories, for their extrapolation to the production point and for the reconstruction of multiple collision and decay vertices which occur in each bunch crossing. The pixels are therefore of crucial importance to the flavour tagging performance. Any inefficiency of the innermost B-Layer would result in a degradation of that performance.

A first assessment of the expected improvements in tracking and vertex reconstruction performance was performed for the IBL Technical Design Report (TDR) [6]. Since then, the ATLAS simulation, digitisation and cluster reconstruction algorithms have been refined and improved. The IBL improves the track extrapolation resolution with respect to the Pixel detector of Run 1 by providing an additional high-precision hit closer to the interaction point. This is particularly important for low  $p_T$  particles, where it mitigates the effect of multiple scattering in the detector material on the track extrapolation, thus improving the impact parameter resolution in both the transverse ( $d_0$ ) and longitudinal ( $z_0$ ) projections. The smaller pixel pitch of the IBL in the longitudinal direction contributes to improving the resolution in  $z_0$  across the full  $p_T$  spectrum.

The track reconstruction performance has been evaluated using Monte Carlo simulations of  $t\bar{t}$  events, comparing the Run 1 detector geometry to a geometry including the IBL, while keeping all other conditions unchanged. An improvement in the  $z_0$  resolution of approximately 2 (1.5) for tracks with  $p_T$  of 1 (100) GeV is observed following the addition of the IBL. In the transverse direction, the addition of the IBL improves the  $d_0$  resolution by a factor of approximately 2 for tracks with  $p_T$  of 1 GeV, with the resolutions for the two geometries converging beyond 10 GeV. These results are confirmed by comparing the track impact parameter resolution measured in Run 1 (2012) data with that in Run 2 (2015) data [16].

In addition to the charged particle track reconstruction, these improvements enhance the primary vertex reconstruction and resolution, the secondary vertex finding, and the flavour tagging performance, hence considerably extending the physics reach of ATLAS analyses.

The IBL also helps to maintain the performance and robustness of the ID track reconstruction when the B-Layer read-out efficiency deteriorates at high peak luminosity, or after a large integrated luminosity (radiation damage to the sensors and front-end electronics as well as possible irreparable failures of its chips and modules).

The flavour tagging performance expected with the addition of the IBL is evaluated using a more realistic simulation of the ATLAS ID based on the final IBL geometry, an updated digitisation model and improved reconstruction algorithms with respect to the IBL TDR. The latter include a refined neural network clustering algorithm [17], a new tracking configuration, which improves the treatment of shared clusters in the core of a dense jet environment [18] and new flavour tagging algorithms. These results supersede those presented in the IBL TDR. Results are based on fully simulated  $t\bar{t}$  production events at a collision energy of 13 TeV. The average level of pile-up is approximately 20, reflecting the Run 1 luminosity profile. Jets used for flavour tagging are reconstructed using the anti- $k_t$  algorithm [19] with radius R = 0.4. ATLAS combines the discriminating variables obtained from impact parameter, inclusive secondary vertex and multi-vertex reconstruction algorithms. A detailed description of these algorithms can be found in reference [20].

The combination of the input variables obtained from these algorithms is obtained using a boosted decision tree (MV2c20) [21]) that returns a continuum variable peaked around 1 for jets likely to contain a *b*-flavoured hadron and around -1 for those likely to originate from light-flavoured quarks. This MV2c20 is an evolution of the neural network algorithm used during Run 1 [20]. In order to perform an useful comparison, the MV2c20 algorithm has been separately re-trained for the  $t\bar{t}$  sample generated using the ATLAS Run 1 geometry, without the IBL, and the ATLAS Run 2 geometry, which includes the IBL.

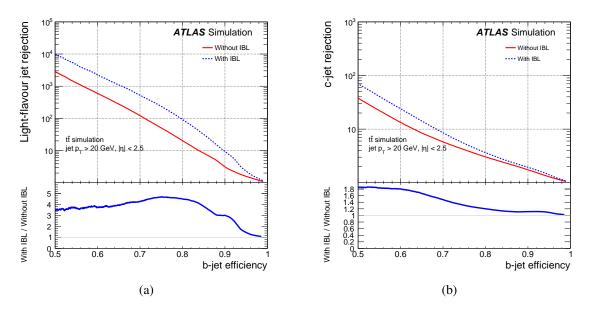

Figure 6 shows the light-jet and *c*-jet rejection as a function of the *b*-jet purity obtained with the two configurations. The addition of the IBL improves the light-jet (*c*-jet) rejection by a factor up to 4 (1.8) for *b*-jet tagging efficiencies up to 85%. Physics analyses will most often profit from the improved performance by re-tuning their *b*-tagging requirements in such a way to keep a

**Figure 6.** Comparison of (a) light-jet and (b) *c*-jet rejection as a function of *b*-jet tagging efficiency for the Run 1 (without IBL) and Run 2 (with IBL) detector layouts under the same conditions, obtained with the MV2c20 algorithm. The rejection is defined as the reciprocal of the tagging efficiency. Results are derived from jets produced in  $t\bar{t}$  events, with jets passing the  $p_{\rm T} > 20$  GeV and  $|\eta| < 2.5$  selection.

similar background rejection with an increased signal efficiency. The improvement in performance at constant rejection is summarised in table 4 for different working points.

**Table 4.** Comparison of the *b*-jet tagging efficiency for fixed light- or *c*-jet rejection for the Run 1 (without IBL) and Run 2 (with IBL) detector layouts under the same conditions. Results are obtained for jets in simulated  $t\bar{t}$  events satisfying  $p_{\rm T} > 20$  GeV and  $|\eta| < 2.5$ .

| light-jet rejection     | <i>b</i> -jet efficiency | <i>b</i> -jet efficiency |

|-------------------------|--------------------------|--------------------------|

|                         | without IBL (%)          | with IBL (%)             |

| 1000                    | 57                       | 65                       |

| 100                     | 71                       | 79                       |

| 10                      | 84                       | 90                       |

| <i>c</i> -jet rejection | <i>b</i> -jet efficiency | <i>b</i> -jet efficiency |

|                         | without IBL (%)          | with IBL (%)             |

| 20                      | 56                       | 62                       |

| 10                      | 63                       | 68                       |

| 5                       | 72                       | 76                       |

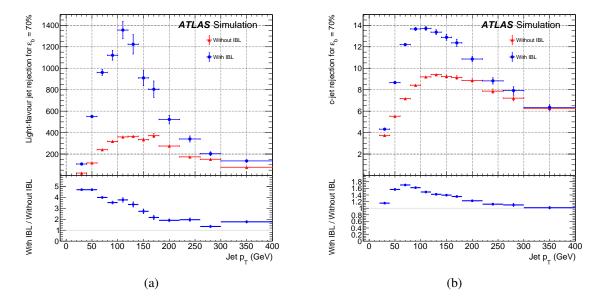

The *b*-tagging performance as a function of jet  $p_T$  is shown in figure 7. The largest improvements are seen at low values of the jet  $p_T$  where the proximity of the IBL to the interaction region significantly reduces the impact of multiple scattering in the track reconstruction. The improvement

in light-jet (*c*-jet) rejection ranges reaches a factor 4 (1.6) for jet  $p_T \leq 100$  GeV while at higher  $p_T$  the tracking performance gain is limited by shared clusters from collimated tracks produced in the core of high  $p_T$  jets.

**Figure 7.** Comparison of (a) light-jet and (b) *c*-jet rejection as a function of jet transverse momentum, while keeping the *b*-tagging efficiency fixed at 70% in each  $p_T$  bin for the Run 1 (without IBL) and Run 2 (with IBL) detector layouts under the same conditions, obtained with the MV2c20 algorithm. The rejection is defined as the reciprocal of the tagging efficiency. Results are derived using jets produced in  $t\bar{t}$  events and passing the  $p_T > 20$  GeV and  $|\eta| < 2.5$  selection.

#### 3 Modules

The basic building block of the IBL detector is the module. For each beam crossing an FE-I4B read-out chip records, digitises and locally stores the data from a silicon sensor that is connected to it. Two sensor technologies are used: planar and 3D. A planar silicon wafer contains four sensor tiles, each of nominal dimension 41 340  $\mu$ m × 18 600  $\mu$ m (41 315  $\mu$ m × 18 585  $\mu$ m in the production process after dicing). A 3D silicon wafer contains eight sensor tiles, each of dimension 20 400  $\mu$ m × 18 700  $\mu$ m. There are consequently two module types, planar and 3D:

- A planar module consists of a planar sensor tile connected to two FE-I4B chips. Each chip consists 26880 pixel cells having analog and digital circuitry arranged in a matrix of 80 columns of 250 µm pitch and 336 rows of 50 µm pitch. Each FE-I4B cell is bonded using Sn/Ag bumps to a corresponding cell of the planar tile;

- A 3D module consists of a 3D sensor tile connected to a single FE-I4B chip with each cell of the FE-I4B chip bonded to a corresponding cell of the 3D tile;

- A double-sided, flexible printed circuit (the module flex hybrid) connects the module to external electrical services.

The sensor design, production and yield is discussed in section 3.1. This is followed by a discussion of the FE-I4B production and yield in section 3.2. The module hybridisation, that is the bump-bonding of the FE-I4B chip(s) and a wafer to produce a bare module, is made industrially. A module flex hybrid is then attached at module production sites to the bare module, prior to detailed performance studies of the final (dressed) module. The module hybridisation, the module flex hybrid connectivity and the final performance are described in sections 3.3 and 3.4. Finally, the overall module production yield is summarised in section 3.5.

#### 3.1 Sensors

Two sensor technologies are used for IBL modules. The planar sensor is a development of the Pixel detector sensor design, with several improvements. Most notably, since the limited IBL clearance precludes sensor shingling along the staves (as in the Pixel detector), the inactive sensor edges are substantially reduced to minimise efficiency losses. The 3D sensor design [22] is a new technology developed for increased radiation hardness, and relies on columnar electrodes penetrating the substrate, reducing the drift path with respect to the planar approach while keeping a similar thickness and thus signal size. As discussed in detail in reference [9], both sensor types show satisfactory test-beam performance in terms of noise, hit efficiency and hit uniformity for a fluence of up to  $5 \times 10^{15} \, n_{eq}/cm^2$ . An effective inactive edge width of 215 µm (175 µm) was measured for planar (3D) sensors.

The planar n<sup>+</sup>-in-n sensors have proven their excellent performance during the Run 1 operation of the Pixel detector and are a well-developed technology. Nevertheless, the 3D sensors have a potentially important advantage in terms of power consumption after high radiation because of their lower operating voltage.

Double-chip planar sensor modules cover the central region of the detector, 75 % of the active area, while the high  $\eta$  regions are populated by single-chip 3D sensor modules. This mitigates the reduced efficiency measured for normal incidence in the region of the 3D sensor electrodes.

#### 3.1.1 Planar design

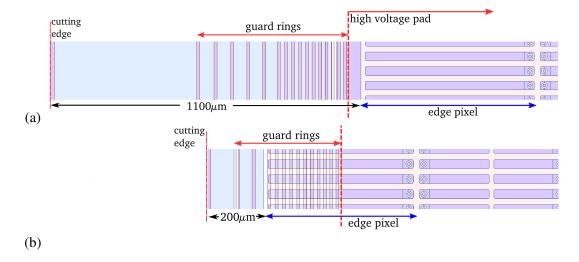

The design of the planar IBL sensor is an evolution of the Pixel detector sensor [4] with n<sup>+</sup>-in-n pixels. The n-side segmentation matches in size the FE-I4B read-out electronics connected via bump-bonds; a guard-ring structure is placed on the p-side. The planar IBL double-chip sensors are produced at CiS,<sup>4</sup> using n-type wafers of 100 mm diameter and 200 µm thickness, with resistivity in the range  $2 - 5 \text{ k}\Omega \text{ cm}$  and a <111> crystal orientation. Each wafer contains four sensor tiles of mean dimension 41 315 µm × 18 585 µm after dicing. Details of the sensor design can be found in reference [23]. Key features include slim edges achieved by stretching the edge pixel size opposite to the guard-rings to 500 µm, possible in n<sup>+</sup>-in-n sensors because of the double-sided process; this option was implemented after extensive studies of the sensor efficiency in the peripheral area [24]. The number of guard-rings was optimised based on a complementary study, which evaluated the breakdown behaviour after partial guard-ring removal [25]. Compared to the Pixel detector sensor, the number of guard-rings has been reduced from 16 to 13 and the cutting edge has been moved

<sup>&</sup>lt;sup>4</sup>CiS Forschungsinstitut für Mikrosensorik und Photovoltaik GmbH, Erfurt (Germany).

closer to them, as indicated in figure 8 where the overall reduction of the inactive edge (from 1100 to  $200 \,\mu$ m) is shown.

**Figure 8.** Comparison of the edge designs of (a) the ATLAS Pixel detector sensor and (b) the planar IBL pixel sensor. The inactive edge has been reduced from 1100 to 200  $\mu$ m. Blue shades represent the n-implantation on the front-side of the sensor. Purple shades represent the blue n-implantation on the front-side of the sensor superimposed with red shading for the p-implantation on the back-side. The HV backplane area is metalised and is indicated by a dashed red line and arrow.

The nominal pixel size is  $250 \,\mu\text{m}$  by  $50 \,\mu\text{m}$  pitch, matched to that of the FE-I4B chip. The two central columns of these double-chip sensors are extended to  $450 \,\mu\text{m}$  rather than  $250 \,\mu\text{m}$  to cover the gap between the two adjacent FE-I4B chips.

#### 3.1.2 3D design

In 3D pixel sensors, the columnar electrodes penetrate the substrate instead of being implanted on the wafer surface. The depletion electric field is therefore parallel to the wafer surface. The position and doping of the  $\sim 10 \,\mu$ m wide columns define the pixel configuration; the distance between electrodes can be typically fives times smaller than the  $\sim 230 \,\mu$ m sensor thickness, thereby dramatically reducing the charge-collection distance and depletion voltage. Although the fabrication process of 3D sensors is more complex, significant advantages can potentially be realised by independently controlling the drift distance and the sensor thickness. Because of the low depletion voltage, the power dissipation per unit leakage current is reduced. The cooling requirements are therefore less demanding. The signal size is determined by the sensor thickness, independently of the small drift distance. Furthermore, the drift perpendicular to the track direction results in fast signals, which are robust against charge trapping caused by heavy radiation damage [22].

The IBL 3D sensors were fabricated at FBK<sup>5</sup> and CNM<sup>6</sup> with a double-sided technology [26, 27]. Starting from p-type Float Zone wafers of 100 mm diameter and 230  $\mu$ m thickness, with high-resistivity (10 to 30 k $\Omega$  cm) crystalline silicon and <100> orientation, columnar electrodes of 12  $\mu$ m

<sup>&</sup>lt;sup>5</sup>Fondazione Bruno Kessler, Povo di Trento (Italy).

<sup>&</sup>lt;sup>6</sup>Centro Nacional de Microelectronica, Barcelona (Spain).

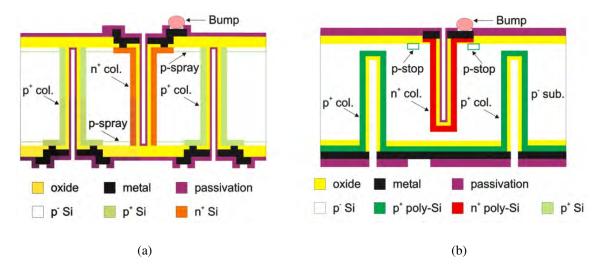

diameter were obtained by Deep Reactive Ion Etching (DRIE) and dopant diffusion from both wafer sides, without the presence of supporting wafers. By doing so, the substrate bias can be applied from the back side  $(p^+)$ , as in planar devices. Figure 9 shows details of the 3D column layout.

Figure 9. Design of the columns of (a) FBK and (b) CNM 3D sensors. This sketch is for illustration only and is not to scale.

Each pixel contains two read-out (n<sup>+</sup>) columns (two-electrode configuration), with an interelectrode spacing between n<sup>+</sup> and p<sup>+</sup> columns of  $\approx 67 \,\mu\text{m}$ . In order to maintain a reasonable yield, each wafer contains eight sensor tiles of dimension 20.4 mm  $\times$  18.7 mm, rather than the four larger sensor tiles of the planar design. A 200  $\mu$ m wide region separates the active pixel area from the physical edge of the tile.

The main differences between FBK and CNM 3D sensors are the following:

- FBK sensors have pass-through columnar electrodes [28]; in CNM sensors, on the other hand, electrode etching is stopped ~20 μm before reaching the opposite side [29];

- in FBK sensors, the surface isolation between n<sup>+</sup> electrodes is obtained by a p-spray layer on both wafer sides, whereas in CNM sensors, p-stops are used on the front side (n<sup>+</sup>) only;

- the edge isolation in FBK sensors is based on multiple rows of ohmic columns stopping the lateral spread of the depletion region [30], whereas in CNM sensors a 3D guard-ring, surrounded by a double row of ohmic columns, is used to sink the edge leakage current.

Table 5 summarises the main parameters of the IBL sensors.

#### 3.1.3 Sensor production and quality assessment

The electrical quality of the sensors was evaluated from the measurement of the current-voltage (I-V) dependence, as this is sensitive to bulk and surface defects. Tiles satisfying the selection criteria described below were chosen for hybridisation (connection between the sensor and the FE-I4B read-out electronics).

| Parameter                                                                  | Planar          | 3D FBK               | 3D CNM                |

|----------------------------------------------------------------------------|-----------------|----------------------|-----------------------|

| Tile dimension [µm <sup>2</sup> ]                                          | 41315 × 18585   | $20450 \times 18745$ | $20450 \times 18745$  |

| Sensor thickness [µm]                                                      | 200             | 230                  | 230                   |

| Sensor resistivity $[k\Omega cm]$                                          | 2 – 5           | 10 - 30              | 10 - 30               |

| Pixel size (normal) [µm <sup>2</sup> ]                                     | $250 \times 50$ | $250 \times 50$      | $250 \times 50$       |

| Pixel size (tile edge) [µm <sup>2</sup> ]                                  | $500 \times 50$ | $250 \times 50$      | $250 \times 50$       |

| Pixel size (tile middle) [µm <sup>2</sup> ]                                | $450 \times 50$ | —                    | —                     |

| Edge isolation                                                             | Guard-rings     | Fences               | 3D guard-ring, fences |

| Pixel isolation                                                            | p-spray         | p-spray              | p-stop on n-side      |

| Nominal operating bias voltage [V]                                         | -80 / -1000     | -20 / -160           | -20 / -160            |

| (non-irradiated / $5 \times 10^{15}  n_{eq}/cm^2$ )                        |                 |                      |                       |

| Maximum operational power [mW cm <sup>-2</sup> ]                           | 90              | 15                   | 15                    |

| $(-15 ^{\circ}\text{C} \text{ and } 5 \times 10^{15}  n_{eq}/\text{cm}^2)$ |                 |                      |                       |

Table 5. Summary of the main design specifications for the planar and 3D sensors of the IBL detector.

The planar design includes a grid structure that allows biasing of the entire sensor by means of a punch-through technique [31]. This bias grid was used to evaluate the quality of the tiles before the sensors were connected to the read-out electronics with the bump-bonding process. After bump-bonding the pixels were biased through the FE-I4B chip while the bias grid, connected to ground via a special bump in the periphery of the pixelated region, was not in operation.

The leakage current of the planar tile, evaluated at an operating voltage  $(V_{op})$  30 V below the depletion voltage  $(V_{dp})$ , was required to be  $I(V_{op}) < 1 \mu A$ , and the slope of the I-V curve was limited to  $I(V_{dp} - 30 \text{ V})/I(V_{dp}) < 1.6$ . Wafers with two or more planar tiles that satisfied this requirement were sent for under-bump metallisation (UBM) and dicing at IZM.<sup>7</sup> The yield of the planar production (the percentage of planar tiles satisfying the above criteria) before under-bump metallisation and dicing was 90.6 %.

Due to the difficulty of implementing a bias grid structure compatible with the 3D design, alternative evaluation methods were developed for 3D sensors:

- FBK sensors include a metal grid connecting all pixels in each column to a pad located in the periphery of the active region. By measuring the I-V curves of the 80 columns with a specially designed probe card, the quality of each sensor on the wafer can be evaluated. The metal layer was removed by chemical etching after the I-V measurement and the wafers with three or more selected tiles were sent to IZM for UBM and dicing. The sensors that passed the selection criteria were bump-bonded to read-out chips. The sensors were required to have a breakdown voltage  $V_{bd} < -25 \text{ V}$ ,  $V_{dp} > -15 \text{ V}$  and  $I(V_{op}) < 2 \mu\text{A}$  where  $V_{op} = V_{dp} - 10 \text{ V}$ . The slope of the I-V curve was also constrained to satisfy  $I(V_{op})/I(V_{dp} + 5 \text{ V}) < 2$ . The sensor yield of the FBK production on the selected wafers was 57 %.

<sup>&</sup>lt;sup>7</sup>Fraunhofer IZM, Gustav-Meyer-Allee 25, 13355 Berlin, Germany.

- The CNM sensor selection criteria were initially based on the leakage current measured through the 3D guard ring structure surrounding the pixelated area. While the p-side of the wafer was biased, the 3D guard ring was connected to ground via a dedicated pad, and the I-V curve was measured for each sensor before the wafer dicing. After hybridization, the 3D guard ring was connected to ground through two special bumps of the FE-I4B chip. The CNM sensors were required to satisfy  $V_{bd} < -25 \text{ V}$ ,  $V_{dp} > -15 \text{ V}$  and  $I_{GR}(V_{op}) < 200 \text{ nA}$  with  $V_{op} = V_{dp} - 10 \text{ V}$ . I<sub>GR</sub> is the leakage current measured on the 3D guard ring. The slope of the I-V curve was required to satisfy  $I(V_{op})/I(V_{dp} + 5 V) < 2$ . Wafers with at least three sensors passing the selection criteria were sent to IZM for UBM and dicing. Initial studies indicated a good correlation between  $V_{bd}$  measured through the 3D guard ring structure and that after detector assembly [9]. However, during module assembly, the correlation proved to be poor, with several CNM 3D modules showing a low V<sub>bd</sub>. This was because of defects located in the central volume of the sensor that do not affect the region probed by the 3D guard ring.Once this lack of correlation was established, all CNM sensors that were not assembled were retested on a probe station. The n-side of the sensor was placed in contact with a grounded chuck via the under-bump metallisation (section 3.3.1), while the p-side was connected to the bias potential. Those sensors satisfying  $V_{bd} < -25$  V were selected for hybridisation. The sensor yield of the CNM production on the selected wafers, as measured with the 3D guard ring method, was 72 %. However, after re-testing, the final CNM production yield was similar to that for FBK wafers.

The typical sensor I-V behaviour of prototype sensors was previously detailed before and after radiation [9, 23]. Typical I-V curves for each sensor type are shown after module assembly in section 3.4.1.

#### 3.2 On-detector electronics

#### 3.2.1 The FE-I4 front-end chip

The FE-I4B front-end chip was developed for the IBL read-out. A first version, the FE-I4A [8, 32], was fabricated in 2010 and used to develop and validate the IBL module design [9]. The FE-I4A was not intended for the final detector and the pixel matrix was non-uniform to allow performance comparisons between various analog circuit design choices. The FE-I4B chip was first fabricated in 2011 [33, 34] and tailored to fully meet the IBL requirements. In addition to selecting the analog design and making the pixel matrix uniform, specific powering choices were made and data acquisition features added.

The FE-I4A and FE-I4B both contain read-out circuitry for 26 880 hybrid pixels arranged in 80 columns of 250 µm pitch by 336 rows of 50 µm pitch. Each FE-I4 pixel contains a free running clock-based amplification stage with adjustable shaping, followed by a discriminator with an independently adjustable threshold. The chip keeps track of the time stamp for each discriminator as well as the 4-bit Time over Threshold (ToT).<sup>8</sup> Information from all firing discriminators is kept in the chip for a latency interval programmable up to 255 LHC clock cycles of 25 ns, and is retrieved if a trigger is supplied within this latency. The IBL data output is a serial Low Voltage Differential

<sup>&</sup>lt;sup>8</sup>The Time over Threshold is defined as the time the amplifier output signal stays above threshold, measured in units of the LHC clock (25 ns). This quantity is related to the collected charge.

Signal (LVDS), 8b/10b encoded at a rate of 160 MBit/s. The chip has many configurable settings that are stored in triple-redundant registers providing the required radiation hardness to single event upsets (SEU) [35].

Because of space and material limitations, the IBL FE-I4B chips are powered from a single DC supply over long cables providing a resistive load. The single voltage feeds two Shunt-LDO<sup>9</sup> voltage regulators [36, 37] drawing a minimum standing current of 270 mA even when the chip is neither clocked nor configured. This limits the amplitude of voltage transients resulting from current changes on the resistive supply lines, particularly important since the difference between the nominal and maximum input voltage ratings is small. The regulators and attendant voltage references have an input voltage limit of 2.5 V, compared with nominal operation at 1.8 V. Once the chips are configured and clocked, and their internal current draw exceeds 270 mA, the regulator shunt elements shut off and draw no additional current. The chip operates internally with two voltage rails generated by the regulators, nominally 1.4 V for the analog circuitry and 1.2 V for the digital circuitry. Both voltages are adjustable with a hard-wired maximum around 1.5 V (which varies slightly from chip to chip). The voltage references use a combination of a programmable current reference (feeding a poly-silicon resistor) and a fixed voltage reference. This combination was chosen to allow reliable start-up at low temperature (as low as -40 °C), as well as excellent stability (<  $\pm 2$  %) up to high radiation dose (250 MRad).

Several features important for IBL operation were introduced in the FE-I4B design following experience with prototype FE-I4A modules. Some details of the analog bias distribution and charge injection were changed to correct for degradations observed in the FE-I4A after the expected IBL lifetime dose, particularly at low temperatures. A programmable event-size limit was introduced to avoid data acquisition time-outs from occasional pathologically large events. Bunch crossing and trigger counters were increased to respectively 13 and 12 bits, to avoid ambiguities in tracking the state of each chip. Improved diagnostics were implemented to count and report any skipped triggers (the chip will skip any triggers received when the 16-bit trigger buffer is full).

#### 3.2.2 FE-I4B production and quality assessment

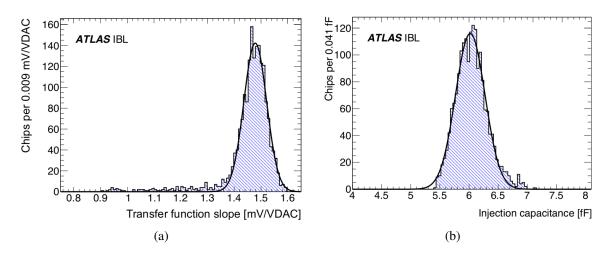

For the IBL production, 3060 FE-I4B chips on fifty-one 200 mm diameter wafers were tested. The data acquisition and handling were performed with a custom read-out system [4, 38]. A custom PCB was used to interface the read-out system hardware with a probe card, establishing electrical contact with 108 FE-I4B pads. All 60 chips of a wafer were probed with an average measurement time of 2.5 days. The goal was to identify FE-I4B chips that were suitable for the IBL and to measure their calibration constants. For chip calibrations it was necessary to make contact with dedicated FE-I4B pads not wire-bonded on the IBL read-out circuit. The chip calibrations were therefore only possible at wafer level. Two calibration constants of the internal charge injection circuit are shown in figure 10. The circuit distributes a voltage step to injection capacitors present in each pixel and is needed to tune the FE-I4B chips during IBL operation. On average for the accepted chips, the injected charge changes with the value (VDAC) of the injection circuit digital-to-analog converter (DAC) setting approximately as

$$\frac{\Delta Q}{\text{VDAC}} = 6.05 \text{ fF} \cdot 1.45 \frac{\text{mV}}{\text{VDAC}} = 55 \frac{\text{e}}{\text{VDAC}}$$

to provide a transfer function between the value of the DAC setting and the signal.

<sup>&</sup>lt;sup>9</sup>A shunt combined with a Low-Drop-Out regulator.

**Figure 10.** Calibration constants of the internal charge injection circuit for accepted FE-I4B chips. The circuit distributes a voltage step to injection capacitors on board each pixel. The superimposed curves are Gaussian fits. (a) The slope of the transfer function between the signal voltage and the value VDAC of the DAC setting. (b) The measured injection capacitance.

More than 50 tests were used to evaluate the chip response to charge injection, the functionality of digital hit processing, the chip configurability, and the power consumption. Approximately 18000 values were recorded per wafer. A custom made software designed for wafer and module tests of the IBL production was used to automatically determine the chip status. The selection criteria were defined after the distributions of the first ten wafers were studied. A detailed description of the tests and selection criteria is available elsewhere [39].

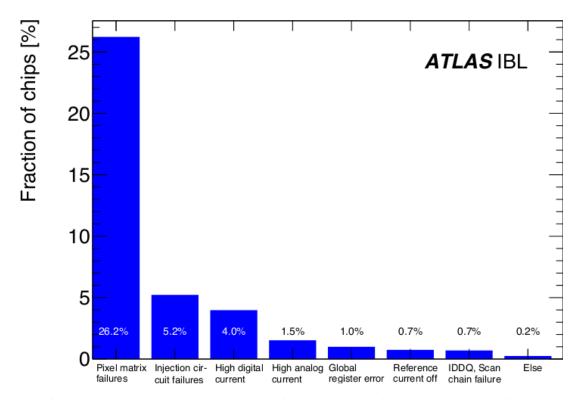

Test results of 2814 fully probed chips are listed in figure 11. In addition, 246 chips (8 % of all chips) were not fully probed because of an anomalous high current at start-up (dead-shorts). Additional IDDQ,<sup>10</sup> Scan chain and Shmoo plot<sup>11</sup> tests were made by an external company for the first ~20 wafers, but the failure rate was low (less than 0.5 %). In total, 1821 chips (59.5 %) were qualified for IBL module assembly.

Since the powering scheme was not finalised at the time of wafer testing, the on-chip power regulators of the FE-I4B chips were only tested after the module assembly (section 3.4).

#### 3.3 Module assembly

#### 3.3.1 Hybridisation of the FE-I4B chip and the sensor

The connection between sensor and electronics was achieved using fine-pitch bump-bonding and flip-chip technology. This was already used with a 50 µm pitch for the construction of the Pixel detector modules [4]. The IBL modules use a similar electroplated (SnAg) bumping process provided by IZM. The bumping process is divided into three steps: under-bump metallisation (UBM) on the sensor and FE-I4B wafers; solder bump deposition on the FE-I4B wafers; and a flip-chip of the diced FE-I4B chips and sensors. The UBM is necessary due to the non-solderable aluminium pads on the sensors and FE-I4B chips; the UBM metal stack consists of electro-deposited Cu on top of a sputtered Ti/W adhesion layer. Solder bumps are then deposited on the FE-I4B

<sup>&</sup>lt;sup>10</sup>Measurement of the supply current (Idd) in the quiescent state.

<sup>&</sup>lt;sup>11</sup>A plot showing the range of conditions (voltages, temperatures and inputs) in which the chip operates.

**Figure 11.** Failure modes leading to a rejection of FE-I4B chips before module assembly for 2814 fully probed chips. The bin *Pixel matrix failures* groups chips where the number of bad pixels were too high (>0.2% failing pixels or >20 pixels per column). The bin *Injection circuit failures* groups failures (e.g. low maximum voltage, a non-configurable injection delay) that prevent using the charge injection for calibration during IBL operation. The bins *High analog/digital current* combine current measurements in different chip states (un-configured, high digital activity). The remaining bins list the rate for chips failing the global register tests, the reference current generation tests and the Scan chain tests, respectively. All failure modes that are not explicitly mentioned contribute only 0.2% and are included in the bin *Else* The failures are non-exclusive and are evaluated as a percentage of the probed chips.

wafers using electroplating only. The flip-chip operation follows the dicing of the sensor wafers. The FE-I4B chip is placed on the sensor substrate with high accuracy and the assembly is soldered to form the electrical and mechanical interconnection in a reflow soldering process. The sensor bonded to the FE-I4B chip(s) is commonly referred to as a bare module.

The procedure was modified with respect to that for Pixel detector modules, to suit the dimensions of the IBL module components. The FE-I4B chip covers an area of  $20.27 \times 19.20 \text{ mm}^2$  and was thinned to  $150 \,\mu\text{m}$  before bump-bonding. Unconstrained, the thinned FE-I4B would undergo a distortion exceeding 40  $\mu\text{m}$  during the high temperature reflow soldering phase, which would result in unconnected bumps especially in the outer areas of the assemblies. To avoid this, a temporary 500  $\mu\text{m}$ -thick sapphire glass handle wafer was bonded to the FE-I4B chip before UBM. A polyimide bonding technique allowed a laser-induced debonding of the glass carrier at room temperature after dicing and flip-chipping. This debonding process used an UV excimer laser with a wavelength of 248 nm traversing the glass carrier to the bonding interface. The glass carrier was optimised to ensure that the laser light was fully absorbed in the polyimide bonding layer, thus releasing the FE-I4B chips.

Only 2 mm of the chip length is dedicated to End-of-Column (EoC) logic outside the active pixel matrix. The size is determined by the need to wire bond the I/O and power pads to the read-out chip with the bump bonded sensor in place. The chip-level logic and global configuration occupy less than 20% of the periphery. Once bonded, most of the EoC part extends beyond the sensor area so that the wire bonding pads at the output of the EoC logic are still accessible to connect the read-out chip via aluminium-wire wedge bonding.

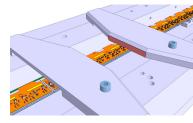

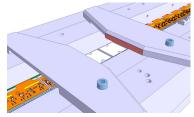

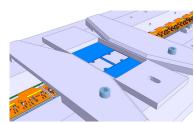

#### 3.3.2 Module flex hybrid

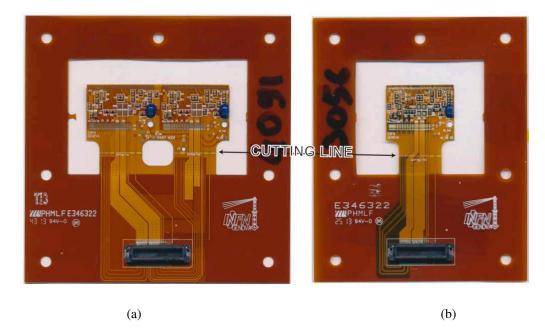

The module flex hybrid is a double-sided, flexible printed circuit board which routes the signal and power lines between the stave flex hybrid and the FE-I4B chips, holds the required passive components, and routes the bias voltage to the sensor via Cu traces. Figure 12 shows a photograph of the module flex hybrids for single-chip and double-chip modules. The envelope of the module flex hybrid is defined by the sensor dimensions and it is slightly narrower than the sensor width.

**Figure 12.** Photographs of (a) a double-chip and (b) a single-chip module flex hybrid. The frame and flex extensions allow testing of the module before stave loading. The hybrid cutting line (see text) is visible as a white trace slightly outside the module envelope.

The module flex hybrids are glued to the back side of the sensor and connected to the longitudinal stave flex, which is located at the back side of the stave, via thin transversal wings, one per read-out chip (section 4.2). The 130 µm-thick flex stack consists of two 18 µm-thick copper layers embedded in dielectric polyimide sheets, glued with acrylic adhesive. Passive components are soldered on the module flex hybrid for the FE-I4B chip decoupling, power supply and HV filtering, and for terminations of the signal traces. The module temperature monitoring and interlock is made via a Negative Temperature Coefficient thermistor (NTC) mounted on the module flex hybrid. All passive components are soldered on the top layer of the module flex hybrid. Special emphasis is given to HV routing and filtering since the flex hybrid must be functional up to 1000 V. To avoid

HV discharges, wider spacing between the HV traces and the data and LV traces is introduced. The HV capacitor is encapsulated with a polyurethane resin and  $27 \,\mu\text{m}$  thick Kapton<sup>® 12</sup> cover layers are used on the top and bottom of the flex hybrid.

All signal and power traces of the module flex hybrid are routed to a connector on a frame outside the module area that is used during the module production QA. A temporary wire bond connection is necessary to connect all signal and power lines from the flex to the connector on the frame. Prior to the loading of the module to a stave the connector area is cut away. The cutting line is approximately 1.5 mm from the sensor.

The module flex hybrids were produced by Phoenix S.r.l.<sup>13</sup> and the surface mount component loading and encapsulation was made by Mipot S.p.A.<sup>14</sup> Basic QA operations such as testing of line integrity for open and shorted connections were made by the vendors and were followed by more detailed tests at the two module assembly sites. These procedures included HV standoff tests at 1.5 kV, visual inspection and dedicated cleaning to allow for high-quality wire bonding.

#### 3.3.3 Final module assembly

The final (dressed) module assembly was made at two module production sites in the period 2012 to 2014, following four assembly steps described below.

A detailed visual inspection of the module flex hybrid was initially made, together with electrical tests of the line and pad integrity, and the hybrid components. To ensure a good wire bonding performance, the flex hybrid was then cleaned in an ultrasonic bath, rinsed with distilled water, and dried. The visual inspection was then repeated.

A visual inspection of the bare module was made to identify scratches or other damage. For planar double-chip modules a re-measurement of the I-V was made to check the sensor quality. Thirteen planar modules (3.2%) and eight 3D modules (2.9%) were rejected.

The key assembly step is the alignment and attachment of the bare module and the module flex hybrid. The module flex is glued on the sensor back-side. For this reason, it is necessary to visually access the sensor alignment marks, and to be able to wire-bond to both the FE-I4 chip and the flex wings. An alignment precision of order 100 µm is required. The alignment and gluing procedure differed slightly between the production sites, and the detailed jig designs were developed autonomously. Separate alignment jigs were developed for the planar double-chip and 3D single-chip modules. Several jig sets were made to ensure production capacity, but the module assembly rate was in fact determined by the component supply. Both the module flex and the bare module were initially aligned on separate jigs using alignment marks, and fixed in place via vacuum. The module flex was then removed with a special jig, maintaining the alignment position but allowing access for the deposition of glue. The jig was designed to protect the hybrid components. Glue patterns were then deposited on the flex hybrid: a double tape strip (PPI RD-577F<sup>15</sup> or ARclad<sup>16</sup>) was placed

<sup>&</sup>lt;sup>12</sup>Kapton<sup>®</sup> is a Dupont Corp. trademark for polyimide films, see http://www.dupont.com.

<sup>&</sup>lt;sup>13</sup>Phoenix S.r.l., Via Burolo 22, 10015 Ivrea (Torino), Italy.

<sup>&</sup>lt;sup>14</sup>Mipot S.p.A., Via Corona 5, 34071 Cormons (Udine), Italy.

<sup>&</sup>lt;sup>15</sup>PPI RD-577F<sup>®</sup>, PPI Adhesive Products GmbH, see www.ppi-germany.de.

<sup>&</sup>lt;sup>16</sup>ARclad<sup>®</sup>, Adhesives Research Corp., see www.adhesivesresearch.com.

underneath the FE-I4B wire bond pads, and epoxy glue patterns (UHU EF 300<sup>17</sup> or Araldite 2011<sup>18</sup>) were placed under the remainder of the module flex hybrid, especially under the wire bond bridge area and the HV connection pads. The jigs were then aligned and brought into contact. Pressure was applied on the assembly, and in particular around the critical wire bond regions, during curing.

The final step was the wire bonding of the FE-I4B chip and sensor to the module flex hybrid and of the wire bond bridge to the test connector (section 3.3.2), using 25 µm-thick aluminium wire (at least three wire bonds were applied to the low- and high-voltage pads for redundancy and safety). Wire bond pull tests were consistently recorded to ensure the bond integrity.

At each stage of the assembly, details of the module components, as well as metrology and bonding information, were recorded. No site dependence of the module quality was identified.

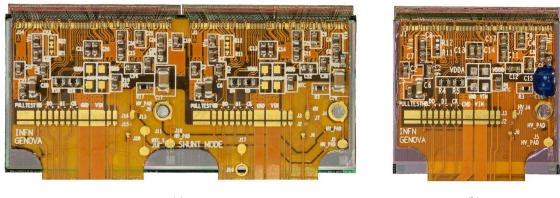

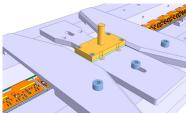

Fully dressed planar (double-chip) and 3D (single-chip) modules are shown in figure 13. Table 6 summarizes the material budget (units of radiation length for normal incidence) of the IBL modules; the contributions of the different components are averaged over the active module area.

A total of 688 fully dressed modules (410 planar, 162 3D CNM and 116 3D FBK) were delivered for module testing, tuning and characterisation.

(a)

(b)

**Figure 13.** Photographs of (a) an IBL planar module and (b) an IBL 3D module after the removal of the module handling frames. The HV encapsulation step is not yet made on the planar module.

#### 3.4 Module performance and quality assurance

Prior to the loading of modules onto a stave, each module was tested to ensure its mechanical and electrical functionality, its tolerance to environmental stress, and its electrical performance. The performance validation identified both module-level failures and pixel-level failures. Modules were selected for stave loading on the basis of this validation and only modules passing all tests were selected. At the pixel level, any pixel that failed at least one electrical test was recorded and modules with a bad pixel count of more than 1 % were rejected. The bad pixel category also included bad pixels resulting from nonconformities such as re-work, sensor scratches or the chipping of electronic components.

$<sup>^{17}\</sup>text{UHU}$  EF  $300^{\textcircled{R}}$  , UHU GmbH, see www.uhu.com.

<sup>&</sup>lt;sup>18</sup>Araldite<sup>®</sup> is a trademark of Huntsman Advanced Materials, see http://www.huntsman.com/advanced\_materials/a/ Home.

| <b>Table 6.</b> Material budget of the IBL module components in units of radiation length $(X/X_0)$ for normal |

|----------------------------------------------------------------------------------------------------------------|

| incidence. The contributions of the different components are averaged over the active module area. Sub-        |

| components are shown in a separate column.                                                                     |

|                          |                 | X/X <sub>0</sub> (%) |

|--------------------------|-----------------|----------------------|

| Total FE-I4B + bumps     |                 | 0.21                 |

| FE-I4B chip              | 0.20            |                      |

| Bump-bonds               | $\lesssim 0.01$ |                      |

| Planar (3D) sensor       |                 | 0.24 (0.27)          |

| Total module flex hybrid |                 | 0.13                 |

| Cu traces                | 0.076           |                      |

| Polyimide/epoxy          | 0.028           |                      |

| SMD components           | 0.025           |                      |

| Total planar (3D) module |                 | 0.58 (0.61)          |

An initial electrical verification, including the sequential room-temperature tests labelled Q in table 7, was performed after the module assembly. Modules accepted by this initial test were then subjected to an environmental stress test of 10 thermal cycles between -40 °C and 40 °C. The modules were not powered during the thermal cycles. Seventy-three modules (10.6 % of those delivered) were rejected at this stage because of major mechanical or electrical failure, a large fraction being due to a defective on-chip power regulator on the FE-I4B chips. As noted in section 3.2.2, the power regulators were not tested at the wafer level.

An extensive validation stage was then made for each module at both the module and individual pixel level. This included the sequential tests labelled F in table 7. The different measurements are described in sections 3.4.1 through 3.4.5.

A measurement of the sensor I-V was initially made at room temperature with a requirement on the breakdown voltage ( $V_{bd}$ ) depending on the module type. Modules failing the  $V_{bd}$  requirement were rejected. A detailed electrical calibration and characterisation was then made at the foreseen detector operation temperature of -15 °C. This included the module timing and threshold calibration and validations of the operational range (for example the low threshold operability). Finally, pixellevel failures, for example threshold tuning failures, bump-bond failures and noisy pixels, were identified and recorded. Forty-one modules (6 % of the delivered modules) were rejected following this detailed electronic validation. Accepted modules were ranked according to their quality, and as discussed in section 5.3, an additional penalty was applied to a module in case of mechanical rework or any other problems in the production and testing procedure.

#### 3.4.1 Module I-V characteristics

The leakage current was measured as a function of the sensor bias voltage (I-V characteristic) during both the initial room-temperature electrical test and the full performance test. The breakdown

| <b>Table 7.</b> Test flow of the initial electrical test after module assembly (Q) and the intense module functionality |

|-------------------------------------------------------------------------------------------------------------------------|

| and performance validation test (F). The tests labelled Q are made at room temperature.                                 |

| Test Name                               | Test Purpose                                     | Test stage |

|-----------------------------------------|--------------------------------------------------|------------|

| Sensor current vs. applied bias voltage | Sensor operability and                           | Q, F       |

|                                         | reference characteristics measurement            |            |

| Power-up test                           | Chip supply voltage and current test             | Q, F       |

| Shunt-LDO I/V scan                      | Shunt-LDO warm/cold calibration                  | Q, F       |

|                                         | and functionality test                           |            |

| Generic ADC test                        | Generic ADC warm/cold calibration and            | Q, F       |

|                                         | Shunt-LDO calibration verification               |            |

| Sensor bias ON                          | Ramp-up of sensor depletion bias                 | Q, F       |

| Digital test (high threshold)           | Pixel read-out chain functionality               | Q, F       |

| Module tuning                           | Multi-step threshold and feedback                | Q, F       |

|                                         | current adjustment (global and pixel level)      |            |

| Digital test (operation threshold)      | Pixel digital read-out chain functionality       | Q, F       |

| Analog test (operation threshold)       | Pixel analog read-out chain functionality        | Q, F       |

| Threshold and noise measurement         | Threshold and noise (ENC) measurement            | Q, F       |

| ToT verification at the charge          | Charge measurement verification                  | Q, F       |

| of 16 000 e <sup>-</sup> (MIP)          |                                                  |            |

| Crosstalk test                          | High analog charge injection                     | Q, F       |

|                                         | for inter-pixel crosstalk test                   |            |

| t <sub>0</sub> -tuning                  | Injection timing fine adjustment                 | F          |

| In-time threshold measurement           | Threshold for hit detection within               | F          |

|                                         | single bunch crossing measurement                |            |

| ToT calibration                         | Full range ToT to charge calibration             | F          |

| Noise occupancy measurement             | Noise hit probability at operation threshold     | F          |

|                                         | and noisy pixel masking                          |            |

| Source scan                             | <sup>241</sup> Am high statistics source scan    | F          |

|                                         | for bump connectivity test                       |            |

| Low threshold operability test          | Noise occupancy as function                      | F          |

|                                         | of threshold measurement                         |            |

| Sensor bias OFF                         | Ramp-down of sensor depletion bias               | Q, F       |

| Threshold and noise measurement         | Threshold and noise (ENC) measurement            | Q, F       |

|                                         | with undepleted sensor to detect defective bumps |            |

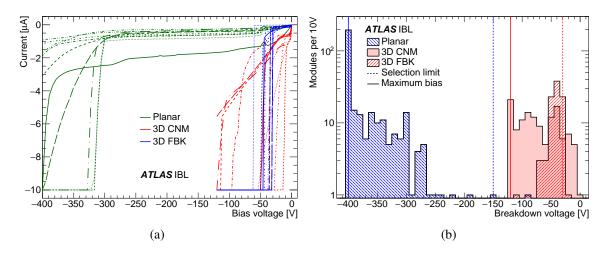

voltage (V<sub>bd</sub>) was used as an acceptance criterion for the modules. Example I-V curves for ten randomly chosen modules of each module type are shown in figure 14a. From these curves, V<sub>bd</sub> can be determined. The I-V behaviour was measured with the FE-I4B chip unpowered and at approximately 20 °C. A current limit of  $-10 \,\mu\text{A}$  was used to protect the modules.

**Figure 14.** (a) The I-V characteristics of ten randomly chosen modules of each sensor type. The I-V curves were measured at approximately 20 °C and a current limit of  $-10 \,\mu$ A was used to protect the modules. The FE-I4B chips were not powered. (b) The breakdown voltage (V<sub>bd</sub>) distributions of the tested IBL modules (313 planar, 128 3D CNM and 93 3D FBK modules). The solid vertical lines indicate the maximum measurement point of  $-400 \,\text{V}$  for the planar modules and  $-120 \,\text{V}$  for the 3D CNM and FBK modules. The V<sub>bd</sub> acceptance criteria of below  $-150 \,\text{V}$  (blue) for the planar modules and below  $-30 \,\text{V}$  (red) for 3D modules are also indicated as dashed lines.

As shown in figure 14b,  $V_{bd}$  depends on the module type. The  $V_{bd}$  of planar modules was required to be less than -150 V, 70 V below the nominal bias voltage,  $V_{op} = -80 \text{ V}$ . Only four of the dressed planar modules failed the sensor breakdown voltage criterion. The  $V_{op}$  of the FBK and CNM modules is -20 V, and for this reason all 3D modules having a  $V_{bd}$  above -30 V at the final performance test were rejected. As already noted (section 3.1.3), the sensor test procedure at wafer level was significantly different for the CNM and the FBK modules. For the 3D FBK modules, only one module was rejected. However, for CNM modules, the correlation between  $V_{bd}$  at wafer level and for dressed modules was poor. For this reason, the wafer-level criteria were relaxed and 27 of the dressed CNM modules failed the  $V_{bd}$  requirement. Furthermore, in some cases, the early soft breakdown is thought to originate in the p-stop region around the n-columns. After radiation, the leakage current due to radiation damage in the silicon bulk dominates.

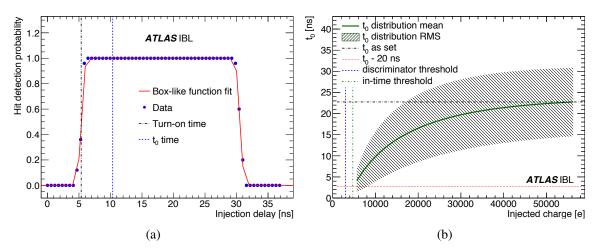

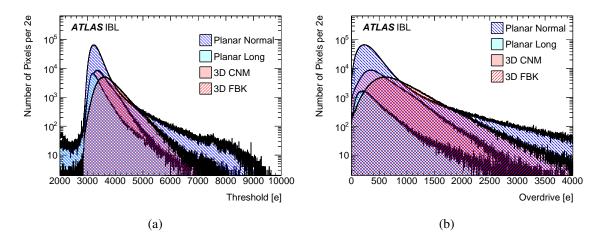

#### 3.4.2 Module time-walk and threshold tuning

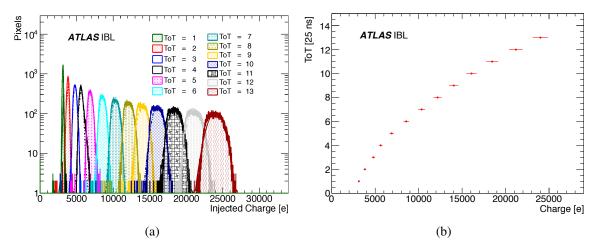

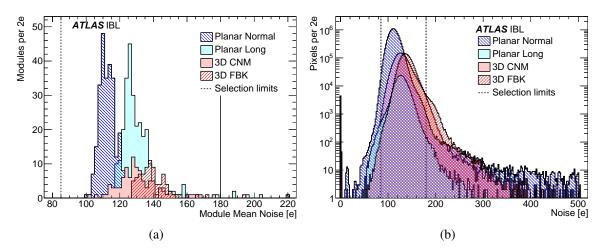

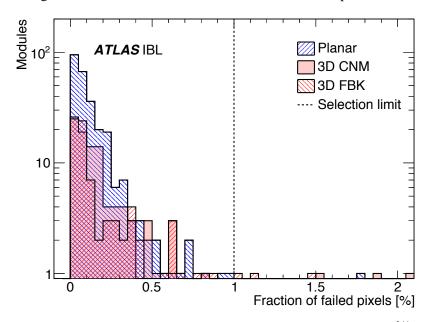

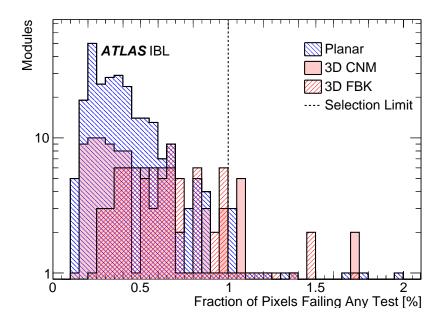

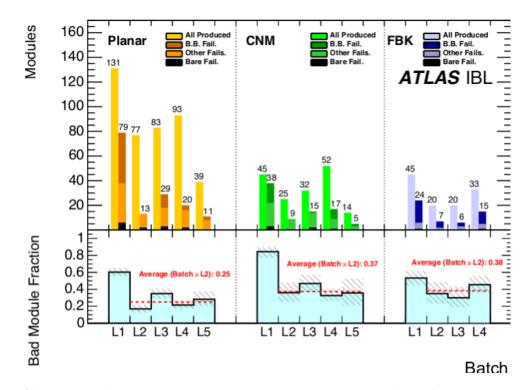

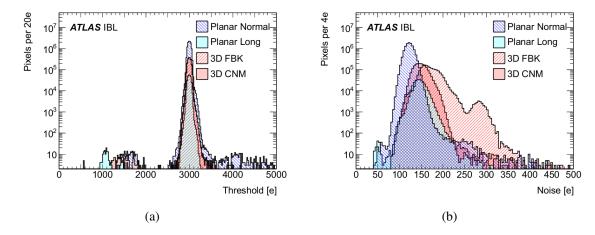

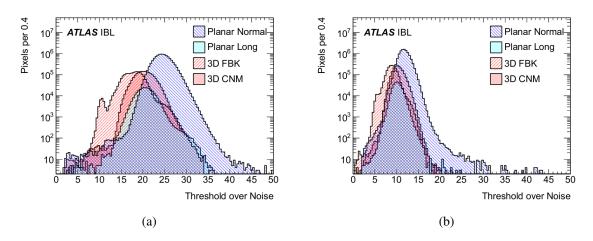

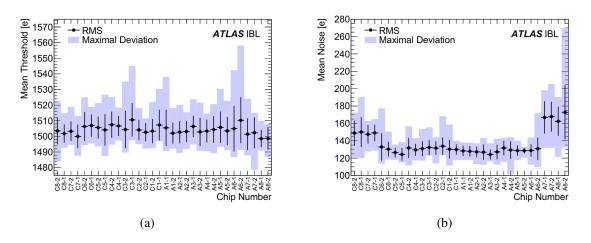

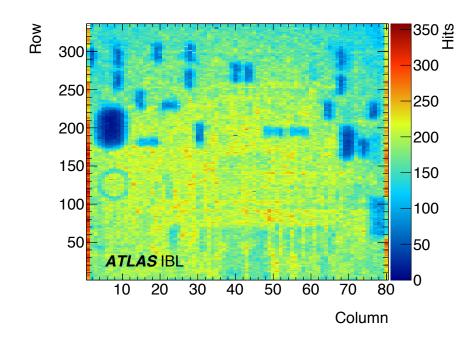

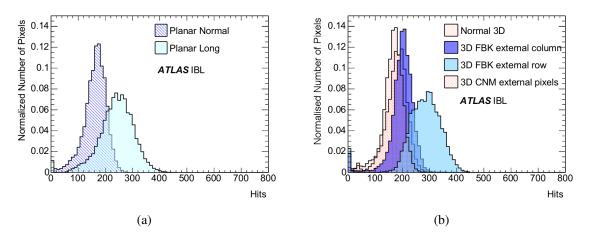

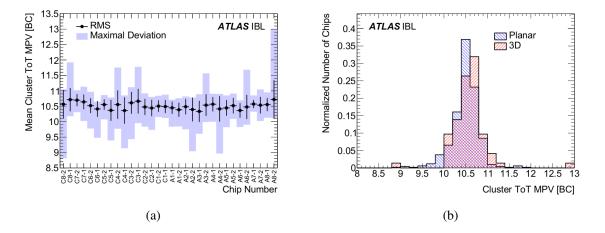

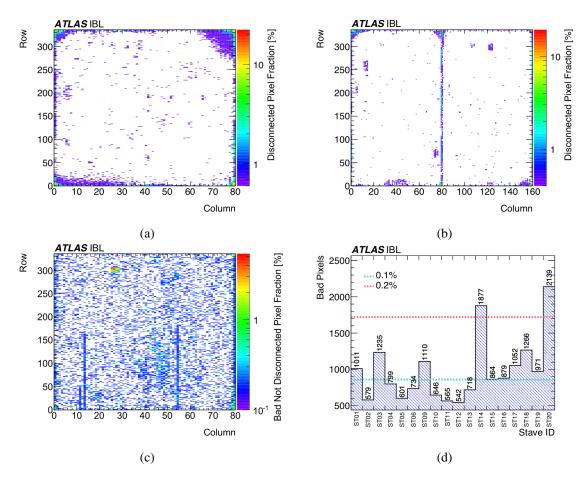

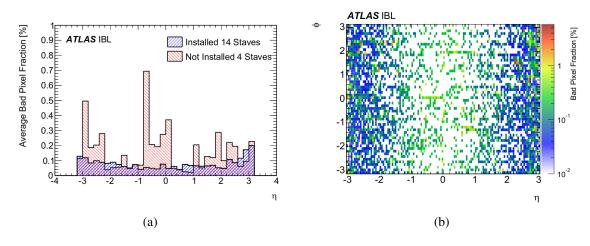

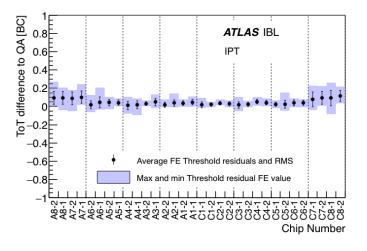

During detector operation, the IBL modules digitise the measured hits with respect to the master clock, which is synchronised to the LHC clock. Only hits that are recorded within one clock cycle, i.e. within a sensitive time of 25 ns, can be assigned to the correct bunch crossing of the LHC. The in-time hit detection probability is significantly influenced by the time-walk effect of the charge sensitive amplifier. Small signal charges at the input of the amplifier cross the discriminator threshold with some time delay with respect to a large reference charge and therefore the knowledge of this time-walk is important for the IBL operation.