#### FrontEnd LInk eXchange

#### FELIX: a PCIe based high-throughput approach for interfacing front-end and trigger electronics in the ATLAS upgrade framework

Kai Chen Brookhaven National Laboratory

On behalf of the ATLAS Collaboration

# Outline

- □ Introduction to the FrontEnd LInk eXchange (FELIX) system

- □ FELIX hardware

- □ FELIX firmware & software

- □ Integration test with Front-Ends

- □ Status & summary

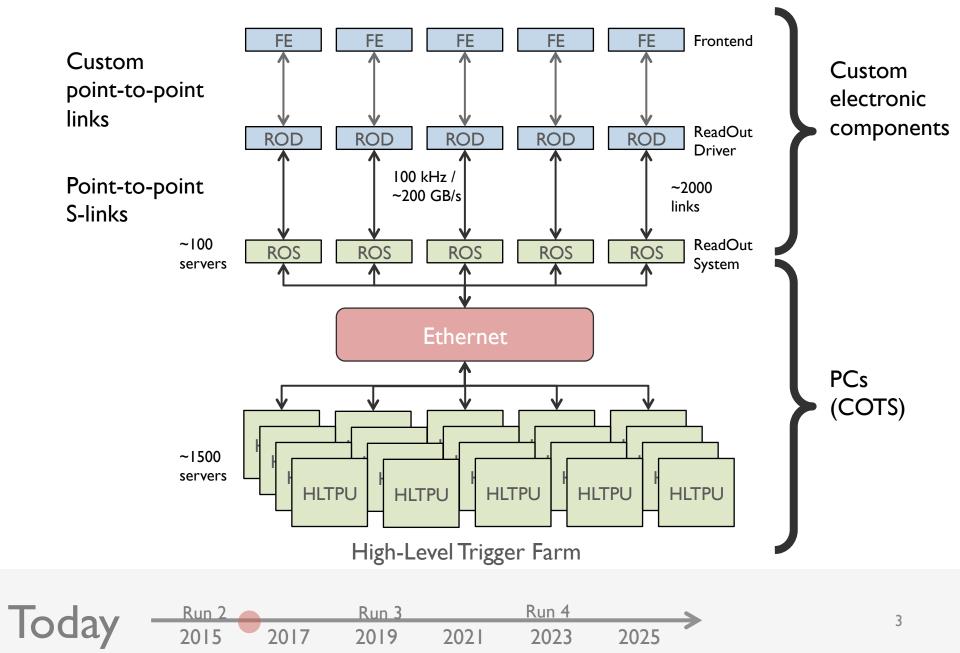

#### ATLAS DAQ Today

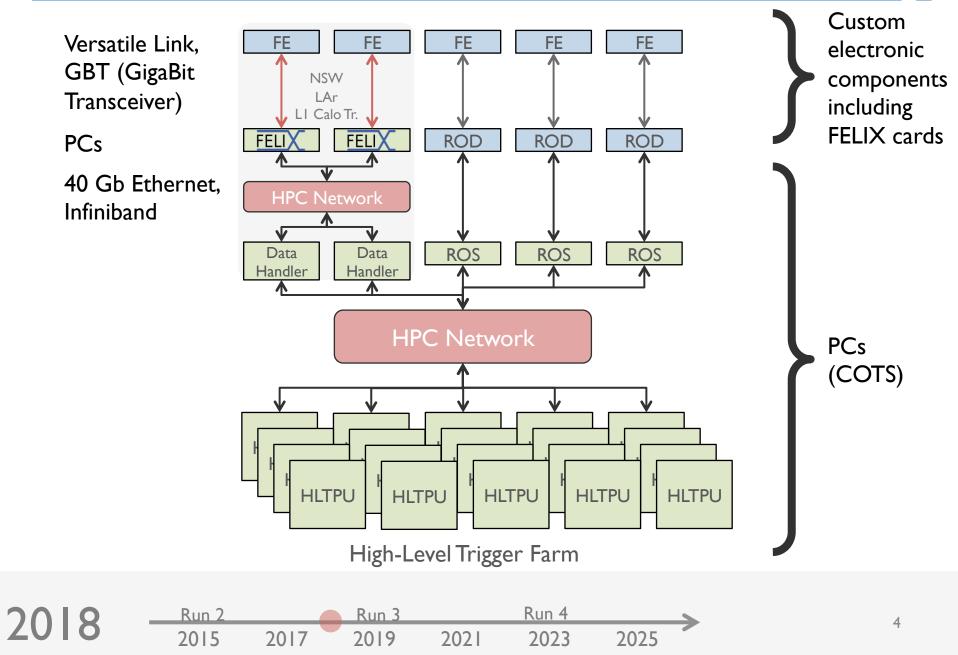

#### Upgrade for Phase-I

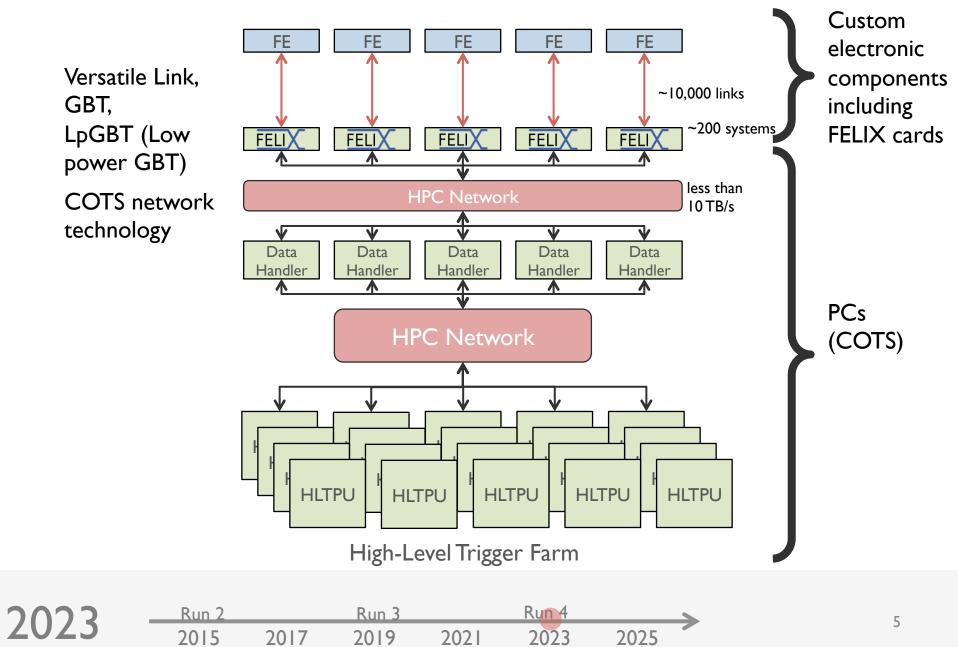

#### Upgrade for HL-LHC

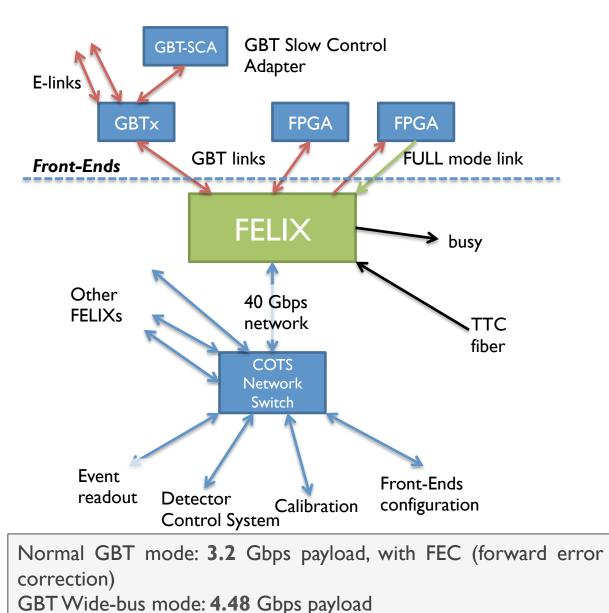

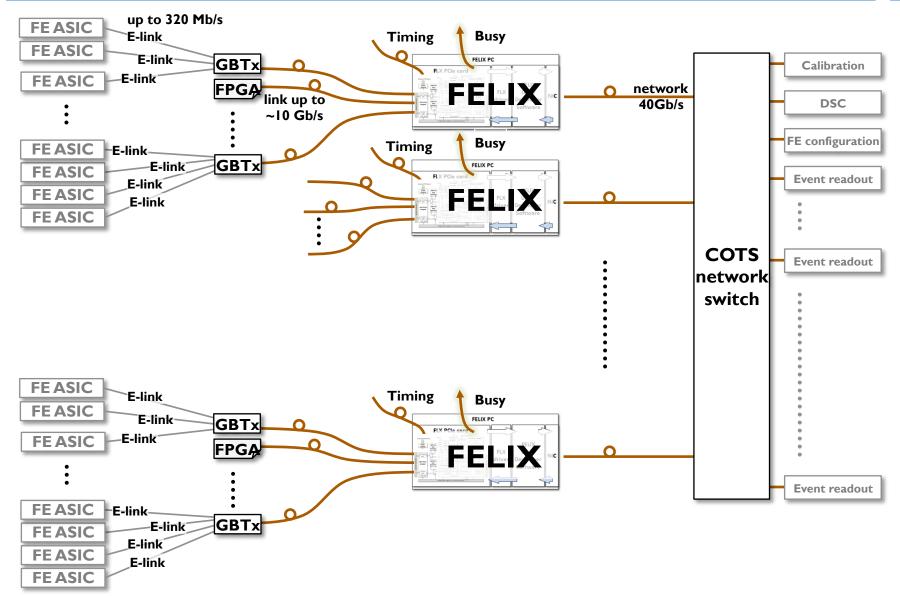

# FELIX functionality

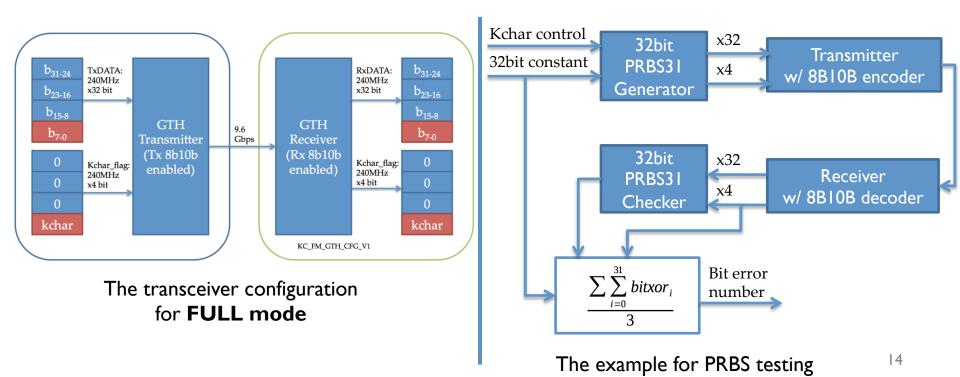

FULL mode: current plan is 9.6 Gbps link speed in 8B/10B

#### Scalable architecture

Routing of event data, detector control, configuration, calibration, monitoring

Connect the ATLAS detector Front-Ends to the DAQ system, for both the to and from FE directions

E-links configuration configurable

Detector independent

TTC (Timing, Trigger and Control) distribution is integrated

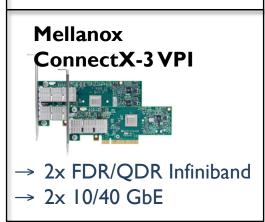

#### FELIX server PC components

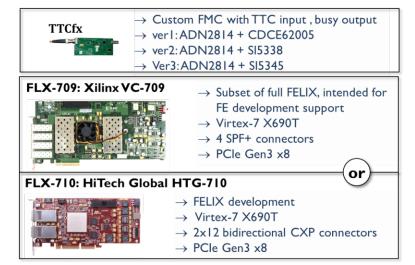

- → FELIX Phase-1 prototype

- → TTC input ADN2814 + SI5345

- → Xilinx Kintex **Ultrascale** XCKU115

- → 48 duplex optical links (based on MiniPODs)

- $\rightarrow$  PCIe Gen3 x16

#### SuperMicro X10SRA-F used for development

→ Broadwell CPU, e.g.

E5-1650V4, 3.6 GHz

→ PCle Gen3 slots

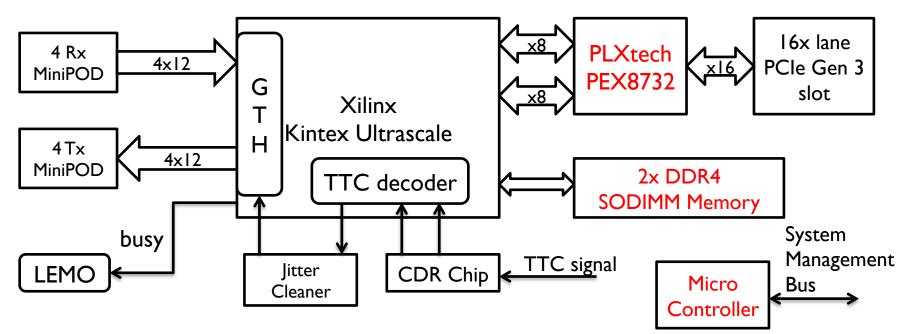

### Features of BNL-711

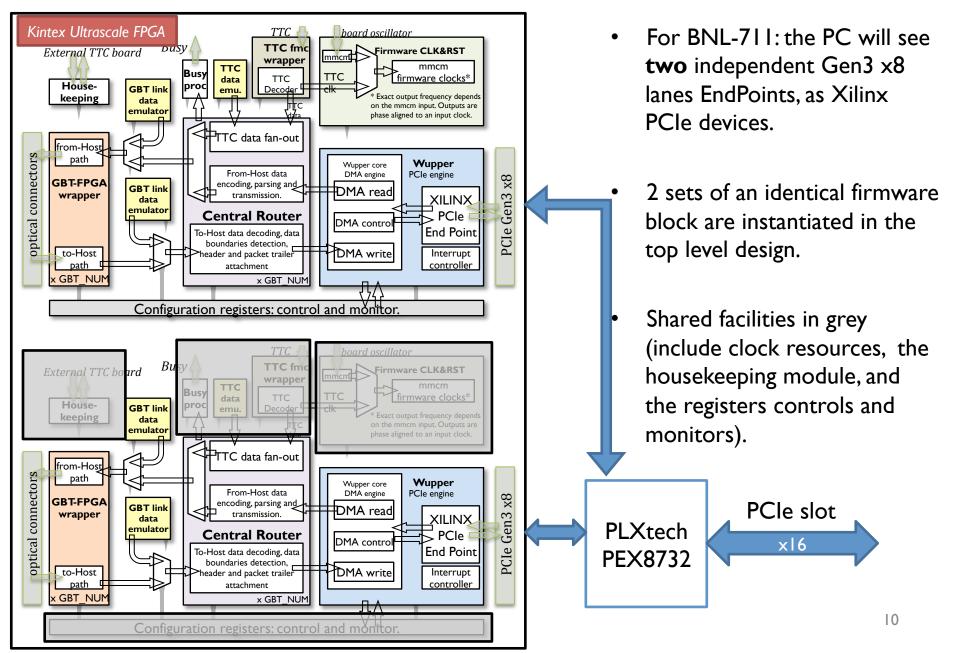

FELIX base line hardware platform: PCIe FPGA board gen3 x16, "BNL-711"

- Developed at BNL also as the DAQ platform for the LTDB (Liquid Argon Trigger Digitizer Board) production test platform

- PLXtech PEX8732 to handle PCIe Gen3 x16 lanes (max 128 Gbps) interface to host

- 48-ch MiniPOD TX & RX, up to 14Gb/s per link

- 2x SODIMM DDR4 interfaces (not used in FELIX)

- Integrated TTC interface, busy output, and on-board jitter cleaner

- Micro-Controller (Atmega 324A) for FPGA firmware update and version control

### Status of BNL-711

- All hardware features are verified.

- PCle throughput: 101.7 Gbps.

- Optical links can operate at 12.8 Gbps.

- The FPGA can be (re)programmed with different bitfiles in the FLASH (4 images per memory).

- FELIX firmware is successfully migrated to BNL-711

- A second version has been fabricated.

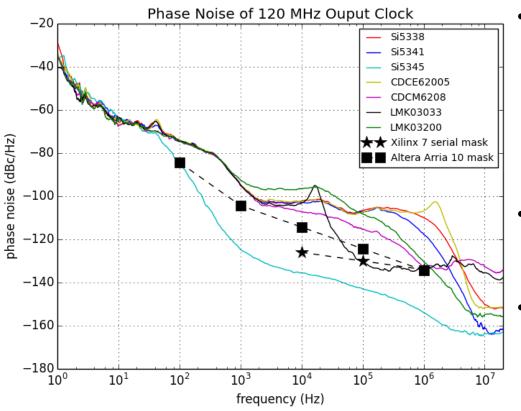

- Jitter cleaner with better performance (Si5345).

- More accurate FPGA voltage control.

Jitter (10 kHz to 1 MHz)

| Devices     | SI5338 | SI5345 | SI5341 | CDCE62005 | CDCM6208 | LMK03200 | LMK03033 |

|-------------|--------|--------|--------|-----------|----------|----------|----------|

| Jitter (ps) | 8.58   | 0.09   | 6.39   | 8.61      | 2.06     | 5.91     | 2.74     |

9

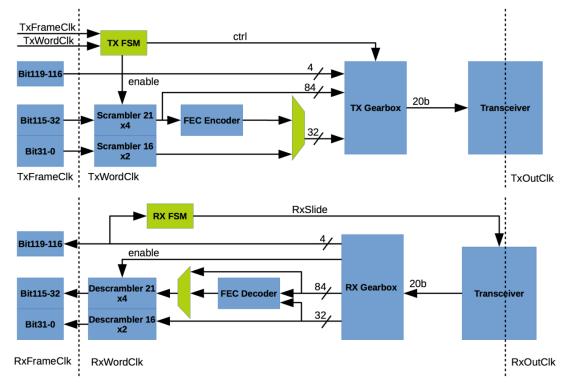

### FELIX firmware block diagram

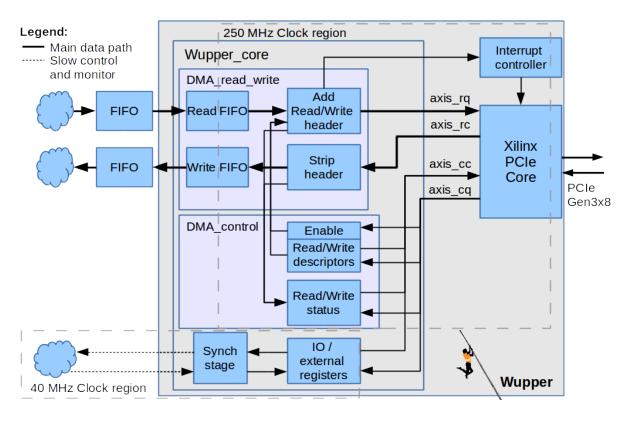

### Wupper: PCIe engine for FELIX

- Developed for use in FELIX

- Published as Open Source (LGPL) on OpenCores <u>http://opencores.org/project.virtex7\_pcie\_dma</u>

- $\hfill\square$  Extended functionality to support and endless DMA

- $\hfill\square$  Extensive stress testing of the core

- Core maturing to maintenance only phase

- $\hfill\square$  Positive feedback from the community

- PCIe Engine with DMA interface to the Xilinx

Virtex-7 (Kintex Ultrascale)

PCIe Gen3 Integrated Block for PCI Express

- Xilinx AXI (ARM AMBA) Stream Interface (UG761)

- MSI-X compatible interrupt controller

- Applications access the engine via simple FIFOs

- Register map for programmed I/O synchronized to a lower clock speed

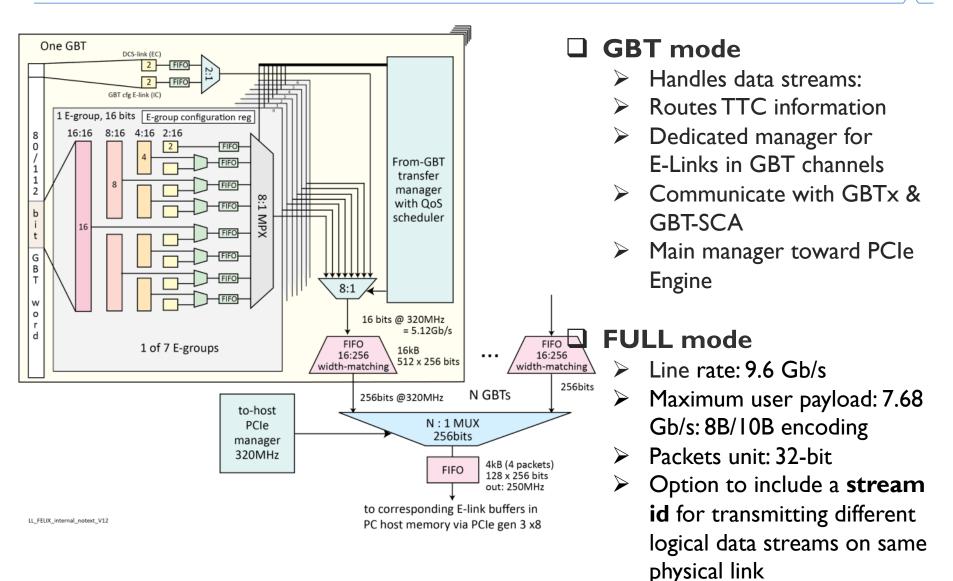

#### Central router: internal data multiplexing

Shown: I of 7 E-groups of a GBT; I of "N" GBTs

Support for BUSY-ON and BUSY-OFF

#### Transceiver wrapper for FELIX

□ Supports 4.8 Gb/s **GBT mode**, and 9.6 Gb/s **FULL mod**e defined for FELIX.

**FELIX GBT Wrapper** is based on CERN GBT-FPGA, with some improvements:

- Separated GBT firmware from transceiver block.

- Run-time choice of GBT mode : Normal (FEC) mode or Wide-Bus mode.

- Lower fixed latency (Tx: 27.8~32 ns; Rx: FEC mode 56.4ns; Rx:Wide mode 43.9 ns).

- The GBT encoding/decoding are in the 240 MHz domain.

- Some blocks like Rx side frame alignment, Tx side time domain crossing are redesigned.

- The single channel example design for KC705/VC709 can be found at <u>https://github.com/simpway/GBT\_KC705</u>

#### Transceiver wrapper for FELIX

Supports 4.8 Gb/s GBT mode, and 9.6 Gb/s FULL mode defined for FELIX.

FELIX FULL mode:

- The transceiver is configured as 32 bit x 240 MHz.

- The Least Significant Byte is used for the 8B/10B alignment.

- An example design with **32-bit PRBS31** generator and checker is provided.

- 5 control symbols are used for the flow control, busy control.

- No error occurred for ~72 hours run. **BER < IE-I5**.

- Has been used in the integration test with **gFEX** (Global Feature Extractor) board.

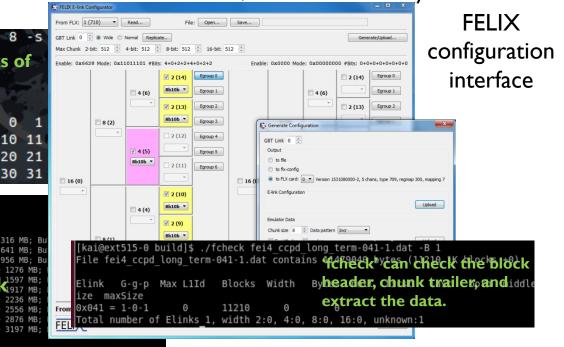

### FELIX software: control, monitor

#### FELIX low-level tools: FLXtools

| FELIX 'housekeeping' functions<br>→ Performance testing, data flow control                         | 911 (A.V. 1   | General information<br>General information<br>General ID: 8261718<br>Card ID: VC-709 |                                                        | FELIX firmware configuration<br>through register map |

|----------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------|

| → Performance testing, data flow control Number of interrupts: 8                                   | 330           | FW version date: 26/8/15 17<br>SVN version: 1966<br>Interrupts, descriptors & c      | chips) via I2C and SPI.                                |                                                      |

| System test and debugging       and verification.                                                  | 8<br>4        | Number of descriptors: 8<br>Number of channels: 4                                    |                                                        | System test and debugging                            |

| Complete user toolset → Collection of tools to control, monitor,<br>configure different FLX cards. | s<br>11<br>11 | CDCE Lock : Yes<br>CXP1 @ 240 MHz : NO !!<br>CXP2 @ 240 MHz : NO !!                  | $\rightarrow$ Collection of tools to control, monitor, | Complete user toolset                                |

#### \$ flx-dump-blocks -n 100 -f output.blocks

| <pre>\$ flx-config f fly dra tost</pre>                                  |                 | daqmustud@gimone:<br>Card model HTG 71<br>Switch I2C addres                                                       |                                                                                                                                                                  | oral                                                                    |                                           |                                           |

|--------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------|

| <pre>\$ flx-dma-test \$ flx-eeprom</pre>                                 | FLXtools<br>set | List of available<br>Device                                                                                       | devices: monitor                                                                                                                                                 | witch port Addres                                                       | ss                                        |                                           |

| <pre>\$ flx-i2c \$ flx-info \$ flx-init \$ flx-irq-test \$ flx-spi</pre> |                 | CLOCK_RAM<br>CLOCK_SYS<br>CLOCK_CXP1<br>CLOCK_CXP2<br>FMC_ADN<br>FMC_TEMP_SENSOR<br>CXP1_TX<br>CXP1_RX<br>CXP2_TX | ICSEN4Q001L IDT<br>ICSEN4Q001L IDT<br>IDT 8N3Q001<br>IDT 8N3Q001<br>ADN2814 (on TTCfx FMC)<br>TC74 (on CRORC TEST FMC)<br>AFBR-83PDZ<br>AFBR-83PDZ<br>AFBR-83PDZ | 0:0 0x66<br>1:0 0x66<br>daqmustud@gimone:\$<br>GBT CHANNEL ALIGN<br>0 1 | e<br>./flip-info GBT -c<br><b>Various</b> | card statuses<br>(FLXtools)<br>(FLXtools) |

| <pre>\$ flx-reset \$ flx-throughput</pre>                                |                 | CXP2_RX<br>DDR3-1                                                                                                 | AFBR-83PDZ<br>SRAM-MT16JTF25664HZ                                                                                                                                | Aligned   Yes Yes                                                       |                                           | es Yes Yes Yes                            |

dagmustud@gimone:\$ ./flip-info

### FELIX software: support

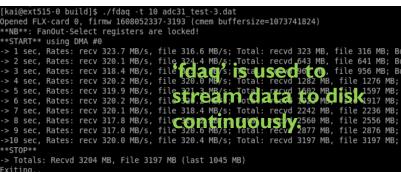

#### FELIX support software (WupperCodeGen, fel, fdaq, fcheck, FELIX E-link configurator)

Automatic generation of a register map

Firmware development tools

Firmware test and debugging

dagmustud@gimone:\$ ./fel -u 2048 -f 64 -t 8 -s FelixCardBuffer 1 loopback via GBT links of data from internal BufSize 4194304 2 8 0.000068 generator ('fel' tool 1 cd ab aa @ 89 0 0 a0 0 bb aa 16 - 4 5 17 18 19 1a 1b 1c 1d 1e 1f 20 21 32 14 15 16 48 24 25 26 27 28 29 2a 2b 2c 2d 2e 2f 30 31

- → Automation software (Jinja based) to handle register map consistently between firmware (HDL), software (C headers), and documentation (Latex) and beyond (ATLAS configuration database, ...).

- Configuration of the internal data emulators to verify the functionality 'off-line'.

- Sommunication with FLX card, data read and analysis.

### Integration test with front-ends

#### ATLAS sub-detectors connected to FELIX

- Liquid Argon Calorimeter

- LTDB (LAr Trigger Digitizer Board)

- LDPB (LAr Digital Processing Blade)

- Level-I calorimeter trigger

- gFEX (Global Feature Extractor)

- ROD, Hub for eFEX (Electron Feature Extractor) and jFEX (Jet Feature Extractor)

- **TREX** (Tile Rear Extension) modules

- New small wheel of the muon spectrometer

- **sTGC** (Small-strip Thin Gap Chamber) and **MicroMegas** (Micro Mesh Gaseous Structure) detector for muon tracking

- Tile Calorimeter

- Test system for Phase-II readout

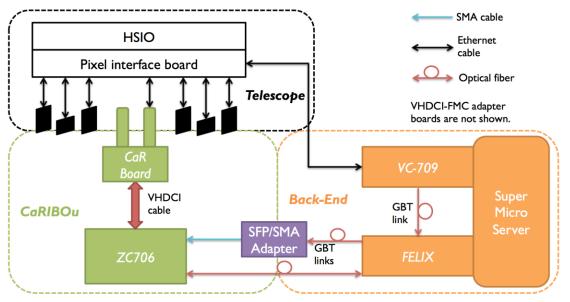

- CaRIBOu (Control and Readout ITk Board)

- Test system for Phase-II ITk HV-CMOS pixel sensor R&D

### Integration test with front-ends

64-ch LTDB prototype

Back-End for LTDB test

- 64-ch LTDB (Liquid Argon Calorimeter Trigger Digitizer Board) Prototype

- With GBTx and GBT-SCA on board

- Software based tool is used to control the GBTx and GBT-SCA

- FELIX (BNL-711 or FLX-709) systems are used

- Perform control and monitoring

- Clock and **BCR** (Bunch Counter Reset) command distribution.

- Successful testing was accomplished in April 2016.

### Integration test with front-ends

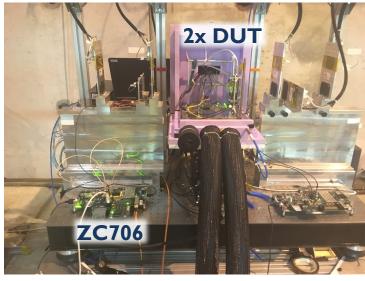

Telescope & CaRIBOu with 2 DUT (Device Under Test)

- CaRIBOu readout system for HV-CMOS sensor

- Data transmission between CaRIBOu and FELIX is in normal GBT mode.

- FELIX is used to

- control and monitor the setup

- distribute clock and TTC commands.

- calibrate the sensor, and readout ASIC FE-I4 by software.

- fdaq: to stream data to disk continuously; fcheck: to check and extract FE-I4 data.

- The testbeam for the system integration was carried out successfully at the end of August 2016 @ CERN.

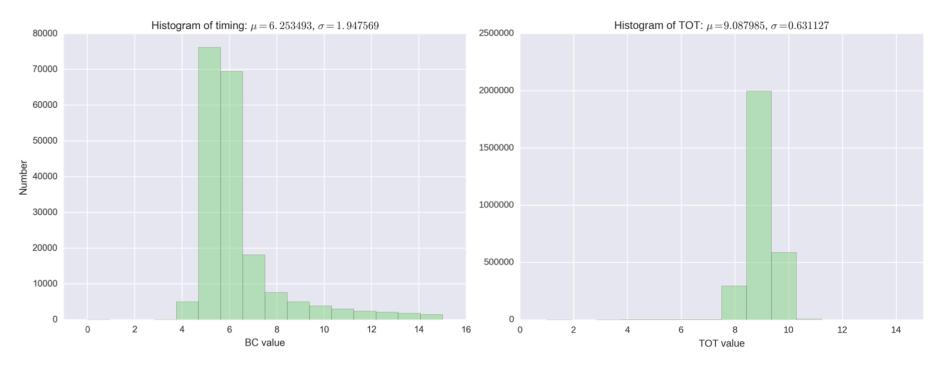

#### Results of CaRIBOu + FELIX integration

Timing distribution compared to trigger from telescope

Time-over-Threshold distribution of the events

- Very stable continuous data taking (up to 13 hours in one night) without any glitch

- Calibration can be done in ~5 minutes, while FE-I4B calibration takes 2 minutes 50 seconds only.

- These results are consistent with current telescope readout system (<u>http://arxiv.org/abs/1603.07798</u>).

# Summary

- FELIX is a **router** between custom serial links and a commodity network, separates data transport from data processing.

- In LHC Run-3 (2020-2022) FELIX will be used by some detectors and trigger systems to interface the data acquisition, detector TTC systems. In LHC Run-4 this is planned for all ATLAS detectors.

- Status:

- FLX-709 (Xilinx VC-709) and its software reached a development status sufficient to be distributed to ATLAS Sub-Detectors Front End developers.

- Initial tests with the BNL FLX-711 successfully accomplished.

- A second revision with minor bug fixes is produced and will be tested soon.

- Ongoing efforts

- Increase overall system reliability.

- Increase the number of input channels supported.

- Extend the system testing and integration: firmware to control of GBTx ASIC via its IC port, GBT-SCA ASIC via EC port.

- A C++ API, an OPC server and client are in progress to fully support the GBT-SCA ASIC.

- Final Design Review planned for November 2016.

# Thanks!

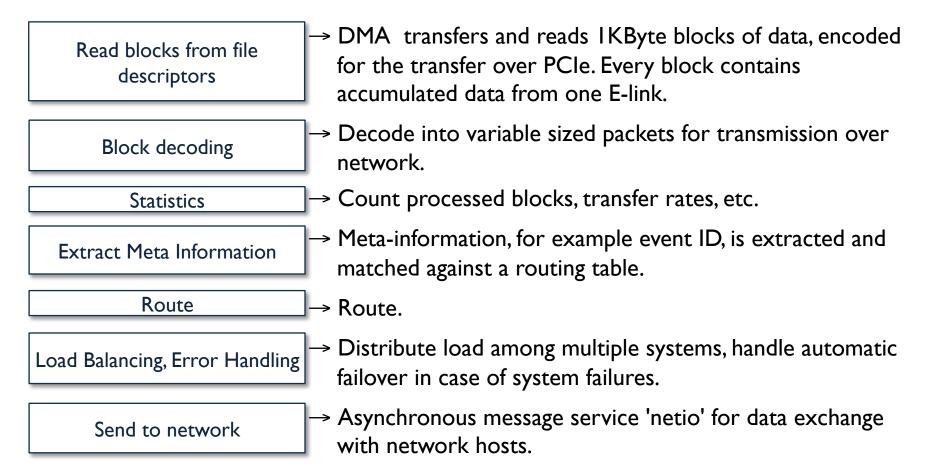

#### FELIX data flow overview

#### FELIX software: data path

#### FELIX application: