AIDA-SLIDE-2015-015

### **AIDA**

Advanced European Infrastructures for Detectors at Accelerators

## Presentation

# Development of front-end electronics for LumiCal detector in CMOS 130 nm technology

Moron, J (AGH-UST) et al

22 September 2014

The research leading to these results has received funding from the European Commission under the FP7 Research Infrastructures project AIDA, grant agreement no. 262025.

This work is part of AIDA Work Package **9:** Advanced infrastructures for detector **R&D**.

The electronic version of this AIDA Publication is available via the AIDA web site <a href="http://cern.ch/aida">http://cern.ch/aida</a> or on the CERN Document Server at the following URL: <a href="http://cds.cern.ch/search?p=AIDA-SLIDE-2015-015">http://cds.cern.ch/search?p=AIDA-SLIDE-2015-015</a>

AGH UNIVERSITY OF SCIENCE AND TECHNOLOGY

# Development of Front-end Electronics for LumiCal Detector in CMOS 130 nm Technology

Jakub Moroń M. Firlej, T. Fiutowski, M. Idzik, K. Swientek AGH-UST

Faculty of Physics and Applied Computer Science AGH University of Science and Technology

TWEPP Topical Workshop on Electronics for Particle Physics, 22-26 September 2014, Aix en Provence, France

- Motivation

- Analog Front-End

- Architecture

- Simulations

- Measurements results

- Deconvolution performance

- Summary

# AGH

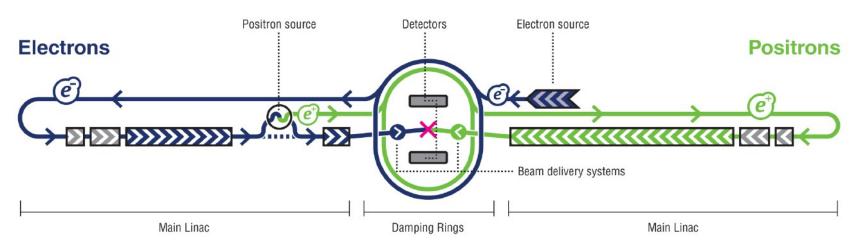

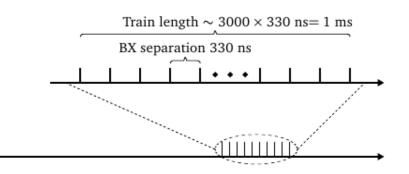

# International Linear Collider (ILC) Schematic layout and beam structure

- Center-of-mass energy = 500 GeV

- Peak luminosity =  $2 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>, particles per bunch =  $2 \times 10^{10}$

- Bunch spacing = 330 ns

- Pulse length = 1 ms

- Pulse rate = 5 Hz

ILC Beam

Train separation 200 ms  $\rightarrow$  Repetition rate 5 Hz

Jakub Moron (AGH-UST) - Development of Front-end Electronics for LumiCal Detector

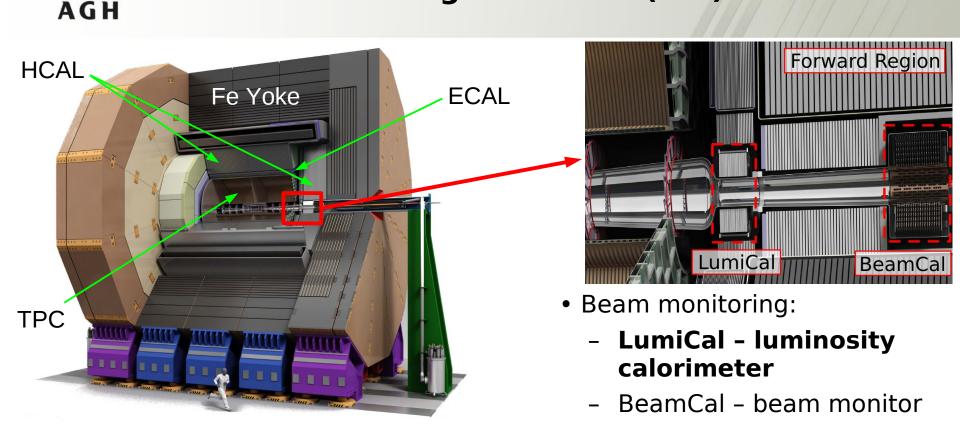

# International Linear Collider (ILC): International Large Detector (ILD)

- Particle detectors:

- Time Projection Chamber (TPC) tracking

- Electromagnetic/Hadronic Calorimetes (E/HCAL) calorimetry

- Fe Yoke muon system

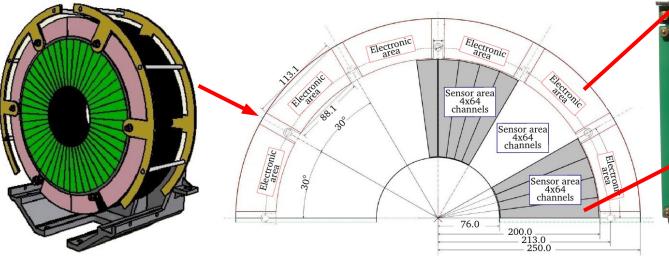

# Luminosity measurements at ILC LumiCal – dedicated luminosity calorimeter

- Gauge process for luminosity measuremet Bhabha scattering with  $\sigma \sim \theta^{\text{-3}}$

- Main LumiCal features:

- 30 layers of tungsted + silicon detectors

- Each layer 12 sensors with 4 sectors each

- Each sector divided into 64 radial pads

- $\rightarrow$  3072 channels in single layer

- $\rightarrow$  92 160 channels on the entire barrel

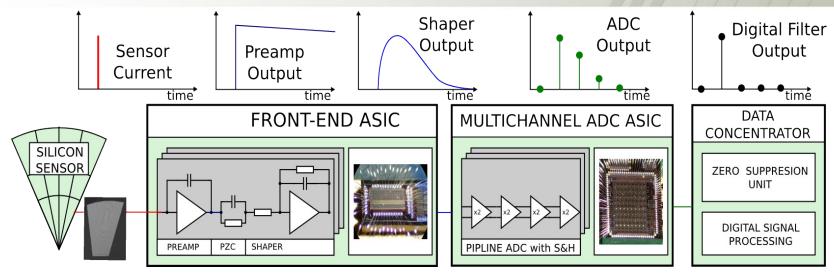

# Luminosity measurements at ILC: LumiCal readout chain

#### Existing LumiCal detector readout comprises:

AGH

- 8 channel front-end ASIC with preamp & CR-RC shaper Tpeak~60ns, ~9mW (AMS 0.35um)

- 8 channel pipeline ADC ASIC, Tsmp<=25MS/s, ~1.2mW/MHz (AMS 0.35um)

- FPGA based data concentrator and further readout

#### New developments for LumiCal detector readout:

- Prototype front-end ASIC in CMOS 130 nm under development... (main subject of this talk)

- Prototype SAR ADC ASIC in CMOS 130 nm fabricated, tested and working well, already presented at TWEPP2013. New 8-channel version waiting for tests

# LumiCal front-end in CMOS 130 nm Specifications

- CMOS 130 nm technology

- Analog Front-End and ADC conversion in each channel

- Detector capacitance  $C_{det} \approx 5 \div 50 pF$

- At present stage CR-RC shaping with peaking time  $\rm T_{peak}\approx50$  ns, allows strightforward deconvolution implementation at asynchronous test-beam sampling

- Variable gain:

- calibration mode MIP sensitivity

- physics mode input charge up to  $\sim$ 6 pC

- Noise: ENC ~ 1000e<sup>-</sup> @10pF

- Crosstalk < 1%

- Analog Front-End power consumption ~1.5 mW/channel

- ADC 10-bit resolution,  $F_{sample} > 20$  MSps (asynchronous read-out), power<1 mW

- Power pulsing average power will be decreased by  $\sim 10^2$

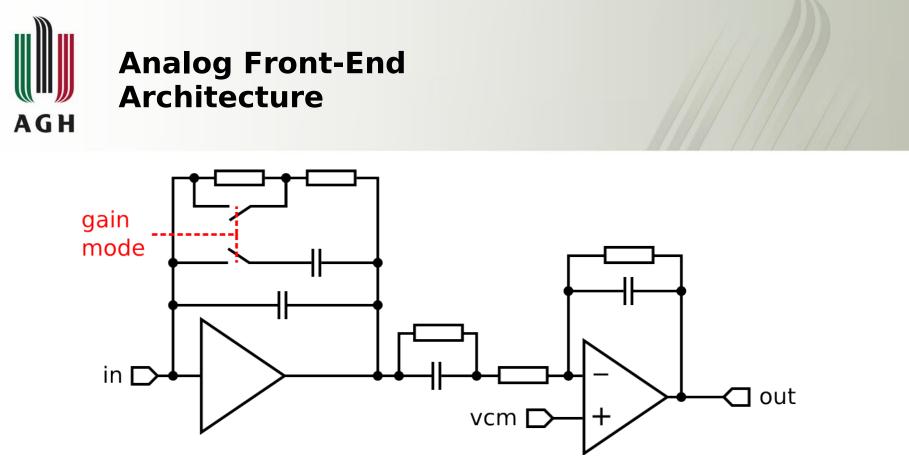

- Preamplifier + PZC + CR-RC shaping

- Two gain modes (calibration and physics) applied by switching R,C components in preamplifier feedback circuit

- Preamplifier telescopic cascode with boosting amplifiers

- Shaper amplifier recycled folded cascode (RFC)

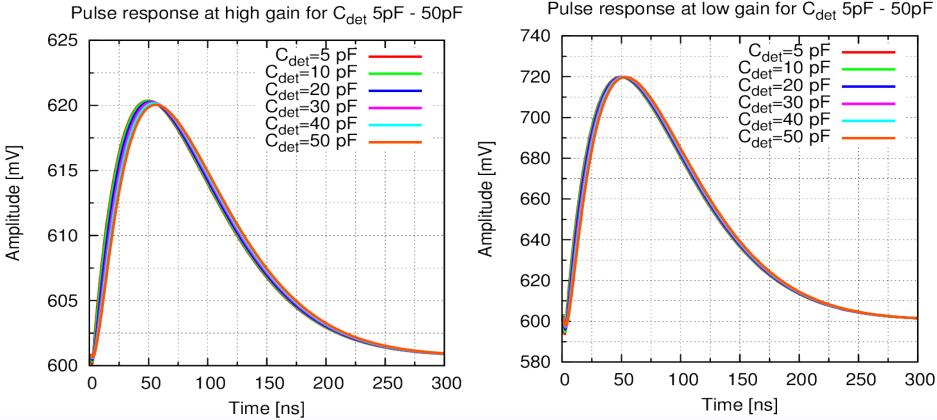

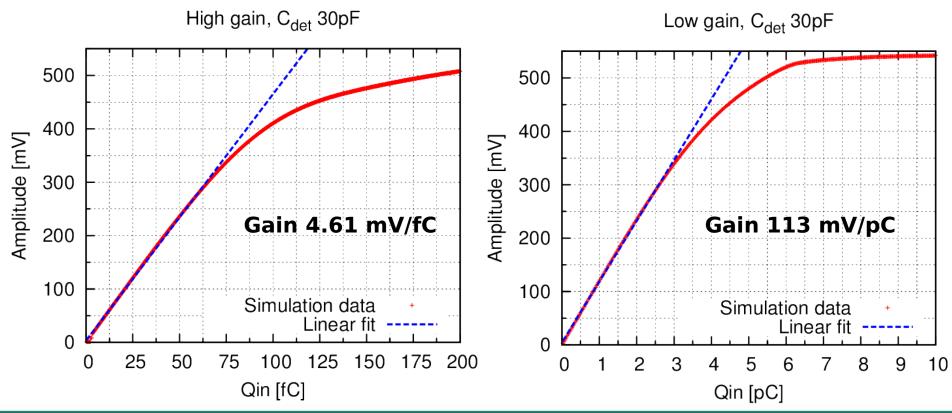

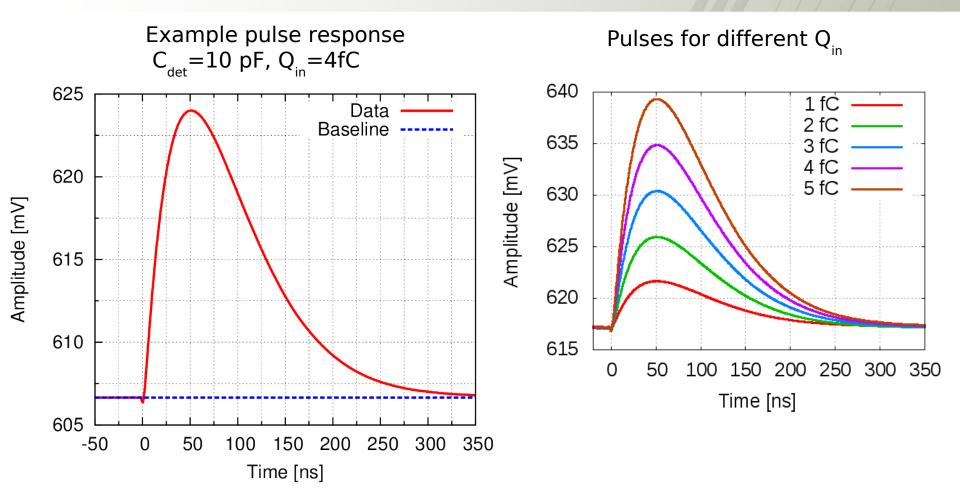

# Analog Front-End simulations Pulse response

- Pulse response for both gains for various detector capacitance Cdet:

- Pulse for  $Q_{in} = 4$  fC (1 MIP) in high gain mode on the left

- Pulse for  $Q_{in} = 1 \text{ pC}$  (250 MIPs) in low gain mode on the right

#### • Two gain modes in Front-End:

- Position calibration with muons sensitivity for MIP (~4fC) high gain

- Luminosity measurement high energy particle  $\rightarrow$  electromagnetic shower  $\rightarrow$  charge deposition up to few pC **low gain**

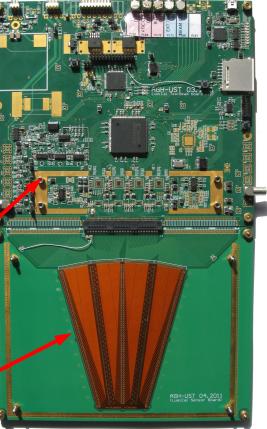

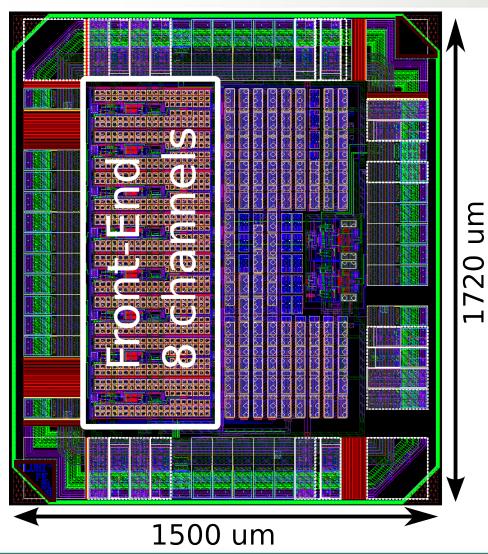

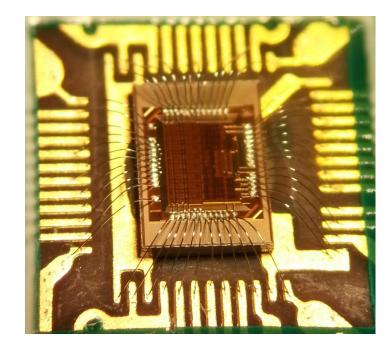

# Analog Front-End Prototype ASIC

- Front-end ASIC prototype contains:

- 8 channels of Preamplifier&Shaper in pitch of 140 um

- 2 channels of Single-to-Differential converter

#### Design submitted in February 2013

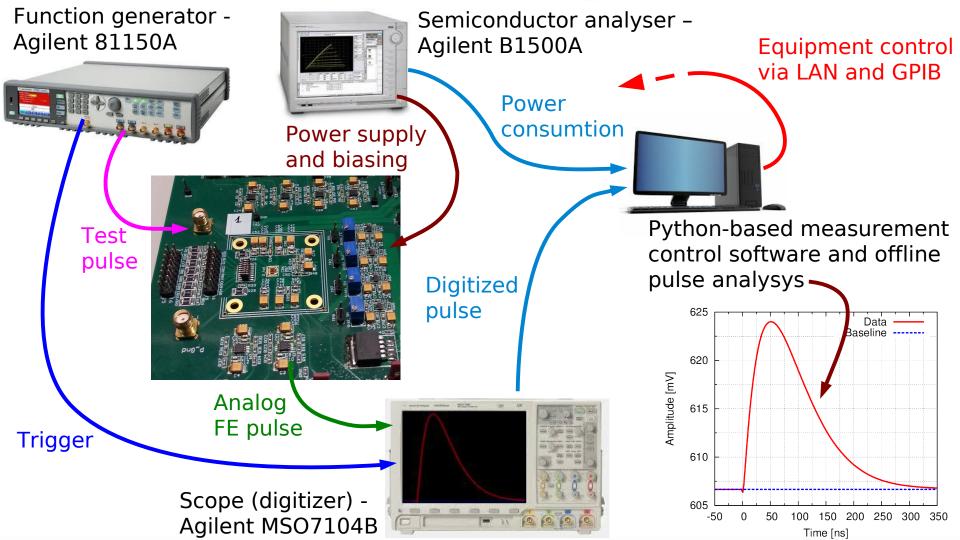

# Analog Front-End measurements Pulse response in high gain mode

AGH

Measured shapes agree with simulations

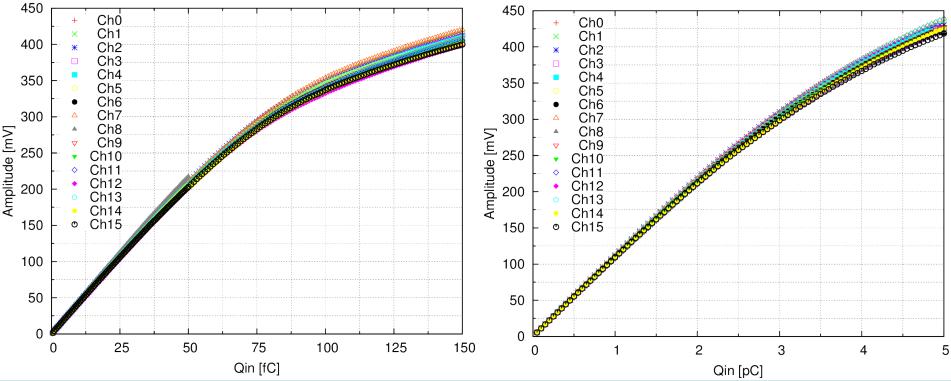

# Analog Front-End measurements Linearity

- Measurements reasults with agreement with simulations

- High gain 4.2 mV/fC (4.6 mV/fC from simulations) -

- varies between 4.03 to 4.37 mV/fC

- Low gain 105 mV/pC (113 mV/pC from simulations)

- varies between 101.7 to 106.4 mV/pC

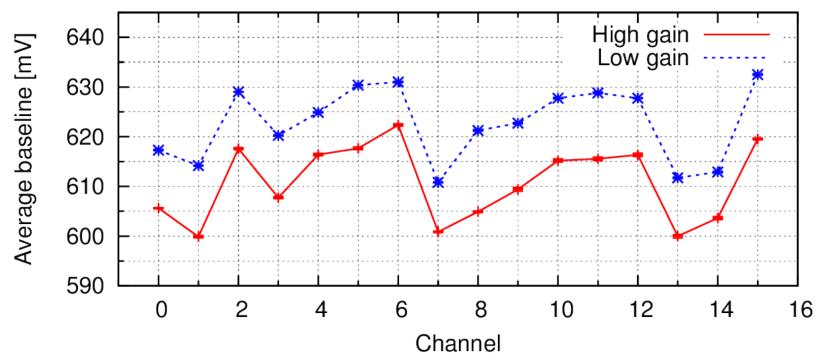

# Analog Front-End measurements Baseline spread

Baseline spread between channels

- 2 ASICs tested channels 0-7 from first ASIC and 8-15 from the second

- Baseline spread is below 25 mV for both gains in agreement with shaper amplifier offset simulations

- Baseline spread in high gain 600 mV to 622 mV

- Baseline spread in low gain 610 mV to 633 mV

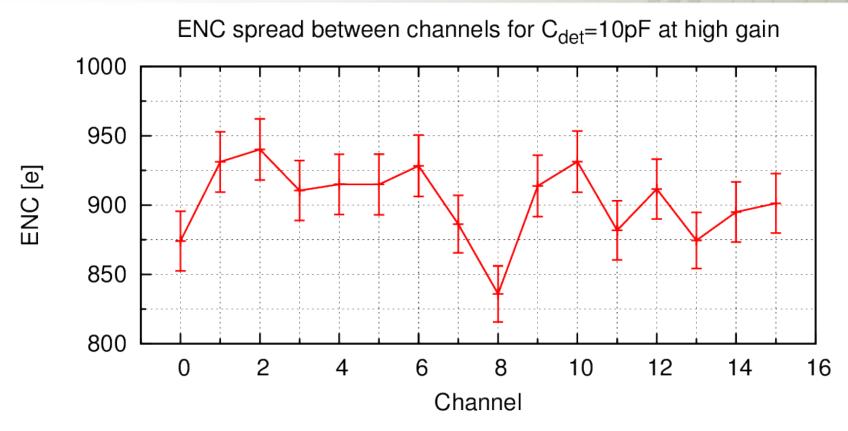

## Analog Front-End measurements Noise performance

- Noise is uniform between the channels

- ENC (Equivalent Noise Charge) is **below 950** electrons giving **SNR** (Signal to Noise Ratio) in high gain mode **above 25** for **1 MIP** input charge

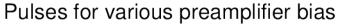

## **Analog Front-End measurements Power consumption vs performance:** Preamplifier bias current in high gain

2.5

2

1.5

1

Default bias value

- Power consumption at typical biasing 1.5 mW / channel

- Power consumption may be decreased without significant decrease of performance

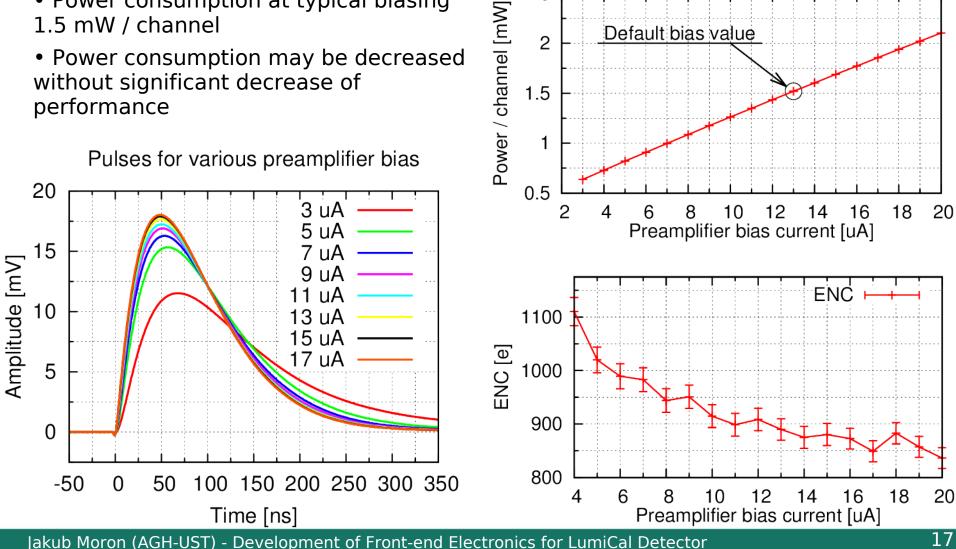

## **Analog Front-End measurements Power consumption vs performance:** Shaper bias current in high gain

2

1.75

1.5

Default bias value

Power consumption at typical biasing Power / channel [mW] 1.5 mW / channel Power consumption may be decreased

without significant decrease of performance

- Measurements results agree with simulations and specifications

- Pulse shape and peaking time (50ns) as excepted

- Gains in both modes differs within 10% from simulated

- Baseline spread below 25 mV

- Noise ENC at 10 pF below 1000 e-

- Crosstalk measuremets:

- High gain 0.64%

- Low gain 0.80%

- Power consumption ~1.5 mW/channel can be reduced by factor of ~2 by lowering bias currents

- All parameters uniform between channels (2 ASICs measured)

- Detector capacitance measurements needs to be completed...

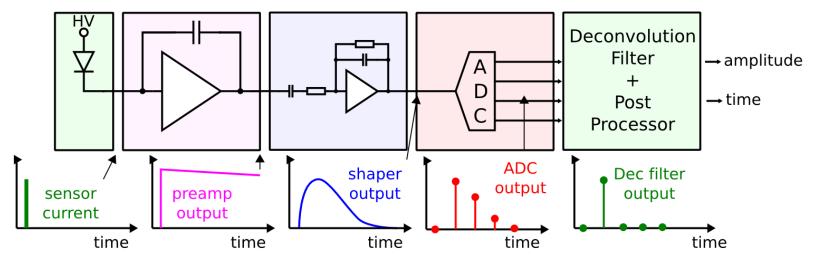

# LumiCal readout electronics diagram – Deconvolution theory

• In the FCAL test-beams performed last years (with asynchronous trigger) deconvolution procedure was used to reconstruct the pulse amplitude and the time of its occurence

•Pulse at output of shaper v(t) is convolution of input signal (current from sensor – s(t)) and impulse response of readout chain h(t):

$$v(t) = \int_{-\infty}^{+\infty} h(t-x) s(x) dx$$

•Using data from continuously running ADC and taking advantage of known pulse shape one can perform invert procedure – **deconvolution** – to get information about event time and amplitude

Amplitude

Amplitude

0.2

0

-2

-1

0

2

3

Time

Δ

5

6

7

8

Look Up Tables used

$d_i = s_i + w_1 s_{i-1} + w_2 s_{i-2}$

Only two multiplications and three additions (very fast and light !)

Deconvolution produces non-zero data only when one or two first samples are on baseline, and second/third is on pulse

•Initial time of pulse is found from ratio of those samples

Can be done off-line •Amplitude is found from sum of those samples, multiplied by time dependent correction factor

Deconvolution reduces (infinite number) of CR-RC pulse samples to 1 or 2 non zero samples !

CR-RC,  $T_{smp} = T_{peak} = 1$ , amp =1 Synchronous sampling (t0 = int \* Tsmp) analog 0.8 sampled 0.6 deconvoluted 0.4 0.2 0 -2 -1 0 2 3 8 5 6 9 Time Asynchronous sampling (t0 / int \* Tsmp) analog 0.8 sampled 0.6 deconvoluted 0.4

9

# AG H

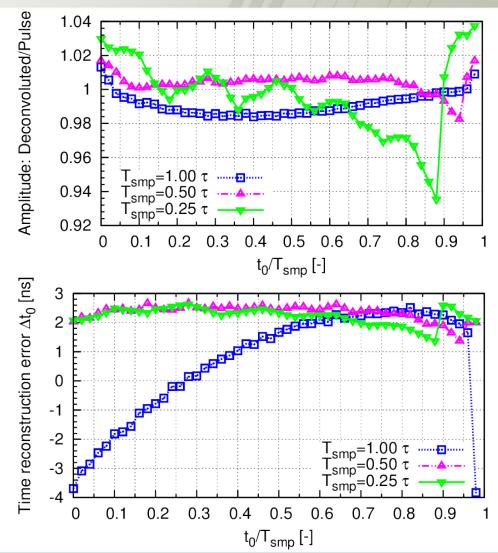

# Deconvolution for new Front-End prototype Averaged pulses, ideal deconvolution weights

- Real pulse (1 MIP) deconvoluted for various phase shift t0 between the Front-End pulse and ADC sampling

- Deconvolution done for different sampling periods (12.5, 25 and 50 ns are presented)

- **Amplitude reconstruction** (top plot) deconvoluted to real pulse amplitude ratio

- Error is below 2% except shortest sampling period

- **Time reconstruction** (bottom plot) difference between reconstructed and real pulse peak position

- Constant offset of around 2 ns except longest sampling period

# S/N after deconvolution still to be measured...

# **Summary and Future Plans**

- Development of new, low power, front-end electronics in CMOS 130 nm for LumiCal detector readout at linear collider is proceeding well

- Low power 10-bit SAR ADC has been already positively verified and presented at TWEPP2013, 2nd prototype of 8 channel ADC is fabricated and waiting for tests

- 1st prototype of 8 channel analog front-end, shown here, is working well, some quantitive tests (e.g. Cdet dependence) still need to be done...

- Works on deconvolution implementation for new read-out system ongoing

• We hope to integrate and submitt in 2015 (in one or two ASICs) the whole front-end containing preamp+shaper+ADC in each channel, and all other functionalities (DACs, I2C, PLL, DLL, SLVS) needed in complex SoC type chip

# Thank you for attention