# A NEW SPARK DETECTION SYSTEM FOR THE ELECTROSTATIC SEPTA OF THE SPS NORTH (EXPERIMENTAL) AREA

R. Barlow, B. Balhan, J. Borburgh, E. Carlier, C. Chanavat, T. Fowler, B. Pinget CERN, Geneva, Switzerland

Abstract

Electrostatic septa (ZS) are used in the extraction of the particle beams from the CERN SPS to the North Area experimental zone. These septa employ high electric fields, generated from a 300 kV power supply, and are particularly prone to internal sparking around the cathode structure. This sparking degrades the electric field quality, consequently affecting the extracted beam, vacuum and equipment performance. To mitigate these effects, a Spark Detection System (SDS) has been realised, which is based on an industrial SIEMENS S7-400 programmable logic controller and deported Boolean processor modules interfaced through a PROFINET fieldbus. The SDS interlock logic uses a moving average spark rate count to determine if the ZS performance is acceptable. Below a certain spark rate it is probable that the ZS septa tank vacuum can recover, thus avoiding transition into a state where rapid degradation would occur. Above this level an interlock is raised and the high voltage is switched off. Additionally, all spark signals acquired by the SDS are sent to a front-end computer to allow further analysis such as calculation of spark rates and production of statistical data.

#### INTRODUCTION

At CERN, the SPS is equipped with a slow extraction channel to fixed target beam lines in the North experimental area. This channel comprises five wire type electrostatic septa (ZS) followed by nine thick electromagnetic septa (MS).

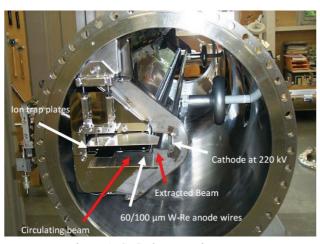

The ZS are composed of a field free region for circulating beam, a high field region for extracted beam and ion traps for active protection (Fig. 1).

Figure 1: SPS electrostatic septa.

High electrostatic field is obtained through the application of a high voltage on a flat anode/cathode construction: the anode electrode, connected to ground, is made out of a set of 60/100 µm thin wires. The cathode electrode is powered by a PANTAK -300 kV generator (Cockcroft-Walton type) currently operated at -220 kV.

The ion traps [1] are cleaning electrode devices placed in the region containing the circulating beam and typically operated around -6.6kV. These ion traps employ an electrostatic field to remove the ions produced by the beam interactions with the residual gas molecules, in order to reduce the high-voltage sparking between the anode and the cathode.

Due to the technology used, both the cathode and the ion trap can spark internally causing degradation to their electric field, affecting the performance of the equipment and the machine [2] through:

- Electrical stress on high-voltage feed-throughs;

- Thermal heating of septa wires;

- Degradation of the vacuum affecting both circulating and extracted beams:

- Increased level of beam losses in the extraction channel.

To alleviate these effects and protect the device, a Spark Detection System (SDS) has been developed in order to interlock the high-voltage power supplies in case of high spark rate.

#### **SIMULATIONS**

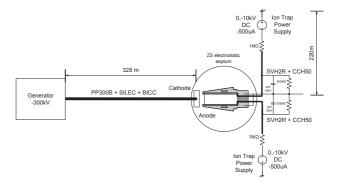

In the initial stage of the SDS design process, simulations of the high-voltage circuit between the generator, the ion trap power supplies and the septum (Fig. 2) were made with PSPICE.

Figure 2: Simplified view of ZS powering circuits (generator and ion traps).

The goals of these simulations were:

- To understand the functioning of the complete highvoltage path of the entire system including coupling effects between the ion traps and the septum electrode structures;

- To quantify the dynamic characteristics of the different type of electrical breakdowns;

- To validate the spark detection circuits.

The initial model included the power source, the high-voltage transmission lines, the line resistances, the spark breakdown model, the connector's capacitance, and the spark detection circuitry. The first series of simulations showed limitations of the model in the dynamic response of the circuit to a spark when compared to actual measurements. The model was improved by including the following additional parameters:

- Improved generator model including voltage and current regulation monitoring;

- High-voltage transmission line lumped parameters including R, L, C and G;

- Monitoring of cathode and ion trap sensing circuit outputs;

- Enhanced spark breakdown model.

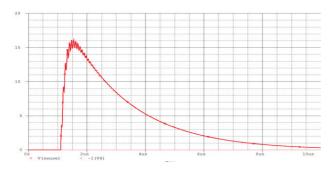

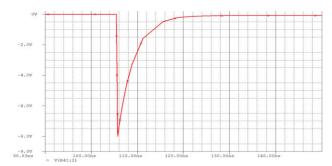

Simulations using this improved model show, that in the worst-case conditions of a breakdown at maximum voltage, the shape and amplitude of the spark signal at the SDS input are acceptable for acquisition with standard electronic technologies as shown in Fig. 3 and Fig. 4.

Figure 3: Simulated 300 kV high-voltage breakdown between anode and cathode electrodes at SDS input.

Figure 4: Simulated -10 kV high voltage breakdown between ion trap plates at SDS input.

#### SPARK SENSING CIRCUITRY

In order to acquire the spark signals and to transmit them to the SDS, two different types of pickups have been devised.

The generator pickup is made up of a capacitive divider which sits inside a shielding box mounted onto the electrostatic septa tank. The nominal spark ratio between spark amplitude and measured signal amplitude, taking into account the long coaxial line between the sensor and the SDS, is:

$$Spark_{ratio} = \frac{Vo}{Vi} = \frac{Z1}{Z1 + Z2} = \frac{\left\{\frac{1}{j\omega C_{coax}//C1}\right\}}{\left\{\frac{1}{j\omega C_{coax}//C1}\right\} + \left\{\frac{1}{j\omega C2}\right\}} \cong \frac{1}{19300}$$

for a spark frequency range of 2 MHz.

The ion trap pickup is based on a RC divider which is embedded inside the ion trap high-voltage box located behind the tank. The nominal spark ratio is:

$$Spark_{ratio} = \frac{Vo}{Vi} = \frac{1}{\sqrt{1 + (\omega RC)^2}} \cong \frac{1}{1222}$$

for a spark frequency range of 40 MHz.

#### **SDS ARCHITECTURE**

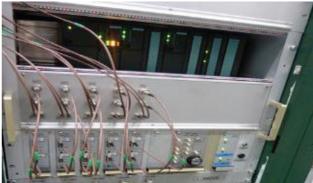

The SDS is housed in a 19 inch rack chassis that contains 5 analogue acquisition cards (one per septum), 1 self-test card and a set of SIEMENS S7-300 PLC modules for data acquisition (Fig. 5).

Figure 5: Frontal view of the 19 inch rack chassis containing the SDS hardware.

The high-voltage inputs which receive the spark signals from the septum are located on the rear side of the unit. These signals are internally transferred onto a backplane for distribution to the analogue acquisition layer. The signals are then conditioned in order to be compliant with industrial signal levels for connection to off-the-shelf SIEMENS modules.

## Spark Inputs

The spark sensor high-voltage input connectors (15 kV LEMO) are fitted onto a thick epoxy resin plate for a proper galvanic isolation between the generator high-voltage and the electronic grounds.

Each high-voltage connector is equipped with a spark gap and a bipolar transient voltage suppressor for protection of the acquisition input circuit against fast transients.

## Analogue Acquisition

The SDS is based on a custom made electronic Analogue Acquisition Card (AAC) which interfaces the different types of spark sensing circuit with the digital counting system (Fig. 6). One AAC can acquire and condition simultaneously 2 channels, one for the septum cathode and one for the ion trap. Its principal characteristics are:

- Galvanic isolation through a wide bandwidth pulse transformer between generator high-voltage circuit and electronic;

- Passive front-end circuit for spark signal acquisition;

- Generation of clean pulse from spark edges through adjustable fast comparators;

- Isolated low impedance and wide bandwidth analogue outputs of the spark input signals;

- Level conversion of comparator output pulses to industrial standards (typically +24 V);

- Production of a trigger pulse train synchronised to any spark event in the system.

Each card treats one septum tank; hence 5 cards (10 channels) are necessary for the complete ZS system.

A Spark Test Card (STC) is incorporated in the SDS for the implementation of an on board self-test facility (Fig. 6). It emulates spark events for all 10 channels with variable spark amplitude and spark rate in order to check whether the system is functioning correctly.

Figure 6: SDS spark test card (top) and analogue acquisition card (bottom).

## Digital Acquisition

The integration of the SDS within the PLC-based ZS control architecture is realised through the use of a specific SIEMENS module for fast process control. The counting of the spark events is based on the SIEMENS FM352-5 Boolean Processor module [3].

This module provides an independent and extremely fast acquisition of input events using an on-board processor coupled with a Field Programmable Gate Array (FPGA). Acquisition and control codes are executed in parallel which results in scan cycles in the range of a few microseconds.

#### **FUNCTIONALITIES**

## Spark Count

The spark counting mechanism is based on two SIEMENS FM352-5 Boolean Processors for the acquisition of the 10 channels. The shaped spark signals coming from the AAC are detected by the FM352-5 and then internally counted at the level of the FPGA logic.

The two Processors are configured to read back each count increment to carry out a check that each detected pulse has been counted reliably.

The system also determines three different categories of spark magnitude (low, medium and strong) and is able to count them accordingly. The thresholds of each category are adjusted per channel at the level of the AAC.

## Spark Rate

Presently the SDS is configured to produce an interlock for 5 sparks within a 10 seconds time frame. These parameters are configurable by the user within an expert interface to suit a wide range of interlocking configurations.

At the same time a rapid salve of sparks must neither be recorded as a fault nor create an interlock. To allow this, the AAC has an internal inhibition mechanism that masks the unwanted salves. This inhibition ensures also that only "true" spark events are recorded and that any reflections or noise spikes will not be counted as a spark.

## SOFTWARE APPLICATIONS

#### Local Control

Local facilities for the control and the monitoring of the SDS are provided within a "Supervisory Control And Data Acquisition" (SCADA) system. The hardware consists of a SIEMENS Touch Panel communicating with the ZS master PLC and it's deported/decentralised I/O's via PROFINET. The SCADA software is based on SIEMENS WinCC Flexible.

## Remote Control

The SDS is controlled and monitored from the CERN Control Centre (CCC) using the standard communication protocols developed at CERN, which are not available on SIEMENS hardware. To interface the SIEMENS PLCs to

the CERN Control Middleware (CMW), a 'proxy' computer running an implementation of a CERN standard Front-End Software Architecture (FESA) class is used. It communicates with the PLC on one side using the generic IEPLC framework for interconnecting logic controllers and front-end computers [4], and to the CERN control environment on the other side using CMW.

This allows the remote control of the SDS through generic Java application (Fig. 7) and the continuous publication of the various SDS data to the SPS logging database for off-line analysis or to fixed displays in the CCC for real time visualisation of the spark rates during machine performance optimisation.

Figure 7: Java application showing spark rate trending.

## Spark Waveforms Visualisation

Acquired sparks signals are also sent from the SDS to an Open Analogue Signal Information System (OASIS) [5] for fast analogue signals acquisition and display. Within OASIS, the acquired spark signals can be correlated with other accelerator signals like beam losses, beam intensity or vacuum for a better understanding of the sparking process.

#### **CONCLUSIONS**

The SPS extraction electrostatic septa system has benefited vastly from the SDS. It has successfully protected the equipment against potential internal failure induced by high sparking rate and has also shown to be an invaluable tool for a more in-depth understanding of the sparking process thanks to its extensive possibilities of data analysis and monitoring.

Despite its initial design based on the requirements for the SPS, the SDS has also been successfully deployed for the sparking surveillance of electrostatic septa in the PS Complex at CERN but also for electrostatic injection and extraction septa at the MedAustron facility.

#### REFERENCES

- [1] Barlow, R A et al., "The ZS Electrostatic Septa Ion Traps control," CERN-ATS-Note-2011-018 TECH.

- [2] B. Balhan et al., "Performance of the SPS extraction channel equipment in 1996," CERN-SL-Note-97-42-MS.

- [3] M. Zaera-Sanz, "Evaluation of a fast PLC module in prospect of the LHC beam interlock system," CERN-AB-Note-2005.

- [4] F. Locci et al., "IEPLC, Automated Communication in a Heterogeneous Control System Environment," MOPPC031, ICALEPCS 2013, to be published.

- [5] S Deghaye et al., "Oasis: A New System to Acquire and Display the Analog Signals for LHC," ICALEPCS'2009, Gyeongju, Korea, 13 – 17 Oct 2003, pp.359.