# ATLAS Liquid Argon Calorimeter Phase-I Upgrade

# **Technical Design Report**

Issue: 1 Revision: 0 Reference: CERN-LHCC-2013-017 ATLAS-TDR-022-2013 Created: September 1, 2013 Last modified: December 2, 2013 **Prepared by:** ATLAS Collaboration

CDS: https://cds.cern.ch/record/1602230/

# The ATLAS Collaboration

#### Argentina

Universidad de Buenos Aires, Buenos Aires Universidad Nacional de La Plata, La Plata

Armenia Yerevan Physics Institute, Yerevan

Australia

University of Adelaide, Adelaide Research Centre for High Energy Physics, Melbourne University, Melbourne University of Sydney, School of Physics, Sydney

#### Austria

Institut für Astro- und Teilchenphysik, University of Innsbruck, Innsbruck Fachhochschule Wiener Neustadt (FHWN), Wiener Neustadt

Azerbaijan Republic

Institute of Physics, Azerbaijan Academy of Sciences, Baku

#### **Republic of Belarus**

Institute of Physics, National Academy of Sciences of Belarus, Minsk

National Centre for Particle & High Energy Physics, Minsk

#### Brazil

Universidade Federal de Juiz de Fora, Universidade Federal do Rio De Janeiro, COPPE/EE/IF, Rio de Janeiro, Universidade Federal de Sao Joao del Rei and Universidade de Sao Paulo

#### Canada

University of Alberta, Edmonton University of Carleton, Carleton University of Montreal, Group of Particle Physics, Montreal, Quebec Department of Physics, McGill University, Montreal Simon Fraser University, Burnaby, BC Department of Physics, University of Toronto, Toronto TRIUMF, Vancouver and York University, Toronto Department of Physics, University of British Columbia, Vancouver University of Victoria, Victoria

European Laboratory for Particle Physics (CERN), Geneva

#### Chile

Joint team from Pontificia Universidad Católica de Chile, Santiago and Universidad Técnica Federico Santa María, Valparaíso

#### China

Chinese cluster formed by IHEP Beijing, Nanjing, Shandong, Shanghai Jiao Tong and Hefei

#### Colombia

Universidad Antonio Narino (UAN), Bogotá

#### Czech Republic

Palacký University, Olomouc

Academy of Sciences of the Czech Republic, Institute of Physics and Institute of Computer Science, Prague

Charles University in Prague, Faculty of Mathematics and Physics, Prague

Czech Technical University in Prague, Faculty of Nuclear Sciences and Physical Engineering, Faculty of Mechanical Engineering, Prague

#### Denmark

Niels Bohr Institute, University of Copenhagen, Copenhagen

#### France

Laboratoire d'Annecy-le-Vieux de Physique de Particules (LAPP), CNRS-IN2P3, Annecy-le-Vieux

Laboratoire de Physique Corpusculaire, Université Blaise Pascal, CNRS-IN2P3, Clermont-Ferrand

Laboratoire de Physique Subatomique et de Cosmologie de Grenoble (LPSC), CNRS-IN2P3, Université Joseph Fourier, Grenoble

Centre de Physique de Particules de Marseille (CPPM), CNRS-IN2P3, Marseille

Laboratoire de l'Accélérateur Linéaire (LAL), CNRS-IN2P3, Orsay

Laboratoire de Physique Nucléaire et de Hautes Energies (LPNHE), Universités de Paris VI et VII, CNRS-IN2P3, Paris

Commisariat a l'Energie Atomique (CEA), DSM/DAPNIA, Centre d'Etudes de Saclay, Gif-sur-Yvette

#### Georgia

Institute of Physics of the Georgian Academy of Sciences and Tbilisi State University, Tbilisi

#### Germany

Physikalisches Institut, University of Bonn, Bonn Deutsches Elektronen-Synchrotron (DESY), Hamburg and Zeuthen TU Dortmund, Experimentelle Physik IV, Dortmund Technical University Dresden, Dresden Fakultät für Mathematik und Physik, Albert-Ludwigs-Universität, Freiburg Justus-Liebig-Universität, Giessen Fakultät für Physik, II. Physikalisches Institut, Georg-August-Universität, Göttingen Ruprecht-Karls-Universität Heidelberg, Kirchhoff-Institut für Physik and Zentrales Institut für Technische Informatik (ZITI), Heidelberg Institut für Physik, Humboldt Universität, Berlin Institut für Physik, Universität Mainz, Mainz Sektion Physik, Ludwig-Maximilians-Universität München, München Max-Planck-Institut für Physik, München Fachbereich Physik, Universität Siegen, Siegen Fachbereich Physik, Bergische Universität, Wuppertal Julius-Maximilians-University, Würzburg **Greece** National Technical University of Athens, Athens University of Athens, Athens

University of Thessaloniki, High Energy Physics Department and Department of Mechanical Engineering, Thessaloniki

#### Israel

Department of Physics, Technion, Haifa School of Physics, Tel Aviv University, Tel Aviv Department of Particle Physics, The Weizmann Institute of Science, Rehovot

#### Italy

Dipartimento di Fisica dell' Università di Bologna e I.N.F.N., Bologna Dipartimento di Fisica dell' Università della Calabria e I.N.F.N., Cosenza Laboratori Nazionali di Frascati dell' I.N.F.N., Frascati Dipartimento di Fisica dell' Università di Genova e I.N.F.N., Genova Dipartimento di Fisica dell' Università di Lecce e I.N.F.N., Lecce Dipartimento di Fisica dell' Università di Milano e I.N.F.N., Milano Dipartimento di Scienze Fisiche, Università di Napoli 'Federico II' e I.N.F.N., Napoli Dipartimento di Fisica Nucleare e Teorica della Università di Pavia e I.N.F.N., Pavia Dipartimento di Fisica dell' Università di Pisa e I.N.F.N., Pisa Dipartimento di Fisica dell' Università di Roma I 'La Sapienza' e I.N.F.N., Roma Dipartimento di Fisica dell' Università di Roma II 'Tor Vergata' e I.N.F.N., Roma Dipartimento di Fisica dell' Università di Roma III 'Roma Tre' e I.N.F.N., Roma

#### Japan

Hiroshima Institute of Technology, Hiroshima KEK, High Energy Accelerator Research Organization, Tsukuba Kobe University, Kobe

Department of Physics, Kyoto University, Kyoto

Kyoto University of Education, Kyoto

Kyushu University, Kyushu

Nagasaki Institute of Applied Science, Nagasaki

Nagoya University, Nagoya

Faculty of Science, Okayama University, Okayama

Osaka University, Osaka

Faculty of Science, Shinshu University, Matsumoto

International Center for Elementary Particle Physics and Department of Physics, The University of Tokyo

Tokyo Institute of Technology, Tokyo

Physics Department, Tokyo Metropolitan University, Tokyo

Institute of Physics, University of Tsukuba, Tsukuba

Waseda University, Tokyo

#### Morocco

Faculté des Sciences Ain Chock, Université Hassan II, Casablanca, Université Mohamed Premier et LPTM, Oujda, Université Cadi Ayyat et LPHEA, Marrakech, CNESTEN et Université Mohamed V, Rabat

#### Netherlands

FOM - Institute SAF NIKHEF and University of Amsterdam/NIKHEF, Amsterdam

Radboud University Nijmegen and NIKHEF, Nijmegen

#### Norway

University of Bergen, Bergen

University of Oslo, Oslo

#### Poland

Institute of Nuclear Physics (IFJ PAN), Polish Academy of Sciences, Cracow

Faculty of Physics and Applied Computer Science, AGH University of Science and Technology and Marian Smoluchowski Institute of Physics, Jagiellonian University, Cracow

#### Portugal

Laboratório de Instrumentação e Física Experimental de Partículas (LIP), Faculdade de Ciências, Universidade de Lisboa, Centro de Física Nuclear da Universidade de Lisboa, Department of Physics, University of Coimbra, Departamento de Física, Universidade do Minho, Dep Física and CEFITEC of Faculdade de Ciências e Tecnologia, Universidade Nova de Lisboa, University of Granada

### Romania

Horia Hulubei National Institute of Physics and Nuclear Engineering (IFIN-HH), Institute of Atomic Physics, Bucharest, ITIM, Cluj Napoca, West University, Timisoara and University Politehnica Bucharest

#### Russia

Institute for Theoretical and Experimental Physics (ITEP), Moscow

P.N. Lebedev Institute of Physics, Moscow

Moscow Engineering & Physics Institute (MEPhI), Moscow

Moscow State University, Moscow

Budker Institute of Nuclear Physics (BINP), Novosibirsk

State Research Center of the Russian Federation - Institute for High Energy Physics (IHEP), Protvino

Petersburg Nuclear Physics Institute (PNPI), St. Petersburg

#### JINR

Joint Institute for Nuclear Research, Dubna

#### Serbia

Institute of Physics, University of Belgrade and Vinca Institute of Nuclear Sciences, Belgrade

#### **Slovak Republic**

Bratislava University, Bratislava, and Institute of Experimental Physics of the Slovak Academy of Sciences, Kosice

#### Slovenia

Jožef Stefan Institute and Department of Physics, University of Ljubljana, Ljubljana

#### South Africa

University of Cape Town, University of Johannesburg (UJ) and University of the Witwatersrand (WITS), Johannesburg

#### Spain

Institut de Física d'Altes Energies (IFAE), Universitat Autònoma de Barcelona, Bellaterra (Barcelona)

Physics Department, Universidad Autónoma de Madrid, Madrid

Instituto de Física Corpuscular (IFIC), Centro Mixto UVEG-CSIC, Valencia and Instituto de Microelectrónica de Barcelona, Bellaterra (Barcelona)

#### Sweden

Fysiska institutionen, Lunds universitet, Lund Royal Institute of Technology (KTH), Stockholm

Stockholm University, Stockholm

University of Uppsala, Department of Physics and Astronomy, Uppsala

#### Switzerland

University of Bern, Albert Einstein Center for Fundamental Physics, Laboratory for High Energy Physics, Bern

Section de Physique, Université de Genève, Geneva

#### Taiwan

Academia Sinica, Taipei

#### Turkey

Department of Physics, Ankara University, Gazi University and TOBB ETU, Ankara Department of Physics, Bogazici University, Dogus University and Gaziantep University, Istanbul

#### United Kingdom

School of Physics and Astronomy, The University of Birmingham, Birmingham University of Sussex, Brighton Cavendish Laboratory, University of Cambridge, Cambridge University of Warwick, Coventry School of Physics & Astronomy, University of Edinburgh, Edinburgh Department of Physics and Astronomy, University of Glasgow, Glasgow Physics Department, Lancaster University, Lancaster University of Liverpool, Liverpool Department of Physics, Queen Mary and Westfield College, University of London, London Department of Physics, Royal Holloway, University of London, Egham Department of Physics and Astronomy, University College London, London Department of Physics and Astronomy, University of Manchester, Manchester Department of Physics, Oxford University, Oxford Rutherford Appleton Laboratory, Science and Technology Facilities Council, Didcot Department of Physics, University of Sheffield, Sheffield

#### **United States of America**

State University of New York at Albany, New York Argonne National Laboratory, Argonne, Illinois University of Arizona, Tucson, Arizona Department of Physics, The University of Texas at Arlington, Arlington, Texas Lawrence Berkeley National Laboratory and University of California, Berkeley, California Physics Department of the University of Boston , Boston, Massachusetts Brandeis University, Department of Physics, Waltham, Massachusetts Brookhaven National Laboratory (BNL), Upton, New York University of Chicago, Enrico Fermi Institute, Chicago, Illinois Nevis Laboratory, Columbia University, Irvington, New York University of Texas at Dallas, Dallas, Texas Department of Physics, Duke University, Durham, North Carolina Department of Physics, Hampton University, Virginia Department of Physics, Harvard University, Cambridge, Massachusetts Indiana University, Bloomington, Indiana Iowa State University, Ames, Iowa University of Iowa, Iowa City, Iowa University of California, Irvine, California Louisiana Tech University, Louisiana University of Massachusetts, Amherst, Massachusetts Massachusetts Institute of Technology, Department of Physics, Cambridge, Massachusetts Michigan State University, Department of Physics and Astronomy, East Lansing, Michigan University of Michigan, Department of Physics, Ann Arbor, Michigan Department of Physics, New Mexico University, Albuquerque, New Mexico Department of Physics, New York University, New York Northern Illinois University, DeKalb, Illinois Ohio State University, Columbus, Ohio Department of Physics and Astronomy, University of Oklahoma Oklahoma State University, Oklahoma University of Oregon, Eugene, Oregon Department of Physics, University of Pennsylvania, Philadelphia, Pennsylvania University of Pittsburgh, Pittsburgh, Pennsylvania Institute for Particle Physics, University of California, Santa Cruz, California SLAC National Accelerator Laboratory, Stanford, California Physics Department, Southern Methodist University, Dallas, Texas State University of New York at Stony Brook, New York Tufts University, Medford, Massachusetts High Energy Physics, University of Illinois, Urbana, Illinois Department of Physics, Department of Mechanical Engineering, University of Washington, Seattle, Washington Department of Physics, University of Wisconsin, Madison, Wisconsin

Yale University, New Haven, Connecticut

# Contents

| 1 | Ove      | erview of the Phase-I LAr upgrade project 1                                                               |

|---|----------|-----------------------------------------------------------------------------------------------------------|

| • | 1.1      | LHC baseline roadmap                                                                                      |

|   | 1.2      | ATLAS upgrade plans up to 2030 and beyond                                                                 |

|   | 1.3      | Objectives of the Phase-I LAr upgrade project                                                             |

|   | 1.4      | Compatibility with Phase-II upgrades                                                                      |

|   | 1.4      |                                                                                                           |

| 2 | Phv      | sics Requirements and Expected Performance 9                                                              |

| _ | 2.1      | Super Cell Energy Reconstruction and Resolution                                                           |

|   |          | 2.1.1 Energy reconstruction                                                                               |

|   |          | 2.1.2 Energy Resolution                                                                                   |

|   | 2.2      | Level-1 trigger performance studies                                                                       |

|   | 2.2      | 2.2.1 EM trigger performance                                                                              |

|   |          | 2.2.1         Livingger performance         12           2.2.2         Tau trigger performance         16 |

|   |          |                                                                                                           |

|   |          | 55 1                                                                                                      |

|   |          | 2.2.4 Trigger performance in heavy ion events                                                             |

|   |          | 2.2.5 $E_{\rm T}^{\rm miss}$ trigger performance                                                          |

|   |          | 2.2.6 Expected trigger rates                                                                              |

|   | 2.3      | Impact on physics                                                                                         |

|   |          | 2.3.1 Higgs physics                                                                                       |

|   |          | 2.3.2 Impact on other physics channels                                                                    |

| 3 | 0.40     | erview of the Existing Readout and Trigger System 33                                                      |

| 3 | 3.1      | Readout electronics                                                                                       |

|   | 3.1      | 3.1.1 On-detector front-end electronics                                                                   |

|   |          |                                                                                                           |

|   | <u> </u> | 3.1.2 Off-detector readout                                                                                |

|   | 3.2      | Level-1 trigger readout                                                                                   |

| 4 | Fro      | nt End electronics 37                                                                                     |

|   | 4.1      | Upgraded front end electronics components                                                                 |

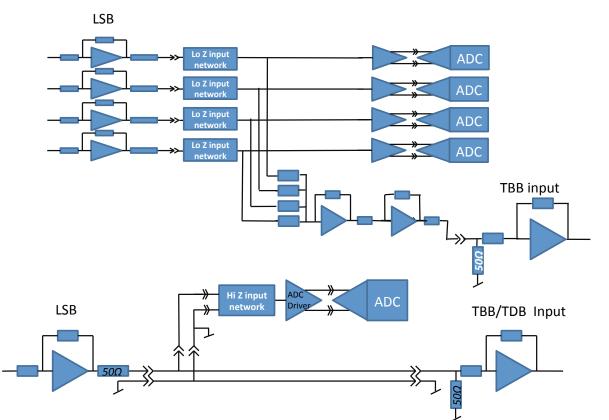

|   |          | 4.1.1 LSBs for the upgraded system                                                                        |

|   |          | 4.1.2 Modifications to the Front End Crate                                                                |

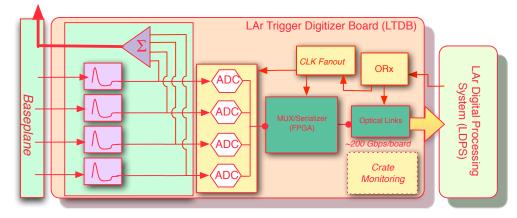

|   |          | 4.1.3 LAr Trigger Digitizer Board (LTDB)                                                                  |

|   |          | 4.1.4 Optical fibers                                                                                      |

|   | 4.2      | System Integration of the FE electronics upgrade                                                          |

|   | 7.2      | 4.2.1 EM Barrel Calorimeter                                                                               |

|   |          |                                                                                                           |

|   |          | 4.2.2 EM Endcap Calorimeter                                                                               |

|   |          | 4.2.3 Hadronic Endcap Calorimeter                                                                         |

|   |          | 4.2.4 Forward calorimeter                                                                                 |

| 5 | Bac      | k End electronics 76                                                                                      |

|   | 5.1      | LAr Digital Processing System Overview                                                                    |

|   | 5.2      | Upgrade Back End electronics components                                                                   |

|   |          | 5.2.1 ATCA platform                                                                                       |

|   |          | 5.2.2 LAr Digital Processing Blade (LDPB)                                                                 |

|   | 5.3      | LAr Digital Processing System Integration                                                                 |

|   | 0.0      | 5.3.1 FELIX                                                                                               |

|   |          | 0.0.1 I LLIA                                                                                              |

|       |            | 5.3.2 Trigger, Timing, and Control                                              |   |

|-------|------------|---------------------------------------------------------------------------------|---|

|       |            | 5.3.3 Infrastructure                                                            |   |

|       |            | 5.3.4 Configuration of FE and BE electronics                                    |   |

|       | 5.4        | Data flow through the BE system                                                 |   |

|       |            | 5.4.1 Digital Super Cell Data from the FE system                                |   |

|       |            | 5.4.2 Data flow to L1Calo                                                       |   |

|       |            | 5.4.3 Data to TDAQ                                                              |   |

|       |            | 5.4.4 Data monitoring on LDPB                                                   |   |

|       |            | 5.4.5 Slow control                                                              |   |

|       | 5.5        | Firmware                                                                        |   |

|       |            | 5.5.1 Firmware on AMC                                                           |   |

|       |            | 5.5.2 Firmware developments                                                     |   |

|       | 5.6        | Signal reconstruction                                                           |   |

|       | 0.0        | 5.6.1 Signal characterization and filter requirements                           |   |

|       |            | 5.6.2 Filter algorithms and performance                                         |   |

|       | 5.7        | Potential variations on the baseline design and compatibility with Phase-II 104 |   |

|       | 5.7        |                                                                                 |   |

|       |            |                                                                                 |   |

|       | - 0        | 5.7.2 Compatibility with Phase II                                               |   |

|       | 5.8        | Conclusions                                                                     |   |

| 6     | Droi       | ect Organization and Milestones 106                                             |   |

| U     | 6.1        | Project organization and management                                             |   |

|       | 0.1        | 6.1.1 LAr Group Representatives                                                 |   |

|       |            | 6.1.2 Management structure                                                      |   |

|       | 6.2        | Deliverables and Cost estimates                                                 |   |

|       | 6.3        |                                                                                 |   |

|       | 0.3        | Schedule and milestones                                                         |   |

|       |            | 6.3.1 Construction                                                              |   |

|       | <b>•</b> • | 6.3.2 Installation and commissioning                                            |   |

|       | 6.4        | Resources and Participating Institutes                                          |   |

| 7     | Sum        | mary 114                                                                        |   |

| ۸.    | know       | ladaomento 115                                                                  |   |

| AC    | KIIOV      | ledgements 115                                                                  |   |

| Th    | e AT       | AS Collaboration 116                                                            |   |

| Re    | eferer     | ces 135                                                                         |   |

| Δr    | opend      | ix-A Super Cell Layout A-1                                                      |   |

| · · r | •          | LAr EM Barrel Calorimeter                                                       |   |

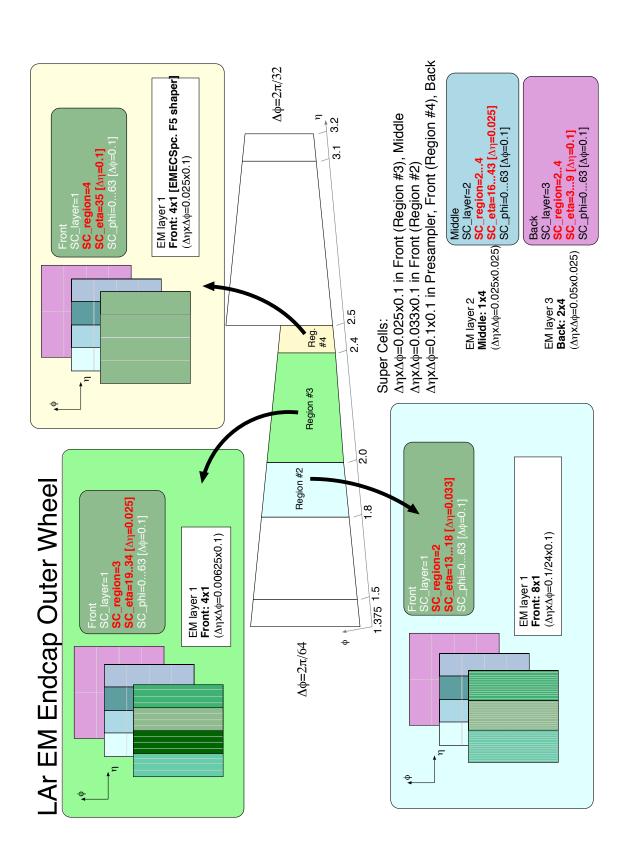

|       |            | LAr EM Endcap calorimeter                                                       |   |

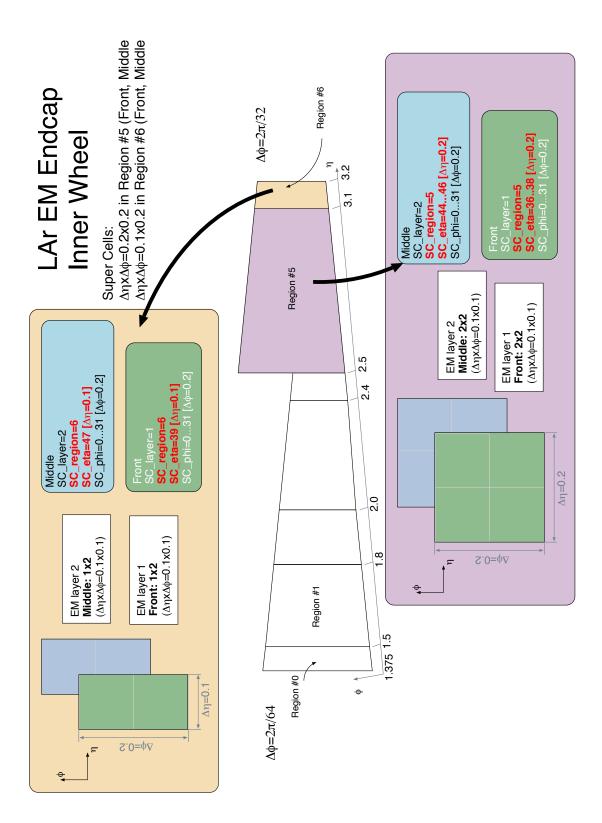

|       |            | LAr Hadronic Endcap calorimeter                                                 |   |

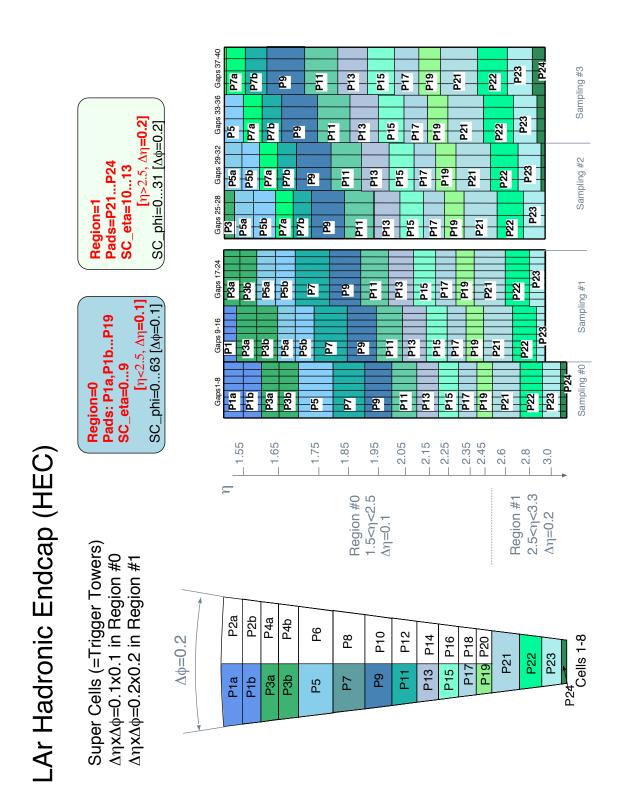

|       |            | LAr EM Forward calorimeter                                                      |   |

|       | A.4        |                                                                                 |   |

| Ap    | openo      | ix-B Legacy front end electronics components B-9                                |   |

|       | B.1        | Front End Board                                                                 |   |

|       |            | B.1.1 Preamplifiers                                                             |   |

|       |            | B.1.2 Shaper ASIC                                                               | 0 |

|       |            | B.1.3 Digitizer for the main readout                                            | 0 |

|       | B.2        | Calibration Board                                                               |   |

|       | B.3        | Tower Builder Board                                                             | 2 |

| B.4<br>B.5 | Tower Driver Board                                  |             |

|------------|-----------------------------------------------------|-------------|

| Append     | dix-C PBS                                           | <b>C–14</b> |

| Append     | dix-D In-situ Demonstrator                          | D–17        |

| D.1        | Motivation, risks, staged approach                  | D–17        |

|            | D.1.1 Motivation                                    | D–17        |

|            | D.1.2 Risks                                         | D–18        |

|            | D.1.3 Staged approach                               | D–18        |

| D.2        | Demonstrator construction, parts used and timetable | D–18        |

|            | D.2.1 Baseplane                                     | D–18        |

|            | D.2.2 LSB                                           | D–19        |

|            | D.2.3 LTDB demonstrator                             | D–19        |

| D.3        | Tests, further review, installation                 | D–21        |

|            | D.3.1 Tests during construction                     | D–21        |

|            | D.3.2 Tests at EMF                                  | D–21        |

|            | D.3.3 Further review                                | D-22        |

|            | D.3.4 Installation and tests on detector            | D-22        |

# 1 Overview of the Phase-I LAr upgrade project

This Technical Design Report details the scientific motivations and the technical implementation of the ATLAS Liquid Argon (LAr) Calorimeter Phase-I upgrade project proposed to enhance the physics reach of the experiment in the high-luminosity environment foreseen in the next 10 years. The scope of the project is to design, build, and install new trigger readout electronics during the second long shutdown (LS2) of the Large Hadron Collider (LHC) in 2018.

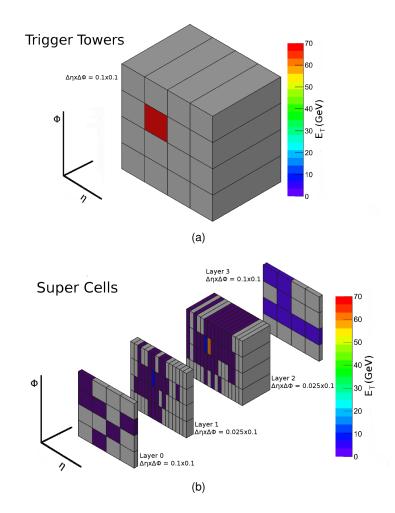

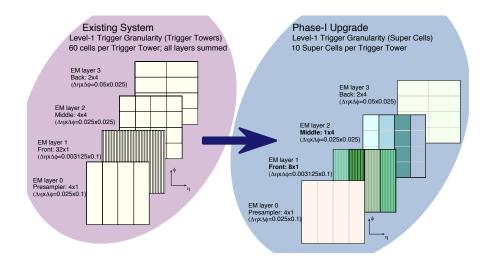

The objective of this upgrade is to provide higher-granularity, higher-resolution and longitudinal shower information from the calorimeter to the Level-1 trigger processors. The 10-fold increase in granularity can be seen in Fig. 1, which compares the energy deposition of an electron in the existing trigger readout system to that of the proposed upgrade system. This upgrade improves the trigger energy resolution and efficiency for selecting electrons, photons,  $\tau$  leptons, jets, and missing transverse momentum ( $E_{\rm T}^{\rm miss}$ ), while enhancing discrimination against backgrounds and fakes in an environment with high instantaneous luminosity, i.e. with a large number of multiple interactions per LHC bunch crossing, or "pileup". As the LHC luminosity increases above the design value, the improved calorimeter trigger electronics will allow ATLAS to deploy more sophisticated algorithms, enhancing the ability to measure the properties of the newly discovered Higgs boson and the potential for discovering physics beyond the Standard Model.

The Phase-I upgrade project is an essential part of a broad upgrade program of the LAr calorimeters through the lifetime of the Large Hadron Collider and is fully compatible with the future Phase-II upgrade program of the ATLAS experiment planned for the third long shutdown (LS3) in 2022 - 2023, as briefly outlined in Secs. 1.1 and 1.4.

## 1.1 LHC baseline roadmap

Probing electroweak symmetry breaking (EWSB) will remain at the core of the physics program at the LHC over the course of the next two decades. This will include as complete an exploration as possible of the Higgs phenomenology with measurements of the couplings to both fermions and bosons and the observations of rare decay modes. Furthermore, the LHC will continue to exploit its unique access to the energy frontier in the search for new phenomena such as Supersymmetry (SUSY), extra dimensions, and other scenarios.

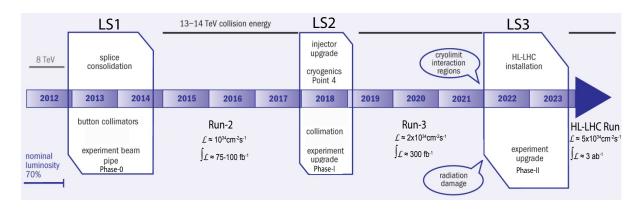

To support and extend the physics program and the discovery reach of the experiments, the LHC complex will be upgraded in three phases, as laid out in the mid- and long-term baseline plan [1] shown in Fig. 2:

- Long Shutdown 1 (LS1): 2013-2014. The ongoing shutdown is used to consolidate machine elements (repairing the magnet splices and upgrading the collimation scheme) in order to achieve the design beam energy and luminosity.

- **Run 2:** 2015 2017. The LHC will collide beams at  $\sqrt{s} \approx 13$  TeV in 2015, and is expected to reach and possibly exceed the design peak luminosity of  $\mathcal{L} = 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>. An integrated luminosity of 75 100 fb<sup>-1</sup> is expected to be delivered to ATLAS and CMS during the 3 years of running in Run 2.

- Long Shutdown 2 (LS2): 2018. The Linac4 will be connected into the injector complex, and the injection beam energy of the Proton Synchrotron Booster will be upgraded in order to reduce the beam emittance. New cryogenics plants will be installed to separate the cooling of the superconducting radio frequency modules and the magnet cooling circuit.

- Run 3: 2019 2021. The LHC design parameters should allow for an ultimate peak instantaneous luminosity of *L* ~ 2.2×10<sup>34</sup> cm<sup>-2</sup> s<sup>-1</sup> (Phase-I operation) and for delivering an integrated luminosity of ~ 300 fb<sup>-1</sup> during Run 3.

**Figure 1.** An electron (with 70 GeV of transverse energy) as seen by the existing Level-1 Calorimeter trigger electronics (a) and by the proposed upgraded trigger electronics (b).

- Long Shutdown 3 (LS3): 2022 2023. The LHC will undergo a major upgrade of its components (e.g. low-β quadrupole triplets, crab cavities at the interaction regions).

- High-Luminosity LHC (HL-LHC): 2024 2030 and beyond. The LHC complex will deliver levelled instantaneous luminosity  $\mathcal{L} = 5 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> (Phase-II operation) and an annual integrated luminosity of 250 fb<sup>-1</sup>, i.e. up to 3 ab<sup>-1</sup> after 12 years of running.

# 1.2 ATLAS upgrade plans up to 2030 and beyond

To optimize the physics reach at each phase of the accelerator complex upgrades, ATLAS has devised a staged program in three phases, corresponding to the three long shutdowns.

The upgrades during LS1 consist of consolidation of the existing sub-detectors including the installation of a fourth (inner) layer for the pixel detector requiring a new, smaller radius central (Be) beam pipe, additional chambers in the muon spectrometer to improve the geometrical coverage, and more neutron shielding in the muon endcap toroids.

After LS2, instantaneous luminosities of  $\mathcal{L} \sim 2.2 \times 10^{34} \text{ cm}^{-2} \text{ s}^{-1}$  are expected with 25 ns bunch spacing and the average number of interactions per crossing will be  $\langle \mu \rangle \sim 60$ . If ATLAS is to exploit this increase in luminosity and maintain a low- $p_{\rm T}$  lepton threshold (~ 25 GeV) in the Level-1 trigger

**Figure 2.** LHC baseline plan 2013 - 2030. The first long shutdown (LS1) is scheduled for the consolidation of the machine elements to achieve design beam energy and luminosity. A second shutdown (LS2) is planned to upgrade the injector system and secure the ultimate LHC luminosity. The third shutdown (LS3) will allow for the installation of new focusing quadrupoles for the HL-LHC. The total integrated luminosity at the end of the HL-LHC lifetime will be approximately 10 times higher than the luminosity expected by the time of LS3. (from Ref. [1]).

while keeping the same trigger bandwidth (100kHz), the development of new detector and readout components are needed [2]. This is the primary motivation of the Phase-I detector upgrades, which include the additional chambers in the forward muon spectrometer, the upgrade of the calorimeter trigger electronics and the installation of new Level-1 trigger processors, a new Level-1 topological trigger processor, and a fast track trigger at the input of the Level-2 trigger system. The performance requirements and design specifications of each upgrade component are defined for  $\mathcal{L} = 3 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> and  $\langle \mu \rangle = 80$  interactions per bunch crossing, to allow some margin in case of further improvements in the LHC peak instantaneous luminosity.

The Phase-II upgrades [3] for the HL-LHC run are motivated by the aging of the inner tracker (primarily because of radiation exposure), by the increased occupancy of the detector systems and data volumes that would saturate the readout links, by the obsolescence of some of the detector sub-system electronics, and by additional requirements that the trigger system will impose on the detector readout in order to cope with the expected luminosity during the HL-LHC era ( $5 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> with  $\langle \mu \rangle = 140$  interactions per bunch crossing). Specifications of each upgrade component are then defined for up to  $\langle \mu \rangle = 200$  interactions per bunch crossing.

## 1.3 Objectives of the Phase-I LAr upgrade project

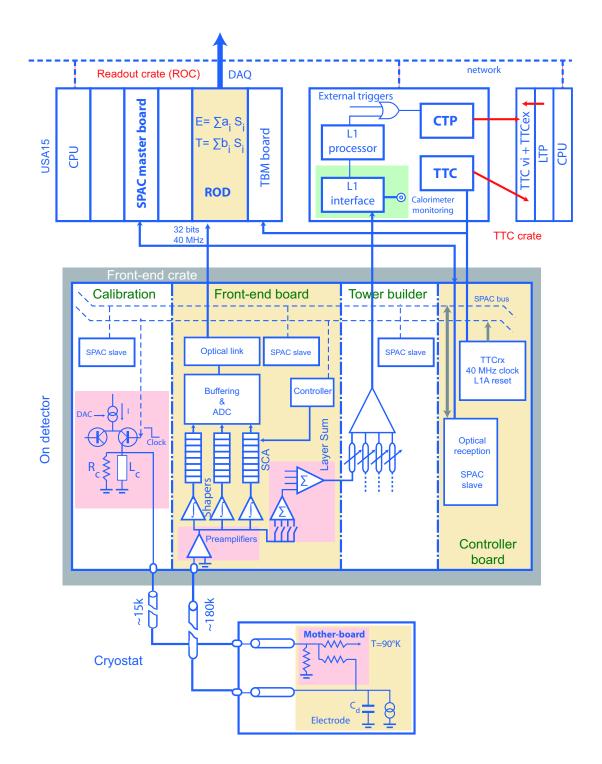

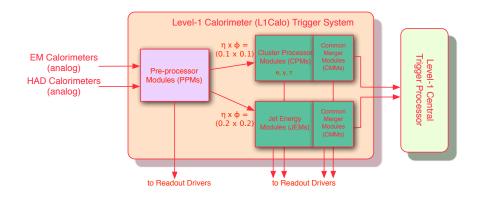

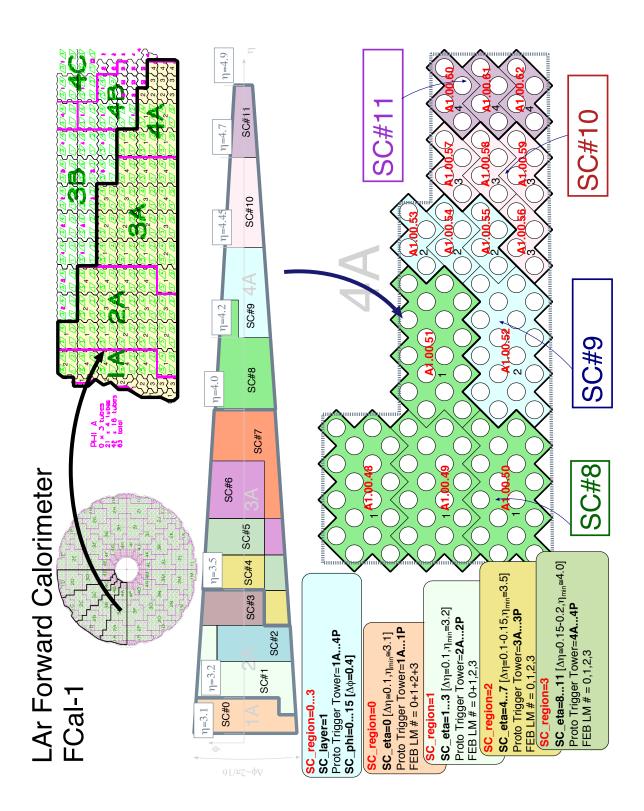

The existing calorimeter trigger information is based on the concept of a "Trigger Tower" that sums the energy deposition across the longitudinal layers of the calorimeters in an area of  $\Delta \eta \times \Delta \phi = 0.1 \times 0.1$ . The Trigger Tower is created through several stages of on-detector analog electronics, whose technical implementation is briefly outlined in Sec. 3.

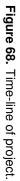

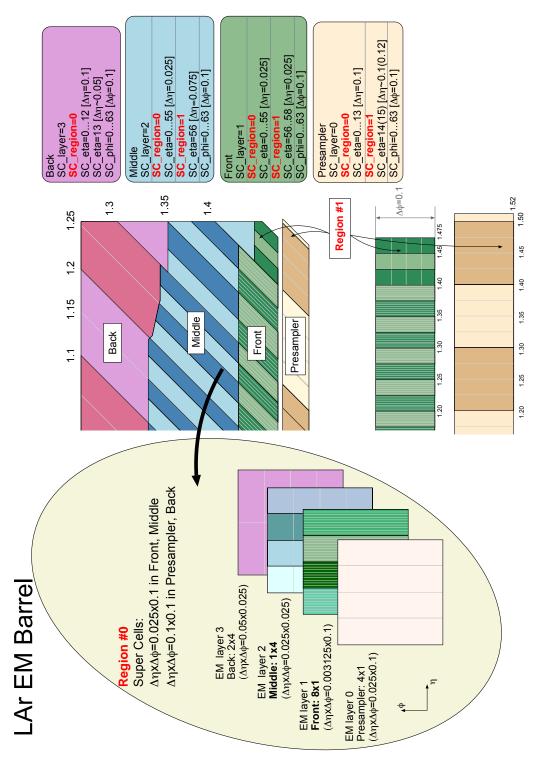

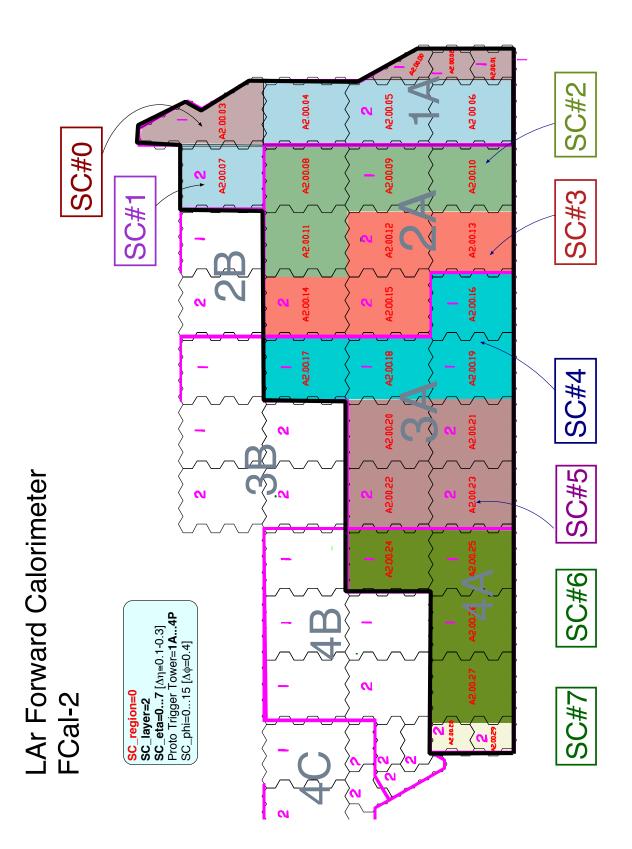

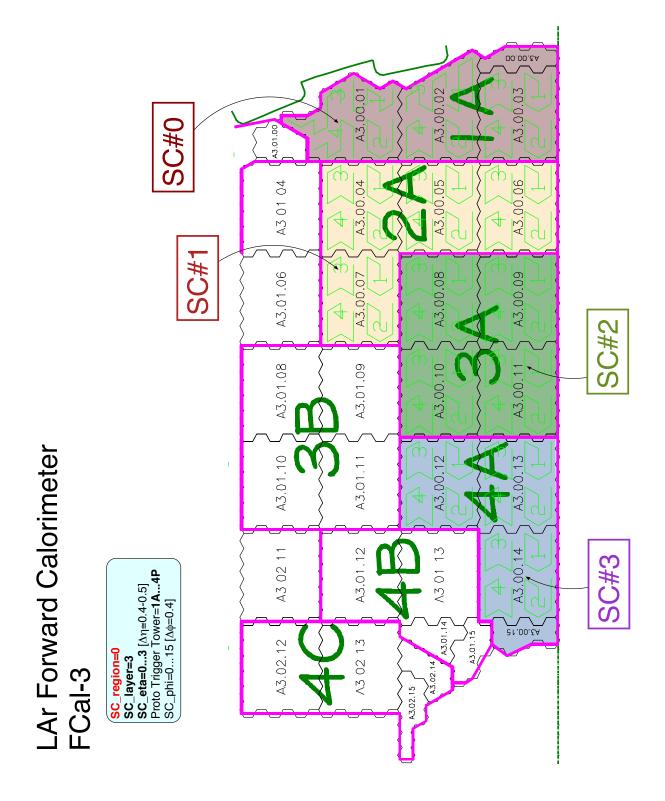

The new finer granularity scheme is based on so-called "Super Cells", which provide information for each calorimeter layer for the full  $\eta$  range of the calorimeter, as well as finer segmentation ( $\Delta \eta \times \Delta \phi = 0.025 \times 0.1$ ) in the front and middle layers of the EM barrel (EMB) and endcap (EMEC) for  $|\eta| \le 2.5$ . This scheme is detailed for the EMB in Table 1 and is illustrated in Figs. 1 and 3. A full description of the geometrical representation of the Super Cells proposed for the entire calorimeter can be found in Appendix A.

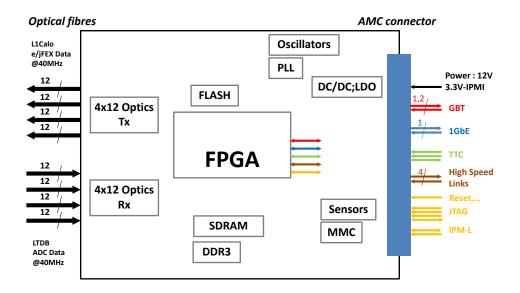

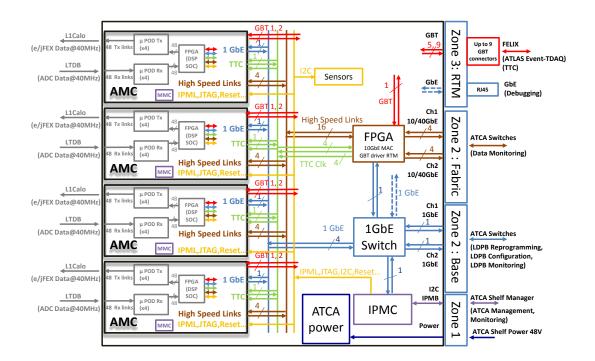

The architecture of the upgraded calorimeter trigger electronics is depicted in Fig. 4, with the upgraded and new components outlined in red. The technical implementation of the upgraded front-

**Table 1.** Comparison of the current Trigger Tower granularity vs. the proposed Super Cell granularity in the LAr EM barrel calorimeter, in terms of both elementary cells and  $\Delta \eta$  and  $\Delta \phi$ . The number of elementary cells grouped for the trigger readout in  $\eta$  and  $\phi$  are indicated by  $n_{\eta}$  and  $n_{\phi}$ , respectively.

|  |       |            | Elementary Cell                | Trigger Tower          |                                | Super Cell             |                                |

|--|-------|------------|--------------------------------|------------------------|--------------------------------|------------------------|--------------------------------|

|  | Layer |            | $\Delta\eta \times \Delta\phi$ | $n_\eta \times n_\phi$ | $\Delta\eta \times \Delta\phi$ | $n_\eta \times n_\phi$ | $\Delta\eta \times \Delta\phi$ |

|  | 0     | Presampler | 0.025 × 0.1                    | 4 × 1                  |                                | 4 × 1                  | 0.1 × 0.1                      |

|  | 1     | Front      | 0.003125 × 0.1                 | 32 × 1                 | 01.01                          | 8 × 1                  | $0.025 \times 0.1$             |

|  | 2     | Middle     | $0.025 \times 0.025$           | 4 × 4                  | 0.1 × 0.1                      | 1 × 4                  | $0.025 \times 0.1$             |

|  | 3     | Back       | $0.05 \times 0.025$            | 2 × 4                  |                                | 2 × 4                  | 0.1 × 0.1                      |

**Figure 3.** Geometrical representation in  $\eta$ , $\phi$  space of an EM Trigger Tower in the current system, where the transverse energy in all four layers are summed (left) and of the Super Cells proposed for the Phase-I upgrade, where the transverse energy in each layer is retained in addition to the finer granularity in the front and middle layers (right). Each square represents an area of size  $\Delta \eta \times \Delta \phi = 0.1 \times 0.1$ .

end and back-end electronics is described in detail in Sec. 4 and 5 respectively.

To provide high-granularity and high-precision information to upgraded trigger processors called Feature EXtractors (FEXs) [4], new LAr Trigger Digitizer Boards (LTDB) are installed in the available spare slots of the Front-End crates. The upgrade of the layer sum boards and of the baseplanes allows the LTDBs to digitize information with granularity up to  $\Delta\eta \times \Delta\phi = 0.025 \times 0.1$  in the front and middle layers of the EM calorimeters. The LTDB also recreates the  $0.1 \times 0.1$  analog sums and feeds them back to the Tower Builder Board (TBB) to maintain the "legacy" system as fully operational. The digitized signals are processed remotely by the LAr Digital Processing System (LDPS) modules, which convert the samples to calibrated energies in real-time and interface to the FEX processors.

Technical Design Report

December 2, 2013

The scope of the ATLAS Phase-I upgrades is limited to a few sub-detectors only. The readout of most of the systems will remain unchanged, limiting the capability of extending some of the parameters of the Level-1 trigger system, like the maximum rate and maximum latency. Reference [5] documents the latency budget assigned to each sub-system. Table 2 details the estimated latency of the components of the proposed LAr Phase-I upgrades. The total latency amounts to 44.2 bunch crossings (BCs). In addition, the Feature Extractor processors require 14 BCs to extract the trigger primitives and transmit them to the Topological processors. The overall 58.2 BC latency of the calorimeter trigger system is consistent with the maximum (65 BCs) value allowed in [5] at the input of the Topological Trigger processors where data from both the calorimeter and the muon trigger modules are combined.

|                                        |     |      | Sub-total [BCs] | Total [BCs] |  |

|----------------------------------------|-----|------|-----------------|-------------|--|

|                                        |     |      |                 |             |  |

| Time-of-flight at $\eta = 2$           | 15  | 0.6  |                 |             |  |

| Cable to pulse preamplifier            | 30  | 1.2  |                 |             |  |

| Preamplifier and shaper                | 10  | 0.4  |                 |             |  |

|                                        |     |      | 2.2             | 2.2         |  |

| Digitization on LTDB                   | 200 | 8.0  |                 |             |  |

| Multiplexing on LTDB                   | 25  | 1.0  |                 |             |  |

| Serializer on LTDB                     | 50  | 2.0  |                 |             |  |

| Optical Cable (70 m) from LTDB to LDPS | 349 | 14.0 |                 |             |  |

|                                        |     |      | 25.0            | 27.2        |  |

| Deserializer on LDPS                   | 50  | 2.0  |                 |             |  |

| Channel Demultiplexing on LDPS         | 25  | 1.0  |                 |             |  |

| Pedestal Subtraction                   | 25  | 1.0  |                 |             |  |

| $E_{\rm T}$ with forward correction    | 125 | 5.0  |                 |             |  |

| Digital summation                      | 50  | 2.0  |                 |             |  |

| Multiplexing $40 - 320$ MHz on LDPS    | 25  | 1.0  |                 |             |  |

| Serializer on LDPS                     | 50  | 2.0  |                 |             |  |

| Optical cable (15 m) from LDPS to FEX  | 75  | 3.0  |                 |             |  |

|                                        |     |      | 17.0            | 44.2        |  |

Table 2. Latency budget for the Phase-I upgrade of the LAr trigger readout electronics

The upgrades aim to better control the trigger rates by improving the selectivity of EM and  $\tau$  objects, the resolution of jets and  $E_T^{miss}$  trigger signatures, and the discrimination power against background emerging from both the out-of-time and in-time pileup. Performance studies and impact on physics analyses are outlined in Sec. 2 of this report and in the complementary TDAQ TDR [4]. Ultimately the project targets are:

- 1. Reduce jet backgrounds in the Level-1 EM trigger by deploying shower shape algorithms and high-precision isolation criteria for electron and photon identification.

- 2. Deploy algorithms currently used in the high-level trigger to improve  $\tau$  identification in the Level-1 trigger.

- 3. Improve the Level-1 jet and  $E_{\rm T}^{\rm miss}$  resolutions and efficiencies to effectively reduce the rates while retaining the same physics acceptance in the offline analyses.

These improvements will be achieved by taking advantage of the higher  $\eta$ -granularity of the Super

Cells compared to Trigger Towers, the layer segmentation, providing longitudinal shower information for the Level-1 trigger, and the higher precision of the energy in the Super Cells due to a smaller quantization scale. Ultimately the goal is to maintain the thresholds of single and multi-object Level-1 calorimeter triggers at values comparable to those used in Run 1 despite the increased centre-of-mass energy, potential instantaneous luminosity up to  $\mathcal{L} = 3 \times 10^{34} \text{ cm}^{-2} \text{ s}^{-1}$ , and pileup up to  $\langle \mu \rangle = 80$ .

To demonstrate the expected performance, an "in-situ Demonstrator" is planned to be installed on a partition ( $\Delta\eta \times \Delta\phi = 1.4 \times 0.4$ ) of the ATLAS LAr EM barrel calorimeter at the end of LS1 (see App. D for more details).

## 1.4 Compatibility with Phase-II upgrades

The long-term plan of the ATLAS LAr calorimeters foresees installation of upgraded trigger electronics in LS2 and replacement of the main readout electronics during LS3 to be able to continue to operate the LAr calorimeter system at its full potential during the HL-LHC era. The radiation levels measured in ATLAS after Run 1 [6] show that the on-detector electronics will be able to survive the integrated luminosity before LS3.

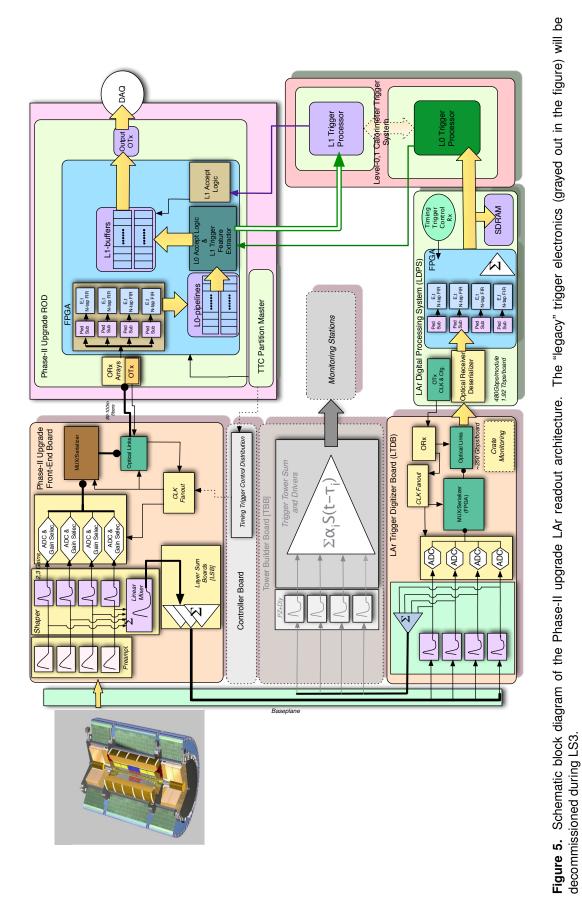

Figure 5 shows the readout architecture planned for the Phase-II upgrades: the Phase-I upgrade components will be maintained during the HL-LHC run, the "legacy" trigger electronics (grayed out in the figure) will be decommissioned, and the main readout electronics will be completely replaced by new front-end boards, which will digitize the signals at each bunch crossing and send them over fast optical links to pre-processor readout modules which will apply full precision calibration and fill trigger pipelines.

This architecture fits naturally in the ATLAS plans described in [3]. The hardware-based first level trigger will be divided into two (Level-0 and Level-1) sub-systems: in the Level-0 trigger the calorimeter trigger "core" is made out of the LTDB, LDPS, and FEX systems installed in LS2 for the Phase-I upgrades, while a Level-1 trigger will access the full granularity detector information to further enhance discrimination against backgrounds.

For these reasons, the Phase-I upgrade project is fully compatible with the overall ATLAS upgrade long-term plans and can be considered the first step of a single, staged upgrade path.

# 2 Physics Requirements and Expected Performance

Probing the details of the electroweak symmetry breaking is among the highest priorities for the LHC experiments after the summer 2012 discovery of a 125 GeV Higgs boson. The Phase-I upgrade of ATLAS will provide an excellent laboratory to make precision measurements of this new particle, in particular its couplings to fermions and electroweak gauge bosons. Additionally, ATLAS will continue to explore the energy frontier in order to address outstanding questions by looking for new physics including supersymmetry (SUSY) and extra dimensions.

The Super Cell trigger readout of the LAr Calorimeter upgrade provides additional information and more powerful tools to the Level-1 trigger feature extraction. These improvements will be essential to maximize the physics potential at the higher instantaneous luminosities and more severe pileup conditions expected after the Phase-I and Phase-II upgrades of the LHC. The motivation and ultimate goal of the upgrade is to improve the performance of the Level-1 single object triggers based on the calorimeter information by (i) enabling the use of shower-shape variables for a more effective identification of electrons, photons and  $\tau$  leptons; (ii) sharpening the EM, jet, and  $E_{\rm T}^{\rm miss}$  efficiency turn-on curves using more advanced reconstruction algorithms at Level-1 and utilizing pileup subtraction techniques on an event-by-event basis (as currently implemented in the offline analyses).

These performance improvements are possible thanks to the following upgrades:

- The calorimeter segmentation available in the Level-1 trigger is made finer using Super Cells as described in Sec. 1.3: groups of calorimeter cells are summed together in the front-end electronics to form areas as narrow as  $\Delta\eta \times \Delta\phi = 0.025 \times 0.1$  in the front and middle layers of the EM calorimeters. Information on the longitudinal shower development the Super Cells provide the transverse energy for each layer in the electromagnetic calorimeter will also become available for the Level-1 trigger decision.

- The digitization precision of the Super Cell signals is improved by at least a factor of 4 compared to the existing Level-1 system: the quantization scale and the dynamic range of the digitizers are optimized in each η-region and for each layer of the calorimeter to achieve sensitivities at the level of the Super Cell electronic noise or better.

- The transverse energy deposited in the Super Cells is calculated at each bunch crossing through optimized algorithms; techniques similar to the optimal filtering currently implemented in the LAr Readout Drivers [7] provide results close to the energy resolution obtained from the offline reconstruction.

In the performance studies presented here, the transverse energy reconstruction in each Super Cell is assumed to be implemented through optimal filtering on the digitized signals of the individual calorimeter cells forming the Super Cell as explained in Sec. 2.1. A detailed comparison of the different signal processing techniques with merit and issues related to the implementation of the algorithms in FPGAs is summarized in Sec. 5.6.

This chapter is structured in three sections. After a brief summary of the transverse energy reconstruction in the Super Cells (Sec. 2.1), Sec. 2.2 summarizes the expected performance for Level-1 trigger objects: electrons and photons,  $\tau$  leptons, jets, and  $E_{\rm T}^{\rm miss}$ . Section 2.3 shows the impact of this upgrade on the event selection and background rejection for a few relevant examples from the LHC physics program.

# 2.1 Super Cell Energy Reconstruction and Resolution

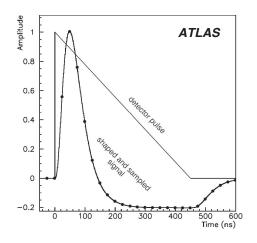

Energy reconstruction in the calorimeter Super Cells aims to extract the energy deposited by particle showers with high precision and assign it to the correct bunch crossing with high efficiency and a low

misidentification rate. To achieve this goal, the pulse shape in the LAr calorimeter must be known to high accuracy. The extensive experience gained in Run 1 with respect to the energy reconstruction and calibration at the level of the elementary calorimeter cells can be directly applied to the Super Cells.

## 2.1.1 Energy reconstruction

The energy deposited in the elementary LAr calorimeter cells is reconstructed through an optimal filtering [7] algorithm based on a linear combination of the signal samples with coefficients that minimize the contribution of electronics and pileup noise (see also Sec. 5.6). This minimization relies on the precise knowledge of the pulse shape and, in particular, of its autocorrelation function, which is attainable with detailed calibration procedures.

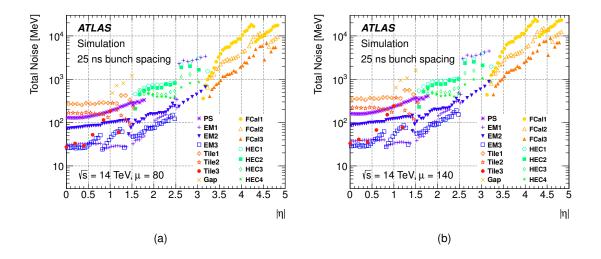

As the luminosity increases, pileup becomes the dominant contribution to the total noise in many regions of the calorimeter. Figure 6 shows the predicted total noise of the cells of the ATLAS calorimeters (LAr and Tile) for the conditions expected during Phase-I (a) and Phase-II (b) operations.

**Figure 6.** Simulated noise (transverse energy per cell) in the various layers of the Liquid Argon and Tile calorimeters as a function of  $|\eta|$  for proton-proton collisions at  $\sqrt{s} = 14$  TeV and a bunch spacing of 25 ns. The average numbers of interactions per bunch crossing (pileup events) are  $\langle \mu \rangle = 80$  (a) and  $\langle \mu \rangle = 140$  (b), corresponding to the nominal Phase-I and Phase-II pileup conditions, respectively.

It is important to emphasize that in all the performance studies described in Secs. 2.2.1–2.2.5, the Super Cell energy is reconstructed by summing the energies of the individual cells belonging to it. This procedure is a good approximation considering that the optimal filtering techniques are a linear estimation of the input deposited energy, the cross-correlation of the electronics noise among cells in a Super Cell is negligible<sup>1</sup>, and the effective pulse shape of the Super Cell signal is similar to the shapes of the individual calorimeter cells. Furthermore, the correlations of the pileup contribution are handled by the simulation. However, this procedure does not take into account any other coherent contribution to the noise fluctuations, or any second-stage noise sources in the readout processing of the Super Cell pulses. For a full and detailed analysis of the performance of the analog signal filtering, the digitization and the digital signal processing will be implemented directly in the Geant4

$<sup>^1 \</sup>text{The coherent noise contributes less than } 10\%$  of the total electronics noise.

simulations. This is an ongoing effort that will be completed after this Technical Design Report is submitted.

#### 2.1.2 Energy Resolution

The high-granularity and high-resolution data provided by the Super Cells will enable the upgraded Level-1 trigger system to reconstruct electromagnetic clusters with improved precision.

The transverse energy ( $E_{\rm T}$ ) in each Super Cell is obtained through an optimal filtering algorithm on the raw input data with a quantization scale of 125 MeV in the middle EM layer and 32 MeV elsewhere. EM clusters are then formed from the Super Cells over an area of size  $\Delta\eta \times \Delta\phi = 0.075 \times 0.2$ ; the optimal size and shape of the clusters will continue to be studied beyond this report. Corrections are applied to each layer<sup>2</sup> and as a function of  $\eta$  to account for the material in front of the calorimeter: a strategy that is only possible with the Phase-I upgrade.

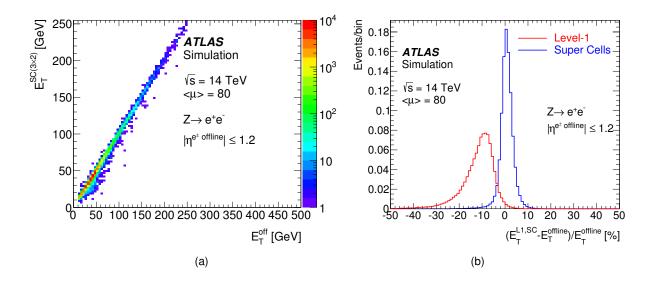

The excellent correlation between the resulting Super Cell cluster  $E_T$  ( $E_T^{SC(3\times2)}$ ) and the transverse energy of the offline reconstructed electrons ( $E_T^{off}$ ) is shown in Fig. 7 (a). Preliminary studies, shown in Fig. 7 (b), demonstrate the significant improvement in the energy resolution using the layer-weighted  $3\times2$  Super Cell cluster  $E_T$  compared to the existing Level-1  $E_T$  ( $E_T^{L1}$ ). This resolution improvement translates into an improved efficiency for EM objects in the trigger for a given offline  $E_T$ , sharpening the turn-on curve and thus making it possible to lower the offline  $E_T$  threshold by several GeV for the same trigger rate.

**Figure 7.** (a) Distribution of  $E_{\rm T}^{\rm SC(3\times2)}$  vs.  $E_{\rm T}^{\rm off}$ , and (b) the percent difference between  $E_{\rm T}^{\rm L1}$  and  $E_{\rm T}^{\rm off}$  (red) compared to that between  $E_{\rm T}^{\rm SC(3\times2)}$  and  $E_{\rm T}^{\rm off}$  (blue) for simulated  $Z \to e^+e^-$  events in the LAr EM barrel calorimeter. The electron candidates are required to be within  $|\eta| \le 1.2$

The dynamic range of the digitized pulses will be optimized for the overall performance by taking into account the impact of noise due to the least significant bit and second stage noise in the amplifiers, and the expected saturation energy. Current studies assume a least significant bit of transverse energy equal to 32 MeV and 125 MeV in the front and middle layer, respectively. This choice of least significant bit has a negligible effect on the resolution while optimizing the dynamic

<sup>&</sup>lt;sup>2</sup>The technical implementation of the layer correction in the FPGA would be through look-up tables and will need to be evaluated to fully assess the impact on the system latency.

range. With a 12-bit range,  $E_{\rm T}$  values up to 102 GeV and 400 GeV in the corresponding calorimeter layers will be properly processed without loss of precision. Very energetic electrons, which have a more concentrated shower than taus or jets, may exceed these values. Additional details of the energy reconstruction using various filtering techniques, as well as a discussion of saturation and bunch crossing identification, can be found in Sec. 5.6.

# 2.2 Level-1 trigger performance studies

The results presented in this section are based on full simulation studies of the ATLAS detector [8] made with Geant4 [9]. The trigger efficiency for the various physics objects (e,  $\tau$ , etc.) is evaluated using samples of signal (e.g.  $Z \rightarrow e^+e^-$  and  $Z \rightarrow \tau^+\tau^-$ ) events overlaid with an average of 80 (unless otherwise stated) minimum-bias events generated with PYTHIA [10], to reproduce the pileup conditions expected in Run 3. Rejection of background and trigger rates are obtained from a sample of overlapping minimum-bias events with  $\langle \mu \rangle = 80$ . The improved resolution provided by the upgraded electronics is included in the studies presented here.

### 2.2.1 EM trigger performance

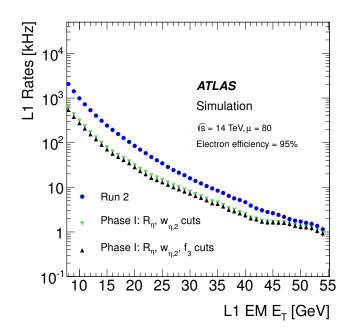

The trigger rates at the LHC design energy and instantaneous luminosity expected in Run 3 will be unaffordable for the relatively low- $p_{\rm T}$  thresholds required by many crucial physics studies unless additional discriminating criteria are introduced to separate electrons and photons from jets. EM showers due to electrons and photons can be effectively distinguished from the background of QCD jets through the use of additional shower shape variables which will become accessible at the upgraded Level-1 trigger thanks to the higher Super Cells granularity, the calorimeter longitudinal layer information and the finer quantization scale. The studies presented below demonstrate a substantial reduction in trigger rates when using these variables, which translates into a possible reduction of the Level-1 trigger threshold by 7 GeV compared to Run 2.

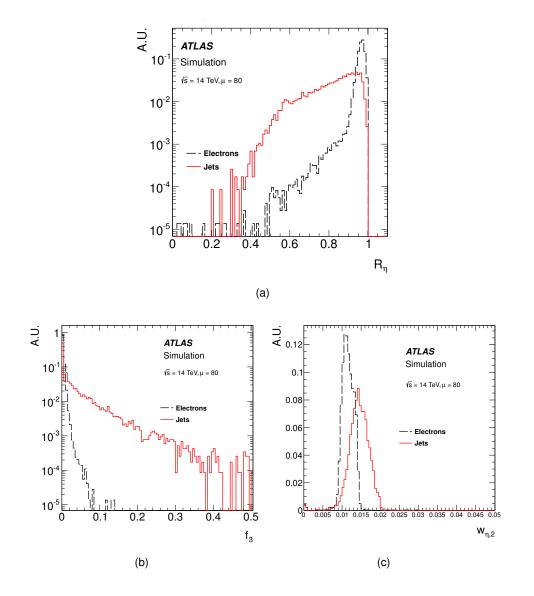

**2.2.1.1 Shower shape analysis** The finer granularity of the Super Cells enables a more sophisticated rejection of jet backgrounds than in the current system through the use of shower shape variables. The performance of the following three discriminating variables (chosen for their importance to offline electron identification) is investigated:

$R_{\eta}$  Given a 3×2 group of Super Cells in  $\eta \times \phi$  centered on the highest-energy Super Cell in the middle layer (2),  $R_{\eta}$  is defined as the transverse energy measured in the 3×2 group divided by the transverse energy measured in a 7×2 group:

$$R_{\eta} = \frac{E_{\mathrm{T},\Delta\eta \times \Delta\phi=0.075 \times 0.2}^{(2)}}{E_{\mathrm{T},\Delta\eta \times \Delta\phi=0.175 \times 0.2}^{(2)}}$$

(1)

$f_3$  The ratio of the transverse energy measured in the back EM layer (3) in an area of size  $\Delta \eta \times \Delta \phi = 0.2 \times 0.2$  to that deposited in all three layers for an EM cluster; the energies in the front (1) and middle (2) EM layers are reconstructed in the area  $\Delta \eta \times \Delta \phi = 0.075 \times 0.2$ :

$$f_3 = \frac{E_{\mathrm{T},\Delta\eta\times\Delta\phi=0.2\times0.2}^{(3)}}{E_{\mathrm{T},\Delta\eta\times\Delta\phi=0.075\times0.2}^{(1)} + E_{\mathrm{T},\Delta\eta\times\Delta\phi=0.075\times0.2}^{(2)} + E_{\mathrm{T},\Delta\eta\times\Delta\phi=0.2\times0.2}^{(3)}}.$$

(2)

$w_{\eta,2}$  The spread of the shower in the middle EM layer (2) in a 3×2 Super Cell region, defined as:

$$w_{\eta,2} = \sqrt{\frac{\Sigma \left(E_{\rm T}^{(2)} \times \eta^2\right)_{\Delta\eta \times \Delta\phi = 0.075 \times 0.2}}{E_{{\rm T},\Delta\eta \times \Delta\phi = 0.075 \times 0.2}^{(2)}} - \left(\frac{\Sigma \left(E_{\rm T}^{(2)} \times \eta\right)_{\Delta\eta \times \Delta\phi = 0.075 \times 0.2}}{E_{{\rm T},\Delta\eta \times \Delta\phi = 0.075 \times 0.2}^{(2)}}\right)^2,\tag{3}$$

where the sums run over the Super Cells.

The separation power of these variables is illustrated in Fig. 8 for electrons from  $Z \rightarrow e^+e^-$  events and background jets. As expected,  $R_\eta$  has a narrow distribution for electrons, close to unity. In comparison, the distribution for jets is much broader. Similarly, the distributions of  $w_{\eta,2}$  and  $f_3$  are typically narrower for EM showers than for hadronic showers.

**Figure 8.** Distributions of variables allowing to distinguish between electrons (black) and jets (red) with  $p_T > 20 \text{ GeV}$  and with the upgraded Level-1 trigger:  $R_\eta$  (a),  $f_3$  (b), and  $w_{\eta,2}$  (c), as defined in the text. Each distribution is normalized to unit area.

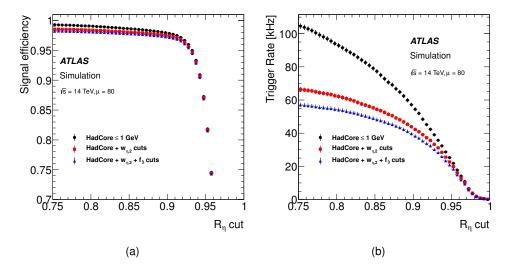

**2.2.1.2 Multi-dimensional optimization of shower shape variables** A multi-dimensional optimization is performed to minimize the trigger rate while keeping a high signal efficiency. This optimization explores the parameter space covered by the discriminating variables  $R_{\eta}$ ,  $w_{\eta,2}$ , and  $f_3$  in minimum bias events. In addition, hadronic isolation ( $HadCore \leq 1 \text{ GeV}$ ) is required for each electron candidate, where HadCore is defined as the transverse energy deposited in a  $\Delta \eta \times \Delta \phi = 0.2 \times 0.2$  region of the hadronic calorimeter behind the EM shower. The trigger efficiencies quoted in this section are derived from simulated  $Z \rightarrow e^+e^-$  signal events. All efficiencies are computed as the fraction of offline electrons with  $p_T > 20$  GeV in the signal sample reconstructed with tight identification requirements [11] that pass the trigger selection. Using this definition of efficiency leads to slightly lower values than obtained with a higher  $p_T$  selection: e.g., requiring  $p_T > 30$  GeV would lead to an approximately 2% higher efficiency.

The dependence of the signal efficiency on the parameter  $R_{\eta}$  is shown in Fig. 9 (a) with the *HadCore* requirement and with successive cuts on optimized values of  $w_{\eta,2}$  and  $f_3$ . Figure 9 (b) shows the corresponding trigger rates as measured from simulated  $\langle \mu \rangle = 80$  minimum bias events. The curves labeled *HadCore*  $\leq 1$  GeV correspond to the present Level-1 trigger without EM isolation.

**Figure 9.** (a) Trigger efficiency as a function of the requirement on the  $R_{\eta}$  variable for a  $p_{\rm T}$  threshold of 20 GeV from  $Z \rightarrow e^+e^-$  events. The curves refer to the present Level-1 trigger (black points) and upgraded Level-1 trigger with various requirements on the  $R_{\eta}$ ,  $w_{\eta,2}$  and  $f_3$  variables. (b) Trigger rate evolution for  $\mathcal{L} = 3 \times 10^{34} \text{ cm}^{-2} \text{ s}^{-1}$  with requirements on  $R_{\eta}$  for electrons with  $p_{\rm T} > 20$  GeV.

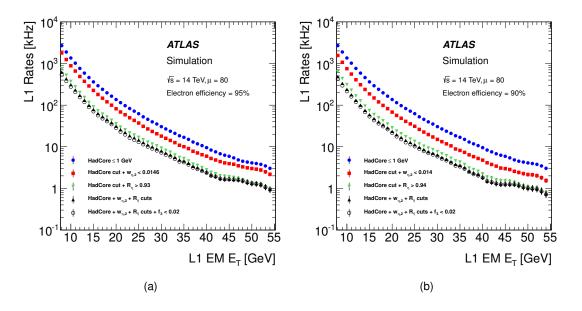

Figure 10 displays the dependence of the trigger rate on  $E_{\rm T}$  threshold for successive selection criteria: *HadCore*,  $w_{\eta,2}$ ,  $R_{\eta}$ , and  $f_3$ . The individual criteria were optimized in all three shower-shape variables. The use of these three new variables to reject jet backgrounds provides a decrease (by up to a factor of 4 for  $p_{\rm T} \sim 20$  GeV) in the trigger rate for the same electron efficiency. The correlations among the three variables clearly do not allow the total gain in trigger rates to be a sum of the individual improvements.

As a result of these studies, the optimized parameters were chosen to be  $R_{\eta} \ge 0.93$  (0.94),  $w_{\eta,2} < 0.0146$  (0.014), and  $f_3 \le 0.02$  (0.02), yielding a trigger efficiency of 95% (90%) and a 20 kHz rate for an  $E_{\rm T}$  threshold of 21.5 (20.5) GeV, respectively. The trigger rates can be further reduced to 15 kHz and 11 kHz by raising the  $E_{\rm T}$  threshold to 24 (22) GeV and 25.5 (24) GeV, respectively. Figure 11 provides a comparison of the Run 2 Level-1 trigger performance to that of the upgraded Level-1 trigger for a 95% electron efficiency in both cases. It shows that for a given bandwidth of

**Figure 10.** Trigger rates for  $\mathcal{L} = 3 \times 10^{34} \text{ cm}^{-2} \text{ s}^{-1}$  as a function of  $E_{\text{T}}$  thresholds with optimized requirements on *HadCore*,  $w_{\eta,2}$ ,  $R_{\eta}$ , and  $f_3$ . Subfigures (a) and (b) correspond to trigger efficiencies of 95% and 90%, respectively, for electrons from simulated  $Z \rightarrow e^+e^-$  decays.

e.g. 20 kHz, the Level-1 threshold, which would need to be 28.5 GeV assuming Run 2 conditions, could be lowered by 7 GeV to 21.5 GeV with the proposed upgrade. On top of this improvement, the better Level-1 EM resolution due to the possible application of layer weights, as shown in Sec. 2.1.2, will substantially sharpen the trigger turn-on curves, resulting in an additional reduction of the offline threshold by several GeV. This translates into a considerable improvement of the signal acceptance for many physics channels, as discussed with a few examples in Sec. 2.3.

It should be noted that the exact values of the parameters  $R_{\eta}$ ,  $w_{\eta,2}$  and  $f_3$  will have to be reoptimized using data to correct for small differences between the simulated shower shapes and those observed in data. The same had to be done for the offline selection criteria for electrons and photons after the first data were recorded in 2010.

**2.2.1.3 Photon performance** A verification of the photon trigger efficiency with the optimized EM shower shape requirements derived in the previous section is needed, given the importance of high-sensitivity measurements of the Higgs boson in the  $\gamma\gamma$  decay mode. Simulated  $H \rightarrow \gamma\gamma$  events with leading photon  $p_{\rm T} > 40$  GeV (as used in the standard ATLAS analysis) have therefore been studied. Table 3 shows the resulting photon efficiencies for the working points derived from the  $Z \rightarrow e^+e^-$  sample. It should be noted that the requirements for  $R_{\eta}$ ,  $w_{\eta,2}$  and  $f_3$  were chosen so as to yield the same electron efficiencies as during Run 1 conditions. This implies that the single photon and di-photon efficiencies will also be very similar.

**2.2.1.4 Clustering algorithms** The studies shown in this document are performed using the present ATLAS clustering algorithms to define EM showers. Similar results are expected with algorithms based on Super Cells, where an initial seed is any Super Cell above 3 GeV in the EM calorimeter with  $|\eta| < 2.5$ . The electron energy is then computed by adding the energy from all EM layers in a  $3 \times 2$  region for  $|\eta| < 1.4$  and a  $5 \times 2$  region beyond. The electron  $\eta$  and  $\phi$  are determined by an energy-weighted average of the Super Cell position.

**Figure 11.** Level-1 trigger rates for a 95% electron efficiency as a function of the EM  $E_{\rm T}$  threshold assuming Run 2 conditions (blue points) and for Run 3 conditions ( $\mathcal{L} = 3 \times 10^{34} \text{ cm}^{-2} \text{ s}^{-1}$ ) for two sets of variables (green and black triangles), as measured from a sample of simulated minimum bias events with  $\langle \mu \rangle = 80$ .

**2.2.1.5 Dependence on quantization scale** With the electronics upgrade, the least significant bit for the front and middle EM layer trigger readouts are lowered to 32 MeV and 125 MeV, respectively, as compared to 1 GeV in Run 2. This increased precision results in improved resolutions and sharper trigger turn-on curves: approximately 1 GeV is gained in the rise from 5% to 98% efficiency.

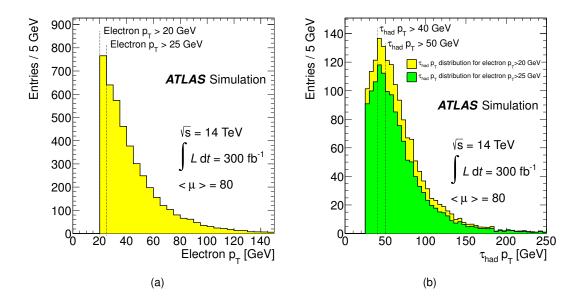

#### 2.2.2 Tau trigger performance

The ATLAS physics program with  $\tau$  leptons includes Higgs boson studies in the di- $\tau$  channel, several electroweak measurements, searches for Supersymmetric particles and other new physics processes. Approximately 65% of  $\tau$  decays are hadronic, indicated here as  $\tau_{had}$ , with one neutrino and one or more hadrons. The challenge at the trigger level, especially at the low- $p_{T}$  values required by

**Table 3.** Photon efficiencies and corresponding electron efficiencies for various sets of (optimized) requirements on the parameters  $R_{\eta}$ ,  $w_{\eta,2}$ , and  $f_3$ . The photon (electron) efficiencies are calculated for photons (electrons) with  $p_{\rm T} > 40$  GeV ( $p_{\rm T} > 20$  GeV).

| Variables                   | Optimized Values                                   | Single Photon | Di-Photon  | Electron   |

|-----------------------------|----------------------------------------------------|---------------|------------|------------|

| variables                   | Optimized values                                   | efficiency    | efficiency | efficiency |

| $R_{\eta}, w_{\eta,2}$      | $R_{\eta} > 0.93, w_{\eta,2} < 0.0146$             | 97.5%         | 94.9%      | 95%        |

| $R_{\eta}, w_{\eta,2}$      | $R_{\eta} > 0.94, w_{\eta,2} < 0.014$              | 94.5%         | 88.6%      | 90%        |

| $R_{\eta}, w_{\eta,2}, f_3$ | $R_{\eta} > 0.93, w_{\eta,2} < 0.0146, f_3 < 0.02$ | 95.8%         | 91.9%      | 95%        |

| $R_{\eta}, w_{\eta,2}, f_3$ | $R_{\eta} > 0.94, w_{\eta,2} < 0.014, f_3 < 0.02$  | 92.8%         | 85.8%      | 90%        |

Higgs boson studies, is to distinguish hadronic tau decays from QCD jets.

In the offline analysis,  $\tau_{had}$  reconstruction and identification is based on both tracking and calorimeter information. The track multiplicity is a powerful handle as  $\tau_{had}$  decays mostly give rise to one or three tracks. The calorimeter uses the shape of the energy deposit in both the transverse and longitudinal directions to distinguish the narrow  $\tau$  clusters from the broader jets. Furthermore, the transition radiation information from the TRT provides discrimination between electrons and pions and thus rejection of the electron background.

For the ATLAS Level-1 trigger system, where there is no tracking information available, the entire burden is on the calorimeter system. Given the importance of the longitudinal and transverse shower profiles to discriminate between taus and jets, the increased granularity available with the Super Cells over the present Level-1 trigger towers is expected to be crucial to keep low thresholds on  $\tau_{had}$  decays in the increased luminosity and pileup environment after LS2, hence achieving high sensitivity on Higgs boson couplings measurements and other physics studies involving low- $p_T$  taus.

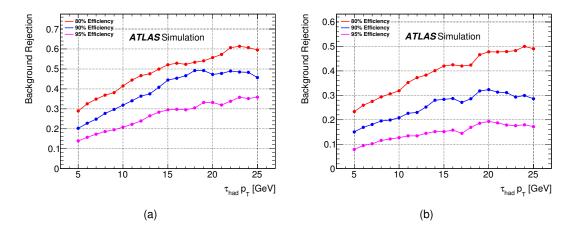

The following studies are based on a simulated  $Z \rightarrow \tau \tau$  sample with  $\langle \mu \rangle = 60$ . The signal efficiency is calculated by matching the Level-1 trigger object to the true  $\tau_{had}$  from the simulation. The background rejection is determined using minimum bias events simulated at  $\sqrt{s} = 14$  TeV, with  $\langle \mu \rangle = 80$ , and 50 ns bunch-spacing. Slight variations in the simulation conditions are not expected to have a large impact on the results.

The variables described below are studied at three operating points that correspond to 80%, 90% and 95% efficiency, respectively. Only the middle layer (2) of the EM calorimeter is used in these studies, with additional rejection power expected from including additional layers.

$f_{core}$  This variable is designed to take advantage of the narrowness of the  $\tau_{had}$  cluster compared to the background jets. The variable builds a numerator and denominator based on the transverse energies deposited within a region up to  $\Delta\eta \times \Delta\phi = 0.4 \times 0.4$ . The numerator is a set of Super Cells that form a subset of the denominator Super Cells:

$$f_{\text{core}} = \frac{E_{\text{T, small area}}^{(2)}}{E_{\text{T, large area}}^{(2)}} , \qquad (4)$$

where the sizes of the small and large areas were optimized to achieve maximum rejection power. Typical values used are:  $\Delta\eta \times \Delta\phi = 0.175 \times 0.1$  for the small area and  $\Delta\eta \times \Delta\phi = 0.275 \times 0.3$  for the large area.

**EM Radius** The EM radius variable  $R_{\text{EM}}$  takes advantage of the distribution of the Super Cells in the cluster, weighted as a function of their energy:

$$R_{\rm EM} = \frac{\sum_{\rm area} E_{\rm T}^{(2)} \times \sqrt{(\eta_{\rm SuperCell} - \eta_{\rm cluster})^2 + (\phi_{\rm SuperCell} - \phi_{\rm cluster})^2}}{\sum_{\rm area} E_{\rm T}^{(2)}} , \qquad (5)$$

where — similar to the variable  $f_{core}$  — the size of the area was optimized to achieve maximum rejection power within an area of  $\Delta \eta \times \Delta \phi = 0.4 \times 0.4$ .

The minimum Super Cell transverse energy entering these variable definitions was also optimized, and the optimal value was found to be 1 GeV. The background rejection for each of these variables is shown in Fig. 12.

The current Level-1 trigger system employs an EM isolation variable, which uses an isolation ring in the middle layer of the EM calorimeter to reject events with significant energy outside the tau

**Figure 12.** The background rejection corresponding to 80%, 90% and 95%  $\tau_{had}$  efficiencies for the  $f_{core}$  (a) and EM radius (b) variables, optimized as a function of the  $\tau$   $p_{T}$ .

cluster core. However, the background rejection using this variable was only 12% for 15 GeV  $\tau_{had}$  candidates in Run 1, and a similar performance is expected in Run 2.

The increased granularity provided by the Super Cells gives a significant additional rejection of the background even with only one additional variable. Using the variable  $f_{core}$  alone, a rejection of nearly 50% can be achieved with a 90% efficiency for 25 GeV  $\tau_{had}$  objects. Studies are ongoing to optimize the performance combining several variables and using the most important physics channels as benchmarks.

#### 2.2.3 Jet trigger performance

The high-luminosity environment in Run 3 and beyond will pose new challenges to jet reconstruction and identification at the trigger level.

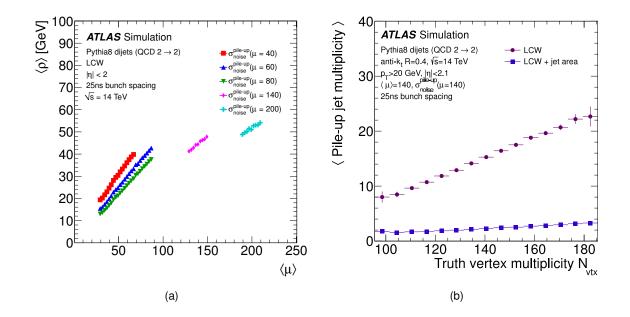

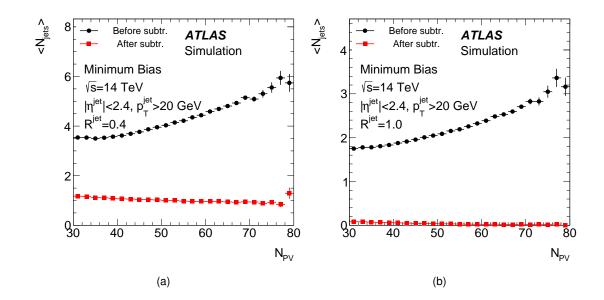

Offline jets in ATLAS are reconstructed from three-dimensional locally calibrated (LCW) clusters [12] of calorimeter cells using the anti- $k_t$  recombination algorithm [13]. The noise used in the clustering algorithm is the sum in quadrature of the electronics noise and pileup noise ( $\sigma_{noise}^{pile-up}$ ). For these studies,  $\sigma_{noise}^{pile-up}$  is recomputed for each  $\langle \mu \rangle$  value. The median  $p_T$  density in an area corresponding to the jet size is used in ATLAS [14] to subtract the pileup contribution to each offline jet  $p_T$ , as proposed originally in Ref. [15].

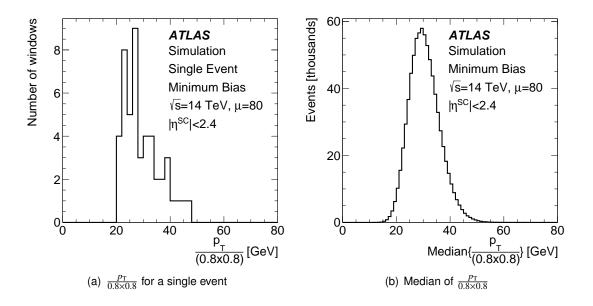

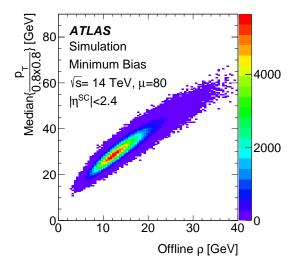

Significantly increased in-time and out-of-time pileup collisions will lead to a dramatically larger event activity than in Run 1, as shown in Fig. 13 (a) for the event-by-event median  $p_{\rm T}$  density ( $\langle \rho \rangle$ ) as a function of the mean number of interactions per bunch crossing. Without a pileup subtraction procedure applied to jet reconstruction, this increased energy per event would result in a linear growth of the multiplicity of jets produced from pileup collisions as a function of the number of vertices ( $N_{\rm vtx}$ ), as shown in Fig. 13 (b). A direct consequence of the increased jet multiplicity from pileup is the increase in overall jet trigger rates, which would reduce the efficiency for high- $p_{\rm T}$  jets of interest from hard scattering due to the limited trigger bandwidth, unless pileup is already subtracted in the Level-1 trigger. In the following, jet reconstruction algorithms expected to be robust against pileup and which can be implemented in the upgraded ATLAS trigger system are discussed.

The jet simulation studies presented in this section use Trigger Towers reconstructed from Super Cells (cells) in the LAr (Tile) calorimeters as the input to jet reconstruction algorithms within  $|\eta| < 2.5$ . The current Level-1 jet trigger is simulated by forming jet elements of the size  $\Delta \eta \times \Delta \phi = 0.2 \times 0.2$

**Figure 13.** (a) Event-by-event median  $p_{\rm T}$  density as a function of the mean number of interactions per bunch crossing in simulated dijet events for R = 0.4 jets. For each choice of pileup noise ( $\sigma_{\rm noise}^{\rm pile-up}$ ), the dependence is approximately linear. (b) Average number of jets ( $p_{\rm T} > 20$  GeV and  $|\eta| < 2.1$ ) reconstructed as a function of the number of true (i.e. from the Monte Carlo generator record) vertices in a simulated dijet sample with  $\langle \mu \rangle = 140$ . The upper (lower) curve corresponds to the distribution before and after pileup subtraction using an event-by-event  $p_{\rm T}$  density.

from the Trigger Towers and running a sliding window algorithm. The sliding window comprises  $4 \times 4$  jet elements, covering an area of  $\Delta \eta \times \Delta \phi = 0.8 \times 0.8$ . The studies presented in the following profit from the finer quantization of the Super Cell energies and make use of global event quantities for pileup suppression which could be calculated in the proposed L1Calo global FEX [4] and applied in the Level-1 topological processor planned for Run 2. The exact implementation of the algorithms presented will need to be worked out in detail. The expected performance results will depend on this technical implementation. The studies here are based on reasonable assumptions which will be verified once the full design is complete.

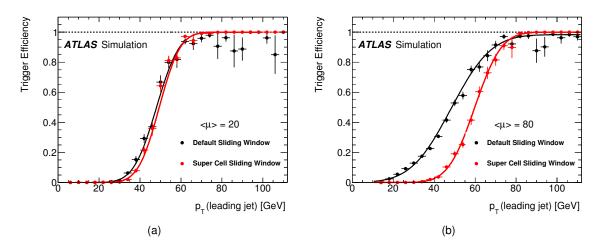

**2.2.3.1** Inclusive Jet and Multijet Trigger Performance The improved energy resolution of the LAr calorimeter upgraded trigger electronics allows for an improvement in the energy resolution of jets reconstructed in the Level-1 trigger system. Figure 14 compares the trigger efficiency as a function of the highest  $p_T$  jet in QCD dijet events between the current and the upgraded systems for a Level-1 jet threshold of 20 GeV. The performance of the Super Cell-based algorithm is comparable to that of the current system in a low pileup environment ( $\langle \mu \rangle = 20$ ), but a clear improvement in the steepness of the turn-on curves is seen in a high pileup environment ( $\langle \mu \rangle = 80$ ) when an algorithm based on Super Cells is used.

The upgraded electronics can also improve the efficiency for triggering on events with many jets (multijet events). This study investigates a particular jet clustering algorithm, called a Gaussian filter

**Figure 14.** The trigger efficiency as a function of the highest  $p_T$  offline jet for  $\langle \mu \rangle = 20$  (a) and  $\langle \mu \rangle = 80$  (b) in simulated QCD dijet events. The performance of the default sliding window algorithm (black points) is compared to that of the sliding window algorithm based on Super Cells (red points) for jets within  $|\eta| < 2.5$ .

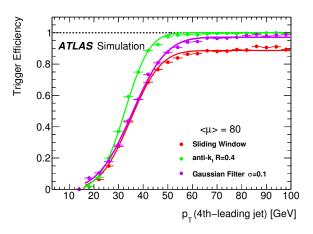

algorithm, that has been used to reconstruct heavy ion collision events in the PHENIX experiment at RHIC [16]. As shown in Fig. 15, the present Level-1 jet trigger system based on the sliding window algorithm displays an inefficiency for multijet triggers at the plateau region, mainly caused by a limited capability to separate jets produced in close proximity to one another. This effect is especially illustrated in  $Z' \rightarrow t\bar{t}$ , where the top quarks are Lorentz-boosted and their decay products are close together. The default algorithm is compared to the anti- $k_t$  algorithm with a distance parameter of R = 0.4 that is used in ATLAS for offline jet reconstruction. Results are also shown for a Gaussian filter algorithm where the value of the standard deviation ( $\sigma = 0.1$ ) is chosen to optimize the jet separation. In contrast to the default sliding window algorithm, the jets reconstructed with the Gaussian filter reach full efficiency in the plateau region and therefore will help to recover current inefficiencies of multijet triggers. Such an algorithm can only be applied to a Level-1 jet trigger based on Super Cells.

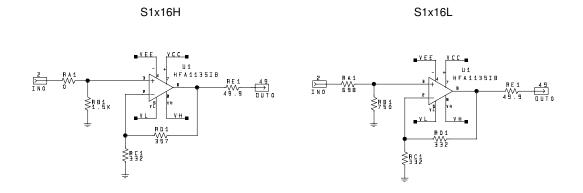

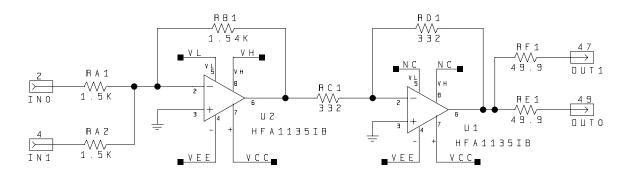

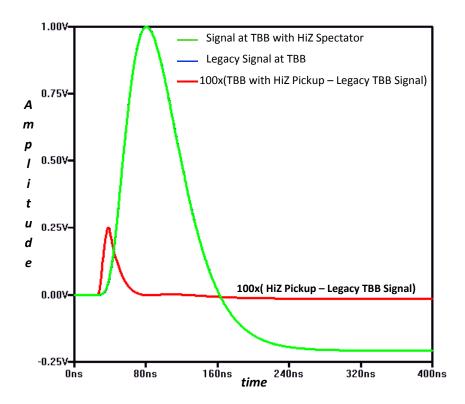

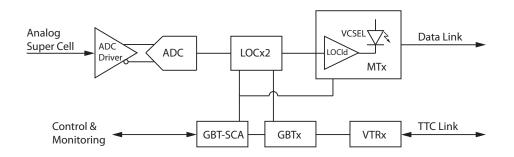

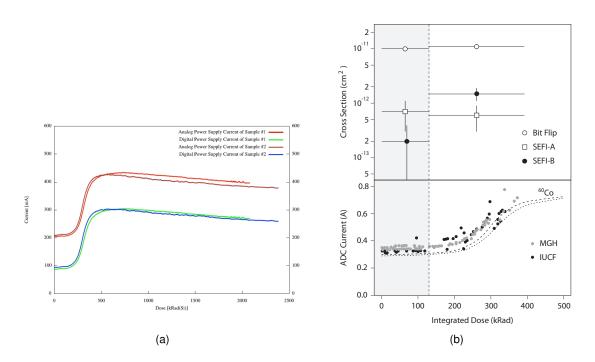

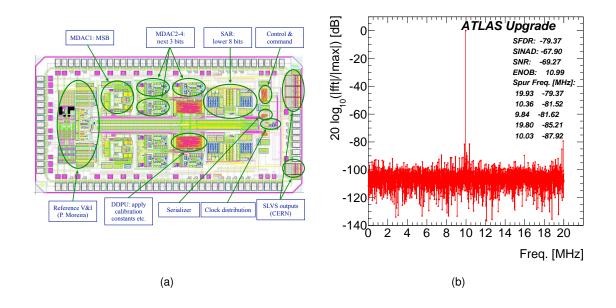

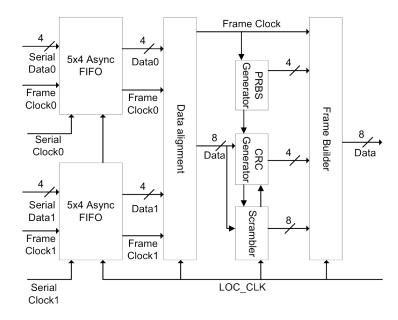

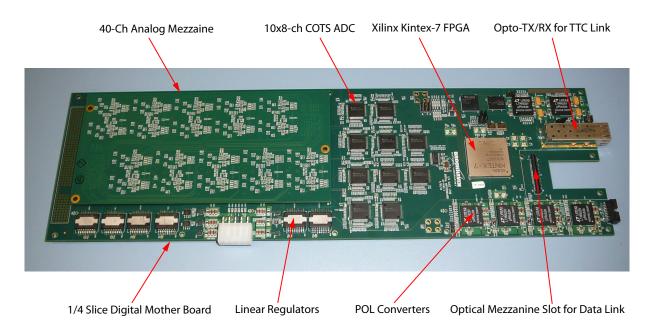

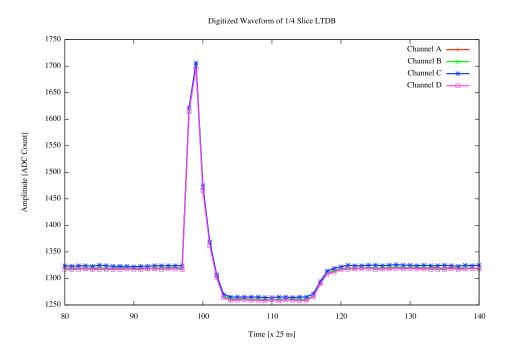

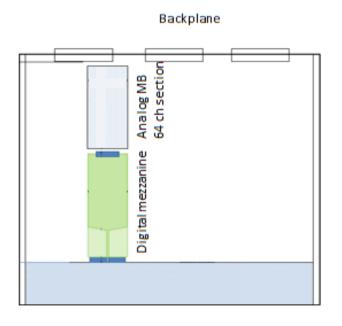

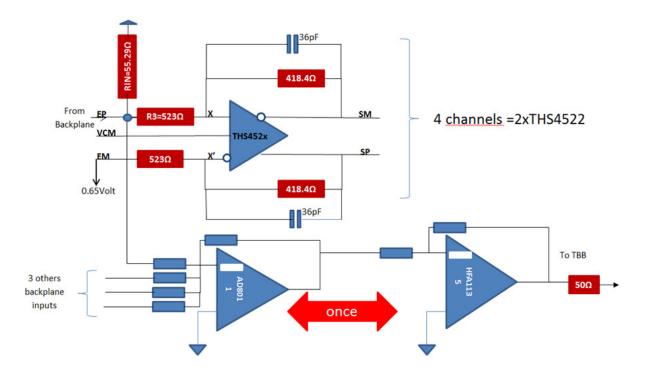

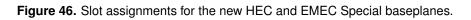

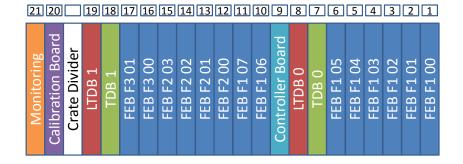

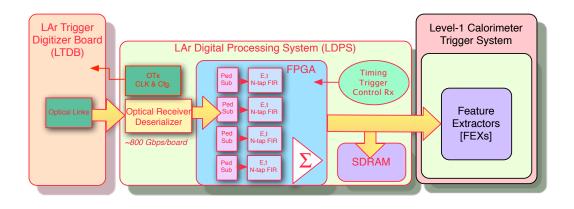

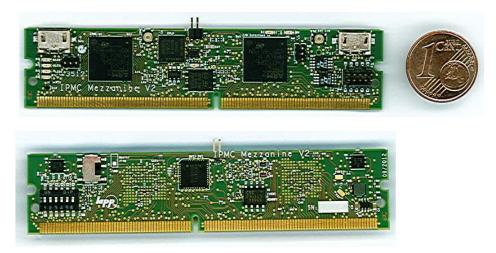

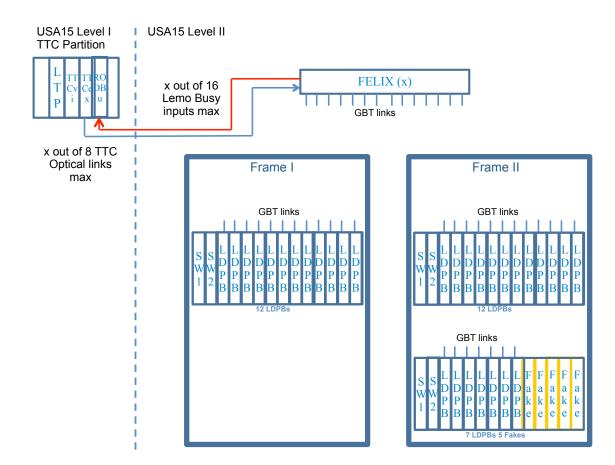

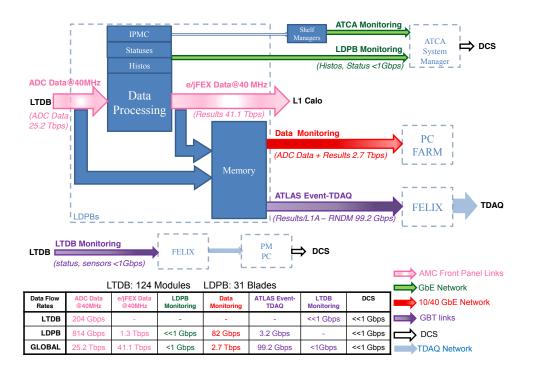

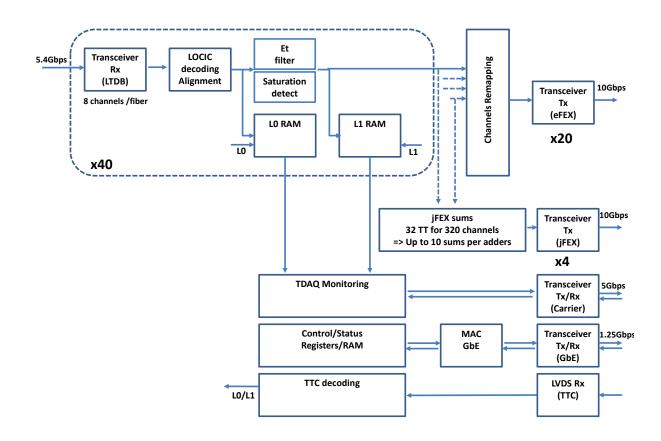

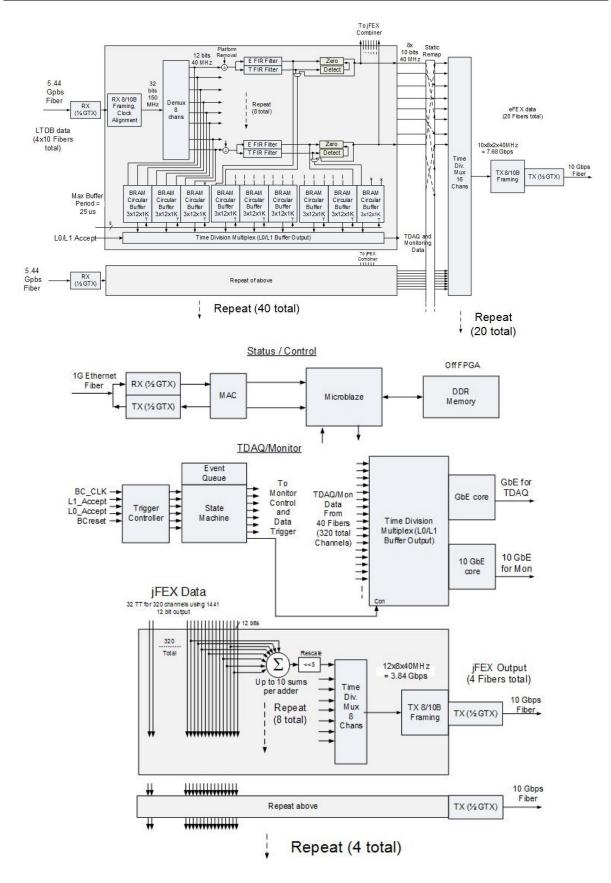

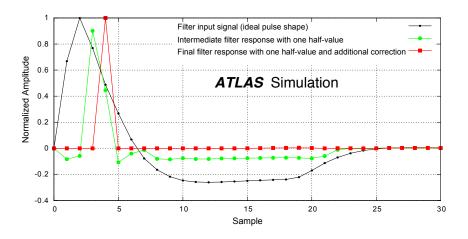

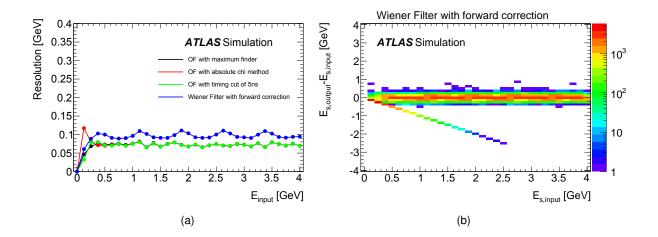

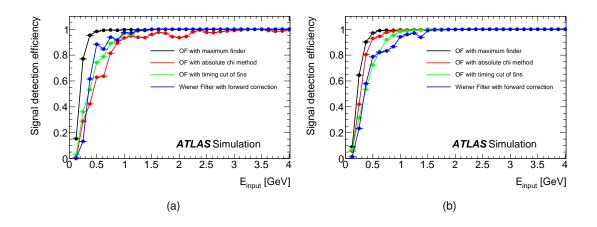

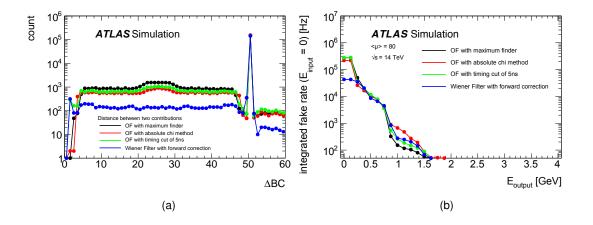

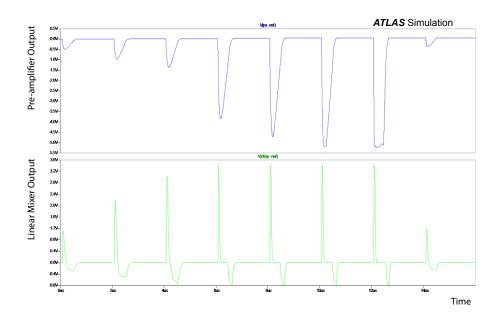

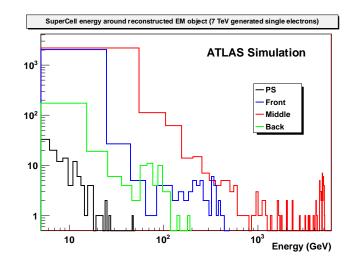

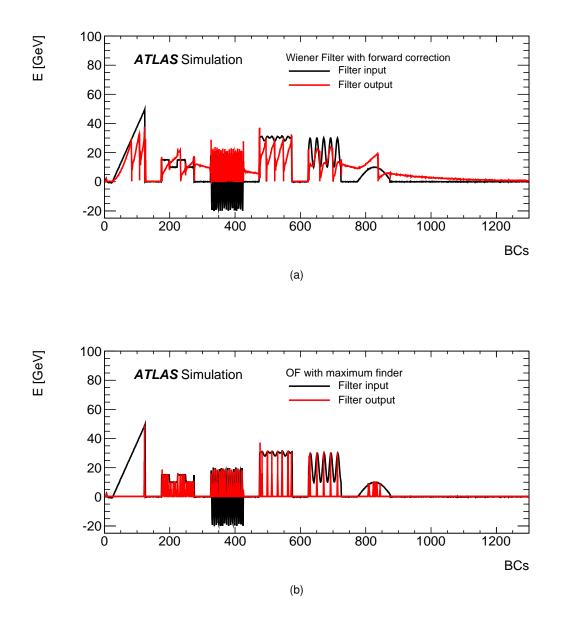

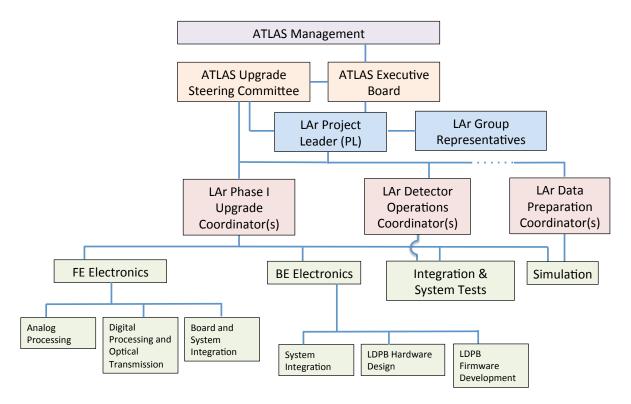

**Figure 15.** The trigger efficiency as a function of the fourth-highest  $p_T$  offline jet for  $\langle \mu \rangle = 80$  in simulated  $Z' \rightarrow t\bar{t}$  events. The Level-1 jet thresholds require four jets with  $p_T > 20$  GeV. The default sliding window algorithm (red points) is compared to a Gaussian filter algorithm (purple points) and the anti- $k_t$  algorithm (green points) for jets within  $|\eta| < 2.5$ .