#### Control and Operation of the LHCb Readout Boards using Embedded Microcontrollers and the PVSSII SCADA System

#### **Stefan Koestner**

on behalf of the LHCb Online Group (email: Stefan.Koestner@cern.ch)

IEEE - Nuclear Science Symposium San Diego, Oct. 31<sup>st</sup> 2006

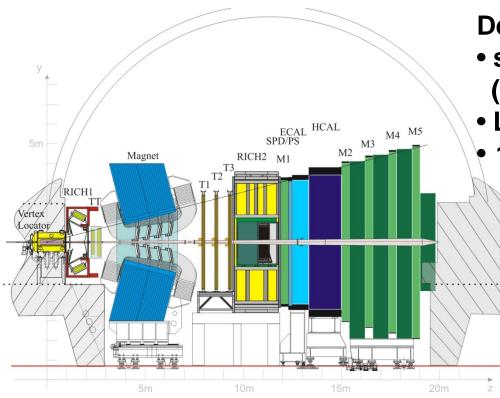

# The LHCb experiment

Dedicated to 'B-physics':

- single arm forward spectrometer (15 - 300 mrad)

- $L = 2 \times 10^{32} \text{ cm}^{-2} \text{ s}^{-1} (\sim 1 \text{ evt/bx})$

- 10<sup>12</sup> bb-pairs (~100 kHz)

fraction of interest just 10<sup>-5</sup> → efficient trigger necessary to enrich the data sample! (implemented in 2 levels)

- Ten sub-detectors with approx. 1.1 million readout channels in total

- average total event size (at average occupancy) is 35 kB (after ZS)

**Stefan Koestner**

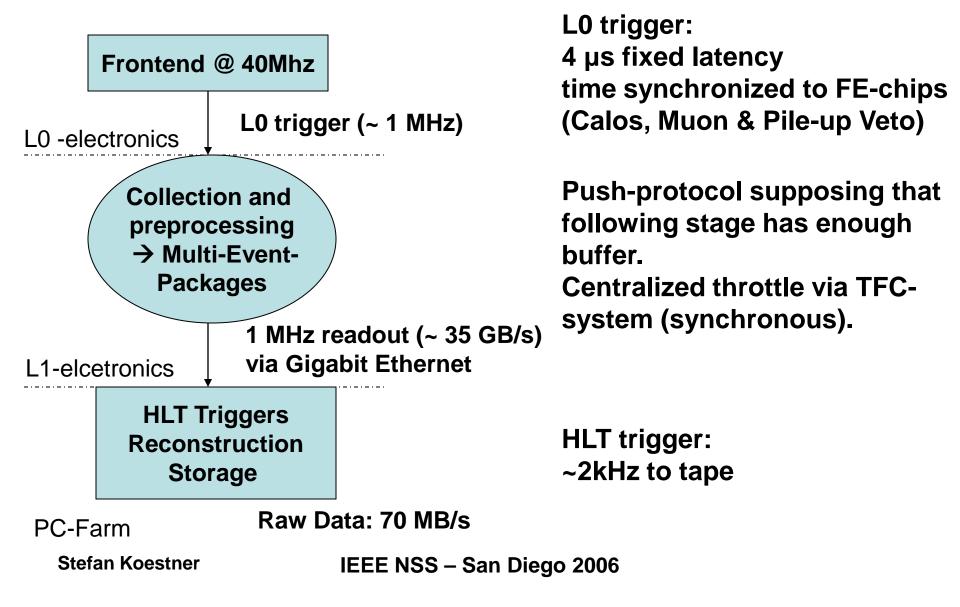

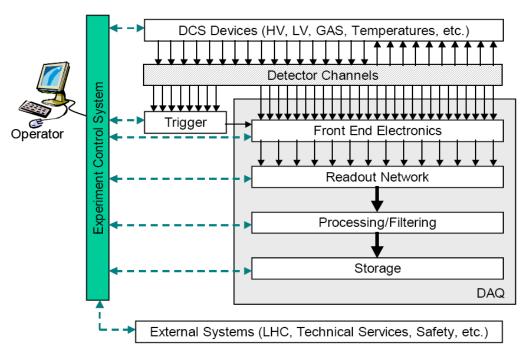

## Trigger and DAQ system

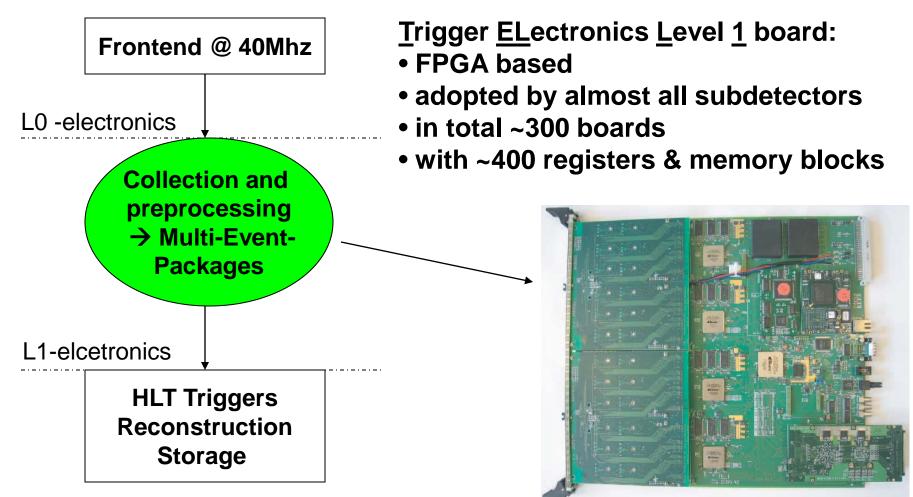

## TELL1 - board

PC-Farm

**Stefan Koestner**

## TELL1 - board

- ADC conversion

- Synchronisation, reordering, pedestal subtraction

- Common mode suppression

- Zero Suppression

- Multi Event Packing

- IP Framing

- Gigabit Ethernet Link

- ECS interface via creditcard sized PC connected to 10/100 Ethernet

- Controls network separated from Data network

- isolated access path  $\rightarrow$  robustness

Stefan Koestner

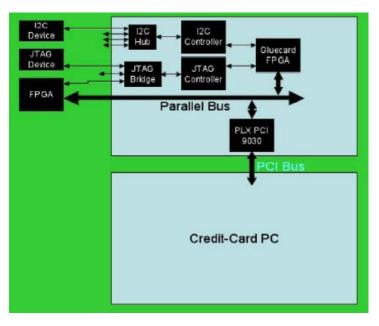

# Credit Card PC

- 4" SM520PCX (Digitallogic) CCPC:

- i486 compatible microcontroller (AMD ELAN 520)

- Linux Kernel at 133 MHz

- reading from local bus 20 MB/s

- filesystem shared over server

Access to board via gluecard over a PLX PCI9030 bridge:

Parallel bus (8/16/32), 3 JTAG chains (2 MHz), 4 I<sup>2</sup>C lines and 9 GPIO lines

| low level libraries | LIBI2CU | LIBJTAG |  |

|---------------------|---------|---------|--|

| under SLC4          | CB_x    | xx.so   |  |

| (maintenance)       | LIBLB   | LIBGLUE |  |

| (maintenance)       | PLX     | driver  |  |

**Stefan Koestner**

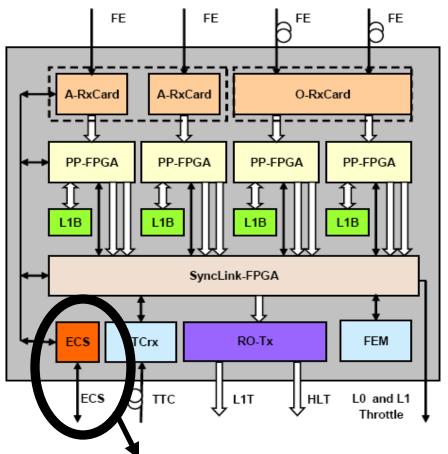

# **Experiment Control System**

A uniform and homogenous control system based on the 'Joint Controls Project' (JCOP) framework - tailored for LHCb needs:

- eases development as well as operation

- distributed and scalable system

- coherent interfaces

Configuration, monitoring and operation of the 'whole' experiment:

- Data acquisition & trigger

- Detector Operations (DCS)

- Experimental Infrastructure

- Interaction with accelerator

& CERN Safety System

# Industrial SCADA (PVSSII)

The CERN's common JCOP framework is built upon an industrial SCADA system: PVSSII

- data (registers or probes) is stored in 'data points' (=complex structures) connected to the PVSS internal memory-DB

- Change of these entries triggers a callback function

- Upon certain thresholds alerts can be launched

Extended to allow for finite state modeling & hierarchical control:

- intuitive model of subsystem

- several levels of abstraction

- sub systems can run alone

- auto-recovery from errors

**Stefan Koestner**

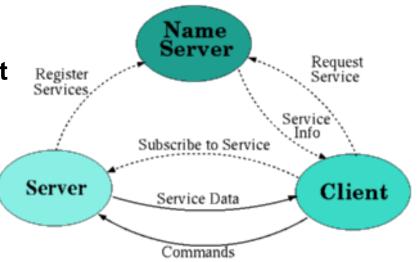

## **Communication Layer - DIM**

Interface from ECS to hardware realized with the 'Distributed Information Management' System (DIM) – a portable lightweight communication layer:

DIM server running on CCPC publishes services to DIM Name Server (DNS) from where the client (ECS) can subscribe to it.

Data exchange peer to peer from server to client.

Client sends commands (write/read) – server updates services (data/status)

- Portability: Clients can be installed on any machine just specifying DNS node (no need to take care of connectivity)

- Robustness: If server crashes it can easily republish on DNS node

Stefan Koestner

IEEE NSS San Diego 2006

## Abstraction Layer - FwHw

| HARDWARE ADVANCED Hardwares (type: TELL1_OT  - myTell1_OT PROM (type: TEMP) TIFPGA (type: TEMPSENS) T2GBE (type: TEMPSENS) TTCRX (type: TTCRX) - PPO (type: PPOT) CHNCTRL (type: CONTROL) | Common settings (hardware: CMNCTRL)       PC     pctell07                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| - myTelll_OT<br>PROM (type: EEPROM)<br>- TEMP (type: TEMP)<br>TLFPGA (type: TEMPSENS)<br>T2GBE (type: TEMPSENS)<br>TTCRX (type: TCRX)<br>- PPO (type: PPOT)<br>CMNCTRL (type: CONTROL)    |                                                                                       |

| PROM (type: EEPROM)<br>- TEMP (type: TEMP)<br>T1FPGA (type: TEMPSENS)<br>T2C6BE (type: TEMPSENS)<br>TTCRX (type: TTCRX)<br>- PPO (type: PPOT)<br>CMNCTRL (type: CONTROL)                  | PC pctell07                                                                           |

|                                                                                                                                                                                           |                                                                                       |

| Create     Remove     Clone       Save as Default Settings     Apply Default Settings       Subscribe     Unsubscribe     View/Recipes                                                    | Save Cancel Defaul                                                                    |

| egisters (hardware: PORTD)  PPResetReg (type: LBUS) PPCtrlReg0 (type: LBUS)                                                                                                               | Specific settings (register: PPCtrlReg1)           LBUS address (hex)         4000008 |

| PPCtrlReg1 (type: LBUS)                                                                                                                                                                   | Type 4<br>Size (words) 1                                                              |

|                                                                                                                                                                                           | Refresh rate (seconds)     0       Data change (0 or 1)     0                         |

| Show registers of type (All)                                                                                                                                                              | Save Cancel Defaul                                                                    |

Introduced a tool to model hardware as PVSSdatapoints:

- hides diversity and complexity of the various hardware/bus types

- takes care of the communication with the Tell1 (using DIM)

- framework function calls by register name

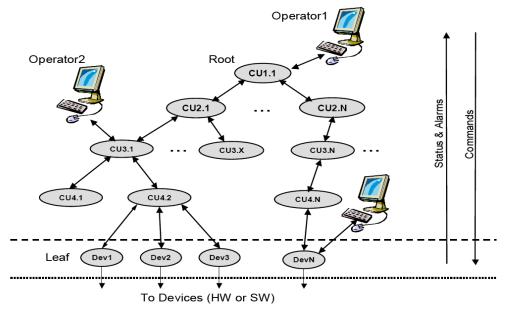

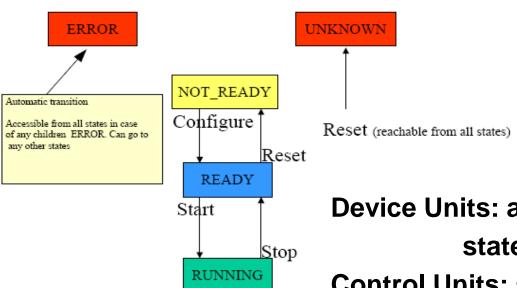

## **Finite State Machines**

Further abstraction as finite state machines (SMI++): defined transition from one state of the board into another with possibility to autorecover

Device Units: act on hardware (data points) state can be triggered by hardware Control Units: send commands to children (DU) state transition when children change

- Firmware can be downloaded to board in state NOT\_READY

- Configuration of board (mainly writing registers) via 'recipes' downloaded from Configuration Database (different settings for different run conditions)

Stefan Koestner IEEE NSS – San Diego 2006

## **Tell1 Control Unit**

#### An example for a Tell1 CU panel (under construction)

| 🕅 Tell1Control: dis                                                                                                                            | t_1:Manager4                                                                                                               |                    |                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sub-System           myTell1_OT           myTell1_VeLo           Velo1           Velo2           OT1           OT2           OT3           OT4 | System<br>Tell1Control<br>State<br>CONFIGURING<br>NOT_READY<br>READY<br>READY<br>READY<br>READY<br>READY<br>READY<br>READY | State<br>NOT_READY | 25/10/2006 01:54:<br>TELL1<br>CONTROL<br>UNIT                                                                                                                               |

| 0T4<br>0T5                                                                                                                                     | READY                                                                                                                      | ×                  |                                                                                                                                                                             |

|                                                                                                                                                |                                                                                                                            |                    | Configuration (Start Up)<br>Choose Device Unit myTell1_OT<br>Assign POF File: D:/tell1_OT_v1.7.pof Send<br>Assign CFG File: D:/OT_v17.cfg Send<br>Send Configuration to ALL |

|                                                                                                                                                |                                                                                                                            |                    | Assign CCPC: pctell07 Send                                                                                                                                                  |

| Messages                                                                                                                                       |                                                                                                                            |                    |                                                                                                                                                                             |

|                                                                                                                                                |                                                                                                                            |                    | Clos                                                                                                                                                                        |

states of children (DUs) define state of CU

commands are propagated downwards

partitioning of the system is a key feature (partitions can have their own trigger)

• clicking on device unit allows to open operator panels for the device (boards)

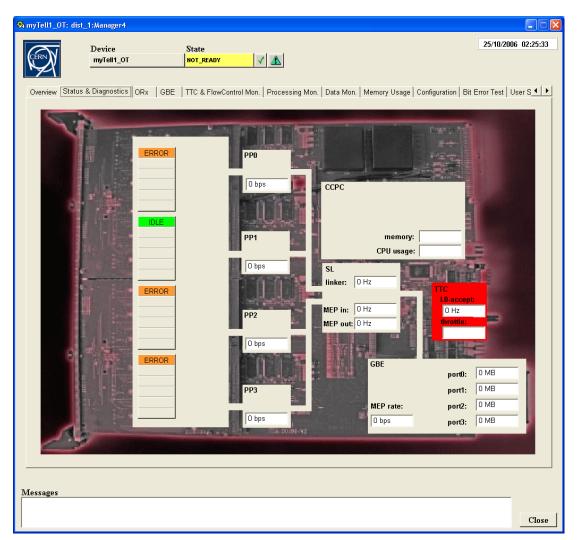

### **Tell1 Device Unit**

#### **Screenshot of a Tell1 DU panel – operator interface:**

| yTell1_OT: dist_1:Ma  | nager4                      |                    |                     |              |                 |                          |                       |                     |

|-----------------------|-----------------------------|--------------------|---------------------|--------------|-----------------|--------------------------|-----------------------|---------------------|

|                       | rice<br>Tell1_OT            | State<br>NOT_READY | 1                   | ′ 🔺          |                 |                          |                       | 25/10/2006 03:01:4  |

| Overview Status & Dia | gnostics ORx GBE            | TTC & Flow         | Control Mon.        | Processing N | lon.   Data Mon | .   Memory Us            | age Configuration Bit | Error Test   User S |

| гнср                  |                             |                    | Temp PP<br>Temp GBE | 27 C<br>21 C | _               | TC: • ORx<br>:PC: • CFG: | flow contr            | ol: OK<br>Jsage: OK |

| Counters              | Hexadeo                     | imal: 🔽            |                     |              |                 |                          |                       |                     |

| LO-Events             | 0x0000000                   |                    |                     |              |                 |                          |                       |                     |

| LO-FE resets          | 0x0                         |                    |                     |              |                 |                          |                       |                     |

| LO-EvCnt resets       | 0x0                         |                    |                     |              |                 |                          |                       |                     |

| BCNCnt resets         | 0x0                         |                    |                     |              |                 |                          |                       | . D. L. W. C.       |

| MEPs transm.          | 0x0000000                   |                    |                     |              |                 |                          |                       |                     |

| MEP factor            | No MEPs sent currently      |                    |                     |              |                 |                          |                       |                     |

|                       | GBE Tx Status GBE ID ASCII: |                    |                     |              |                 |                          |                       |                     |

|                       | More Coun                   | ters               | [MBytes]            | Tx_OK        | Tx_Error        | Link Status              | Dest. MAC             | Dest. IP            |

| Versions              |                             |                    | port 0              | 0 MB         | 0 MB            | Not_OKI                  | 00:02:B3:D4:FB:96     | 11.0.0.14           |

| Frmwr Version         | USR: 0.0 PP: 0.0 S          | L: 0.0             | port 1              | 0 MB         | 0 MB            | Not_OK!                  | 00:02:B3:D4:FB:96     | 11.0.0.14           |

| CFG Version           |                             |                    | port 2              | 0 MB         | 0 MB            | OK!                      | 00:02:B3:D4:FB:96     | 11.0.0.14           |

| Server Version        | 2-2-1                       |                    | port 3              | 0 MB         | 0 MB            | OK!                      | 00:02:B3:D4:FB:96     | 11.0.0.14           |

|                       | More Inform                 | nation             | Tell1 Src IF        |              |                 |                          |                       |                     |

| Configure             | Registers used in Panel     |                    | Source IP           | 11.0.0.15    |                 | Souri                    | e MAC 00:02:83:D4:    |                     |

|                       |                             |                    |                     |              |                 |                          |                       |                     |

| essages               |                             |                    |                     |              |                 |                          |                       |                     |

|                       |                             |                    |                     |              |                 |                          |                       | Clos                |

- identifies board type

- evaluates malfunctioning parts of the board

- quick overview of important counters and registers

- reconfiguration of refresh rate

## **Tell1 Device Unit**

registers (=data points) can be connected to callback functions which allow to evaluate the functionality of subcomponents (inside Ctrl-script)

• error recovery or alerts can be implemented

## **Tell1 Device Unit**

## many panels to monitor registers – grouped in sub panels panels for interaction and

#### reconfiguration of registers AmyTell1\_0T: dist\_1:Manager4 25/10/2006 02:15:28 Device State CERN myTell1\_OT NOT\_READY V 🔥 🕅 myTell1\_OT: dist\_1:Manager4 Overview Status & Diagnostics ORx GBE TTC & FlowControl Mon. Processing Mon. Data Mon. Memory Usage Configuration Bit Er 25/10/2006 02:13:18 -TTC Counters Device State ÇERN mvTell1 OT NOT READY V \Lambda number of SPI3 TX MEP 32 bit 00000000 SPI3 TX packet size 16 bi number of SPI3 TX SOP 32 bi 00000000 Overview | Status & Diagnostics | ORx | GBE | TTC & FlowControl Mon. | Processing Mon. | Data Mon. | Memory Usage | Configuration | Bit Error Test | User S 4 🕨 number of SPI3 TX EOP 32 bit number of TTC triggers 32 bit 00000000 GBE Configuration number of TTC trigger types 32 bi number of TTC dest IP 32 bi 00000000 Port 0 Port 1 Port 2 Port 3 Enable/Disable number of TTC LD-EVID Error 16 bit 0 number of TTC MEP flush signals 8 bit 00 Dest. MAC Scr MAC number of TTC LOFE reset signal 8 bit 08 number of TTC BCNT reset signal 00 8 hi Hex Dest. IP Src IP number of TTC EVCNT reset signal 8 bit 00 C Dec configure configure configure configure configure Scr Flow Control information (only hexadecimal) Throttle cunters Current log All Ports like Port0 configure all Ports cancel all PP-FPGA 0 16 bit FlowCtrl info in SL\_FRAG\_LEN\_FIFO\_ALMOST\_FULL 0 PP-FPGA 1 16 bit FlowCtrl info in SL\_FRAG\_HEADER\_FIFO\_ALMOST\_FULL PP-FPGA 2 16 bit FlowCtrl info in SL FRAG DATA FIFO ALMOST FULL Processing Configuration ECS Configuration 16 hit PP.EPGA 3 FlowCtrl info in SL SEP FIFO ALMOST FULL MEP Buffer 16 bit FlowCtrl info in SL SL INFIFO ALMOST FULLD Info sent by ECS - triggers and all info sent by ECS $\overline{\mathbf{A}}$ Trigger number per DAQ loop FlowCtrl info in SL\_SL\_INFIFO\_ALMOST\_FULL1 Trigger info 16 bit Consecutive trigger numbe FlowCtrl info in SL\_SL\_INFIFO\_ALMOST\_FULL2 Total 00000000 32 bit FlowCtrl info in SL\_SL\_INFIFO\_ALMOST\_FULL3 Wait cycles between triggers (25ns) Dest IP sent by ECS - triggers and all info sent by ECS MEP Factor max 31 ECS - triggers and all info sent by ECS Physics Trigger Type sen by Trigger Type • $\checkmark$ Data Gen Enable ★ disable ped nZS ZS 0 🗸 Bank Class err ✓ enable Error bank cancel configure Messages • Hex C Dec Messages Close

**Stefan Koestner**

# Conclusions

- Presented the basic concepts for implementing the LHCb readout boards into the Experiment Control System with a focus on the various layers and frameworks used

- The system is currently under test for commissioning of the sub-detectors (refinements still ongoing)

- A generic design was of major importance to allow for the usage by different subdetectors and board types

- Further wizards to facilitate board implementation by non experts