CERN LIBRARIES, GENEVA

CM-P00063923

CERN-PRE-78-067

# A FAST AND FLEXIBLE DATA ACQUISITION SYSTEM FOR MULTIWIRE PROPORTIONAL CHAMBERS AND OTHER DETECTORS

J.B. Lindsay, C. Millerin, J.C. Tarlé, H. Verweij and H. Wendler CERN, Geneva, Switzerland

#### ABSTRACT

A system is described which can handle high input rates and provide very short read-out times. The delay element is a twisted-pair cable. ECL 10k circuitry is used throughout, part of which is hybridized. The non-destructive and fast read-out makes the system attractive for experiments with data pre-processing. Typical read-out time is ~ 120 nsec per coded 16-bit data word. One crate contains a maximum of 704 channels, and up to 16 crates may be chained on a branch. Further expansion is possible by the use of several branches. Additional modules provide for the following: reading of multiple branches, multiple outputs of processed data, reading of several systems via one CAMAC interface, normalized data for chamber and cluster identification, and burst buffering.

To be presented at the Wire Chamber Conference, Vienna, Austria, 14-16 February 1978

Geneva - 10 February 1978

## 1. INTRODUCTION

Multiwire proportional chambers (MWPC) in a number of experiments at CERN are subject to high particle intensities. Efficient operation can only be obtained by equipping them with electronics capable of handling high input rates. To take full advantage of high intensities, the read-out of the stored information should take as little time as possible; this will also be advantageous if data reduction or selection or processing before final storage is applied. The system described in the following fulfils these requirements; it accepts high input rates and provides short read-out times.

The configuration of the system is similar to the RM system, described in an earlier report<sup>1)</sup>. In view of the large number of channels required, the receiver and memory circuit has been hybridized to give higher packaging density. Short read-out times have been obtained by applying the ECL 10,000 family of integrated circuits throughout.

The modularity of the system permits many different system configurations. By the replacement or addition of existing modules the system can be extended and the output format can be changed from binary coding to data reduction by clustering or to pattern transfer.

This paper summarizes mainly the read-out aspects of the system; a more detailed description is in preparation.

#### 2. GENERAL DESCRIPTION

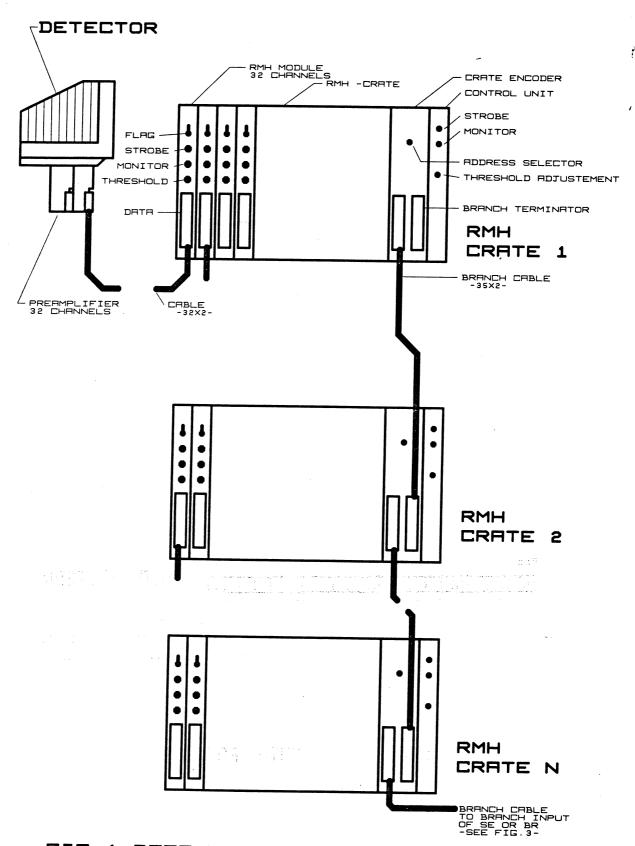

A complete data acquisition chain can be seen in Fig. 1. The preamplifiers, mounted directly on the detectors, are modular (32 channels) and drive a 32-twisted-pair cable which serves also as delay element. The receiver-memory-hybrid modules<sup>2)</sup> (RMH) amplify the received detector signals and, in case of a valid event, strobe them into memory. An RMH contains 32 channels with a hybrid circuit having an amplifier-discriminator for each channel, a threshold voltage input, a flag switch, a strobe input, and a monitor output giving real time

signals. Up to 22 of these modules can be housed in a special crate (RMH crate), composed of CAMAC mechanics equipped with a fast (active) dataway. All stations can be strobed in parallel via the control unit (CU), which also contains the common threshold adjustment, a common monitor output, and fast reset input to reset all RMHs in the crate.

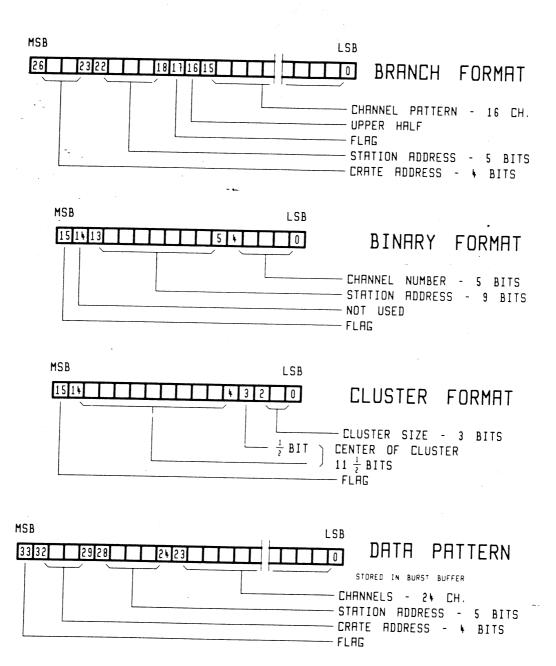

The read-out of the stored information is performed by a crate encoder (CE) in each crate. Up to 16 CEs can be connected to the vertical highway (branch), which is controlled by a system encoder (SE). This permits a maximum of 11,264 channels on a branch. The CE controls the read-out in the crate and encodes the station (module) address; the hit channel patterns are transferred uncoded to the SE. For technical reasons these patterns are only 16 bits wide; data from an RMH are logically divided into lower (LH) and upper halves (UH) -- channels 0 to 15 and channels 16 to 31. Only modules and halves containing data are addressed. Figure 2 shows the format. A "daisy chain" signal (EI) enables the CEs on the branch in the right order, each transmitting its address which is set via the crate address switch. The EI signal only propagates to the next CE if the active CE has transferred all module patterns within that crate.

The SE, which can be housed either in an RMH crate or in a CAMAC<sup>3)</sup> crate, starts the read-out via the start read (SR) signal, received from the external device, such as the CAMAC interface (I/F), processor, etc. Upon request, SE receives branch data in strobed mode and forms for each piece of data a 16-bit binary coded word (Fig. 2). The output data flow is controlled via double handshake mode, thus enabling the system to handle (very) different transmission speeds. The end of read (EOR) signal indicates the completion of an event.

A feature is the possibility of re-reading events several times. Upon receipt of a new SR signal internal logic enables the re-reading of the same event, commencing with the first data word. The system can also transfer incomplete events -- less data words than available in the RMHs -- by use of the SR signal. A discontinuity of SR during data transfer halts SE and internal logic prepares

#### 3.3 Multi-output system

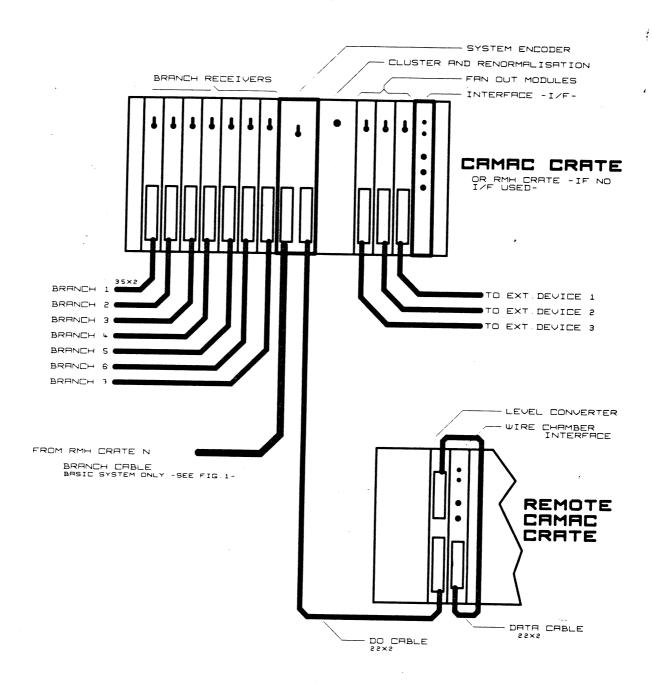

Some experiments demand several data outputs to external devices. The basic system (3.1) provides one separate output (DO) apart from the I/F. Fan-out modules (FO), connected to the internal output bus of the SE, each provide an additional output identical to the DO (Fig. 3). The FOs can either be read in parallel (P), where the slowest external device dictates the conversation speed, or in series (S), one FO after the other, or is not read [disabled (D)] depending on the mode switch (P,S,D).

#### 3.4 System with remote CAMAC crate

In some applications [WA4 <sup>5)</sup>], where the RMH system is remote from the CAMAC system (20 to 80 m) a level converter module (L/C) can be used to translate ECL into TTL signals used by a wire chamber interface (WCI)<sup>6)</sup>, chamber interface (CH/I) <sup>7)</sup> or similar. A twisted-pair cable connects the SE to the L/C, housed close to the WCI (Fig. 3). The read-out will be controlled via the WCI. The SE is placed in two free slots of an RMH crate. This configuration avoids long CAMAC branches.

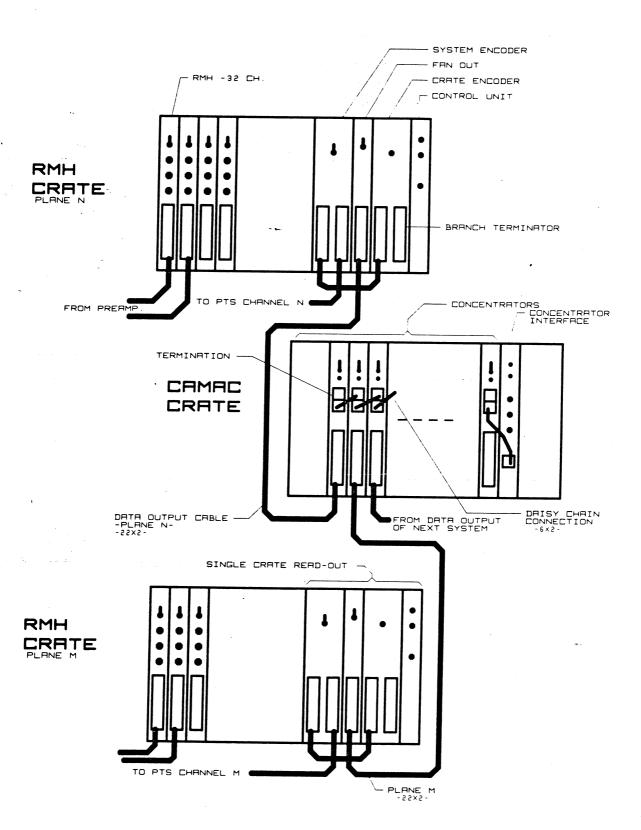

### 3.5 Single crate system for fast read-out

The fastest access to coded data will be via this configuration (Fig. 4). Up to 19 stations can be used within a crate ( $\leq$  608 channels). The SE is connected to an FO unit in order to provide two data output channels. The DO output will be linked to a digital decision system, e.g. using PTS units<sup>8</sup>, to a fast pre-processor or similar device. For a special application [WA6 <sup>5</sup>] data from the FO output will be read into a concentrator unit (C). This configuration may present data from up to 16 systems, each via a C unit, to a concentrator interface (CI). Only CI will be addressed by CAMAC, hence only one DMA transfer has to be set up for many systems. Address capability of a C unit is 1024 channels, the remaining four bits are used for the C address. See Table 1 for transfer speeds.

for a new read-out cycle. The reset signal (RT) enables new data taking by resetting data in all RMHs and logic in all CEs.

The CAMAC interface (I/F) communicates with the SE via the internal output bus. It is designed to perform block transfer operations via the following modes: repeat, pause, or stop mode (see Ref. 4 for details). Re-reading via I/F is possible but only of complete events. The (front-panel) data output connector (DO) of the SE provides fast access to data, for use in fast pre-processors, etc.

Table 1 shows comparisons of read-out times using different configurations.

#### 3. SYSTEM CONFIGURATIONS

#### 3.1 Basic system

This is shown in Fig. 1. Data can also be read via the DO output to, for example, the pre-processor, and re-read into CAMAC via I/F. The I/F is not essential for the operation of the system, if CAMAC is not used. For a full description see Section 2.

## 3.2 Multibranch system

Systems exceeding 11,264 channels or systems for multi-users with different detector configurations will use a multibranch configuration (Fig. 3). The individual branches ( $\leq$  16 crates) are connected to branch receiver modules (BR), which operate onto the internal input bus. BRs are read in a "daisy chain" configuration similar to the CEs. Three different operating modes are possible: disable, normal, or first (D,N,F) depending on a switch. Position F indicates that the branch connected to that BR will be read first, the BRs to the right of it are read if they are in mode N, the remaining BRs (to the left) are not read, including BRs in mode D. The maximum number of 18 BRs can be connected to the system, giving access to  $\leq$  202,752 channels.

## 3.6 Systems with other output formats

## 3.6.1 Clustering and renormalization

In experiments with a high probability of adjacent hits [WA7 5)] a reduced number of data transfers is desirable. The cluster and renormalization module [CRN] 9) will modify the binary coded data from the SE output bus as follows:

- a) Consecutive channel addresses (cluster) will be compressed into a cluster word containing the centre address and the cluster size. The addressing capability is then reduced to 2048 channels.

- b) Data are also renormalized, meaning that each chamber plane will start at address zero. Plane markers are made by use of the flag switches of the RMHs.

A CRN, designed by L. Rossi, INFN, Genoa, will be placed between the SE and the FOs (Fig. 3) and provide an output to the FO bus similar to that of the SE, but with the cluster format.

# 3.6.2 <u>Use of the RMH system for photomultipliers:</u> burst buffering as an application of data pattern transmission

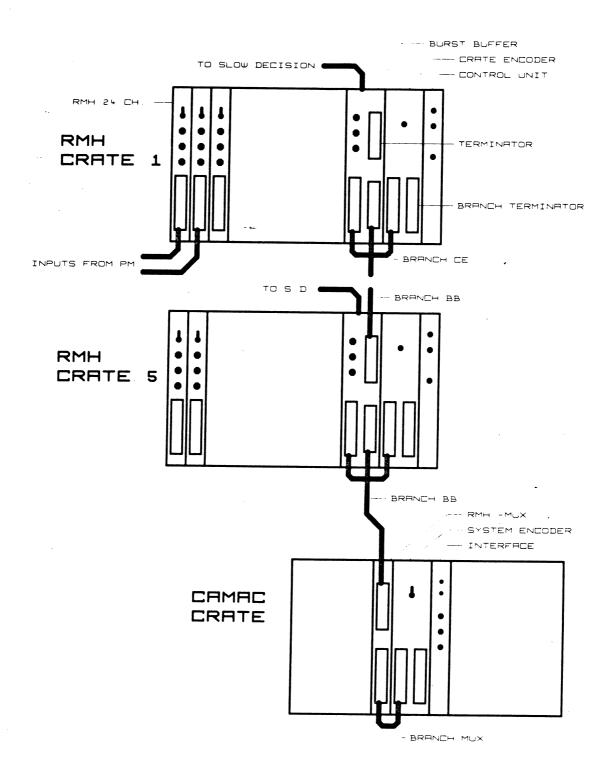

In a particular case [WA18 <sup>5)</sup>] a 24-channel version<sup>10)</sup> of the RMH is used with incorporated auto-reset function. A prime necessity is also the fastest possible reading and storing of detector data. Binary coding of single hits proved too slow for this task, especially if many channels within an RMH are hit. The method of data pattern transfers from the RMHs via the CE to a burst buffer module (BB) was used (Fig. 5). It is faster because a pattern can contain more than one hit channel thus saving transmission time. A disadvantage is the necessity for a large number of bits in a data word (pattern, station and crate address give 30 bits) (Fig. 2). The BB receives the pattern containing hits from the RMHs and stores them in the memory which is able to store up to 40 events within a burst. The complete pattern is available on a connector and can be used as input to a slow-trigger-logic box<sup>11)</sup> or for testing. A reject signal (REJ) enables the overwriting of the last event with new data. Up to 5 BBs can be connected in a "daisy

chain" configuration via the RMH multiplexer (RMH-MUX) to a single SE. After completion of a burst, events with identical event numbers will be read out from each BB in sequence, thereby maintaining the chronological order of event data.

The SE codes the data in binary and transfers them via the I/F into CAMAC.

This configuration demonstrates the flexibility of the RMH system philosophy and shows its application as an economic discriminator and pattern unit for photomultiplier signals.

## 3.7 Other configurations

Of course many more system configurations can be built from the elements of this system, for example, Multibranch - multi-output with clustering and renormalization  $[WA7^{5}]$ , etc.

### Acknowledgements

We would like to thank the following experimental teams for their co-operation and most valuable comments as first users of the system in experiments:

WA4 (J. Litt et al.), WA6 (G. Fidecaro et al.) and WA7 (A. Lundby et al.).

#### REFERENCES

- 1) J. Lindsay, Ch. Millerin, J.C. Tarlé, H. Verweij and H. Wendler, A general purpose amplifier and read-out system for multiwire proportional chambers, CERN 74-12 (1974).

- 2) J.C. Tarlé and H. Verweij, RMH module, type 4236, Technical Specifications, CERN, NP Division (1975).

- 3) ESONE Committee, CAMAC, A modular instrumentation system for data handling, EUR 4100e (1972).

- 4) Block transfers in CAMAC systems, TID-26616 (Energy Research and Development Administration, Washington, 1976).

- 5) Experiments at CERN in 1977 (Ed. J.V. Allaby), (CERN, Geneva, 1977).

- 6) J. Lindsay and H. Wendler, Wire chamber interface, Type 134, CERN CAMAC Note 55-00 (1974).

- 7) H. Wendler, Chamber interface, Type 160, CERN CAMAC News No. 13 (1978).

- 8) I. Pizer, J. Lindsay and G. Delavallade, Programmable track selector for nuclear physics experiments, presented at this conference.

- 9) L. Rossi, A fast clustering processor for multiwire proportional chamber read-out, INFN Genoa, Int. Rep. 78/2 AEB 104.

- 10) J.C. Tarlé and H. Verweij, RMH module, Type 4248, Technical Specifications, CERN, EP Division (1977).

- 11) M. Letheren, WA18 slow trigger logic box, private communication.

Table 1

Data transfer times

| System           |                    | Maximum read-out and encoding times per data word (nsec) |                |                     |                       |                           |                       | Limitations                 |

|------------------|--------------------|----------------------------------------------------------|----------------|---------------------|-----------------------|---------------------------|-----------------------|-----------------------------|

| Туре             | Read-out<br>via    | T <sub>0</sub>                                           | T <sub>1</sub> | T <sub>N</sub>      |                       | T <sub>E</sub>            |                       |                             |

|                  |                    | No data                                                  | First word     | Next word           |                       | No more<br>words          |                       | Response of external device |

|                  |                    |                                                          |                | Same<br>crate       | Any<br>other<br>crate | Same<br>crate             | Any<br>other<br>crate | ≤ 30 nsec                   |

| Single<br>branch | External<br>device | 160                                                      | 210            | 100                 | 200                   | 80                        | 100                   | ≤ 16 crates                 |

| Multi-<br>branch | External<br>device | 1050                                                     | 1150           | 200                 | 990                   | 100                       | 880                   | ≤ 70,000 channels           |

| Single<br>crate  | External<br>device | 80                                                       | 160            | 120                 | _                     | 80                        |                       | ≤ 608 channels              |

| Burst<br>buffer  | Burst<br>buffer    | 75                                                       | 140-220*)      | 80-160*)            | _                     | 75                        | -                     | ≤ 480 channels              |

| Any<br>system    | CAMAC              | Within start of read-out cycle                           |                | Every read<br>cycle |                       | Within last<br>read cycle |                       | –                           |

## \*) Data one half to both halves.

Read-out times: a) No data in system:  $T = T_0$

b) Data in system:  $T = T_1 + N \times T_N + T_E$  N is the number of hits (exception: burst buffer, where N is the number of modules containing data).

## Figure captions

Fig. 1 : Data acquisition chain

Fig. 2 : Data formats

Fig. 3 : System and extensions

Fig. 4 : Single crate system

Fig. 5 : Burst buffer system

FIG. 1 DATA ACQUISITION CHAIN

FIG.2 DATA FORMATS

BOLD DRAWN UNITS AND CABLE GIVE BASIC SYSTEM CONFIGURATION

FIG. 8 SYSTEM AND EXTENSIONS

FIG. 4 SINGLE CRATE SYSTEM

FIG. 5 BURST BUFFER SYSTEM