# System Integration Issues of DC to DC converters in the sLHC Trackers

B. Allongue<sup>a</sup>, G. Blanchot<sup>a</sup>, F. Faccio<sup>a</sup>, C. Fuentes<sup>a,b</sup>, S. Michelis<sup>a,c</sup>, S. Orlandi<sup>a</sup>

<sup>a</sup> CERN, 1211 Geneva 23, Switzerland <sup>b</sup> UTFSM, Valparaiso, Chile <sup>c</sup> EPFL, Lausanne, Switzerland

### georges.blanchot@cern.ch

#### Abstract

The upgrade of the trackers at the sLHC experiments requires implementing new powering schemes that will provide an increased power density with reduced losses and material budget. A scheme based on buck and switched capacitors DC to DC converters has been proposed as an optimal solution. The buck converter is based on a power ASIC, connected to a custom made air core inductor. The arrangement of the parts and the board layout of the power module are designed to minimize the emissions of EMI in a compact volume, enabling its integration on the tracker modules and staves.

#### I. POWERING TRACKERS AT THE SLHC

Today's high energy physics experiments at LHC embed large and very sensitive front-end electronics systems that are usually remotely powered through long cables. The innermost region of the experiments, the trackers, are those providing the largest density of channels, that must be powered with the minimal mass of cables and with reduced heat dissipation to avoid complex and massive cooling systems.

With the upgrade of the accelerator and its physics experiments already being planned, the detectors will require an increased number of electronic readout channels, which will demand more power. This increase of delivered power should be achieved without the addition of material in the detector volume, because of lack of physical space to run more cables and because material in this volume is detrimental to the physics performance of the detector. A solution to deliver more power without increasing the cable volume and mass relies on the distribution of power through on-detector DC-DC converters. These converters must be capable of reliable operation in high radiation (total ionizing dose of 250 Mrad(SiO2) and neutron fluencies of 2.5×10<sup>1</sup> n/cm<sup>2</sup>, 1 MeV neutron equivalent, based on the simulated environment in the central tracker detector over its projected lifetime) and strong DC magnetic field environment (up to 4 T) of the detector.

To be compatible with this harsh environment, the electronic devices need to be designed in specific technologies that have been qualified for the required doses and fluencies. Together with the high degree of miniaturization required, this fact imposes the development of a custom ASIC for the implementation of the power controller and switches in a known, radiation qualified technology [1].

The LHC tracker operates with magnetic fields up to 4 T to bend the particles thus allowing their identification. The DC-DC converters will be exposed to this DC magnetic field.

This forbids the use of conventional ferromagnetic cores, since they saturate at flux densities below 3 T. Coreless (aircore) inductors have to be used instead, limiting the accessible values of inductance below 700 nH in order to maintain affordable size and mass [2].

A comparative study indicated that the buck converter is one of the most suitable converter topology for the intended application [3]. Given the range of available coreless inductors, the switching frequency has to be set beyond 1 MHz in order to limit the current ripple.

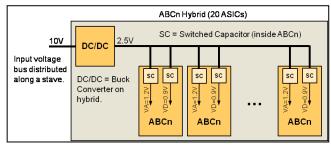

A typical tracker front-end system is made of strip detectors that are bonded to front-end hybrid circuits. These hybrids are fitted with several front-end chips. Several hybrid and detector modules are then mounted together to form a stave [4]. Based on this and on the estimated power requirements of the hybrids, an optimal powering scheme based on DC-DC converters (Figure 1) has been defined [3], that relies on an input voltage bus (10V) distributed along the stave to all the hybrids. Each hybrid circuit would be equipped with one Buck DC/DC converter delivering an intermediate bus voltage (2.5V) that brings the power to each front-end chip with a conversion efficiency of 80%. Each front-end chip would then convert the intermediate voltage down to the levels that it requires (1.2V and 0.9V) through integrated switched capacitors point-of-load DC/DC converters, whose efficiency is expected to be around 95%.

Figure 1: Powering topology.

Beyond the environmental constrains that are set to this powering scheme, the electromagnetic compatibility between the tracker electronics and the DC-DC converter used to power it is essential. The sLHC tracker powered from DC/DC converters in close proximity of the front-end electronics must be able to achieve levels of performance equivalent to those obtained when using remote, regulated power supplies in the present system. The proximity of switching converters with the strips and front-end ASICs (less than 5 cm) expose the front-end electronics to conducted and radiated couplings that could compromise the tracker performance. The compatibility can be achieved by appropriate design of the converter,

together with an adequate integration in the front-end system. In order to succeed, the susceptibility of the front-end system to conducted and radiated noise needs to be explored. On the other hand, the conducted and radiated noise properties of the converters need to be characterized in a standard manner, enabling their EMC optimization for the targeted system.

### II. RADIATED COUPLINGS AND INDUCTORS

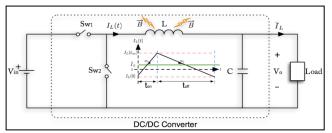

Some preliminary system tests have put in evidence the sensitivity of the hybrid modules to radiated magnetic fields [5]. Several sources of magnetic noise emissions can be identified in a buck converter: the top side switch current, the low side switch current, and the output filter inductor current.

Figure 2: current in buck output inductor.

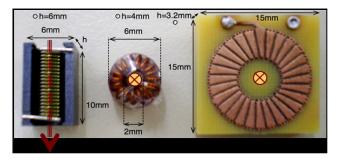

The variation of current in the inductor (Figure 2) results in a radiated magnetic field whose magnitude and direction considerably depends on the inductor topology. Three types of air-core inductors topologies (200 nH) have been characterized: air core solenoid, air core toroid and flat PCB toroid (Figure 3). Appropriate shielding options were explored as well.

Figure 3: solenoid (left), air core toroid (center), PCB toroid (right).

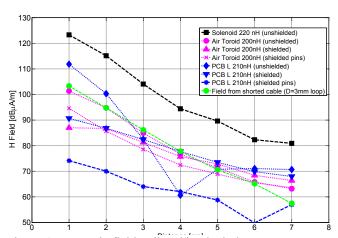

The magnetic field radiated by these inductors, driven with an RF source of 1.55 MHz at 0.9 A (peak), was measured up to distances of 10 cm in steps of 1cm, using a calibrated magnetic field probe.

The solenoid, which is the most commonly available topology, emits the full magnetic field along its axis. The field surrounds the coil, which leads to the largest radiated emissions (Figure 4). The addition of a shield aiming to attenuate the main magnetic field would result in a reduction of the inductance that could only be compensated by a larger number of loops, hence more material [2].

The toroidal topology allows enclosing the main magnetic field (that sets the inductance value) inside the coil volume. A parasitic field is still emitted through the central hole of the toroid, as a result of the current flowing along the toroid loop (Figure 3). This parasitic field is equivalent to that of a single loop turn having the diameter as large as the central hole of the toroid. This topology enables the introduction of a shield without reducing significantly the inductance value. The radiated emissions of this topology are 25 dB lower than those of the equivalent solenoid (Figure 4). The addition of a shield brings a further reduction of 5 to 10 dB.

Figure 4: Magnetic field radiated by the inductors.

The third topology explored is made of a printed circuit board toroidal inductor (3.2 mm high, 15 mm diameter). In order to obtain the required inductance, its flat geometry must be compensated with a larger diameter (and area), that results in a non negligible radiated field in its unshielded version. The addition of a copper shield (35  $\mu$ m copper) wrapped around the inductor board reduces the magnetic emission down to a level that is comparable with the one of the shielded air core toroid.

The connection pins of the inductors actually form an additional loop that originates a magnetic field emission whose amplitude is comparable with the field emitted by the coil itself. The placement of these pins as close as possible between them results in the reduction of the loop area and hence of the radiated field. In addition to this, the shield of the coil can be extended to the pins as well, achieving in this manner the lowest emission of magnetic field (Figure 4).

### III. BOARD LAYOUT ISSUES

The inductor is not the unique source of noise emitted by the DC/DC converter. The currents flowing on the board tracks and the voltage waveforms originate couplings to the surrounding components of the system, and within the converter itself. This noise gets visible in the form of common mode (CM) and differential mode (DM) currents that are conducted on input and output ports. The CM and DM currents are measured on a reference test stand [6] in frequency domain with calibrated probes connected to an EMI receiver; they are compared with reference levels.

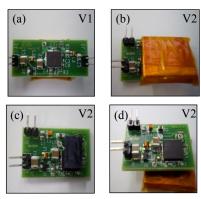

To explore the impact of the board design for the resulting conducted noise, two DC/DC converters prototypes built on the basis of the same schematic are compared. The two converters used a radiation tolerant buck converter ASIC prototype (AMIS2) [7] that integrated the switches and the

controller. A shielded external PCB inductor was mounted on top of the boards to provide the main filter (Figure 5a and 5b).

Figure 5: Converters prototypes, separated input and output (a) on V1, top (b) and bottom (d) PCB inductor mounting on V2, with solenoid inductor (c) on V2.

### A. Board Layout.

The mitigation of the radiated magnetic field is achieved with the reduction of the current loop areas, while the mitigation of the electric field emission is obtained through the reduction of copper areas that are subject to fast voltage transitions. However these basic guidelines find their limits in the choices made during the placement of the components and connectors.

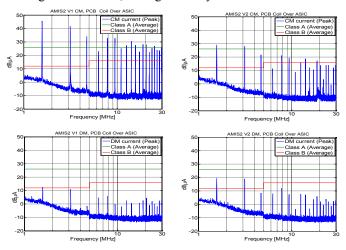

The first converter (V1) features a physical segregation between the input and the output ports that leads to a non negligible ground inductance between them. This ground path carries switched power currents, resulting in a common mode voltage between the input and the output ports. This configuration develops common mode currents that are 25 dB above those developed by the second board (Figure 6, top). By placing the input and output connectors close together instead (V2), the ground inductance, and hence the CM voltage and currents, are significantly reduced.

Figure 6: CM (top) and DM (bottom) noise for V1 (left) and V2 (right) layouts with top mounted PCB inductors.

However, the reduced distance between the input and output blocks increases the magnetic coupling between the input and output filter coils. As a result of this, the second

board (V2) develops larger DM noise (up to 10 dB, Figure 6, bottom).

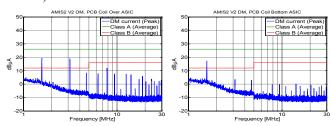

Figure 7: DM noise of prototype V2 with top (left) and bottom (right) mounting inductors.

Because it is a source of magnetic field emission, the inductor couples some noise currents onto the board that hosts it. An appropriate position of the inductor that minimizes the couplings with the components and loops of the PCB would reduce the levels of conducted and radiated noise. The conducted noise was measured on the second converter (V2) with the PCB inductor mounted on the top and on the bottom positions of the board. Moving the shielded PCB inductor from the top to the bottom side of the converter provided a reduction of the DM currents by up to 10 dB beyond 3 MHz (Figure 7): in this position, the converter ground plane acts as a shield against the couplings between the coil and the other components. Attenuation is also observed in the CM noise at the switching frequency and its first harmonic.

# C. Inductor Type.

The effectiveness of the magnetic coupling between the inductor and the other components depends on the magnetic field lines radiated by the coil, the distance and the direction with respect to the other parts. The CM current of the second prototype was compared when using the PCB shielded inductor or the unshielded solenoid. Using an appropriate placement, the latter is inducing slightly less CM and DM noise (< 6 dB of difference) because of its reduced size that allows keeping some distance between the filters and the connectors and at the same time orienting the magnetic axis perpendicularly to the filters. However, it was already seen that the solenoid actually radiates 40 dB more magnetic field towards the detector than the shielded PCB inductor.

#### IV. SUSCEPTIBILITY OF MODULES

The optimization of the noise performance of a front-end system is achieved by means of:

- The mitigation of the noise sources, for instance from the DC/DC converter.

- The improvement of the immunity of the system against these noise sources.

Independently of the powering scheme used, the noise performance of a front-end system can be improved significantly through appropriate layout choices. Uncontrolled powering loops, exposed preamplifier inputs or inadequate pin assignments on connectors and ASICs can radically compromise a system: the sensitive areas need therefore to be identified so that the powering device can be tuned to mitigate the coupling of critical noise frequencies and also to allow for system layout corrections.

# A. Susceptibility of Hybrids.

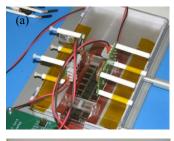

The noise susceptibility of two versions of the hybrid prototypes for the ATLAS Short Strip Tracker (SST) has been explored when powering them with DC/DC converter prototypes. These hybrids incorporate twenty ABCn front-end chips that can process 128 input strip channels each; however this setup was not bonded to any strip detector, enabling the study of the noise susceptibility of the hybrids exclusively.

The first hybrid circuit (LPL) required 2.5 V at 4.5 A from one converter to power the front-end chips; the power for the analogue circuitry of the ABCn chips was derived from low dropout linear regulators that are embedded in the front-end ASICs. The second hybrid circuit (KEK) required two converters, one delivering 2.5V for the digital section, the other one delivering 2.2V for the analogue section of the front-end ASICs.

The gain of every input channel was first calibrated using the reference charge injection circuit of the ASICs. Then a threshold scan with a reference input charge of 2 fC was performed to obtain individual S-curves. The RMS parameter of the fitted curve is then divided by the calibrated gain to obtain the equivalent noise charge (ENC) of the channel.

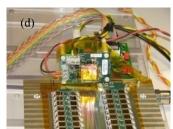

For both circuits, the ENC distribution was not degraded when powering them with the DC/DC converters, in comparison with the distribution obtained using linear power supplies (Table 1). Furthermore, the ENC distribution of the KEK hybrid obtained with two DC/DC converters placed straight on top of the ASICs did not reveal any noise degradation either (Figure 8, a). This puts in evidence the full compatibility of the hybrid circuit with DC/DC converters, even when those are in close proximity with the ASICs.

Table 1: Table 1: Noise on hybrids without strips.

| ENC at 2 fC         | Average |       | RMS   |       |

|---------------------|---------|-------|-------|-------|

|                     | Row 0   | Row 1 | Row 0 | Row 1 |

| LPL Linear PS       | 392.3   | 390.8 | 27.5  | 27.7  |

| LPL with DC/DC      | 392.6   | 390.9 | 27.0  | 27.9  |

| KEK Linear PS       | 388.1   | 390.0 | 26.4  | 27.6  |

| KEK with DC/DC      | 386.1   | 387.0 | 27.4  | 26.0  |

| KEK, DC/DC on ASICs | 386.4   | 388.0 | 27.8  | 26.3  |

## B. Tests with Strips.

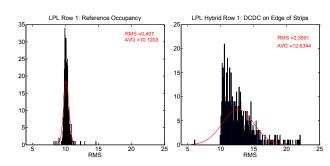

Similar measurements were carried out on a similar setup [8], using one LPL hybrid bonded to a strip detector (Figure 8, b,c,d). Here, the gain calibration is followed by the gain equalization of all channels. A threshold scan is then performed on every channel without injection of a test charge, and the resulting S-curves are fitted to obtain the threshold voltage and the RMS parameter. The equalized gains were measured to be about 110 mV/fC, enabling the scaling of the fitted RMS voltages into ENC. The measurement was carried out with three different conditions and the results were compared with those obtained with a linear power supply. First, the hybrid was powered with the DC/DC converter using a 40 cm long cable (Figure 8, b). Afterwards, the converter was moved within 5cm of the side of the hybrid (Figure 8, c), and finally the converter was moved as close as

possible to one of the rows of ASICs (row 1) with the inductor facing the strips (less than 2 cm, Figure 8, d).

The capacitance of the strip detector increases the reference noise obtained with the linear power supply, reaching around 550 electrons. The measurements performed with the DC/DC converter at distances of 40 cm and 5 cm do not show any significant deviation with respect to the reference values. The only noise degradation is observed on the row 1 when the converter is facing it at a distance of less than 2 cm (Figure 9). Even in this configuration, the neighbouring row appears to be insensitive to the field radiated by the converter and by the inductor (Table 2).

Figure 8: system tests on a KEK hybrid without strip (a), and on an LPL module at far (b), close (c) and edge (d) positions of the converter.

**Table 2:** Table 2: Noise from hybrids with strips.

| ENC at 0 fC           | Average |       | RMS   |       |

|-----------------------|---------|-------|-------|-------|

|                       | Row 0   | Row 1 | Row 0 | Row 1 |

| Reference (Linear PS) | 579     | 574   | 23.2  | 18.2  |

| Far (40 cm)           | 558     | 557   | 22.7  | 17.0  |

| Close (5 cm)          | 557     | 556   | 21.6  | 17.0  |

| Edge (< 2 cm)         | 574     | 716   | 21.0  | 134.0 |

Figure 9: noise distribution of LPL module on row 1 using a linear power supply (left) and a DC/DC converter facing the row 1 strips and bondings (right). No effect was observed on row 0.

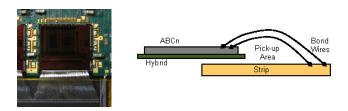

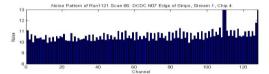

A more detailed analysis of the S-curves parameters allows putting in evidence the magnetic coupling on the input connection of the front-end ASICs and eventually on the strip itself. Effectively, the input pads of the ABCn are arranged in a way that requires the bondings to the strips to be stacked on two layers, resulting in different loop areas between the bond wires and the ground plane (Figure 10). These alternating pick-up loop areas result in an alternating noise pattern that gets visible in the S-curve RMS plot as a function of the channels (Figure 11).

Figure 10: Bonding pattern of the ABCn chips

Figure 11: Noise pattern of the ABCn channels.

## V. CONCLUSIONS

The upgrade of the trackers at LHC requires new powering solutions to be explored. To cope with the increased demand in terms of power, a front-end power conversion system will be required, introducing new challenges to keep up with the required noise performance of the front-end systems. The proposed powering scheme based on DC to DC converter would enable a very efficient distribution of power. Those should be located on the front-end modules exposing them to new noise sources.

The inductor is a dominant source of magnetic field in the converter. The comparison of the inductors and their different shielding options allow excluding the solenoid geometry, favoring instead the toroidal topology. Despite the difficulties to manufacture it, the shielded PCB toroid has shown the lowest emission of magnetic field. As second option, the air core toroid provides a good reduction of the emissions as well. In both cases, care must be taken to minimize the connection loop between the inductor and the board that was found to be a non negligible magnetic field emitter; shielding this loop was found to bring a significant reduction of the emitted field.

The board layout determines also the noise emission of the converter, in particular the conducted emissions. The lowest common mode current is obtained reducing the inductance between the input and the output, placing the connectors close together. Proximity couplings between the filters and in particular with the coil should be avoided by means of a careful orientation and respecting minimal distances between them. If a large PCB inductor is used, it should preferably be placed at the bottom of the board, benefiting from the ground plane as a shield.

The compatibility between an optimized and unshielded DC to DC converter prototype that used discrete components and

a shielded inductor, and a front-end hybrid prototype that used the ABCn ASICs was explored. The tested front-end system was found to be sensitive to magnetic couplings from the DC-DC converter at the inputs of the front-end chips and eventually at the strips, within distances of 2 cm. No susceptibility was observed on the hybrids themselves or at distances beyond 5 cm. To achieve the compatibility between the converter and the system, a careful layout of the interface between the strips and the input channels together with adequate interconnection technologies are required. Also, the magnetic field emitted by the converters has to be minimized.

Given this, the powering of new front-end systems appears to be possible using custom DC to DC converters that use magnetic field tolerant inductors. Proper layout of the hybrid and the use of appropriate interconnection technologies that would minimize the pick-up loops at the front-end inputs will insure the compatibility with compact custom DC to DC converters specifically designed for this application.

### VI. REFERENCES

- F. Faccio et al., "TID and displacement damage effects in Vertical and Lateral Power MOSFETs for integrated DC-DC converters", Proc. of RADECS 2009.

- [2] S. Orlandi et al., "Optimization of shielded PCB aircore toroids for high efficiency dc-dc converters", Proc. of ECCE 2009.

- [3] F. Faccio et al., "Custom DC-DC converters for distributing power in SLHC trackers", Proc. of TWEPP 2008.

- [4] F. Farthouat et al., "Readout architecture of the ATLAS upgraded tracker", Proc. of TWEPP 2008.

- [5] K. Klein et al., "System tests with DC-DC converters for the CMS silicon strip tracker at SLHC", Proc. of TWEPP 2008.

- [6] G. Blanchot et al., "Characterization of the noise properties of DC to DC converters for the sLHC", Proc. of TWEPP 2008.

- [7] S. Michelis et al., "ASIC buck converter prototypes for LHC upgrades", Proc. of TWEPP 2009.

- [8] A. Greenhall, "Prototype flex hybrid and module designs for the ATLAS Inner Detector Upgrade utilising the ABCN-25 readout chip and Hamamatsu large area Silicon sensors", Proc. of TWEPP 2009.