### AN AUXILIARY CONTROLLER IN THE N A 3 DATA ACQUISITION SYSTEM

by P. COURTY, Th. LERAY, J. VALENTIN

Laboratoire de Physique Corpusculaire

Collège de France - Paris.

#### Introduction

The on-line data acquisition system of the NA 3 experiment must be able to cope with up to 200 events per second, at 1000 words apiece. This forces somehow to store about 200 K words into a buffer memory, which is beyond the maximum capability of a standard on-line mini-computer. We use the low duty cycle of the SPS to do it: all data such as wire hits, photomultiplier pulse heights, hodoscope bit patterns, are divided into 3 groups, which are stored in parallel into three 64-K words external buffer memories. At the end of the ls. spill, they are transferred through the computer onto magnetic tape.

We have recently achieved substantial developments of this system, in order to :

- -extend the external buffer memory size,

- shift two tasks of the mini-computer onto auxiliary ontrollers, namely, monitoring of the experiment (histograms) and data packing.

### External memory

The external memories of several years ago had 16 bits of address, and were thus limited to 64 K 2-bytes words of capacity. Memories have now 23 bits of address, and can reach 16 M bytes.

In our previous set-up, the buffer memory blocks were accessed by :

- the mini -computer (a PDP 11-45) via a CAMAC interface

- an automatic controller for parallel data transfer from each detector group into the respective memory block during the spill, without help from the PDP.

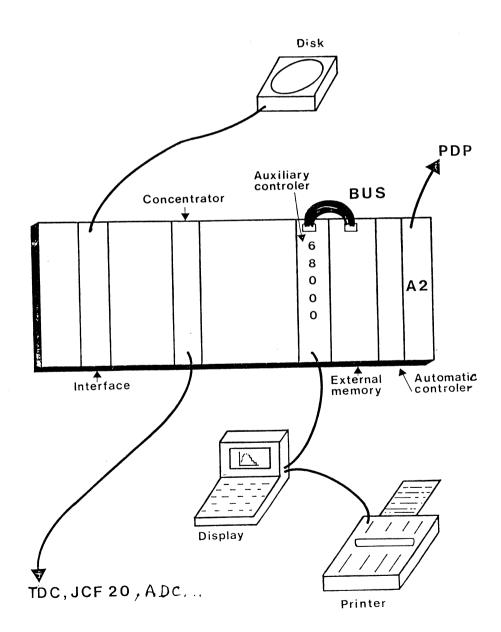

Now the memory is still read and written by the PDP and by the automatic controller, but also by an auxiliary controller mounted in the same CAMAC crate as the memory block and its automatic controller (see Figure)

## Auxiliary Controller:

This apparatus, including a Motorola MC 68000 microprocessor, uses 2/25 CAMAC units.

- One card contains the MC 68000 microprocessor and its memory : 32 K bytes RAM, and 12 K bytes ROM.

- The other card is the CAMAC interface, obeying the EUR 6500 norm.

- A fast bus connects this auxiliary controller with the 256 K bytes external memory block. This memory thus looks external for the mini-computer, via

CAMAC, and internal for the auxiliary controller, via the fast bus (cycle time: 250 ns). The controller works in the interspill time with lower priority than the PDP.

# Cheap Peripherals are used:

A display terminal allows dialogue with the microprocessor: software writing and histogram display; 80 K bytes may be stored on a mini-floppy disk via a CAMAC interface; a teletype is connected to the microprocessor via the display terminal.

### Software.

$\,$  The software system includes the MACSBUG system, and local editor and assembler.