## TAB BONDED SSD MODULE FOR THE STAR AND ALICE TRACKERS

J.R. Lutz\*, L. Arnold, J. Baudot, D. Bonnet, J.P. Coffin, M. Germain, C. Gojak, F. Jundt, C. Kuhn, C. Suire, A. Tarchini Institut de Recherches Subatomiques - IReS - IN2P3/ CNRS - ULP BP28, F 67037 Strasbourg Cedex 02 - France

D. Berst, G. Clauss, C. Colledani, W. Dulinski Laboratoire d'Electronique et de Physique des Systèmes Instrumentaux LEPSI - IN2P3/CNRS - ULP BP28, F 67037 Strasbourg Cedex 02 - France

A. Boucham, S. Bouvier, J. Castillo, C. Drancourt, B. Erazmus, G. Guilloux, L. Martin, C. Roy Laboratoire de Physique Subatomique et des Technologies Associées SUBATECH BP20722, F 44307 Nantes Cedex 03 – France

and the STAR collaboration, and the ALICE collaboration

\*Contribution presented at LEB99 in Snowmass, Co, USA, by <a href="mailto:Jean-Robert.Lutz@ires.in2p3.fr">Jean-Robert.Lutz@ires.in2p3.fr</a>

#### Abstract

A novel compact detector module has been produced by the "IReS"-"Subatech"-"Thomson-CSF-Detexis" collaboration. It includes a Double-Sided (DS) Silicon Strip Detector (SSD) and the related Front End Electronics (FEE) located on two hybrids, one for the N side and one for the P side. Bumpless Tape Automated Bonding (TAB) is used to connect the detector to the hybrids by means of microcables with neither wirebonding nor pitch adapter. Each of the six dedicated ALICE128C FE chip [1], located on the hybrid, is TABed on identical single layer microcables, which connect its inputs to the DS SSD and its outputs to the hybrid [2]. These microcables are bent in order to fold over the two hybrids on the DS SSD. This module meets the specifications of two experiments, ALICE (A Large Ion Collider Experiment) on the LHC accelerator at CERN [3] and STAR (Solenoid Tracker At Rhic) on the RHIC accelerator at BNL (Brookhaven National Laboratory) [4]. It can be used with air cooling (STAR) as well as with water cooling (ALICE) [5]. This mechanically self-consistent FE module has been tested on the SPS beam at CERN. Preliminary results are presented.

## 1. INTRODUCTION

During the summer 1998, a prototype module, including a DS SSD (according to the ALICE ITS Inner Tracking System and STAR SVT Silicon Vertex Tracker specifications) and two sets of ALICE128C FE chips, was tested on the SPS and PS accelerators at CERN and on the Vivitron at IReS. Two talks presented at Rome during LEB98 provided extensive information on the ALICE128C chip [6] and on the test results [7]. Complementary documents have also been produced [8]. These tests revealed an operation meeting all the specifications of the Technical Proposals (TP), the

mechanical aspect excepted. Actually, the integration of this prototype on the ladders was impossible because of its size as well as of its flat layout imposed mainly by the wire bonding connecting the chips to the detector via the pitch adapter. So, based on the same components, a compact detector module using TAB technology has now been produced to fit the geometrical ladder hermeticity requirements and the different cooling options of STAR and ALICE.

## 2. DOUBLE SIDED SSD MODULE

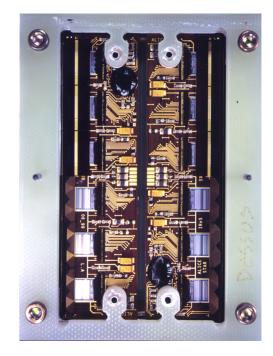

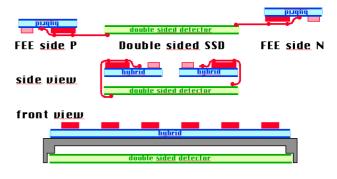

Fig. 1: Detector module in full size

The module consists of the mechanically self-consistent DS SSD and FEE hybrid assembly. Figure 1 represents

this module in top view i.e. from the hybrid side.

One can see the detector's N side through the gap between the two hybrids folded over the detectors. One hybrid is connected to the detector's N side facing the hybrids whereas the other hybrid is connected to the back on P side. On each hybrid, the three lower FE chips have their input microcables back-folded from the chip in order to lower the coupling with the input amplifiers. Two thin Al pins on each hybrid will allow the mechanical fastening and heat connection of the module onto the ladder. The outside frame holds mechanically the module into the spectrometer used for the beam tests. This "credit-card-like" module has the size of the detector and a thickness of about 4 mm.

320 such modules are needed for STAR and 1770 for ALICE.

# 2.1 Detector

The  $75 \times 42 \times 0.3$  mm DS SSD includes 768 AC coupled strips on each side with a pitch of  $95\mu m$  at a stereoscopic angle of  $\pm$  17.5 mrad. Guard and bias rings are all together  $\leq$  1 mm wide.

#### 2.2 Front End Electronics

- The FEE is located on two separate but identical hybrids, one connected to the N and one to the P side of the detector.

- The component side of the two hybrids faces the same orientation

- At least one of the hybrids is electrically floating.

- Hybrids are double-sided printed circuits made of 50 μm thick Kapton with 17 μm Cu, Ni and Au plated, on top.

- One COSTAR multipurpose control chip is located on each hybrid for temperature, low and high voltage and leakage current monitoring, and also for the ALICE128C analog output offset compensation.

#### 3. TAPE AUTOMATED BONDING

### 3.1 Manufacturers

Two French companies, Bull and Dassault have first developed the bumpless Tape Automated Bonding in a joint EuroTAB project. Meanwhile the TAB department of Dassault migrated to Thomson under the name Thomson-CSF-Detexis. These companies which lead this market in France have a great expertise in TAB for the consumer market as well as for air, space and military high level applications. They provide the microcables, the TAB, the bending and the assembling of the module.

### 3.2 Microcables

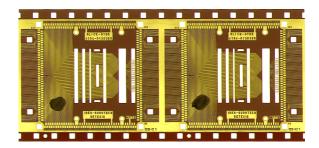

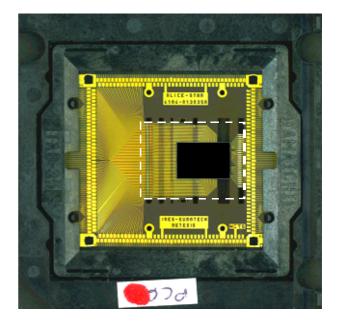

They are produced on long tapes as in figure 2. Each single frame is cut away and fixed into a plastic frame holder for easy handling and labeling as presented in

figure 3, seen from the metal side. The black ALICE128C FE chip is then TABed upside down near the middle of the microcable.

Fig. 2: Microcable tape in full size.

Fig. 3: Magnified Microcable in its frame with TABed FE chip on top.

The outer part, including the test pads, will be removed after testing. The inputs on the left side will then be TABed onto the detector and the outputs on the right side onto the hybrid.

The microcables have the following characteristics.

- One layer only.

- One identical layout for all the FE chips.

- One unique cable for inputs and outputs.

- Two TABing steps are implemented:

- Inside Lead Bonding (ILB) for testing and

- Outside Lead Bonding (OLB) for assembling.

- A so-called "UIIU" ILB input topology to meet the 44 μm input pitch of the chip by splitting the TABs on two staggered rows having an 88 μm pitch each.

- 135 µm ILB output pitch.

- 95 µm OLB detector pitch.

- 240 μm OLB hybrid pitch.

- Thickness: 17  $\mu m$  Cu, Au layered, on top of 70  $\mu m$  Kapton.

- Kapton is removed on bonding locations.

- Kapton is also removed on bending locations in order to avoid mechanical stress on the metal at the bending area.

- TABing is possible from both sides of the microcables, allowing for the components on the hybrids to face any appropriate side of the detector.

- There is no lost channel between 2 neighboring microcables.

The standard industrial Cu cables have been used because they proved their mechanical and electrical ruggedness and reliability on various applications.

Use of Al cables of same geometry is presently investigated.

### 3.3 Test features

From the early project step, this FE module has been designed for being tested all along its manufacturing, assembling and operating [9]. Everything can be remotely set, tuned, tested, checked and monitored at each step [10]. This convenience dictates all the steps of assembly of the DS SSD module.

## 3.4 Steps of TABing and assembling

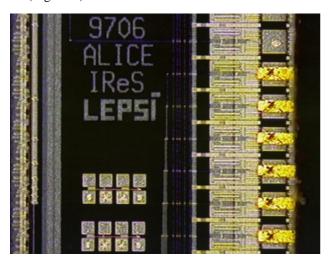

• <u>ILB TAB</u>. Each FE chip is first TABed on its unique single layer microcable (Figure 4), with test pads extensions, fixed inside its plastic frame holder (Figure 3).

Fig. 4: X shaped TABs on the right side of the ALICE128C FE chip.

• Chip test. The frame with its test pads is plugged on a test socket for chip and ILB checking. This test, running on a laptop PC with LabView software, is interfaced by a National Instrument digital an analog I/O PCMCIA card and a compact JTAG module plugged on the printer port. It displays, in real time, the progress of the tests and produces an output file of the measurements corresponding to the data sheet.

- Extension removal. After completion of the tests, the surrounding test pads are removed with the associated plastic frame holder.

- OLB hybrid TAB. The remaining part of the microcable, inside the dotted area on figure 3, is then processed. The output side of this assembly is double folded in order to bring the microcable next to the hybrid surface and TABed onto the pads of the hybrid which has already been equipped before with about 50 passive components and one COSTAR chip. Six FE ALICE128C chips on their microcable are TABed on each hybrid in this way.

- <u>Hybrid test</u>. The full-equipped hybrid is then tested with the same equipment as the single chip, but via a flex cable connector which plugs on the connection towards the ladder end.

- OLB SSD TAB. The remaining free input side is then flat positioned onto the SSD pads and TABed on them

- <u>Location of SSD TAB</u>. One hybrid is connected to one end of the SSD P side, the metal layer of the microcable facing the SSD, whereas the second hybrid is connected to the opposite end of the SSD N side, the Kapton of the microcable facing the SSD (Figure 5 top).

- Folding for air-cooling. The two hybrids are folded over the N side of the detector with their components looking outside the module for air-cooling (Figure 5, middle and bottom view).

Fig. 5: Assembling

- Folding for water-cooling. The hybrids can be folded over the detector with their components inside, facing the detector. They show then a flat surface appropriate for water cooling by means of a heat-bridge.

- <u>Stiffening spacers</u>. The detector is fixed on the hybrids by means of 100 μm thick carbon-fiber-epoxy stiffening spacers glued on the backside of each hybrid. A thin side extension protects the edge of the detector from mechanical shocks. (Figure 5, bottom).

- <u>Ladder tightening pins</u>. Each spacer is equipped with two pins to fix and to cool the module onto the ladder.

- Plan position on the ladder. The modules can be placed jointly on the ladder next to each other because of the thin microcables feeding all the signals on one face in

- a  $100 \, \mu m$  space. They present their insulated Kapton face to the outside. Thus they can be assembled onto the ladder on a single plane with a minimum of dead area (STAR)

- <u>Tile position on the ladder</u>. The modules can also overlap like tiles for a perfect hermeticity but with a higher material budget and a more complex geometric tuning (ALICE).

## 4. RADIATION LENGTH

Available computations on the radiation length of a whole silicon strip layer tend to a  $X/X_0$  of 0,7 – 1%.  $X_0$  Cu = 14.3 mm leads to a  $X/X_0$  of 0.12% for a uniform 17  $\mu$ m thick Cu layer. This value must be weighted by the surface ratio which is about 0.25. So, the mean value of  $X/X_0$  gets down to 0.03% which represents a weak fraction of the total radiation length for the layer. We consider that this value is acceptable, especially when air-cooling is used (STAR option) which reduces the material budget.

### 5. ALUMINIUM CABLES

The use of Al cables has been investigated by the Utrecht-Kharkov collaboration for the ALICE experiment [11]. These cables have a 14  $\mu$ m Al layer on top of 12  $\mu$ m Kapton.

After having investigated different topological options, multilayer multicable input, separate input and output, the collaboration finally adopted the same topological "UIIU" input option, the single layer option, the grouping of input and output on a unique microcable and the addition of test pads. The collaboration kept nevertheless a different input microcable layout for the different FEE chips, depending on their location on the hybrid.

#### 6. BEAM TESTS

The beam tests of different samples of the described module started on 15 September 1999 on the SPS at CERN and they are going on. The modules provided immediately coherent measurements.

#### 6.1 Beam test setup

In the background of the real STAR experiment, the beam tests have been performed with a setup as close as possible to the real experiment operation mode, with the real hardware, crates, boards, power supplies, cable length, locations and distances.

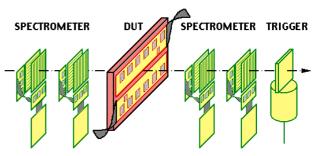

The Device Under Test (DUT) i.e. the DS SSD module is located in the center of a high-resolution spectrometer provided by the LEPSI [12], (Figure 6).

Due to the peculiar geometric relationship between the SSD strips and the readout channels, a lookup table has been implemented in the DAQ in order to provide realistic real time display of the acquisition data.

Distance: 35m

Fig. 6: Beam test setup.

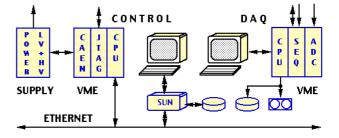

The DAQ system using a MicroDAS program on OS9 Operating System (OS) is running on a VME processor located in the crate housing the hardware interfaces.

Another VME crate, running VxWorks, houses the CAENnet interface for driving and monitoring the power supplies and the JTAG interface for the detector and slow control.

An Ethernet connected SUN workstation, running Solaris OS, operates the higher level control on the VME VxWorks crate and operator interface (later GUI Graphic User Interface).

# 6.2 Results

The baseline for the results is given by the measurements presented in LEB98 [7]. The analysis of the presently acquired data is going on and the plots on figures 7 and 8 are consistent with the results provided by the previous large size wire-bonded prototypes.

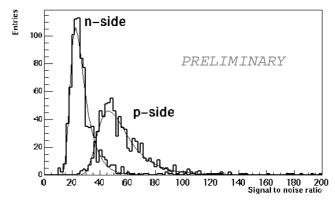

Fig. 7: S/N (Signal/Noise) side P and N.

The preliminary S/N plots of figure 7 present a peak value of about 50 on the P side and about 22 on the N

side. This latter low N side value is strongly dependent on the SSD sensor characteristics.

A spare prototype SSD remaining from the 1998 runs has been used for this module. Production SSD should improve this parameter.

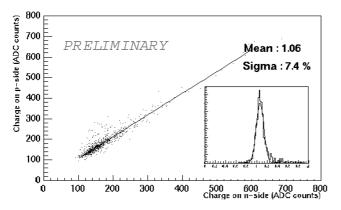

Fig. 8: Charge matching between side P and N.

Figure 8 presents the charge matching characteristics of the module together with the spread of this value that is important for ambiguous multi-hit resolution.

The geometric resolution perpendicular to the strips provides a RMS value of 22.5 micron on the P side and 21.4 micron on the N side of the module.

### 7. CONCLUSION

These preliminary beam test results, based on a low statistic, are consistent with those presented earlier and provided by an older wire-bonded prototype assembled with the same components. Deeper investigations are going on for the extensive specification.

It has nevertheless been demonstrated now that this new TABed DS SSD module exists, that it works and that it meets the electrical, mechanical and cooling specifications of both the STAR tracker and the ALICE tracker.

This module uses safe and reliable options: separate but identical hybrids for ground level and for high voltage FEE, and single layer microcables which are identical for all the FE chips.

Though each module has about 3800 TABs, no defective connection has been observed up to now.

Its compact and monolithic design forming a single  $75 \times 42 \times 4$  mm module ensures an easy assembling on the ladders to form the detector barrels.

## **ACKNOWLEDGEMENT**

We are greatly indebted to the Thomson-CSF-Detexis company and especially to A. Dravet, Y. LeGoff, E. Duriez, J. Pucci and Mr. Meriac for their highly effective contribution in this technical development.

#### REFERENCES

- [1] L. Hébrard et al., "ALICE128C: A CMOS Full Custom ASIC for the Readout of Silicon Strip Detectors in the ALICE Experiment", Proc. of the third workshop on electronics for LHC experiments, Imperial College, London, September 22-26, 1997, pp. 173-177

- [2] S. Bouvier et al., "TAB packaging technology for the Si-strip front end detector assembly", Proc. of the 4<sup>th</sup> workshop on electronics for LHC experiments, Rome, September 21-25, 1998

- [3] "ALICE: Technical Proposal for A Large Ion Collider Experiment at the CERN LHC", CERN/LHCC/95-71, LHCC/P3, December 1995

- [4] "Proposal for a Silicon Strip Detector for STAR", SUBATECH, IReS, LEPSI, France, Wayne State University, USA, 1998

- [5] "ALICE ITS Technical Design Report", CERN/LHCC 99-12

- [6] L. Hébrard et al., "Electrical characterization of ALICE128C: a low-power CMOS ASIC for the readout of Silicon Strip Detectors", CERN/LHCC/98-36, Proceedings of the 4<sup>th</sup> workshop on electronics for LHC experiments, Rome, September 21-25, 1998

- [7] J.R. Lutz et al., "Detector and front end electronics for ALICE and STAR silicon strip layers", CERN/LHCC/98-36, Proceedings of the 4<sup>th</sup> workshop on electronics for LHC experiments, Rome, September 1998

- [8] M. Germain et al., "Irradiation of a Silicon Strip Detector and readout chips for the ALICE experiment at LHC", NIM A 434 (1999) 345.

- [9] L. Hébrard, J.P. Blondé, C. Colledani, G. Clauss, "Design and Test of a CMOS Low-Power Mixed-Analog/Digital ASIC for Radiation Detector Readout Front Ends", Proc. of the 11<sup>th</sup> Annual IEEE International ASIC Conference, ASIC'98, Rochester, New York, September 13-16, 1998

- [10] H. Bleeker, P. Van den Eijnden and F. De Jong, "BOUNDARY SCAN TEST A Practical Approach", Kluwer Academic Publishers, 1993

- [11] A.P. de Haas, A. van den Brick, P. Kuijer, C.J. Oskamp NIKHEF, Utrecht, V.N. Borshchov, S.K. Kiprich, V.M. Ruzhitsky SRTIIM, Kharkov "Very low mass microcables for the ALICE silicon strip detector" Proceedings of LEB99, 1999.

- [12] C. Colledani, W. Dulinski, R. Turchetta, F. Djama, A. Rudge, P. Weilhammer, "A submicron precision silicon telescope for beam test purpose", NIM A 372 (1996) 379-384.