RECEIVED: September 30, 2024 ACCEPTED: November 20, 2024 PUBLISHED: January 16, 2025

25<sup>th</sup> International Workshop on Radiation Imaging Detectors Lisbon, Portugal 30 June – 4 July 2024

# Characterisation of analogue MAPS produced in the 65 nm TPSCo process

```

E. Ploerer [0, a, b, 1, *] H. Baba, [c] J. Baudot [0, d] A. Besson [0, d] S. Bugiel, [d] T. Chujo, [e]

```

*E-mail:* eduardo.ploerer@cern.ch

ABSTRACT: Within the context of the ALICE ITS3 collaboration, a set of MAPS small-scale test structures were developed using the 65 nm TPSCo CMOS imaging process with the upgrade of the ALICE inner tracking system as its primary focus. One such sensor, the Circuit Exploratoire 65 nm (CE-65), and its evolution the CE-65v2, were developed to explore charge collection properties for varying configurations including collection layer process (standard, blanket, modified with gap),

C. Colledani,<sup>d</sup> A. Dorokhov,<sup>d</sup> Z. El Bitar<sup>©</sup>,<sup>d</sup> M. Goffe,<sup>d</sup> T. Gunji,<sup>c</sup> C. Hu-Guo<sup>©</sup>,<sup>d</sup> A. Ilg<sup>©</sup>,<sup>b</sup>

K. Jaaskelainen, T. Katsuno, A. Kluge, A. Kostina, A. Kumar, A. Lorenzetti, b

A. Macchiolo, $^b$  M. Mager, $^g$  J. Park, $^e$  S. Sakai, $^e$  S. Senyukov $_{lacktriangle}$ , $^d$  H. Shamas, $^d$  D. Shibata, $^e$

W. Snoeys, $^g$  P. Stanek, $^h$  M. Suljic, $^g$  L. Tomasek, $^h$  I. Valin, $^d$  R. Wada $^f$  and Y. Yamaguchi $^{\odot}f$

<sup>&</sup>lt;sup>a</sup>Inter-University Institute for High Energies (IIHE), Vrije Universiteit Brussel, Pleinlaan 2, 1050 Brussels, Belgium

<sup>&</sup>lt;sup>b</sup>Physik-Institut, University of Zurich,

Winterthurerstrasse 190, 8057 Zurich, Switzerland

<sup>&</sup>lt;sup>c</sup>Center for Nuclear Study (CNS), University of Tokyo,

<sup>7</sup> Chome-3-1 Hongo, Tokyo 113-8654, Japan

<sup>&</sup>lt;sup>d</sup>Université de Strasbourg, CNRS, IPHC UMR 7178, F-67000 Strasbourg, France

<sup>&</sup>lt;sup>e</sup>University of Tsukuba,

<sup>1</sup> Chome-1-1 Tennodai, Ibaraki 305-8577, Japan

<sup>&</sup>lt;sup>f</sup>Physics Program, Graduate School of Advanced Science and Engineering, Hiroshima University,

<sup>1</sup> Chome-3-2 Kagamiyama, Hiroshima 739-0046, Japan

gEuropean Organization for Nuclear Research (CERN),

Espl. des Particules 1, 1217 Geneva, Switzerland

<sup>&</sup>lt;sup>h</sup>Department of Physics, Czech Technical University (CTU) in Prague, Zikova 4, 16636 Prague, Czech Republic

<sup>\*</sup>Corresponding author.

<sup>&</sup>lt;sup>1</sup>On behalf of the ALICE collaboration.

pixel pitch (15, 18, 22.5  $\mu$ m), and pixel geometry (square vs hexagonal/staggered). In this work the characterisation of the CE-65v2 chip, based on <sup>55</sup>Fe lab measurements and test beams at CERN SPS, is presented. Matrix gain uniformity up to the O(5%) level was demonstrated for all considered chip configurations. The CE-65v2 chip achieves a spatial resolution of under 2  $\mu$ m during beam tests. Process modifications allowing for faster charge collection and less charge sharing result in decreased spatial resolution, but a considerably wider range of operation, with both the 15  $\mu$ m and 22.5  $\mu$ m chips achieving over 99% efficiency up to a ~180 e<sup>-</sup> seed threshold. The results serve to validate the 65 nm TPSCo CMOS process, as well as to motivate design choices in future particle detection experiments.

Keywords: Particle tracking detectors (Solid-state detectors); Solid state detectors; Analogue electronic circuits

ArXiv ePrint: 2411.08740

| Contents |                                          |   |

|----------|------------------------------------------|---|

| 1        | Introduction                             | 1 |

| 2        | Characterisation with radioactive source | 2 |

| 3        | Testbeam results                         | 3 |

| 4        | Conclusion                               | 6 |

## 1 Introduction

Monolitihic Active Pixel Sensors (MAPS) combine the passive sensor and active readout chip onto the same silicon die. MAPS offer a variety of advantages with respect to their hybrid counterparts, including a lower material budget, cost, reduced power consumption, and smaller pitch as bump bonding is not needed. MAPS have already seen adoption by a wide variety of ongoing and proposed (collider) physics experiments including the STAR Experiment [1], the ALICE Experiment [2], the EIC [3], and the FCC-ee [4].

The ALICE experiment implemented a full MAPS-based tracking detector, consisting of 7 concentric layers, during its Inner Tracking System (ITS) upgrade during the second long shutdown of the LHC, denoted ITS2 [2], in the first adoption of MAPS at the LHC. To further improve tracking and vertexing performance, the ITS3 upgrade [5] seeks to replace the three innermost layers of the ITS2 with three fully cylindrical layers consisting of wafer-scale bent sensors, targeting an excellent spatial resolution of the chips (5 µm) and low material budget (0.09% X<sub>0</sub>/layer). The layers will rely on the stitching technique supported in the commercially available TPSco 65 nm CMOS imaging process. In the context of the ITS3 upgrade, a set of small-scale test structures were produced in a submission in December 2020: Analogue Pixel Test Structure (APTS [6]), Digital Pixel Test Structure (DPTS [7]), and the Circuit Exploratoire 65 nm (CE-65 [8]). A second submission at the beginning of 2023 allowed for the evolution of some of the small-scale test structures, including the CE-65v2: the evolution of CE-65.

The CE-65v2 chip was developed to investigate the charge collection and electrical properties of the 65 nm CMOS process through a selection of chip variants. The chip consists of a matrix of 1152 pixels organised in 48 columns and 24 rows, with a rolling-shutter readout. The in-pixel electronics consists of a AC-coupled amplifier that is DC-separated from the input stage of the readout electronics, allowing for the application of a resetting voltage for the reverse biasing of the sensor to the reset node. A resetting voltage of 10 V was applied throughout these studies in order to achieve full depletion. In total, there are 15 variants of the CE-65v2 chip targeting the exploration of 3 main axes:

- Process variation: Standard, Modified, Modified with Gap

- Pitch variation: 15 μm, 18 μm, 22.5 μm

- Matrix geometry: square vs hexagonal

In this work, the first two axes are explored. A total of four chips corresponding to the  $15 \,\mu m$  and  $22.5 \,\mu m$  chips in the Standard process and the  $15 \,\mu m$  and  $22.5 \,\mu m$  chips in the Modified with Gap process were considered in these studies.

Adopting a smaller pitch allows for an improvement in spatial resolution, but comes with significant drawbacks with respect to power consumption, readout-rate, as well as difficulties during manufacturing. Thus it becomes necessary to explore the pitch size at which the desired spatial resolution can be achieved, without compromising other aspects of the chip and system design.

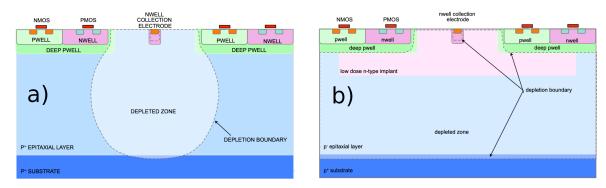

The process variations are detailed in ref. [9]. Figure 1a depicts the Standard process consisting of an n-well collection electrode, and in-pixel CMOS circuitry that is isolated from the epitaxial layer by a deep p-well. The depletion region begins to develop at the n-well collection electrode and follows a balloon shape in the epitaxial layer until the p+ substrate is reached. Due to the limited depth of the epitaxial region of  $O(10 \,\mu\text{m})$ , the lateral region remains undepleted, resulting in diffusion-dominated charge collection. In effect, charge collection is slow and subject to charge trapping, whilst exhibiting high charge sharing between pixels. Figure 1b depicts the Modified with Gap process which has, in addition, a deep low-dose n-type implant between the epitaxial layer and the CMOS circuitry, with gaps at the pixel edges. The depletion region in the Modified with Gap process extends laterally, as the gaps allow for the development of the electric field. The lateral electric field induces drift-dominated charge collection even at the edges, resulting in faster charge collection and reduced charge sharing.

**Figure 1.** Cross-sections of the CE-65v2 pixels detailing the Standard process (a) and the Modified with Gap process (b). Reproduced with permission from [5].

### 2 Characterisation with radioactive source

An extensive characterisation of the CE-65v2 chip was performed using X-rays from an  $^{55}$ Fe source. In particular, the X-ray spectrum of  $^{55}$ Fe is determined by the electron transitions possible during the electron capture decay of  $^{55}$ Fe to  $^{55}$ Mn. The most prominent peak ( $K_{\alpha}$ ) is at a known energy of 5.9 keV, with a secondary peak ( $K_{\beta}$ ) at an energy of 6.5 keV, with the peak width being determined primarily by the energy resolution of the given detector. A mapping from the measured Analog-to-Digital Units (ADUs), resulting from the quantization of the measured voltage by a 16-bit Analog-to-Digital Converter, to energy can be performed by matching the peak position of the  $K_{\alpha}$  (and  $K_{\beta}$ ) X-rays. The energy is often expressed in terms of electrons corresponding to the number of electron-hole pairs produced by the impinging X-ray. The different flavours of the CE-65v2 were measured at constant  $20^{o}$ C using a chiller for temperature control. The signal is computed by subtracting temporally

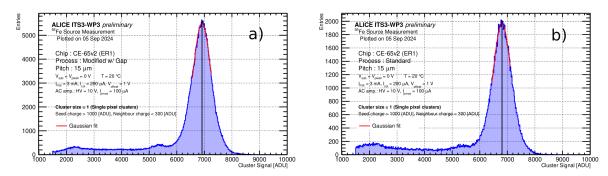

consecutive pixel frames to minimize baseline noise fluctuations. For a given event the  $3 \times 3$  matrix surrounding the most energetic pixel is considered. If the pixel passes a threshold of 1000 ADUs then it is considered a seed for cluster reconstruction. Adjacent pixels must pass a threshold of 300 ADUs, corresponding to approximately 2 times the Root Mean Square (RMS) noise, to be considered neighbours. Figure 2a depicts the measured <sup>55</sup>Fe spectrum for single pixel clusters for the CE-65v2 chip in the Modified with Gap process with a 15  $\mu$ m pitch. The main  $K_{\alpha}$  peak, centered around ~6900 ADUs, is fitted with a Gaussian distribution to extract the peak position. The neighbouring  $K_{\beta}$  peak, which would be expected at ~7480 ADUs, cannot be resolved due to pixel-to-pixel gain variations across the matrix. The same procedure was repeated for the 22.5  $\mu$ m pitch chip, as well as the 15  $\mu$ m and 22.5  $\mu$ m chips in the Standard process, yielding similar spectra and peak positions. As shown in figure 2b, the main  $K_{\alpha}$  peak position for the 15  $\mu$ m Standard process chip is within 1.6% of the 15  $\mu$ m Modified with Gap process chip. This outcome is anticipated, as the capacitance should not vary significantly when the chips are fully depleted. The same procedure was repeated for the single-pixel spectrum of individual pixels, yielding much cleaner spectra, at the cost of limited statistics, as can be seen in figure 3a.

**Figure 2.** <sup>55</sup>Fe spectrum for single pixel clusters of the entire matrix of the CE-65v2 chip in the Modified with Gap process (a) and Standard process (b) with a 15 µm pitch. The Gaussian fit is marked in red.

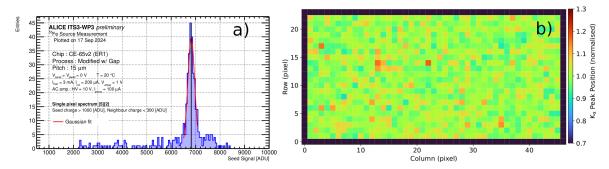

The energy resolution of 4.8%, obtained as the ratio of the Full Width at Half Maximum and mean peak position, is considerably better than that of the global spectrum in figure 2a, where it is 11.5%. Moreover, the  $K_{\beta}$  peak can be clearly resolved. Figure 3b summarizes the gain uniformity of the 15 µm chip in the Modified with Gap process by depicting the  $K_{\alpha}$  peak position for each individual pixel, normalized by the mean  $K_{\alpha}$  peak position for all pixels. No clear spatial pattern can be discerned, and indeed the variance of the gain between pixels is of O(5%). Similar trends hold for the other three chips, with the variance being of O(5%) in all cases. The initial characterisation with radioactive sources provided valuable insights into the gain uniformity and baseline performance, which were essential for validating the test beam measurements.

#### 3 Testbeam results

Test beam measurements were conducted at CERN SPS (H6 beamline) [10] to study the efficiency and resolution of different CE-65v2 variants. A telescope consisting of six ALPIDE [11] planes and using the DPTS [7] chip as a trigger was used. The telescope resolution was estimated to be  $2.2 \,\mu m$  using a telescope optimizer [12] for the given geometry. All tests were conducted at  $20^{\circ}$ C using a chiller to stabilize the device under testing. Data analysis was carried out using the Corryvreckan

**Figure 3.** a) <sup>55</sup>Fe spectrum for single pixel clusters for an individual pixel (x=5, y=2) of the CE-65v2 chip in the Modified with Gap process with a 15  $\mu$ m pitch. The Gaussian fit is marked in red. b) Gain distribution of the CE-65v2 chip in the Modified with Gap process with a 15  $\mu$ m pitch obtained by considering the normalized  $K_{\alpha}$  peak position (figure 3a) for each pixel.

framework [13], with tracks reconstructed using a straight-line track model that required hits on all six ALPIDE planes. Clusters on the CE-65v2 chip were built by summing all pixels in a  $3 \times 3$  window around a seed pixel passing an  $100\,\mathrm{e^-}$  threshold. The maximum cluster size is thus by definition 9. For electron threshold scans, identical seed and neighbour threshold cuts were applied for the pixels in the cluster, before their contributions were summed. A signal-to-noise ratio greater than 3 was required for all seed pixels. Multiple cluster candidates were considered corresponding to each pixel passing the required seed  $\mathrm{e^-}$  threshold and signal-to-noise ratio. Clusters within a 75 µm radius were associated with a given track, with the nearest cluster selected in cases of multiple candidates.

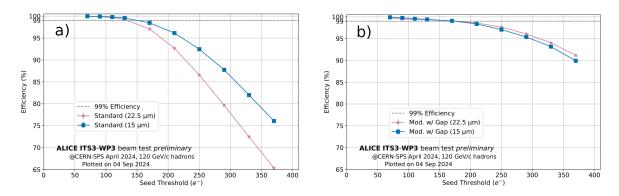

The efficiency as a function of electron threshold was studied for each of the four chip variants. In the Standard process, an efficiency of over 99% is achieved up to  $\sim 130\,\mathrm{e^-}$  and  $\sim 150\,\mathrm{e^-}$  for the 15 µm and 22.5 µm chips respectively, as depicted in figure 4a. The efficiency drops with respect to increasing threshold, but does so faster for the 22.5 µm pitch chip. In the Modified with Gap process, an efficiency of over 99% is achieved up to  $\sim 180\,\mathrm{e^-}$  for both the 15 µm and 22.5 µm chips, as depicted in figure 4b. The drop in efficiency is considerably slower with respect to the Standard process chips. The difference with respect to pitch size is marginal, with the 22.5 µm chip maintaining slightly higher efficiency.

**Figure 4.** Efficiency as a function of seed threshold ( $e^-$ ) for the CE-65v2 chip with 15  $\mu$ m (blue) and a 22.5  $\mu$ m pitch (pink) in the Standard (a) and the Modified with Gap process (b). The 99% efficiency line (dotted) is marked explicitly.

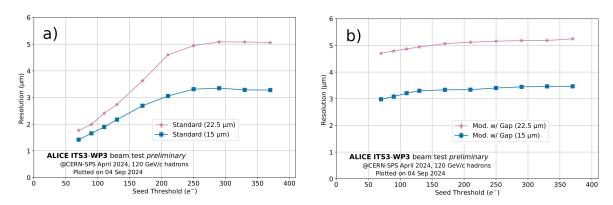

The spatial resolution of the chip variants was likewise studied with respect to increasing electron threshold. For each threshold the full analogue information was used to compute the centre-of-mass position of a given cluster using the seed and neighbour thresholds given previously in this section. In the Standard process, an excellent resolution of  $\sim 1.5 \, \mu m$  and  $\sim 2 \, \mu m$  can be achieved at a seed threshold of  $70 \, e^-$  for the 15  $\, \mu m$  and 22.5  $\, \mu m$  chips, as depicted in figure 5a. The performance degrades quickly in the  $70 \, e^-$  -250  $e^-$  range as the cluster size decreases, before plateauing at  $\sim 3 \, \mu m$  and  $\sim 4 \, \mu m$  for the 15  $\, \mu m$  and 22.5  $\, \mu m$  chips. For both chips a resolution that is considerably better than the binary resolution of pitch/ $\sqrt{12}$  is achieved. Figure 5b depicts the resolution as a function of increasing  $e^-$  threshold for the Modified with Gap process chips. The Modified with Gap chips achieve a worse resolution compared to the Standard process chips for all considered thresholds, especially for the 15  $\, \mu m$  pitch chip. The resolution is, however, more stable with increasing thresholds. Comparing the two pitches for the Modified with Gap process chips, the 22.5  $\, \mu m$  chip displays less variation increasing slightly to just above 5  $\, \mu m$  resolution, in parity with the Standard process chip.

**Figure 5.** Resolution as a function of seed threshold ( $e^-$ ) for the CE-65v2 chip with 15  $\mu$ m (blue) and a 22.5  $\mu$ m pitch (pink) in the Standard (a) and the Modified with Gap process (b).

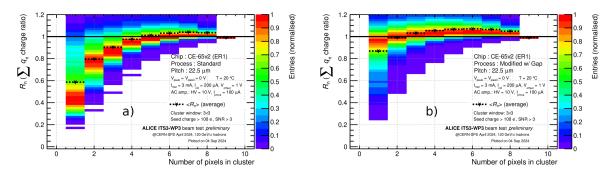

Charge sharing behavior significantly impacts both efficiency and spatial resolution, making it essential to assess across different pixel configurations. To study the extent of charge sharing for the different CE-65v2 variants, the accumulated charge ratio was determined by charge-ordering the pixels in a given cluster, and successively summing the charge of individual pixels, until a cluster size of 9 was obtained. The accumulated charge was then normalized by the total charge, defined as the sum of the charge of all pixels in a 3x3 window around the seed pixel, to obtain the accumulated charge ratio. Figure 6a depicts the accumulated charge ratio as a function of pixels in the cluster for the 22.5 µm pitch chip in the Standard process. The average charge fraction carried by the central pixel is less than  $\sim 60\%$ , with the most probable value being even lower at  $\sim 45\%$ , showing the high charge sharing characteristic of the Standard process. The most extreme charge sharing was found for the 22.5 µm pitch chip in the Standard process due to the competing effects of a larger pitch, whereby more charge is collected due to the larger area, and the electric field not propagating well at the pixel edges, resulting in considerably less charge drift. It is important to note that due to charge ordering, negative noise contributions, resulting from the frame subtraction described in section 2, can appear in the larger cluster size bins, as shown on the right side of figure 6a. These noise contributions may cause the accumulated charge ratio to exceed 100%.

**Figure 6.** a) Accumulated charge ratio as a function of number of pixels in a cluster for the CE-65v2 chip with a 22.5 μm in the Standard (a) and Modified with Gap process (b).

Figure 6b, on the other hand, depicts the accumulated charge ratio as a function of pixels in the cluster for the 22.5 µm pitch chip in the Modified with Gap process. The average charge fraction carried by the central pixel is considerably higher with respect to the Standard process chip, with the charge fraction being over 85%. When considering the two most energetic pixels, both the average and most probable value of accumulated charge are around unity, suggesting that the vast majority of events consist of single-pixel or two-pixel events. Indeed, it is to be expected that if a hit occurs close to the edge of the pixel, then charge is shared with the neighbouring pixel, otherwise it is almost entirely collected due to the strong drift current evident in the Modified with Gap process. Due to the Gap modification at the pixel boundaries, the electric field does propagate well at the pixel edges, unlike in the Standard process. Coupled with a larger pitch this results in the lowest charge sharing of the four chip variants that were studied.

## 4 Conclusion

This work presents the first results of the CE-65v2 chip. A detailed comparison of the Standard process and the Modified with Gap process, as well as varying pixel pitch (15  $\mu$ m, 22.5  $\mu$ m) was made with particular emphasis on charge sharing properties and their ramifications on efficiency and resolution. Gain uniformity up to the O(5%) level was demonstrated for the considered CE-65v2 variants in  $^{55}$ Fe lab tests. An excellent resolution in large-matrix 65 nm CMOS test structures was obtained during beam test measurements at the CERN SPS. The sub 3  $\mu$ m spatial resolution obtained in the Standard process for both pitches satisfies FCC-ee requirements [4], and allows tradeoffs in pixel pitch with respect to power consumption, readout-rate, and manufacturing-ease. This enables a wide range of applications for 65 nm TPSCo MAPS. However, the spatial resolution was observed to quickly degrade when the chip is operated outside the low electron threshold regime, making it particularly sensitive to noise and radiation defects, including charge trapping. The Modified with Gap process displays a wide operating range with over 99% efficiency being achievable up to  $\sim$ 180 e<sup>-</sup> for both the 15  $\mu$ m and 22.5  $\mu$ m chip. The wider range of operation and faster charge collection makes the process more suited for high radiation environments.

The complete characterisation of the CE-65v2 chip is currently underway. A full analysis of the CERN SPS results including the Modified "intermediate" process modification and 18 µm pitch chips is in progress. In addition, the use of the resetting voltage as a tool to tune charge sharing, and the impact of a hexagonal matrix pixel arrangement on cluster size and resolution are likewise being

studied. Radiation tolerance studies using irradiated CE-65v2 chips were performed in May 2024 at DESY, and will complement the results obtained thus far. In summary, the characterisation of the CE-65v2 chip has supplemented the APTS [6] and DPTS [7] studies in the validation of the 65 nm TPSCo process as a candidate technology for advanced particle detection applications, including the ALICE ITS3 upgrade. The demonstrated spatial resolution, efficiency, gain uniformity, and ongoing studies pertaining to matrix geometry and radiation tolerance will further help refine the design parameters necessary for efficient tracking systems in future high-energy physics experiments.

## Acknowledgments

The measurements leading to these results were performed at the Test Beam Facilities at CERN (Switzerland). This project has received funding from the European Union's Horizon 2020 Research and Innovation Programme under Grant Agreements 101004761 (AIDAinnova) and 101057511 (EURO-LABS).

#### References

- [1] A. Dorokhov et al., *High resistivity CMOS pixel sensors and their application to the STAR PXL detector*, *Nucl. Instrum. Meth. A* **650** (2011) 174.

- [2] ALICE collaboration, *Technical Design Report for the Upgrade of the ALICE Inner Tracking System*, *J. Phys. G* **41** (2014) 087002.

- [3] EIC SILICON CONSORTIUM and ATHENA collaborations, *MAPS-based tracking and vertexing for the Electron-Ion Collider*, *Nucl. Instrum. Meth. A* **1050** (2023) 168120.

- [4] N. Barchetta, P. Collins and P. Riedler, *Tracking and vertex detectors at FCC-ee*, *Eur. Phys. J. Plus* 137 (2022) 231 [arXiv:2112.13019].

- [5] ALICE collaboration, *Technical Design report for the ALICE Inner Tracking System 3 ITS3; A bent wafer-scale monolithic pixel detector*, CERN-LHCC-2024-003, ALICE-TDR-021, CERN, Geneva (2024).

- [6] G.A. Rinella et al., Characterization of analogue Monolithic Active Pixel Sensor test structures implemented in a 65 nm CMOS imaging process, Nucl. Instrum. Meth. A 1069 (2024) 169896 [arXiv:2403.08952].

- [7] G.A. Rinella et al., Digital pixel test structures implemented in a 65 nm CMOS process, Nucl. Instrum. Meth. A 1056 (2023) 168589 [arXiv:2212.08621].

- [8] S. Bugiel et al., Charge sensing properties of monolithic CMOS pixel sensors fabricated in a 65 nm technology, Nucl. Instrum. Meth. A 1040 (2022) 167213.

- [9] W. Snoeys et al., A process modification for CMOS monolithic active pixel sensors for enhanced depletion, timing performance and radiation tolerance, Nucl. Instrum. Meth. A 871 (2017) 90.

- [10] D. Banerjee et al., *The North Experimental Area at the Cern Super Proton Synchrotron*, CERN-ACC-NOTE-2021-0015, CERN, Geneva (2021).

- [11] ALICE collaboration, ALPIDE, the Monolithic Active Pixel Sensor for the ALICE ITS upgrade, Nucl. Instrum. Meth. A 824 (2016) 434.

- [12] M. Mager, Telescope optimizer, https://mmager.web.cern.ch/telescope/tracking.html.

- [13] D. Dannheim et al., Corryvreckan: A Modular 4D Track Reconstruction and Analysis Software for Test Beam Data, 2021 JINST 16 P03008 [arXiv:2011.12730].