ELSEVIER

Contents lists available at ScienceDirect

# Nuclear Inst. and Methods in Physics Research, A

journal homepage: www.elsevier.com/locate/nima

# Considerations on time resolution of neutron irradited single pixel 3D structures at fuences up to $10^{17}~n_{eq}/cm^2$ using 120 GeV SPS pion beams

Evangelos-Leonidas Gkougkousis <sup>a,\*</sup> , Edgar Lemos Cid <sup>b</sup>, Viktor Coco <sup>b</sup>

### ARTICLE INFO

Keywords:

3D sensors

Radiation hardness

Silicon detectors

Bandwidth

Test beam

Fast timing

Readout electronics

### ABSTRACT

The proven radiation hardness of silicon 3D devices up to fluences of  $1\times10^{17}$   $n_{eq}/cm^2$  makes them an excellent choice for next generation trackers, providing <10  $\mu m$  position resolution at a high multiplicity environment. The anticipated pile-up increase at HL-LHC conditions and beyond, requires the addition of <50 ps per hit timing information to successfully resolve displaced and primary vertices. In this study, the timing performance, uniformity and efficiency of neutron and proton irradiated single pixel 3D devices is discussed. Fluences up to  $1\times10^{17}$   $n_{eq}/cm^2$  in three different geometrical implementations are evaluated using 120 GeV SPS pion beams. A MIMOSA-26 type telescope is used to provide detailed tracking information with a ~5  $\mu$ m position resolution. Productions with single- and double-sided processes, yielding active thicknesses of 130 and 230  $\mu$ m respectively, are examined with varied pixel sizes from 55  $\times$  55  $\mu$ m<sup>2</sup> to 25  $\times$  100  $\mu$ m<sup>2</sup> and a comparative study of field uniformity is presented with respect to electrode geometry. The question of electronics bandwidth is extensively addressed with respect to achievable time resolution, efficiency and collected charge, forming a 3D phase space to which an appropriate operating point can be selected depending on the application requirements.

# 1. Introduction

Over the past decade, 3D pixel sensors have emerged as tracking devices in high-energy physics experiments, within environments of intense radiation fluxes, encountered in the  $|\eta|<2$  regions of ATLAS Insertable B-Layer [1] and ATLAS Forward Proton (AFP) detector [2]. The sensor design, decoupling charge-generating volume from the drift distance, accommodates shorter electrode spacing, consequently decreasing the charge carrier trapping probability. Recent studies using the Transient Current Technique (TCT) [3,4], have further substantiated the exceptional timing performance of such devices. For vertically incident events, the orthogonal relationship between drift direction and particle trajectory results in an absence of Landau fluctuations, key factor in extending theoretical timing performance of such devices, primarily constrained only by the signal's drift time.

This excellent performance is nevertheless impacted by field non-uniformities, intrinsic to the column geometry of the collection electrodes. The resulting radially expanding field within the pixel volume increases signal time-jitter, degrading time resolution. Such a geometry, though detrimental under normal operation, can lead to high field densities near the collection electrode (>30 V/ $\mu$ m) at higher bias

voltages (>500 V) typically used after irradiation. In this operating mode, impact ionization and charge multiplication occur near the collection electrode in a similar way as in Multi-Wire Proportional Chambers (MWPCs) and can compensate for trapping induced charge collection efficiency issues.

In this study, three different geometries are examined after proton and neutron irradiation, using 120 GeV SPS pion beams [5]. Pixel sizes of 55  $\times$  55  $\mu m^2$  [6], 25  $\times$  100  $\mu m^2$  and 50  $\times$  50  $\mu m^2$  [7] in substrates of 230  $\mu m$  (190  $\mu m$  active depth) for the first geometry and 150  $\mu m$  (140  $\mu m$  active depth) for the second and third, are tested to establish the minimum active thickness and pixel size still yielding sufficient charge and low enough jitter to achieve a 30 ps time resolution. Questions of signal integrity, bandwidth and efficiency are treated.

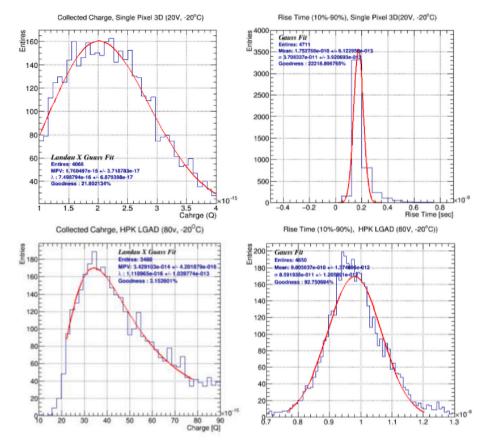

# 2. Timing and signal integrity

Studies under a  $^{90}Sr$  source of the 50  $\times$  50  $\mu m$  variety single pixel structure (Fig. 1 top), yield collected charge of 1.76  $\pm$  0.02 fq (10,980 e^-), in agreement with the theoretically predicted value of  $\sim\!73$  e/ $\mu m$  for a MIP in fully depleted Si [8] at a bias voltage of 20 V at -20 °C. Signals are characterized by a fast rise time (10 %–90 %) of 175  $\pm$  4 ps, but

E-mail address: vagelis.gkougkousis@cern.ch (E.-L. Gkougkousis).

a University of Zurich, Switzerland

<sup>&</sup>lt;sup>b</sup> European Organization for Nuclear Research (CERN), Geneva, Switzerland

<sup>\*</sup> Corresponding author.

Fig. 1. Charge and rise time distributions of a 150  $\mu$ m, 50  $\times$  50  $\mu$ m $^2$  pitch, 3D single pixel devince (top) and a 50  $\mu$ m thick LGAD (bottom).

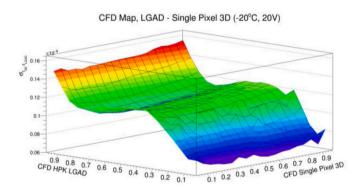

Fig. 2. Time resolution map of an LGAD - 3D ( $50 \times 50~\mu m^2$  single pixel) system with respect to CFD thresholds. Constant slew-rate and abence of Landau fluctuations in the 3D case result in a flat dependence.

present a tail at the slower end, characteristic of filed non-uniformities. Although charge per micrometer in the 3D device is reduced by a factor of 60 with respect to a typical LGAD $^1$  (34.3  $\pm$  0.4 fq for 50  $\mu m$  thick HPK $^2$  device), an almost factor of 6 gain in rise time is noted (980  $\pm$  1.4 ps for LGADs - Fig. 1 bottom).

Analog time resolution of the LGAD-3D system can be approximated as the sum of a Landau fluctuations term, field related distortion effects and the noise-induced jitter [9]. Through a Constant Fraction Discriminator (CFD) time walk correction approach, a 2D time resolution map is established with respect to the CFD of each of the components (Fig. 2).

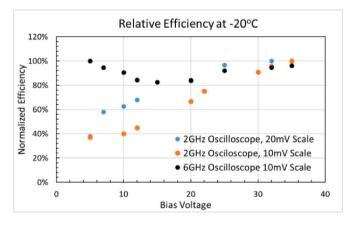

Fig. 3. Relative efficeicny vs bias voltage for different ADC scaling values and badnwidth limits.

For LGADs, selecting higher CFDs to profit from increased signal to noise ratio incurs a penalty in slew rate, deteriorating time resolution, thus resulting in the characteristic S curve along the x-axis. The plateau at  $\sim\!40$  % of peak amplitude corresponds to a time when all primary charges have reached the gain layer. In the case of 3Ds, due to the decoupling of drift and charge generation volumes and reduced electrode distances, the slew rate remains practically constant. Absence of gain under normal operation can be partially addressed by selecting higher CFDs, without degradation on time resolution.

To mitigate statistical biases and efficiency issues at the dynamic range limit, a high bandwidth readout system (>3 GHz) is crucial. Such effects can be studied by leveraging the Poissonian distribution of radioactive decays. Using a two-object coincidence system, a DUT bias

<sup>&</sup>lt;sup>1</sup> Low Gain Avalanche Diode.

<sup>&</sup>lt;sup>2</sup> Hamamatsu Photonics LTd.

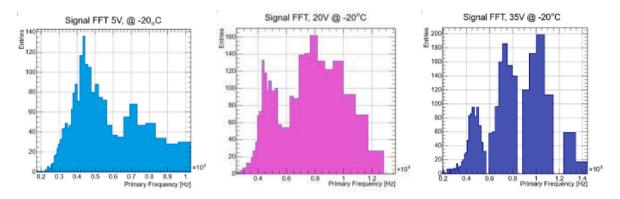

Fig. 4. Distributions of the frequency corresponding to the highest power harmonic for bias votlage of -5 V, -20 V and -35 V at a 4000 events samnple. A compositon change is observed with respect to bias.

scan is performed requesting identical number of events at each step. The reference device (LGAD) is set to a known bias, yielding 100 % efficiency. An event frequency distribution is constructed at each step exploiting timestamp differences of consecutive events. The per bias rate is determined through Bayesian inference of a Poison fit, using the Gamma function as a conjugate prior [10]. The maximum achievable rate corresponds to the full efficiency point, assuming fixed source activity and geometrical acceptance. Relative efficiencies can subsequently be attributed for each bias, by comparing each point's corresponding rate with the one at the 100 % efficiency point.

Fig. 3 displays the relative efficiencies for varying bandwidth limits and analog-to-digital (ADC) scaling as a function of bias voltage. A typical S-curve is observed in the 2 GHz - 10 mV series, achieving 100 % efficiency at  $\sim -36$  V. When the analog scaling is doubled, without additional system changes, an "apparent" relative efficiency improvement is observed, peaking at  $\sim -30$  V. However, this configuration results in a 20 % reduction in the per point event rate, compared to the 10-mV scenario – corresponding to a 20 % reduction in absolute efficiency. In reality, the requirement for a minimum of 3 Time-over-Threshold (ToT) ADC bins for the trigger circuit to latch, alters the signal distribution by eliminating its faster component, when scaling is increased. The charge to ToT proportionality of the used transimpedance amplifier, biases the charge distribution towards higher

values, even though the actual trigger threshold remains the same.

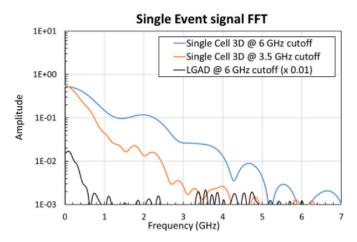

Increasing the ADC bandwidth from 2 to 6 GHz, while maintaining amplifier cut-off at 3 GHz, results to 100 % relative efficiency at the lowest bias, but decreases as voltage rises. Using a square windowing function, the frequency of the highest harmonic is extracted from the Fast Fourier Transform (FFT) of the signal part of each waveform for biases of -5, -20, and -35 V (Fig. 4). Bias noticeable affects signal composition, with the faster component dominating at higher fields. With decreasing bias, the signal fraction around 0.4 GHz increased from 20 % to 80 %. The convolution of a bandwidth cut, evolving signal population and normal efficiency S-curve expected as fields increase, account for the observed shape of the 6 GHz series in Fig. 3. At lower biases, most signals fall below the bandwidth cut and are recorded. However, as the field intensifies, efficiency should increase, but part of the signal exceeds the bandwidth limit, reducing event rate. At the highest bias, 80 % of the signal exceeds the frequency cut-off, yet the increased efficiency compensates, recovering the rate of the slower component to levels observed at lower fields.

# 3. SPS pion test beams

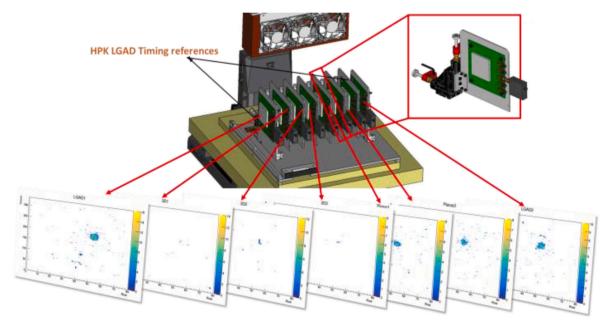

Properly addressing previously detailed issues and studying field non-uniformities require precise position resolution ( $\sim$ 5  $\mu$ m) combined

Fig. 5. CAD representation of the cold box with the DUT and timing reference planes. Occupancy distributions are used for plane alignemet.

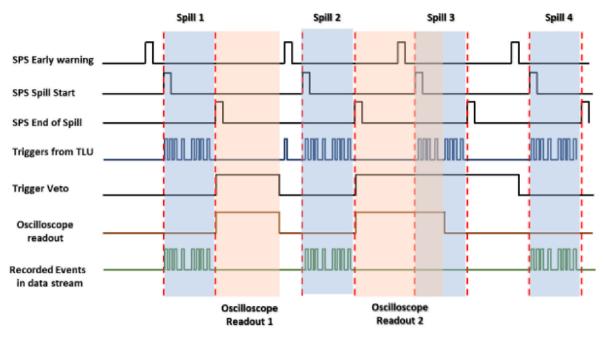

Fig. 6. Timing diagram of the trigger, readout and synchronisation system with respect to the VETO and SPS master clock siganls.

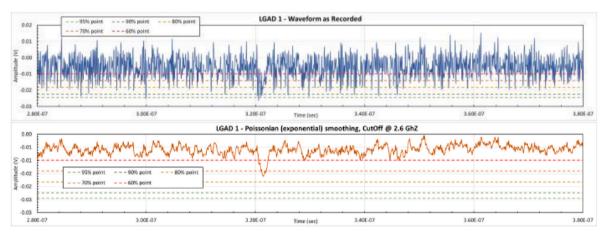

Fig. 7. As recorded and after a 2.4 GHz low-pass Gaussian filter LGAD signal. Dotted lines indicate percentages of the original signal amplitude.

with high statistics and high bandwidth electronics. To that end, an intensive 16-week long test beam campaign using 120 GeV pions was undertaken at CERN SPS. A timing telescope consisting of 6 DUTs and 2

Reference planes in coincidence was placed within a temperature controlled XPS cold box. Plane alignment is achieved through micrometric piezo-electric actuators, while the entire system is positioned

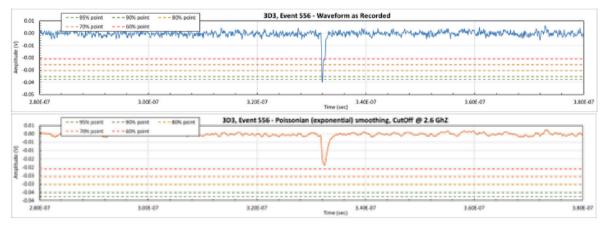

Fig. 8. As recorded and after a 2.4 GHz Gaussian filter 3D signal. Dotted lines indicate percentages of the original signal amplitude.

Fig. 9. Power Spectrum of an LGAD, 3D and Gaussian filtered 3D sigal. A 40 % power loss is observed for the smoothed 3D signal.

between the forward and backward arm of a EUDET-based MIMOSA-26 [11] telescope. An FE-I4 planar module, attached to the back end of cold box, is used as an ROI trigger and alignment plane (Fig. 5).

System read-out is achieved through 2 synchronized 6 GHz oscilloscopes [12], while a fast SiGe-based first stage transimpedance amplifier [13] in conjunction with a 6 GHz s stage voltage amplifier (ZX-60V3 [14]) is attached to each plane. Data, generated in two streams (tracking, timing) are synchronized using the SPS master clock in conjunction with a trigger VETO, while readout is performed during the synchrotron acceleration cycles to eliminate dead time. A timing diagram of the architecture can be seen in Fig. 6.

Individual event waveforms are analyzed using a multi-factor weighted approach to address increased noise, inherent to the high bandwidth and capacitance of the DUTs. A low pass filter, comprised of a rectangular transfer function followed by a Gaussian decrease, with a  $\sigma$  of 0.5 GHz and the -10 dB point centered at 2.4 GHz, is applied at the analysis stage to improve SNR and allow for signal smoothing (Figs. 7

and 8). Although for the reference sensor (LGAD) such an operation dramatically improves signal quality and lowers noise (Fig. 7), for the 3D structure, it results in a 60 % degradation of amplitude and 20 % increase of calculated collected charge, without any advantages on SNR. The lower capacitance of the DUT (20–80 fF depending on geometry) compared to that of reference (2 pF for  $1\times1~\text{mm}^2$  LGADs) eliminates any potential gain from such an approach. In contrast, any low pass filtering will bias the signal statistics towards the high charge region, both due to the distorted signal shape and lower signal amplitudes, resulting to an enhanced rejection of the low amplitude tails, thus pushing the MPV of the Landau to a seemingly higher value.

Using a Keizer window, the Fourier transform of the signal region of Figs. 7 and 9 event waveform is computed for the 3D and the LGAD sensors (Fig. 9). While the unsmoothed 3D signal expands up to 5 GHz, the first harmonic of the LGAD signal debuts at 0.6 GHz. Appling the Gaussian low-pass filter with the 2.4 GHz cut-off frequency on the 3D signal, significantly reduces the higher frequency side of the spectrum. An appropriate readout electronics in this case would need to at least have a bandwidth of 5 GHz, whereas such an approach for an LGAD would be detrimental due to the higher induced noise without any gain on the signal side.

## 4. Fast front-end electronics

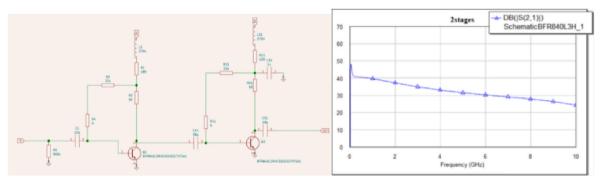

To adequately record high bandwidth signals, a discrete 16-channel read-out board based on a two-stage amplifier approach was designed (Fig. 10). A two-stage single SiGe transistor amplifier geometry, with first stage configured as a transimpedance and the second as a voltage amplifier, was used. Provisions for individual channel shielding to further reduce noise are implemented, while a high frequency Rogers 3035 laminate is used in a five-layer PCB design with the signal plane encapsulated within isolated ground layers. Sensor bias is provided via a triaxial LEMO connector while keyed 8-fold coaxial high bandwidth mini-mcx connector arrays are placed unilaterally to the PCB.

The DUT is placed on a passive 300  $\mu$ m thick mezzanine board, populated with 18 coaxial mini-mcx connectors, to facilitate alignment and exchangeability. Peripheral components were optimized to ensure

Fig. 10. Prototype of the hgih bandwidth versatile multi-channel PCB.

Fig. 11. Scematics of the circuit (left) and simulations (right) for up to 10 GHz of the amplification circuit of the two stage SiGe implementation.

moderate gain fluctuation with frequency (Fig. 11) through AWR simulations up to the 10 GHz limit. A mean noise ( $\sim$ RMS) of 1.2 mV for a gain of  $\sim$ 70 was achieved for the first iteration of the board, with an observed undershoot due to mismatch in lower frequencies.

### 5. Conclusion

In this paper, the bandwidth dependent charge and time resolution of high-speed 3D signals was discussed. Signals extend up to a limit of 5 GHz and adapted read-out electronics are necessary for an unbiased charge and noise measurement. Through an SPS-Pion test beam, time resolution studies are performed using a high bandwidth system, synchronized to the accelerator clock. The issue of higher induced noise in the larger capacitance LGAD device used as time reference is treated through a Gaussian low pass filter. Finally, a dedicated discrete electronics readout-out board with a  $\sim\!\!10$  GHz bandwidth limit was designed where DUTs are placed on a detachable mezzanine to enable rapid exchange and testing.

### **Declaration of competing interest**

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

### References

- B. Mandelli, The pixel Detector of the ATLAS Experiment for the run 2 at the large hadron collider, Nuclear & Particle Physics Proceedings 273–275 (2016) 1166–1172.

- [2] S. Grinstein, The ATLAS Forward Proton Detector (AFP), Nuclear and Particle Physics Proceedings 273–275 (2016) 1180–1184. ISSN 2405-6014.

- [3] G. Kramberger, et al., Timing performance of small cell 3D silicon detectors, Nucl. Instrum. Methods A 934 (2019) 26–32. ISSN 0168-9002.

- [4] Leena Diehl, et al., Comparison of the time resolution of unirradiated and irradiated LGADs and 3D sensors, Nucl. Instrum. Methods A 1046 (2023) 167691.

- [5] G. Brianti, The CERN Synchrotrons, CERN-97-04; RAL-97-011.

- [6] S. Grinstein, Beam Test Studies of 3D Pixel Sensors Irradiated Non-uniformly for the ATLAS Forward Physics Detector, NIMA Vol. vol. 730, p. 28-32, ISSN 0168-9002.

- [7] G. Pellegrini et al., 3D-Si single sided sensors for the innermost layer of the ATLAS pixel upgrade, NIMA, Vol. 924, p. 69-72, ISSN 0168-9002.

- [8] R.L. Workman, et al., (Particle data group), Prog. Theor. Exp. Phys. (2022), 083C01 (2022) and 2023 update.

- [9] H.F.W. Sadrozinski, et al., Ultra-fast silicon detectors (UFSD), NIM A 831 (2016) 18–23. ISSN 0168-9002.

- [10] Misgiyati, et al., Bayesian Inference of Poisson Distribution Using Conjugate and Non-informative Priors, Prosiding Seminar Nasional Metode Kuantitatif, 2017. ISBN 978-602-98559-3-7.

- [11] J. Baudot, et al., First Test Results of MIMOSA-26, a Fast CMOS Sensor with Integrated Zero Suppression and Digitized Output, 2009, IEEE NSS/MIC Record, Orlando, FL, USA, 2009, pp. 1169–1173. https://doi.org/10.1109/NSSMIC.2009.5402399.

- [12] Tektronix 6 Series B MSO Mixed Signal Oscilloscope Datasheet, https://download. tek.com/datasheet/MSO6B-Datasheet-EN-US-48W-61716-10.pdf.

- [13] H.-M. Rein, M. Möller, Design consideration for very-high-speed Si-bipolar IC's operating up to 50 Gb/s, IEEE J. Solid State Circ. 31 (8) (1996) 1076–1090.

- [14] Mini-Circuits ZX60-V63+ Wideband Amplifier Datasheet, https://www.minicircuits.com/pdfs/ZX60-V63+.pdf.