# Demonstrator system for the high-luminosity upgrade of the ATLAS hadronic Tile Calorimeter

Pavle Tsotskolauri, on behalf of the ATLAS Tile Calorimeter System\*,

Tbilisi State University, Tbilisi, Georgia pavle.tsotskolauri@cern.ch

### Abstract

The high-luminosity upgrade to the LHC (HL-LHC) leads to considerable challenges for the ATLAS detector, including greater radiation exposure to the on-detector electronics and increased pileup from low momentum collisions affecting trigger selection performance. The ATLAS Tile Calorimeter (TileCal) is a hadronic sampling calorimeter made of steel tiles as absorber and scintillating plastic tiles as active medium. The light produced by the tiles is read out by photomultiplier tubes (PMTs). The PMT signals are shaped, conditioned, and then digitized every 25 ns before being sent off-detector. A complete replacement of the onand off-detector electronics for TileCal will take place in preparation for the HL-LHC program in 2026. The new system is designed to digitize and transmit all sampled calorimeter data to the off-detector systems, where the data are stored in latency pipelines. Quasi-projective digital trigger tower sums are formed and forwarded to the level-1 trigger. The TileCal upgrade program has included extensive R&D and test beam campaigns. The new design includes state-of-the-art electronics with extensive use of redundancy and radiation-tolerant electronic components to avoid single points of failure. Multi-Gbps optic links drive the high volume of data transmission, and Field Programmable Gate Arrays (FPGAs) provide digital functionality both on- and off- detector.

A hybrid demonstrator prototype module, instrumented with new module electronics and interfaces for backward compatibility with the present system, was assembled and inserted in ATLAS in June 2019 to gain experience in actual detector conditions. We present the current status and test results from the Phase-II upgrade demonstrator module running in ATLAS.

#### Introduction

The upgrade of the Large Hadronic Collider (LHC) to the High-Luminosity LHC (HL-LHC) is aimed to deliver up to ten times peak luminosity [1]. HL-LHC is designed to deliver collisions at the luminosity of  $7.5 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> and up to 200 simultaneous proton-proton interactions per bunch crossing. This environment necessitated a Phase-II upgrade of the ATLAS detector [2].

### The Tile Calorimeter

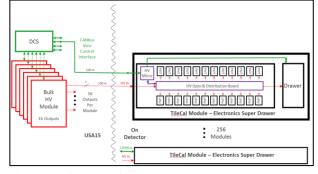

The Tile Calorimeter (TileCal) is the central section of the hadronic calorimeter of ATLAS. It plays an important role in the measurements of jet and missing transverse momentum, jet substructure, electron isolation, energy reconstruction and triggering, including muon information. To meet the requirements of HL-LHC, upgraded electronics were tested by using The Hybrid Demonstrator in real test environment. The Hybrid Demonstrator combining fully functional upgraded Phase-II electronics with analog trigger signals to be compatible with the current ATLAS interface. The Demonstrator comprises four mini-drawers, each equipped with 12 Photo-Multiplier Tubes (PMT) with upgraded 3-in-1 cards, one Mainboard, one Daughterboard, adder cards and one high voltage regulation board. a finger Low Voltage Power supply (fLVPS) powers all four minidrawers with 10V. The Hybrid Demonstrator is connected to an off-detector PreProcessor module via optical fibres. The Demonstrator PreProprocessor operates and reads out the hybrid Demonstrator[3].

#### Photo-Multiplier Tubes

When particles cross the scintillator tiles, produced light is transmitted by wavelength shifting fibres. Tiles in the tile calorimeter are grouped, forming cells A, BC and D. PMTs are responsible for converting this light coming from Tile-Cal cells into analog signal and transfer it to the next stage of a signal chain. Every PMT is equipped with a High Voltage Active Divider (HVAD). The function of HVAD is to divide high voltage coming from high voltage system to 8 PMT dynodes. The high voltage for PMTs is in the range of 600-900 Volts. HVAD is also responsible for linear PMT response. PMT Block consists of PMT, HVAD, upgraded 3-in-1 card, iron and mu-metal cylinders. For individual PMTs and PMT Blocks, there are two different test benches to ensure their performance and correct functionality. Before PMT Blocks are assembled each PMT is tested to ensure their physical properties. After this, PMT Blocks are tested using Portable Readout Module for Tile Electronics (PROMETEO) system which ensures the correct functionality of PMT blocks alongside rest of the demonstrator components [3].

# Upgraded 3-in-1 card

The upgraded 3-in-1 card is part of the PMT Blocks, see Figure 1. They are responsible for shaping, amplification and integration of signal coming from the PMTs. Upgraded 3-in-1 cards feature a 16-bit dynamic range, 50ns full width at half maximum (FWHM) time constant, fast readout with two gains (low gain and high gain), integrated slow

<sup>\*</sup> Copyright [2022] CERN for the benefit of the ATLAS Collaboration. Reproduction of this article or parts of it is allowed as specified in the CC-BY-4.0 license

readout, charge injection for continuous calibration over full dynamic range. The analog sums are transmitted to the current ATLAS L1Calo system. The Low/High gain and integrator signals from the 3-in-1 are digitized by ADCs in the Mainboards and then transmitted to the Daughter-Boards.

Figure 1: Picture of the upgraded 3-in-1 card, currently used by the Demonstrator [3].

## Mainboard

The Demonstrator consists of four mainboards. The picture of the Mainboard is shown in Figure 2. Currently, Mainboard went through four revisions. The Mainboard is responsible for data transfer between PMT Blocks and Daughterboard. Each of them is connected to 12 PMT Blocks. Field Programmable Gate Arrays (FPGA) are used to configure the ADCs and provide clock signal. For The PMT Block readout, the Mainboard uses 12-bit ADC at 40 Msps and 16-bit ADC for slow integration. The Mainboard is designed to be reliable and redundant, therefore it is divided into two sections called A- and B- Side. Each section is completely independent with each side having +10V LVPS supply bricks. In ordered to prevent failure caused by LVPS or total failure each side is connected with a "Diode-Or" connection to make the power supply more redundant. Other functions of the Mainboard are to provide timing signals for low- and high-gain Charge Injection (CIS) calibrations. Mainboard V4 is the final revision that will be used in HL-LHC

Figure 2: Picture of the Mainboard version 4 installed in the Demonstrator [3].

# Daughterboard

The Daughterboard is an on-detector communication board that interfaces between front-end electronics and back-end Tile Pre-Processor (TilePPr) module, the Daughterboard is shown in Figure 3. This is 4th version of the Daughterboard. It sends PMT data and Detector Control System (DCS) and detector readout data to TilePPr over multi-gigabit links. Like the Mainboard, the Daughterboard is also divided into two sections for reliability and redundancy. Redundant optical fibres are also used for protection against single link failure. The GBTx chip developed by CERN is used for remote FPGA and Flash memory configuration. The Daughterboard version 6 is available and is being tested at CERN test beam facilities. Replacement with the latest version on The Demonstrator is under consideration.

Figure 3: Picture of the Daughterboard version 4 installed in the Demonstrator. [3].

## PreProcessor

The PreProcessor (PPr) is the core element of the TileCal off-detector readout electronics. PMT digital samples are transferred to the PPr every bunch crossing, a picture of the PPr is shown in Figure 4. The PPr has bi-directional communication with front-end electronics. It provides DCS commands, timing, trigger and control information and the LHC clock to the front-end electronics. From front-end electronics, the PPr receives PMT data which is stored in pipeline buffers waiting for trigger decision. After the trigger decision, The PPr sends buffered data to legacy Read-Out Driver (ROD) and processes in the same way as for current modules (backward compatibility).

Figure 4: Picture of the Tile PreProcessor, which is currently used for the Demonstrator readout [3].

## Low Voltage Power Supply

The Tile Calorimeter Low Voltage Power Supply (LVPS) provides power to all front-end electronics and provides control and feedback to the monitoring system. Figure 5 is picture of the LVPS. Previous LVPS modules were generating eight different voltages for various subcircuits of front-end electronics. In Phase-II upgrade each super-drawer is powered by one LVPS module which now provides 10V supply to all the front-end. As the result, Tile-Cal has 256 LVPS boxes. Each LVPS box consists of eight bricks which converts 200V input voltage to 10V output. For redundancy eight bricks are grouped into four sets of two bricks.

Figure 5: Low Voltage Power Supply for the Demonstrator [3].

# High Voltage Power Supply

High Voltage Power Supply (HVPS) must supply high voltage to all PMTs in the system. it also needs to monitor, control and report values to DCS System, as shown in Figure 6. There is a total of 256 high voltage regulation boards each equipped with an ethernet interface.

Figure 6: Diagram of the High Voltage Power Supply system [3].

# Test Beam Results

The Demonstrator together with TileCal modules equipped with the legacy system was exposed to different particles and energies in 7 test beam campaigns at CERN SPS North Area, during 2015-2018 [3].

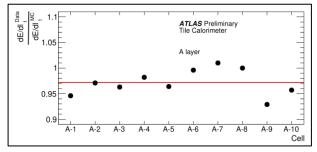

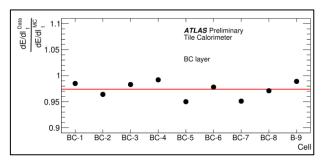

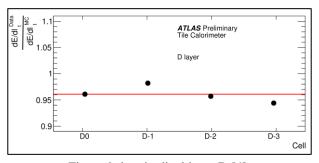

The uniformity of the Demonstrator module, which is segmented into three longitudinal layers (A - Figure 7 BC - Figure 8 and D - Figure 9), was studied using muon beams.

Figure 7: longitudinal layer A [4].

Figure 8: longitudinal layer BC [4].

Figure 9: longitudinal layer D [4].

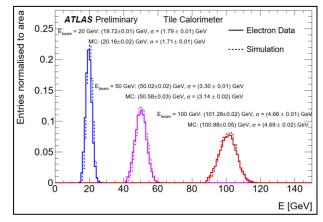

Figure 10 shows the distribution of the total energy deposited in the calorimeter obtained using experimental and simulated electron data.

Figure 10: Total energy deposited in the calorimeter obtained using electron beams [4].

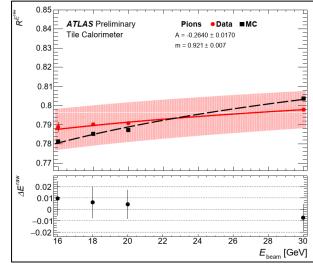

Detector energy response and resolution were studied using the hadron beams with different energies. The results are shown in Figure 11.

Figure 11: Energy response ratios, measured experimentally (red circles) and predicted by simulation (black squares) as a function of beam energy obtained using pions [4]

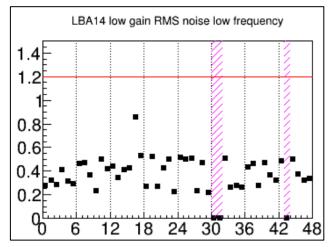

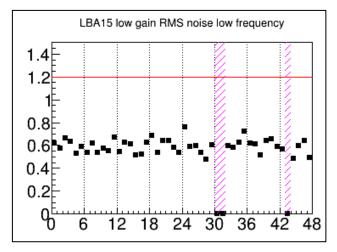

Figure 12 and Figure 13 show a comparison of noise between The Demonstrator and Legacy Module.

Figure 12: RMS noise levels of the low gain channels of the Demonstrator

Figure 13: RMS noise levels of the low gain channels of the legacy module

The above test beam results indicate that the Demonstrator Module performs at least as good as the legacy module.

#### Prometeo

The Portable ReadOut ModulE for Tile ElectrOnics (PRO-METEO), is a mobile test-bench for the in situ certification of the TileCal on-detector electronics at the HL-LHC. It represents an independent and completely autonomous system that includes all necessary components to verify the correct functionality of TileCal on-detector electronics.

# **SUMMARY**

The Tile Demonstrator Module is a prototype of the upgraded readout system for the HL-LHC. It is fully integrated into the ATLAS TDAQ and DCS systems. It was extensively tested during 2015, 2016 and 2017 test beams and demonstrated good performance. New tests will take place in November 2022 in order to validate new on-detector electronics in the radiation environment and associated off-detector electronics. The Tile Demonstrator module will also be present in Tile Calorimeter during the Run-3 period.

## ACKNOWLEDGMENTS

The author was supported by Shota Rustaveli National Science Foundation of Georgia through the grant project No DI-18-293

# REFERENCE

- High-Luminosity Large Hadron Collider (HL-LHC): Technical design report, CERN-2020-010, <u>https://cds.cern.ch/record/2749422</u>

- [2] The ATLAS Experiment at the CERN Large Hadron Collider, JINST 3 (2008) S08003, <u>https://iopscience.iop.org/article/10.1088/1748-</u> 0221/3/08/S08003

- [3] Technical Design Report for the Phase-II Upgrade of the ATLAS Tile Calorimeter, ATLAS-TDR-028, <u>https://cds.cern.ch/record/2285583</u>

- [4] Upgrade of the ATLAS Hadronic Tile Calorimeter for the High Luminosity LHC, ATL-TILECAL-PROC-2020-009, <u>https://iopscience.iop.org/article/10.1088/1748-0221/15/09/C09003</u>