## Global Trigger Technological Demonstrator for ATLAS Phase-II upgrade

*Virtual 2020 IEEE Nuclear Science Symposium (NSS) and Medical Imaging Conference (MIC)*

4 November 2020

Viacheslav Filimonov, Bruno Bauss, Volker Büscher, Ulrich Schäfer, Duc Bao Ta On behalf of the ATLAS TDAQ Collaboration

# Introduction

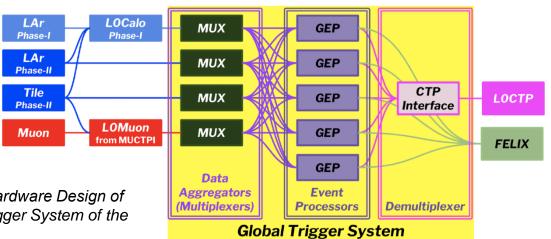

#### Phase-II Global Trigger system: Functionality

- As part of the Phase-II Level-0 Trigger System, the Global Trigger uses fullgranularity calorimeter cells to refine L0Calo & L0Muon output

- Allows iterative algorithms such as topoclustering and use of higher level synthesis

- Reconstructs taus, jets, MET, & calorimeter-based isolation

- Applies topological requirements

#### **Phase-II Global Trigger system: Implementation**

- Time-multiplexed system concentrates data of full event into a single processor

- Composed of 3 main layers

- Multiplexing (MUX) layer

- Global Event Processor (GEP) layer

- Demultiplexing Global-to-Central Trigger Processor (CTP) Interface

- Input: >2300 optical fibers with link speeds up to 25.8 Gb/s

- Global Common Module (GCM) is used as the building block in each layer

- See talk by S. Tang: "The Prototype Hardware Design of Global Common Module for Global Trigger System of the ATLAS Phase II Upgrade"

#### Phase-II Global Trigger system: Deployment Module

- Production Firmware Deployment Module (PFM):

- Serves a dual purpose

- A hardware platform required by each group involved in the GCM firmware development

- Used for pre-commissioning of regular firmware upgrades with the production system in place

- Represents a **slice of the GCM** (including a processing unit, a control FPGA and a number of optical modules) in any layer of the Global Trigger system

- Will be **available well before the production GCM** to allow for early development, testing and debugging of the algorithm and infrastructure firmware

- Design based on the Technological Demonstrator R&D

4 Nov 2020

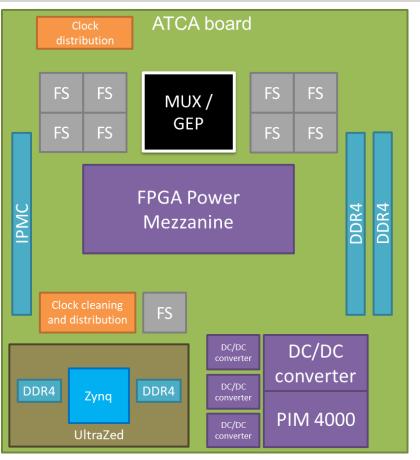

#### Phase-II Global Trigger system: PFM Structure

- ATCA board

- Single MUX / GEP FPGA (Xilinx Ultrascale+ VU13P)

- Up to 8 Finisar BOA modules for real-time data path

- Single Finisar BOA module for interface to FELIX

- UltraZed board with **Zynq UltraScale+**

- IPMC

- Power mezzanines

- DDR4 RAMs

- Many PCB design blocks tested on the Technological Demonstrator

- PCB design is complete

# Global Trigger Technological Demonstrator

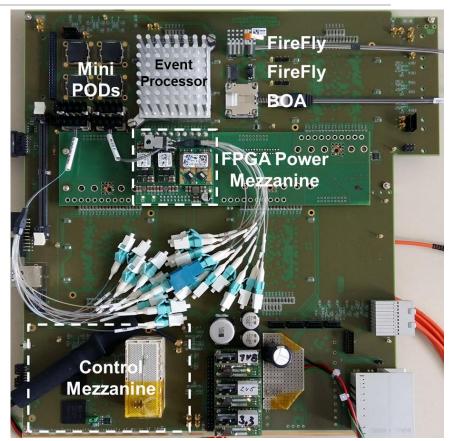

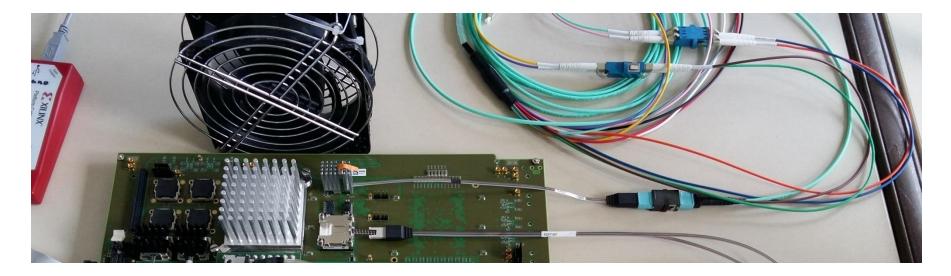

#### **Technological Demonstrator**

- GCM and PFM required an R&D for the new generation of optical modules and FPGAs running at high data rates (up to 25.8 Gb/s) → Technological Demonstrator board designed and tested

- A custom designed ATCA board

- One Xilinx Virtex UltraScale+ 9P FPGA

- Two 28G 2x4 bidirectional Samtec FireFly modules

- One 28G 2x12 bidirectional Finisar BOA module

- Six MiniPODs: 3 RX + 3 TX

- Mezzanines: Power, Control

- Optical modules implemented on-board

Technological Demonstrator

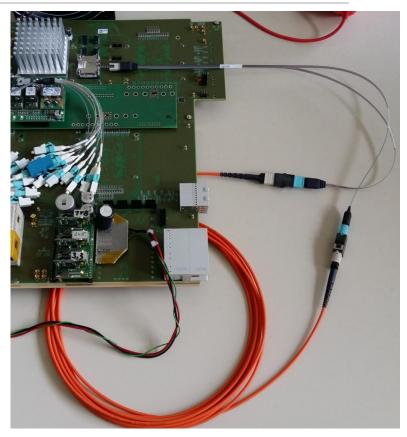

#### Finisar BOA IBERT loopback test: test setup

- Performance of the high-speed optical modules and the FPGA on the Technological Demonstrator has been evaluated with long-run loopback Integrated Bit Error Ratio Tests (IBERT)

- 12 transmitter links of the optical module were looped back to 12 receiver links of the same module with a help of a 24 to 2x12-fiber Y-cable and a 12-fiber trunk cable

#### Link status

- A day-long IBERT test run at 25.65 Gb/s performed

- 31-bit PRBS pattern used

- 1.9E-15 BER reached

- All 12 links functional

- No bit errors detected

| Name                                  | TX           | RX           | Status      | Bits    | Errors | BER       | BERT Reset | TX Pattern  |   | RX Pattern  |   | TX Pre-Cursor   |   | TX Post-Cur  |

|---------------------------------------|--------------|--------------|-------------|---------|--------|-----------|------------|-------------|---|-------------|---|-----------------|---|--------------|

| Ungrouped Links (0)                   |              |              |             |         |        |           |            |             |   |             |   |                 |   |              |

| <ul> <li>Link Group 0 (12)</li> </ul> |              |              |             |         |        |           | Reset      | PRBS 31-bit | ~ | PRBS 31-bit | ~ | 0.00 dB (00000) | ~ | 0.00 dB (000 |

| % Link 0                              | MGT_X0Y43/TX | MGT_X0Y40/RX | 25.652 Gbps | 5.27E14 | 0E0    | 1.897E-15 | Reset      | PRBS 31-bit | ~ | PRBS 31-bit | ~ | 0.00 dB (00000) | ~ | 0.00 dB (00  |

| % Link 1                              | MGT_X0Y40/TX | MGT_X0Y43/RX | 25.651 Gbps | 5.27E14 | 0E0    | 1.897E-15 | Reset      | PRBS 31-bit | ~ | PRBS 31-bit | ~ | 0.00 dB (00000) | ~ | 0.00 dB (00  |

| % Link 2                              | MGT_X0Y42/TX | MGT_X0Y41/RX | 25.651 Gbps | 5.27E14 | 0E0    | 1.897E-15 | Reset      | PRBS 31-bit | ~ | PRBS 31-bit | ~ | 0.00 dB (00000) | ~ | 0.00 dB (000 |

| % Link 3                              | MGT_X0Y41/TX | MGT_X0Y42/RX | 25.651 Gbps | 5.27E14 | 0E0    | 1.897E-15 | Reset      | PRBS 31-bit | ~ | PRBS 31-bit | ~ | 0.00 dB (00000) | ~ | 0.00 dB (00  |

| % Link 4                              | MGT_X0Y35/TX | MGT_X0Y22/RX | 25.651 Gbps | 5.27E14 | 0E0    | 1.897E-15 | Reset      | PRBS 31-bit | ~ | PRBS 31-bit | ~ | 0.00 dB (00000) | ~ | 0.00 dB (000 |

| % Link 5                              | MGT_X0Y34/TX | MGT_X0Y23/RX | 25.651 Gbps | 5.27E14 | 0E0    | 1.897E-15 | Reset      | PRBS 31-bit | ~ | PRBS 31-bit | ~ | 0.00 dB (00000) | ~ | 0.00 dB (000 |

| % Link 6                              | MGT_X0Y33/TX | MGT_X0Y20/RX | 25.651 Gbps | 5.27E14 | 0E0    | 1.897E-15 | Reset      | PRBS 31-bit | ~ | PRBS 31-bit | ~ | 0.00 dB (00000) | ~ | 0.00 dB (000 |

| % Link 7                              | MGT_X0Y32/TX | MGT_X0Y21/RX | 25.650 Gbps | 5.27E14 | 0E0    | 1.897E-15 | Reset      | PRBS 31-bit | ~ | PRBS 31-bit | ~ | 0.00 dB (00000) | ~ | 0.00 dB (000 |

| % Link 8                              | MGT_X0Y19/TX | MGT_X0Y15/RX | 25.651 Gbps | 5.27E14 | 0E0    | 1.897E-15 | Reset      | PRBS 31-bit | ~ | PRBS 31-bit | ~ | 0.00 dB (00000) | ~ | 0.00 dB (000 |

| % Link 9                              | MGT_X0Y18/TX | MGT_X0Y13/RX | 25.651 Gbps | 5.27E14 | 0E0    | 1.897E-15 | Reset      | PRBS 31-bit | ~ | PRBS 31-bit | ~ | 0.00 dB (00000) | ~ | 0.00 dB (000 |

| % Link 10                             | MGT_X0Y17/TX | MGT_X0Y14/RX | 25.651 Gbps | 5.27E14 | 0E0    | 1.897E-15 | Reset      | PRBS 31-bit | ~ | PRBS 31-bit | ~ | 0.00 dB (00000) | ~ | 0.00 dB (000 |

| % Link 11                             | MGT_X0Y16/TX | MGT_X0Y12/RX | 25.651 Gbps | 5.27E14 | 0E0    | 1.897E-15 | Reset      | PRBS 31-bit | ~ | PRBS 31-bit | ~ | 0.00 dB (00000) | ~ | 0.00 dB (000 |

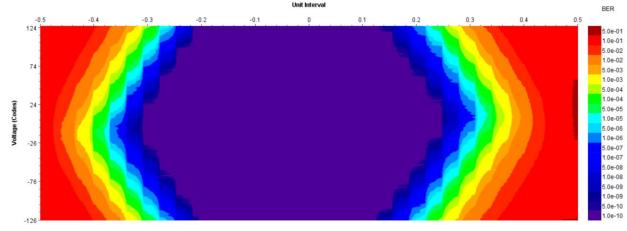

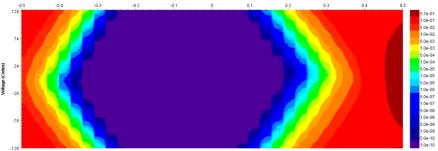

## Eye diagram

- A typical eye diagram

- Low Power Mode of the GTY receiver

- Open area: 7608, Open UI: 57.58 %, 25.65 Gb/s data rate

- Good performance

| Summary      |                      | Metrics    |       | Settings             |                       |

|--------------|----------------------|------------|-------|----------------------|-----------------------|

| Name:        | SCAN_113             | Open area: | 7608  | Link settings:       | N/A                   |

| Description: | 40-43                | Open UI %: | 57.58 | Horizontal increment | 2                     |

| Started:     | 2020-Oct-30 17:04:45 |            |       | Horizontal range:    | -0.500 UI to 0.500 UI |

| Ended:       | 2020-Oct-30 17:40:54 |            |       | Vertical increment   | 2                     |

|              |                      |            |       | Vertical range:      | 100%                  |

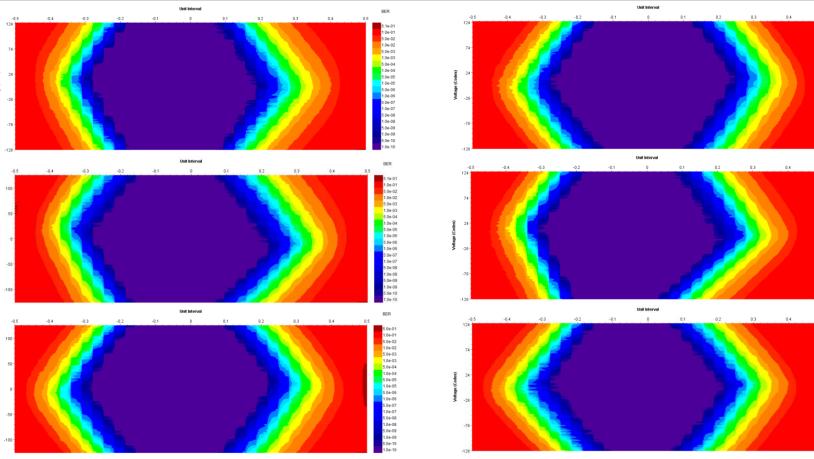

#### Eye diagrams: other channels

4 Nov 2020

BER

5.0e-01 1.0e-01

5.0e-02

1.0e-02

5.0e-03

1.0e-03

5.0e-04 1.0e-04

5.0e-05

1.0e-05

5.0e-06

1.0e-06

5.0e-07

1.0e-07

5.0e-08

1.0e-08

5.0e-09

1.0e-09 5.0e-10

REF

1e-01

1.0e-01 5.0e-02

1.0e-02

5.0e-03

1.0e-03

5.0e-04

1.0e-04

0e-05

1.0e-05

0e-06

.0e-06

0e-0

.0e-07

0e-08

.0e-08

.0e-09

.0e-09

0e-10

5.0e-01 1.0e-01 5.0e-02

1.0e-02

5.0e-03

1.0e-03

5.0e-04

1.0e-04

5.0e-05 1.0e-05

5.0e-06

1.0e-06

5.0e-07

1.0e-07

5.0e-08

1.0e-08 5.0e-09 1.0e-09 5.0e-10 1.0e-10

JGU

0.5

#### 4 Nov 2020

JGU

#### Eye diagrams: other channels

#### Samtec FireFly IBERT loopback test: test setup

4 transmitter links of the optical module were looped back to 4 receiver links of the same module with a help of a 12-fiber MTP to LC breakout cable

4 Nov 2020

#### Link status

- A day-long IBERT test run at 27.58 Gb/s performed

- 31-bit PRBS pattern used

- 1.7E-15 BER reached

- All 4 links functional

- No bit errors detected

| Name                | ТХ           | RX           | Status      | Bits     | Errors | BER       | BERT Reset | TX Pattern  | RX Pattern                      |   | TX Pre-Cursor   |   | TX Post-Curs  |

|---------------------|--------------|--------------|-------------|----------|--------|-----------|------------|-------------|---------------------------------|---|-----------------|---|---------------|

| Ungrouped Links (0) |              |              |             |          |        |           |            |             |                                 |   |                 |   |               |

| Sink Group 0 (4)    |              |              |             |          |        |           | Reset      | PRBS 31-bit | <ul> <li>PRBS 31-bit</li> </ul> | ~ | 0.00 dB (00000) | ~ | 0.00 dB (0000 |

| % Link 0            | MGT_X0Y54/TX | MGT_X0Y54/RX | 27.576 Gbps | 5.732E14 | 0E0    | 1.744E-15 | Reset      | PRBS 31-bit | <ul> <li>PRBS 31-bit</li> </ul> | ~ | 0.00 dB (00000) | ~ | 0.00 dB (0000 |

| % Link 1            | MGT_X0Y55/TX | MGT_X0Y55/RX | 27.575 Gbps | 5.732E14 | 0E0    | 1.744E-15 | Reset      | PRBS 31-bit | <ul> <li>PRBS 31-bit</li> </ul> | ~ | 0.00 dB (00000) | ~ | 0.00 dB (0000 |

| % Link 2            | MGT_X0Y53/TX | MGT_X0Y52/RX | 27.575 Gbps | 5.732E14 | 0E0    | 1.744E-15 | Reset      | PRBS 31-bit | <ul> <li>PRBS 31-bit</li> </ul> | ~ | 0.00 dB (00000) | ~ | 0.00 dB (000( |

| % Link 3            | MGT_X0Y52/TX | MGT_X0Y53/RX | 27.575 Gbps | 5.732E14 | 0E0    | 1.744E-15 | Reset      | PRBS 31-bit | <ul> <li>PRBS 31-bit</li> </ul> | ~ | 0.00 dB (00000) | ~ | 0.00 dB (000( |

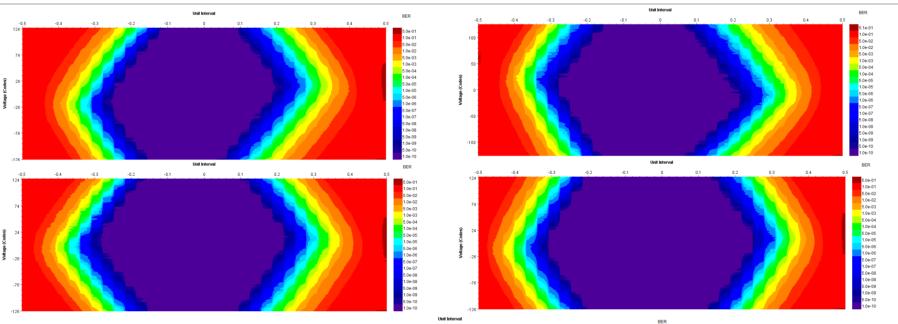

## Eye diagram

- A typical eye diagram

- Low Power Mode of the GTY receiver

- Open area: 8612, Open UI: 63.64%, 27.58 Gb/s data rate

- Good performance

| ummary       |                      | Metrics    |       | Settings              |                       |  |  |  |

|--------------|----------------------|------------|-------|-----------------------|-----------------------|--|--|--|

| Name:        | SCAN_11              | Open area: | 8612  | Link settings:        | N/A                   |  |  |  |

| Description: | 52-53_E10_2          | Open UI %: | 63.64 | Horizontal increment: | 2                     |  |  |  |

| Started:     | 2020-Oct-26 15:06:55 |            |       | Horizontal range:     | -0.500 UI to 0.500 UI |  |  |  |

| Ended:       | 2020-Oct-26 15:42:44 |            |       | Vertical increment    | 2                     |  |  |  |

|              |                      |            |       | Vertical range:       | 100%                  |  |  |  |

#### 4 Nov 2020

#### Eye diagrams: other channels

#### Summary

- The high-speed link support is essential for the Global Trigger system in order to cope with the transmission of high-granularity calorimeter data which drives the bandwidth requirements

- A technological demonstrator has been designed and used for evaluation of 25+ Gb/s Samtec FireFly and Finisar BOA optical modules implemented on-board together with the Xilinx Virtex UltraScale+ 9P FPGA

- A good performance and absence of bit errors during long runs have been demonstrated for both high-speed optical modules

# BACKUP

#### **VU13P PFM Floor plan**

OM = Optical Module connection Connections to a single optical module are grouped with braces

| ſ   | I: 4xOM<br>O: 4xOM<br>I: 4xOM | GTY Quad 135<br>X0Y60-X0Y63<br>AA [LN]<br>GTY Quad 134<br>X0Y56-X0Y59<br>Z [LN]<br>GTY Quad 133 | CMAC<br>X0Y11<br>CMAC<br>X0Y10 | HP VO Bank 75<br>K<br>Readout<br>HP DDR4 <sup>k 74</sup><br>Memory | ILKN<br>X1Y7<br>SYSMON<br>Configuration                     | GTY Quad 235<br>X1Y60-X1Y63<br>K [RN]<br>GTY Quad 234<br>X1Y56-X1Y59<br>J [RN]<br>GTY Quad 233 | I: 4xOM<br>O: 4xOM<br>I: 4xSoC<br>O: 4xSoC<br>I: 4xSoC |

|-----|-------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| 1   | O: 4xOM<br>I: 4xOM            | X0Y52-X0Y55<br>Y [LN] (RCAL)<br>GTY Quad 132<br>X0Y48-X0Y51                                     | ILKN HP I/O Bank 73            | Configuration<br>PCIE4                                             | X1Y52-X1Y55<br>I [RN] (RCAL)<br>GTY Quad 232<br>X1Y48-X1Y51 | O: 4xSoC<br>I: 4xOM                                                                            |                                                        |

| Ļ   | O: 4xOM                       | X [LN]                                                                                          | X0Y9                           | SLR Crossing                                                       | X0Y3                                                        | H [RN]                                                                                         | O: 4xOM                                                |

|     | I: 4xOM                       | GTY Quad 131                                                                                    | 0140                           |                                                                    |                                                             | GTY Quad 231                                                                                   |                                                        |

|     | 0: 4x0M                       | X0Y44-X0Y47<br>W [LUC]                                                                          | CMAC<br>X0Y8                   | HP I/O Bank 71<br>H (Partial)                                      | ILKN<br>X1Y5                                                | X1Y44-X1Y47<br>G [RUC]                                                                         |                                                        |

| 4   | I: 4xOM<br>O: 4xOM            | GTY Quad 130<br>X0Y40-X0Y43<br>V [LUC]                                                          | CMAC<br>X0Y7                   | HP I/O Bank 70<br>G                                                | SYSMON<br>Configuration                                     | GTY Quad 230<br>X1Y40-X1Y43<br>F IRUC1                                                         | I: 4xOM<br>O: 4xOM                                     |

|     | I: 4xOM<br>O: 4xOM            | GTY Quad 129<br>X0Y36-X0Y39<br>U [LUC] (RCAL)                                                   | ILKN<br>X0Y4                   | HP I/O Bank 69                                                     | Configuration                                               | GTY Quad 229<br>X1Y36-X1Y39<br>E [RUC] (RCAL)                                                  |                                                        |

| ľ   | I: 4xOM<br>O: 4xOM            | GTY Quad 128<br>X0Y32-X0Y35<br>T [LUC]                                                          | CMAC<br>X0Y6                   | HP I/O Bank 68                                                     | PCIE4<br>X0Y2                                               | GTY Quad 228<br>X1Y32-X1Y35<br>D [RUC]                                                         |                                                        |

| - 1 |                               | GTY Quad 127                                                                                    |                                | SLR Crossing                                                       |                                                             | GTY Quad 227                                                                                   |                                                        |

| 1   | I: 4xOM<br>O: 4xOM            | X0Y28-X0Y31<br>S [LLC]                                                                          | CMAC<br>X0Y5                   | HP I/O Bank 67                                                     | ILKN<br>X1Y3                                                | X1Y28-X1Y31<br>C [RLC]                                                                         | I: 2xIPBUS<br>O: 2xIPBUS, 2xMMCX                       |

|     | I: 4xOM<br>O: 4xOM            | GTY Quad 126<br>X0Y24-X0Y27<br>R [LLC]                                                          | CMAC<br>X0Y4                   | HP I/O Bank 66<br>B (Partial)                                      | SYSMON<br>Configuration                                     | GTY Quad 226<br>X1Y24-X1Y27<br>B [RLC]                                                         |                                                        |

| - [ | I: 4xOM<br>O: 4xOM            | GTY Quad 125<br>X0Y20-X0Y23<br>Q [LLC] (RCAL)                                                   | ILKN<br>X0Y2                   | HP I/O Bank 65<br>C                                                | Configuration                                               | GTY Quad 225<br>X1Y20-X1Y23<br>A [RLC] (RCAL)                                                  | I: 4xOM<br>O: 4xOM                                     |

| 4   | I: 4xOM<br>O: 4xOM            | GTY Quad 124<br>X0Y16-X0Y19<br>AF [LLC]                                                         | CMAC<br>X0Y3                   | HP I/O Bank 64                                                     | PCIE4<br>X0Y1<br>(tandem)                                   | GTY Quad 224<br>X1Y16-X1Y19<br>P [RLC]                                                         | I: 4xOM<br>O: 4xOM                                     |

| - 1 |                               |                                                                                                 |                                | SLR Crossing                                                       |                                                             |                                                                                                |                                                        |

|     | I: 4xOM<br>O: 4xOM            | GTY Quad 123<br>X0Y12-X0Y15<br>AE [LS]                                                          | CMAC<br>X0Y2                   | HP I/O Bank 63<br>F                                                | ILKN<br>X1Y1                                                | GTY Quad 223<br>X1Y12-X1Y15<br>O [RS]                                                          | I: 4xOM<br>O: 4xOM                                     |

|     | I: 4xOM<br>O: 4xOM            | GTY Quad 122<br>X0Y8-X0Y11<br>AD [LS]                                                           | CMAC<br>X0Y1                   | DDR4                                                               | SYSMON<br>Configuration                                     | GTY Quad 222<br>X1Y8-X1Y11<br>N [RS]                                                           | I: 4xOM<br>O: 4xOM                                     |

|     | I: 4xOM<br>O: 4xOM            | GTY Quad 121<br>X0Y4-X0Y7<br>AC [LS] (RCAL)                                                     | ILKN<br>X0Y0                   | HP I/O Bank 61                                                     | Configuration                                               | GTY Quad 221<br>X1Y4-X1Y7<br>M [RS] (RCAL)                                                     | I: 4xOM<br>O: 4xOM                                     |

| l   | I: 4xOM<br>O: 4xOM            | GTY Quad 120<br>X0Y0-X0Y3<br>AB [LS]                                                            | CMAC<br>X0Y0                   | HP I/O Bank 60                                                     | PCIE4<br>X0Y0                                               | GTY Quad 220<br>X1Y0-X1Y3<br>L [RS]                                                            | I: 4xOM<br>O: 4xOM                                     |

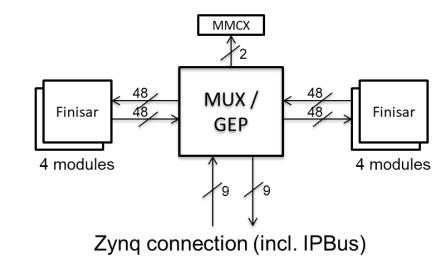

#### **MUX / GEP MGT connections**

- 32 GTY quads (128 RX, 128 TX) available, providing the following connectivity

- Connection to optical modules (96 RX, 96 TX)

- Zynq connection (8 RX, 8 TX)

- IPBus connection: Zynq ↔ MUX / GEP (1 RX, 1 TX)

- Debug (2 TX)

- Spare (23 RX, 21 TX)

MGTs + Finisars operation tested on the Demonstrator

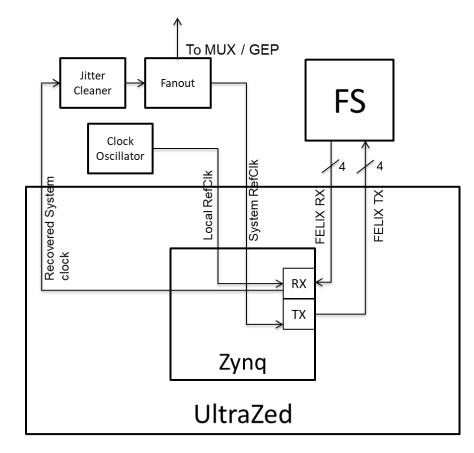

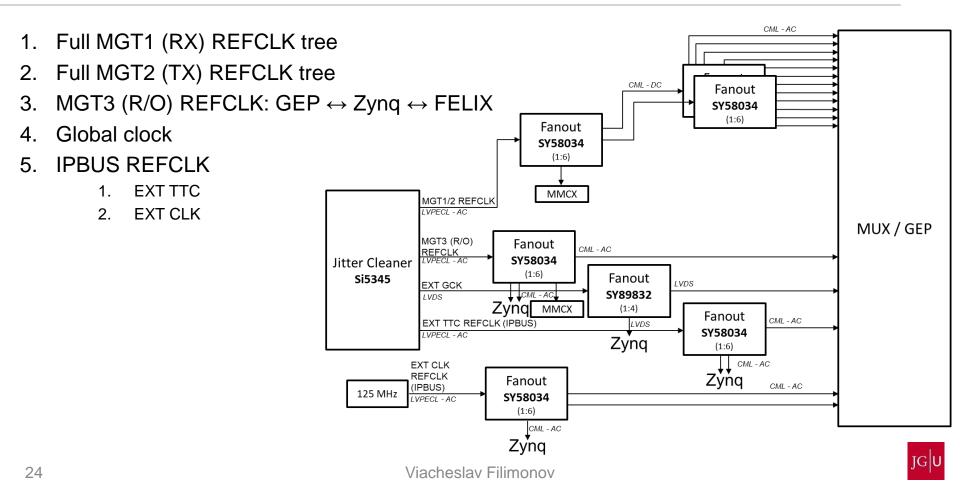

#### **Clock distribution for FELIX interface**

- FELIX RX

- TTC

- FELIX TX

- Data

- Busy

- Samtec high-speed boardto-board connector

- Speed rating: 14GHz / 28Gbps

http://suddendocs.samtec.com/testreports/hsc-reportsma\_seam8-seaf8-07mm\_web.pdf

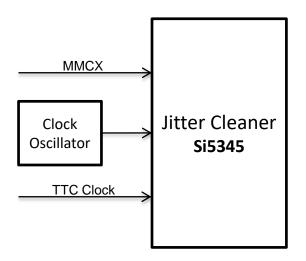

#### **Clock scheme: Jitter Cleaner's input options**

- Three input options

- Recovered TTC clock

- Clock oscillator

- MMCX connectors

#### **Clock trees**

- The MGTs reference clock scheme is designed to minimize the number of signals routed on the PCB

- The reference clocks for a QUAD can also be sourced from one QUAD below or above for high data rates (16.375 – 28.21 Gb/s) and for up to two QUADs below or above for low data rates (below 16.375 Gb/s)

- Reference clock sharing between different SLRs is not allowed

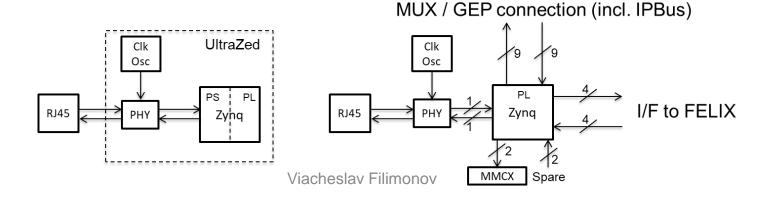

#### **Control block**

- The Control block provides many of the (non-real-time) services required on the PFM prototype

- Hosts the control FPGA of the PFM prototype

- Hosts the MasterSPI configuration circuitry for processor and control FPGAs

- Clock cleaning and distribution

- Monitoring and slow control

- IPbus master

- Interface to FELIX (Incl. TTC clock recovery)

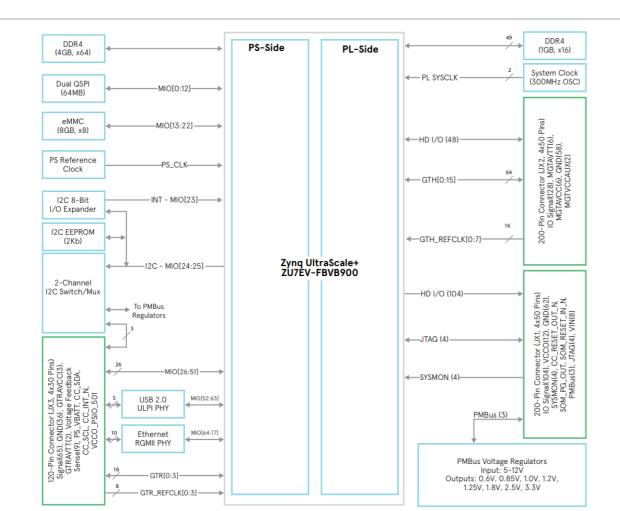

- ZYNQ Ultrascale+ (XCZU7EV-FBVB900) device is used as the control FPGA

- The Control FPGA is located on a commercial system on a module (SoM) from Avnet (UltraZed-EV SOM)

#### Zynq MGT connections

- Four quads (16 RX, 16 TX) available, providing the following connectivity

- Interface to FELIX (4 RX, 4 TX)

- MUX / GEP connection (8 RX, 8 TX)

- IPBus connection: PHY chip (on the main board)  $\leftrightarrow$  Zynq, Zynq  $\leftrightarrow$  MUX / GEP (2 RX, 2 TX)

- Debug (2 TX)

- Spare (2 RX)

- IPBus connection can also use the PS side of the Zynq

- PHY chip on UltraZed

- Flexibility of implementing IPBus either in the PL or PS side of the Zynq

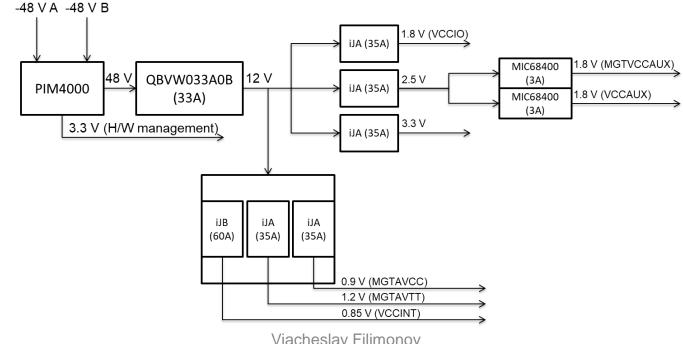

PIM4000 converter, QBVW033A0B DC/DC converter, power mezzanines (based on the TDK-Lambda iJX series of DC/DC converters), linear MIC68400 regulators

4 Nov 2020

#### Power sequencing and operating voltages

- Power on sequence is controlled by a dedicated CPLD, which monitors the Power Good signals of every power regulator

- 1. Board level 2.5 V and 3.3 V

- 2. VCCINT, MGTAVCC

- 3. MGTAVTT, VCCAUX, MGTVCCAUX

- 4. VCCIO

- Operating voltages

- VCCINT: 0.85 V

- MGTAVCC: 0.9 V

- MGTAVTT: 1.2 V

- VCCAUX, MGTVCCAUX, VCCIO: 1.8 V

#### **UltraZed**