# Investigation of modified ATLAS pixel implantations after irradiation with neutrons

A. Gisen\*, S. Altenheiner, C. Gößling, M. Grothe, R. Klingenberg<sup>1</sup>, K. Kröninger, J. Lönker, M. Weers, T. Wittig<sup>2</sup>, F. Wizemann

TU Dortmund, Experimentelle Physik IV, 44221 Dortmund, Germany

#### Abstract

The innermost part of the tracking detector of the ATLAS experiment consists mainly of planar n<sup>+</sup>-in-n silicon pixel

achieve higher signal charge and efficiency at the same voltages or to achieve the same signal charge and efficiency at lower voltages.

Previous investigations showed an increased signal charge after irradiation for thinner detectors [6] and at higher

Abstract

The innermost part of the tracking detector of the ATLAS experiment consists mainly of planar n<sup>+</sup>-in-n silicon pixel sensors. During the phase-0 upgrade, the Insertable B-Layer (IBL) was installed closest to the beam pipe. Its pixel sensors. During the phase-0 upgrade, the Insertable B-Layer (IBL) was installed closest to the beam pipe. Its pixel sensors were bump bonded to FE-14 read-out chips. One of these modules was irradiated with reactor neutrons up to a fluence of 5 × 10<sup>15</sup> n<sub>eq</sub>cm<sup>-2</sup>.

This contribution presents important sensor characteristics, charge collection determined with radioactive sources and hit efficiency neasurements, performed in laboratory and test beam, of this irradiated device. It is shown that the new modified designs perform similar or better than the IBL standard design in terms of charge collection and tracking efficiency, at the cost of a slightly increased leakage current.

\*\*Common of the major experiments at the CERN LHC is ATLAS-LHC, Insertable B-Layer IBL, Planar n<sup>+</sup>-in-n Pixel Sensors, Modifications are made to the beam pipe. As the other layers of the pixel detector, it consists of planar n<sup>+</sup>-in-n silicon pixel sensors, but their design layout was revised [4] and new front-end electronics, the FE-14 read-out chips [5], were used. The IBL is consists of planar n<sup>+</sup>-in-n silicon pixel sensors, but their design layout was revised [4] and new front-end electronics, the FE-14 read-out chips [5], were used. The IBL is consists of planar n<sup>+</sup>-in-n silicon pixel sensors, but their design darage included in the sensors. For this purious design layout was revised [4] and new front-end electronics, the FE-14 read-out chips [5], were used. The IBL is consist of planar n<sup>+</sup>-in-n silicon pixel sensors, but their design layout was revised [4] and new front-end electronics, the FE-14 read-out chips [5], were used. The IBL is consist of planar n<sup>+</sup>-in-n silicon pixel sensors, but their design layout was revised [4] and new front-end electronics, the first planar n<sup>+</sup>-in-n sili inner passivations, which ensure a conductive connection from the n<sup>+</sup> implantation through the metal layer to the bump bond.

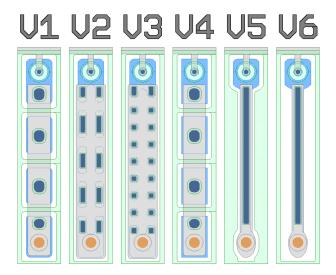

> Based on this IBL pixel design, six modified so-called REINER<sup>3</sup> pixel designs were developed in Dortmund [8]. They are numbered V1 to V6 and their layouts are shown in Figure 2. In V1, the n<sup>+</sup> implantation is divided into four

<sup>\*</sup>corresponding author, andreas.gisen@tu-dortmund.de

<sup>&</sup>lt;sup>1</sup>deceased 24 May 2017

<sup>&</sup>lt;sup>2</sup>now at CiS Forschungsinstitut für Mikrosensorik GmbH, Erfurt

<sup>&</sup>lt;sup>3</sup>**RE**designed, **IN**novative, **E**xciting and **Re**cognizable

Figure 1: Schematic layout of the IBL pixel design. The n<sup>+</sup> implantation is displayed in blue, the metal in grey, the nitride openings, which are also used for moderated p-spray technique, in green and the opening in the outer passivation in orange.

Figure 2: Schematic layout of the modified designs V1 to V6. Again the  $\rm n^+$  implantation is displayed in blue, the metal in grey, the nitride openings, which are also used for moderated p-spray technique, in green and the opening in the outer passivation in orange.

segments. The moderated p-spray profile is continued between the individual segments. V2 and V3 feature further subdivisions to ten and 16 segments, respectively. Due to reduced space between the single segments, no moderated p-spray profile could be implemented. V4 has a similar layout as V1, but with sharp corners of the segments. The usual rounding of the corners was dispensed. V5 and V6 have the n<sup>+</sup> implantation narrowed by the factor three. V6 has the same moderated p-spray profile as the standard design, while it is changed in V5. The width of the high dose area is largely increased.

All designs have an identical bias dot and bias grid structure. It is known [9, 10] that these lead to reduced charge collection and hit efficiency, but improvements in this area are not part of this study.

## 3. Sensors and modules

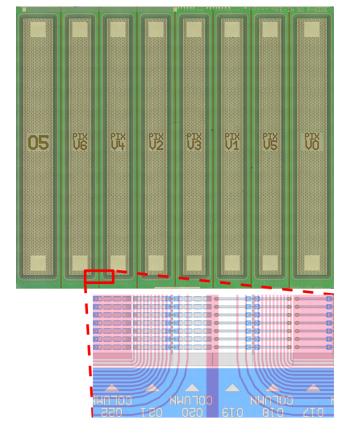

The pixel designs presented in section 2 are placed on planar  $\rm n^+$ -in-n silicon sensors with an n-bulk thickness of 200 µm. They are compatible with IBL single chip sensors. The pixel cells are arranged in 80 columns and 336 rows. Each ten columns the pixel design is changed. While the pixels on the n-side are continuous, the p-side is divided by guard ring design into eight substructures. Each of those features only one pixel design whose name is printed

centrally. High-voltage pads for contacting are located at the top and bottom. Each structure is enclosed by 13 guard rings. This is pictured in an image of the p-side in Figure 3. The six structures containing the modified designs are enclosed by structures with the IBL design. Since this baseline design occurs twice, redundancy and comparability is given within a sensor. The first structure with the IBL design is named 05, the sensor's number on the wafer, while the second appearance is named V0. The other structures have their according structure name imprinted.

A detailed view on the guard ring layout at the bottom of Figure 3 reveals that not all pixel cells are covered by the high-voltage electrode. The next-to-last column is fully shifted beneath the guard rings, the last column even beyond.

Figure 3: Image of the p-side of a REINER pixel sensor. A detailed view on the guard ring layout between two designs is given.

Some sensors were connected to FE-I4 [5] read-out chips with the help of a flip-chip process employing tin-lead-bumps. The investigated module was irradiated with neutrons to  $5 \times 10^{15} \, n_{\rm eq} {\rm cm}^{-2}$  at the Sandia Annular Core Research Reactor<sup>4</sup>, Albuquerque, USA. Afterwards it was mounted to a read-out PCB, which provides connection via wire bonds to the FE as well as connectors for low/high voltage supply and data transmission.

<sup>4</sup>http://www.sandia.gov/research/facilities/annular\_core\_ research\_reactor.html

### 4. IV and power dissipation measurements

Measurements took place in an isolation box which includes a metal heat exchanger. With this setup, on-sensor temperatures down to -50 °C can be reached due to the used regulated chiller. The box is flushed with pre-cooled dried air to keep humidity low and therefore preclude condensation. The FE was not powered during this study to prevent its heat load being transmitted to the sensor. Pt1000 temperature resistors were placed as close as reasonable possible to the module. All measurements were taken at a on-sensor temperature of -30 °C, so scaling of the leakage current could be avoided.

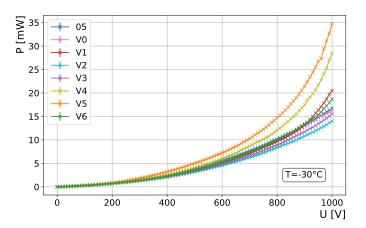

Jumper on the read-out PCB enable biasing of one, all or any combinations of structures during measurements. The current was measured up to a maximum voltage of  $1000\,\mathrm{V}$  in steps of  $10\,\mathrm{V}$  with a delay of  $10\,\mathrm{s}$  between the steps. At each step the current was measured ten times and the mean value was calculated. Differences between individual structures are visible, but none is going into break down. The resulting power dissipation curves for the measurements of all structures individually are shown in Figure 4. An indication for the reliability of the measurements is the good agreement of the curves of  $05\,\mathrm{and}\,\mathrm{V}0$ , the structures with the IBL design. Their mean deviation is  $(0.133\pm0.001)\,\mathrm{mW}$ , while their maximum deviation is  $0.49\,\mathrm{mW}$ .

A stronger rise can be observed for V5 and V4 from 200 V upwards, and for V1 and V6 from 900 V upwards, leading to increased power in comparison to the other designs. The clear differences between the quite similar designs V5 and V6 respective V1 and V4 are remarkable. Especially at high voltages self-heating of the sensor cannot be excluded. However, since neither a significant increase in temperature nor a strong rise in each design is measured, it is very likely that the differences are caused by the different designs.

Figure 4: Power dissipation of individual structures, at -30 °C.

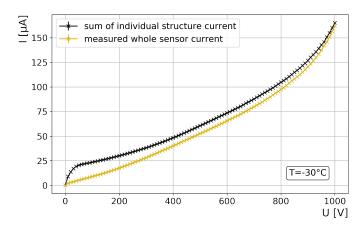

The currents of the individual measurements are summed and plotted along with a measurement of the whole sensor in Figure 5. All structures were biased at the same time for the latter measurement. Other than naively expected, a big difference between both curves is visible. The observed difference decreases for increasing voltage. This effect was also observed at unirradiated REINER sensors and other  $n^+$ -in-n structures [11], indicating that the leakage current contribution from lateral and edge effects is not negligible, especially for small area devices. This should always be considered when statements of test structures are related to full-scale devices.

Figure 5: IV comparison of individual structures being biased and the sensor as a whole.

# 5. Charge collection measurements

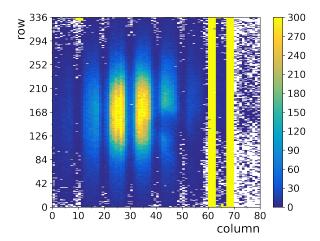

A Strontium-90 beta source and a trigger scintillator were added on top of each other to the cooling setup described in section 4. The module in between was moved in such a way that the structure to be examined was always centered and aligned to the source setup. The emitted electrons pass through the sensor and its read-out chip, a thin aluminium plate and finally the scintillator, which then sends a read-out trigger to the chip. A hit map of a source scan at 600 V is shown in Figure 6. The beam spot is clearly visible, along with the inefficiencies caused by the guard rings between different structures. Noticeable are the two noisy areas between columns 60 and 70 which are related to the guard rings of design V5. With increasing bias voltage, other structures are affected as well. It seems to be a current related issue. The successful operation of pixels being shifted under guard rings has been shown several times [4, 8, 12]. Thus, this behaviour was not expected and seems to be an exclusive feature of this special sensor design with multiple long but narrow guard ring structures placed on the same sensor, also featuring some pixel columns being shifted beyond the guard rings. As an outcome, read-out of all pixel columns in the area of the guard rings was disabled and they are therefore excluded in all further measurements.

Each pixel read-out cell of the FE-I4 chip contains a discriminator with an adjustable threshold. If a signal in

Figure 6: Source scan hit map of the module, at  $600\,\mathrm{V}$ . All pixels were enabled during this scan.

the sensor exceeds this threshold, the time over threshold (ToT) is measured. Therefore the ToT is directly related to the charge induced in the sensor. For all measurements, the FE was tuned to threshold of  $3200\,\mathrm{e}$  and a ToT-response of 6 at a reference charge of  $20\,\mathrm{ke}$ . The on-sensor temperature was -25 °C.

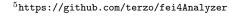

Measurements were done for all structures at several bias voltage points ranging from  $400\,\mathrm{V}$  up to  $1000\,\mathrm{V}$ . At every bias point  $10^6$  trigger hits were recorded. Due to time constraints, not all combinations of voltages and designs could be measured. The raw data was clustered and analysed with  $fei4Analyzer^5$ . A Landau-Gauss convolution was fitted to the distribution of ToT values. The most probable value (MPV) of this function is plotted against the applied bias voltage in Figure 7.

For all structures the MPV increases with the bias voltage. The highest MPV at each voltage is measured at the structure with design V5. As for the leakage current, good agreement of the results of designs 05 and V0 is found. For structures with modified pixel designs except V2, the collected charge is increased. The average increment at 600 V, 800 V and 1000 V with respect to the IBL design is about  $19\,\%$  for V3, about  $32\,\%$  for V1, V4 and V6 and more than  $100\,\%$  for V5.

### 6. Testbeam measurements

Measurements were performed with a pion beam of 120 GeV at CERN-SPS beamline H6. High tracking resolution was provided by six MIMOSA26 sensors of ACONITE, an EUDET-type telescope [13]. An unirradiated FE-I4 planar pixel module was used as the reference plane. All modules were placed in an isolated box, which was cooled with a regulated chiller and flushed with nitrogen. An on-sensor temperature of about -28 °C was determined for the device under test (DUT), which was then tuned to a

Figure 7: MPV vs. bias voltage, measured at a threshold of 3200 e and a ToT-response of 6 at a reference charge of 20 ke. The readout was enabled only for the examined structure. The error bars resulting from the fit are too small to be visible.

threshold of 3200 e and a ToT-response of 6 at a reference charge of 20 ke.

Track reconstruction was performed with EUTelescope. For timing reasons, only tracks given by the telescope which match to hits in the reference plane are considered in the number of tracks  $n_{\rm tracks}$ . Each track which can be matched to a hit in the DUT is considered in the number of hits  $n_{\rm hits}$ . The efficiency  $\varepsilon$  is defined as

$$\varepsilon = \frac{n_{\rm hits}}{n_{\rm tracks}},\tag{1}$$

its relative error  $\sigma_{\varepsilon}$  is defined as

$$\sigma_{\varepsilon} = \sqrt{\frac{\varepsilon \cdot (1 - \varepsilon)}{n_{\text{tracks}}}}.$$

(2)

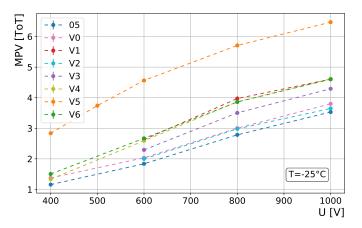

The recorded data were divided into runs with roughly 210 k events each. The efficiency and its error were calculated for each run and pixel design separately, using the *EfficiencyVsGeometry* analysis of *TBmon2.*<sup>7</sup> A weighted mean was then determined for all runs taken under the same conditions. The efficiencies for the individual designs at different bias voltages are plotted in Figure 8. Due to positioning reasons in the setup, no data is available for the second IBL design V0.

For the higher voltage points saturation can be observed. The efficiencies of all designs are compatible with each other. At 1000 V, the average efficiency is  $(97.5 \pm 0.2)$ %, with design 05 showing lowest of  $(97.3 \pm 0.3)$ %. At 800 V, the average efficiency is  $(97.1 \pm 0.2)$ %, again with design 05 showing lowest of  $(96.8 \pm 0.4)$ %. The in-pixel efficiency maps at these voltages reveal that the inefficiencies are entirely in the region of the bias dot and the bias grid, independent from the design.

At  $600\,\mathrm{V}$  the first differences are visible and become more prominent at  $400\,\mathrm{V}$ . The detailed data can be found in Table 1 and Table 2.

<sup>6</sup>http://eutelescope.web.cern.ch/

<sup>7</sup>https://bitbucket.org/TBmon2/tbmon2

Figure 8: Efficiencies for the individual designs, at different bias voltages. Due to positioning reasons, no data is available for the design V0. The error bars represent the standard error of the mean. Some are too small to be visible.

| Table 1: | Efficiencies for the | e individu | al designs, at 600 V |

|----------|----------------------|------------|----------------------|

| 05       | $(94.8 \pm 1.6) \%$  | V4         | $(96.1 \pm 0.3) \%$  |

| V1       | $(96.0 \pm 0.3) \%$  | V5         | $(96.8 \pm 0.2) \%$  |

| V2       | $(95.2 \pm 0.3) \%$  | V6         | $(94.8 \pm 0.7) \%$  |

| V3       | $(96.0 \pm 0.3) \%$  |            |                      |

| Table 2: | Efficiencies for the | e individu | al designs, at 400 V |

|----------|----------------------|------------|----------------------|

| 05       | $(62.4 \pm 1.4) \%$  | V4         | $(72.5 \pm 1.1) \%$  |

| V1       | $(70.2 \pm 1.0)\%$   | V5         | $(92.6 \pm 0.2) \%$  |

| V2       | $(62.6 \pm 0.5) \%$  | V6         | $(74.4 \pm 1.3) \%$  |

| V3       | $(68.3 \pm 0.5) \%$  |            |                      |

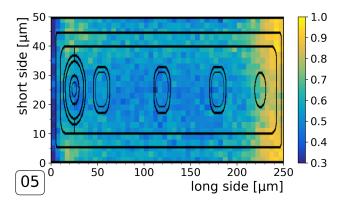

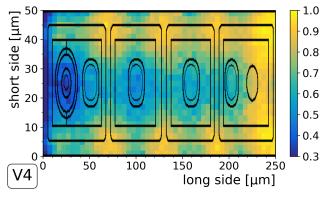

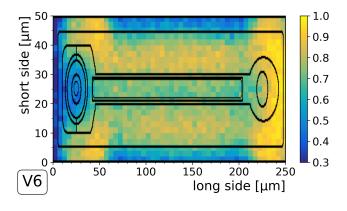

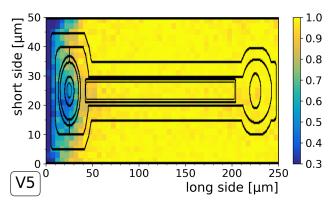

The in-pixel efficiency maps in Figure 9 reveal where the differences come from. The efficiency in the IBL design 05 is uniformly distributed, only some edge effects are visible. For V4 and V6 efficiency hot spots are visible which clearly can be connected to the design. The main area of V5 is highly efficient. Even at low voltages, this design suffers only from inefficiencies caused by the bias dot and the bias grid.

# 7. Summary and Outlook

Several sensors with REINER pixel implantations have been characterized in the laboratory and at testbeams. On a module irradiated with neutrons to  $5\times10^{15}\,n_{\rm eq}{\rm cm}^{-2}$ , the REINER designs perform similar or better than the IBL standard design in terms of charge collection and tracking efficiency, at the cost of a slightly increased leakage current. Comparing design V5 to the IBL design 05, V5 reaches at 800 V the same efficiency of 97.4% as 05 at 1000 V, leading to a sensor power reduction of 12%. A larger power reduction can be achieved at lower bias voltages. V5 reaches at 600 V the same efficiency of 96.8% as 05 at 800 V with the sensor power reduced by 43%.

Designs with larger areas of high-dosed p-spray (V1, V4, V5) perform better than designs without (V2, V3, V6),

Figure 9: In-pixel efficiency maps of design 05, V4, V6 and V5, at  $400\,\mathrm{V}$ , overlayed with their schematic layouts. The bias grid and the bias dot is on the left, the bump bond connection is on the right.

while the effect of the n<sup>+</sup> implantation shape seems minor. The amplification seems to be induced by the additional p-n junction. It is probably a gain effect similar to that already used in avalanche diodes and LGADs [14].

To continue the studies, the same measurements are currently performed on a second REINER pixel module which was irradiated with protons to about  $6\times10^{15}\,n_{\rm eq}{\rm cm}^{-2}$ . To investigate whether these results are easily transferable, all designs were also adopted to n<sup>+</sup>-in-p and a wafer production was submitted.

## 8. Acknowledgements

The possibility to irradiate detector samples at the Sandia Annular Core Research Reactor is kindly acknowledged, especially the help of M. Hoeferkamp and S. Seidel.

Special thanks go to all people attending the ATLAS ITk pixel testbeam campaigns, developing and maintaining the corresponding hardware and software.

The work presented here is carried out within the framework of Forschungsschwerpunkt FSP103 and supported by the Bundesministerium für Bildung und Forschung BMBF under grants 05H15PECAA and 05H15PECA9.

#### References

#### References

- ATLAS Collaboration, The ATLAS Experiment at the CERN Large Hadron Collider, JINST 3 (08) (2008) S08003. doi:10. 1088/1748-0221/3/08/S08003.

- [2] ATLAS Collaboration, ATLAS Insertable B-Layer Technical Design Report, Tech. Rep. CERN-LHCC-2010-013, CERN (2010).

URL http://cds.cern.ch/record/1291633/

- [3] ATLAS Collaboration, ATLAS Insertable B-Layer Technical Design Report Addendum, Tech. Rep. CERN-LHCC-2012-009, CERN, addendum to CERN-LHCC-2010-013, CERN (2012). URL http://cds.cern.ch/record/1451888

- [4] S. Altenheiner, et al., Planar slim-edge pixel sensors for the ATLAS upgrades, JINST 7 (02) (2012) C02051. doi:10.1088/ 1748-0221/7/02/C02051.

- [5] M. Garcia-Sciveres, et al., The FE-I4 pixel readout integrated circuit, Nucl. Instr. Meth. Phys. Res. A 636 (2011) 155 – 159. doi:10.1016/j.nima.2010.04.101.

- [6] G. Casse, et al., Enhanced efficiency of segmented silicon detectors of different thicknesses after proton irradiations up to 1 × 10<sup>16</sup>n<sub>eq</sub>cm<sup>-2</sup>, Nucl. Instr. Meth. Phys. Res. A 624 (2010) 401 404. doi:10.1016/j.nima.2010.02.134.

- [7] G. Kramberger, et al., Investigation of Irradiated Silicon Detectors by Edge-TCT, IEEE Transactions on Nuclear Science 57 (2010) 2294–2302. doi:10.1109/TNS.2010.2051957.

- [8] T. Wittig, Slim Edge Studies, Design and Quality Control of Planar ATLAS IBL Pixel Sensors, Ph.D. thesis, TU Dortmund (2013). doi:10.17877/DE290R-5402.

- [9] J. Weingarten, et al., Planar pixel sensors for the ATLAS upgrade: beam tests results, JINST 7 (10) (2012) P10028. doi:10.1088/1748-0221/7/10/P10028.

- [10] ATLAS IBL Collaboration, Prototype ATLAS IBL modules using the FE-I4A front-end readout chip, JINST 7 (11) (2012) P11010. doi:10.1088/1748-0221/7/11/P11010.

- [11] R. Klingenberg, et al., Power dissipation studies on planar n<sup>+</sup>-in-n pixel sensors, Nucl. Instr. Meth. Phys. Res. A 831 (2016) 105 110. doi:10.1016/j.nima.2016.04.045.

- [12] A. Gisen, et al., Planar n-in-n quad module prototypes for the ATLAS ITk upgrade at HL-LHC, JINST 12 (12) (2017) C12032. doi:10.1088/1748-0221/12/12/32.

- [13] H. Jansen, et al., Performance of the EUDET-type beam telescopes, EPJ Tech. Instrum. 3 (2016) 7 – 27. doi:10.1140/ epjti/s40485-016-0033-2.

- [14] G. Pellegrini, et al., Technology developments and first measurements of Low Gain Avalanche Detectors (LGAD) for high energy physics applications, Nucl. Instr. Meth. Phys. Res. A 765 (2014) 12 16. doi:10.1016/j.nima.2014.06.008.