AIDA-2020-MS64

## **AIDA-2020**

Advanced European Infrastructures for Detectors at Accelerators

## **Milestone Report**

## Final design review of 130nm ASICs

## De la Taille, Christophe (CNRS)

18 October 2017

The AIDA-2020 Advanced European Infrastructures for Detectors at Accelerators project has received funding from the European Union's Horizon 2020 Research and Innovation programme under Grant Agreement no. 654168.

This work is part of AIDA-2020 Work Package 4: Micro-electronics and interconnections.

The electronic version of this AIDA-2020 Publication is available via the AIDA-2020 web site <a href="http://aida2020.web.cern.ch">http://aida2020.web.cern.ch</a> or on the CERN Document Server at the following URL: <a href="http://cds.cern.ch/search?p=AIDA-2020-MS64">http://cds.cern.ch</a> or on the CERN Document Server at the following URL: <a href="http://cds.cern.ch/search?p=AIDA-2020-MS64">http://cds.cern.ch/search?p=AIDA-2020-MS64</a>

Copyright © CERN for the benefit of the AIDA-2020 Consortium

### Grant Agreement No: 654168

# AIDA-2020

Advanced European Infrastructures for Detectors at Accelerators Horizon 2020 Research Infrastructures project AIDA-2020

## **MILESTONE REPORT**

## FINAL DESIGN REVIEW OF 130NM ASICS

## MILESTONE: MS64

| Document identifier:     | AIDA-2020-MS64                               |

|--------------------------|----------------------------------------------|

| Due date of deliverable: | End of Month 30 (October 2017)               |

| Report release date:     | 18/10/2017                                   |

| Work package:            | WP4 : Micro-electronics and interconnections |

| Lead beneficiary:        | CNRS                                         |

| Document status:         | Final                                        |

#### Abstract:

The chip that will be used to read out the SIPM calorimeter of WP13 and the RPC timing detector of WP14 was reviewed by external experts before fabrication. Their recommendations led to the fabrication of the 32-channel chip in July 2017, so that it can meet deliverable D4.2 (Month 36).

#### AIDA-2020 Consortium, 2017

For more information on AIDA-2020, its partners and contributors please see www.cern.ch/AIDA2020

The Advanced European Infrastructures for Detectors at Accelerators (AIDA-2020) project has received funding from the European Union's Horizon 2020 Research and Innovation programme under Grant Agreement no. 654168. AIDA-2020 began in May 2015 and will run for 4 years.

### **Delivery Slip**

|                                                                  | Name                     | Partner | Date       |

|------------------------------------------------------------------|--------------------------|---------|------------|

| Authored by C de La Taille                                       |                          | CNRS    | 10/10/2017 |

| Edited by                                                        | Edited by L. Lapadatescu |         | 10/10/2017 |

| <b>Reviewed by</b> D. Bortoletto [Deputy Scientific Coordinator] |                          | UOXF    | 15/10/2017 |

| Approved by Scientific Coordinator                               |                          |         | 18/10/2017 |

### TABLE OF CONTENTS

| 1. | INTRODUCTION          | 4 |

|----|-----------------------|---|

| 2. | ASIC DESCRIPTION      | 4 |

| 3. | DESIGN REVIEW OUTCOME | 4 |

| 4. | CONCLUSION            | 5 |

| 5. | REFERENCES            | 5 |

#### **Executive summary**

The choice of TSMC130 nm in milestone MS22 and large commonalities with calorimeter upgrades at the LHC have led to the design of a versatile ASIC which matches the requirements of WP13 and WP14. The ASIC has been reviewed by external experts in April 2017. The timetable of review meeting is available at <a href="https://indico.cern.ch/event/634985/">https://indico.cern.ch/event/634985/</a>. The fabrication of the chip was launched in July 2017 allowing the completition of deliverable D4.2.

### 1. INTRODUCTION

Task 4.3 targets high speed, low noise, large dynamic range ASICs for calorimeter readout and high speed timing measurements. These ASICs will be used to read out the detectors of WP13 and WP14, which constitute the deliverables of WP4.3. The choice of TSMC130 nm in milestone M23 made it possible to optimize synergies with calorimeter upgrades, in particular the HGCAL developed for CMS upgrade.

## 2. ASIC DESCRIPTION

The chip developed for the applications in WP13 and WP14 is a very versatile 32-channel ASIC named HGCROC. It provides a charge measurement over a 10 pC range, which is split into two modes. One linear range is read by a 10 bits ADC up to 100 fC with 0.1 fC resolution. The other range is read with a Time over Threshold (TOT) technique, when the preamplifier saturates, covering 100 fC to 10 pC on 12 bits with 2.5 fC resolution. The noise level is kept below 0.32 fC (2000 electrons) for a 60 pF detector capacitance. The ASIC also provides the Time of Arrival (TOA) information with 20 ps resolution for signal larger than 10 fC. Charge and time information are stored in a large memory for 12.5  $\mu$ s to wait for a valid L1 trigger and read out at 1.28 Gb/s e-links.

With this architecture the chip can be used to read out Silicon diodes as in the HGCAL of CMS upgrade, Silicon photomultipliers for WP13 and RPCs foreseen for WP14 or CMS muon chambers upgrade.

The chip has been designed as a collaboration between CERN, CEA/IRFU and Imperial College.

## 3. DESIGN REVIEW OUTCOME

The chip was reviewed at OMEGA by Johan Borg (Imperial), Olivier Gevin (IRFU), Kostas Kloukinas (CERN) and Sandro Marchioro (CERN). Details can be found at https://indico.cern.ch/event/634985/

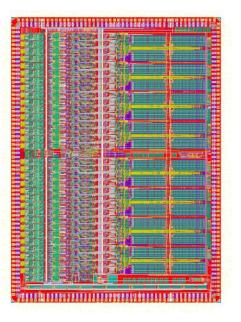

Figure 1: View of the HGCROC chip layout.

| CMS                  |                                           | sign review<br>Apr 2017, 08:30 $\rightarrow$ 15:00 Europe/Zurich | Q-      |

|----------------------|-------------------------------------------|------------------------------------------------------------------|---------|

|                      |                                           |                                                                  | 010-    |

| <b>09:00</b> → 09:10 | Introduction<br>Speaker: Christophe De La | Taille (omega (fr))                                              | ©10m ∠- |

During the review, the detailed schematics and layouts were examined as well as the simulation results. The main analog part had been tested previously thanks to two test vehicles fabricated in 2016 and reported in ref [1]. The digital part and the testability have been improved thanks to the reviewer's comments.

## 4. CONCLUSION

Following the review results, the ASIC has been validated and sent to fabrication in July 2017. It will be received in October 2017 and constitute deliverable D4.2

The review achieves successfully milestone MS64.

## 5. REFERENCES

[1] D. Thienpont et al. « Test vehicles for CMS HGCAL readout ASIC » proceedings of the TWEPP 2017 conference Santa Cruz USA