Home

Search Collections Journals About Contact us My IOPscience

The ATLAS experience and its relevance to the data acquisition of the BM@N experiment at the NICA complex

This content has been downloaded from IOPscience. Please scroll down to see the full text. 2016 J. Phys.: Conf. Ser. 668 012090 (http://iopscience.iop.org/1742-6596/668/1/012090) View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 188.184.3.52 This content was downloaded on 15/02/2016 at 16:23

Please note that terms and conditions apply.

# The ATLAS experience and its relevance to the data acquisition of the BM@N experiment at the NICA complex

## K G Tomiwa<sup>1\*</sup>, I Slepnev<sup>2</sup>, S Bazylev<sup>2</sup> and B Mellado<sup>1\*</sup> on behalf of Wits HEP group

<sup>1</sup> School of Physics, University of the Witwatersrand, Johannesburg 2050, South Africa <sup>2</sup> Joint Institute of Nuclear Research, Dubna, Russia

E-mail: kehinde.gbenga.tomiwa@cern.ch

**Abstract.** The quest to understand the world around us has increased the size of high energy physics experiments and the processing rate of the data output from high energy experiments. The Large Hadron Collider is the largest experimental set-up known, with ATLAS detector as one of the detectors built to record proton-proton collision at about 10 PB/s (Petabit/s) around the LHC interaction point. With the Phase-II upgrade in 2022 this data output will increase by at least 10 times higher than those of today due to luminosity increase, this poses a serious challenge on processing and storage of the data. Also the BM@N fixed target experiment is expected to have event size of about 80,000 bytes/Event, leading to huge amount of data output to be processed in real time. Experimentalists handle these challenges by developing High-throughput electronic, with the capability of processing and reducing big data to scientific data in real time. One of these high-throughput electronics is the Super Readout Driver (sROD) and ARM-based processing unit (PU) developed for ATLAS TileCal detector by the University of the Witwatersrand. The sROD is designed to process data from Tile Calorimeter at 40 MHz. This work takes a look at the architecture of the data acquisition (DAQ) system of the BM@N detectors and the adaptation of the high-throughput systems to last stage of the BM@N DAQ system.

#### 1. Introduction

The field of High Energy Physics (HEP) has contributed to our understanding of the world around us. These contributions are results of various experiments, ranging from fixed target experiment to collision experiments. The size of these experimental setups has grown from table top experiments like the Rutherford experiment to giant collision experiments like the CERN Large Hadron Collider (LHC). These experiments increase our understanding of matter by probing into the constituent of matter. In collision and fixed target experiments particles interactions are observed by detectors. Active materials in detectors interact with particle to produce signals which are converted to electrical signals. These signals are shaped, amplified and processed to observable by data acquisition electronics. Physics experiments rely on these electronics, therefore they are important to our experiments. The usage of electronics poses challenge of big data. Example is the ATLAS detector records proton-proton collisions provided by the Large Hadron Collider (LHC) at CERN produces 10 PB/s data every every 50 ns, with

Content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence. Any further distribution  $(\mathbf{\hat{H}})$ (cc of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI. Published under licence by IOP Publishing Ltd 1

doi:10.1088/1742-6596/668/1/012090

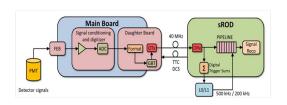

**Figure 1.** ATLAS TileCal future front-end electronics

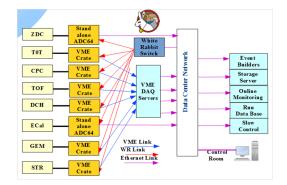

Figure 2. BM@N DAQ System.

the plans to upgrade the detector, the output will be about ten times its previous recording energy which is about 7 TeV (14 TeV collision energy for Phase-II) [1].

## 2. ATLAS Tile Calorimeter Detector and Upgrade

The ATLAS Tile Calorimeter (TileCal) is a hadronic calorimeter for the ATLAS experiment at Large Hadron Collider (LHC)[1], that provides precise measurement of energy and position of electrons, photons, isolated hadrons, taus and jets and measures missing transverse energy. The TileCal detector covers pseudorapidity region of  $-1.7 < \eta < 1.7$  which makes it symmetric with respect to the interaction point [2].

Hadronic showers created at the interaction point of TileCal create light in the scintillating tiles, which is transmitted by wavelength shifting fibers and readout by the photomultiplier tube (PMT). The PMT acts as a transducer that converts light to electric signals, these signals are collected and digitized by the front-end electrons. In the TileCal readout architecture Fig. 1, the signals from PMT are shaped and seperated to high (HG) and low (LG) gain branches in the 3-in-1 card located on the main board. The HG and LG signal are sampled with the LHC bunch-crossing frequency of 40MHz using a 10-bit ADC in the TileCal Data Management Unit (DMU) chip which is located in the digitizer board [3]. The back-end electronics can infer the time and energy of channel's signal from the digitized samples. The L1 trigger is formed by analogue sum of signals (Signature from particles) which represent trigger tower of cell  $\Delta \eta \times \Delta \phi = 0.1 \times 0.1$ .

After Phase-II upgrades in 2022, the data output from the ATLAS Tile Calorimeter will increase significantly. The University of the Witwatersrand has contributed in the following ways towards the Phase-II upgrade in terms of instrumentation.

## 3. Portable Readout Module for TileCal electronics

The plan to upgrade ATLAS TileCal imposes several challenges on the TileCal's readout electronics. The Prometeo system is a test-beach system developed for full certification of the readout electronics by performing multiple tests. Prometeo has been designed to be self-contained and portable, with the ability to readout all channels at the LHC bunch crossing frequency. The Prometeo consist of several parts like the Main board (FPGA based board), Dual QSFP FMC, ADC FMC card and host to test electronics for ATLAS upgrade. The Prometeo's prototypes have been installed at CERN by the University of the Witwatersrand for further development and testing.

## 3.1. Super Readout (sROD)

The sROD (Fig. 1) is an off-detector Electronics at the back-end of the TileCal readout chain, the module uses one Xilinx Virtex 7 and one Xilinx Kintex 7 FPGAs as the processing core. The

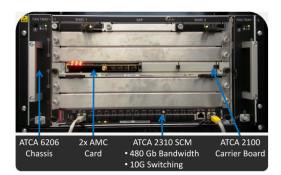

Figure 4. ATCA Chassis [6]

Figure 3. FMC ADC Trigger board [5]

board is a double mid-size Advanced Mazzanine Card (AMC) designed to be compatible with the ATLAS Advance telecommunications computing architecture (ATCA) carrier or the micro Telecommunications computing Architecture (uTCA) system (the new replacement for current VME crates of the DAQ system). The sROD performs several functions like data processing and data reception from ADC boards; Timing, Trigger and control (TTC), Detector Control System (DCS), data reconstruction and transmission to the Read-Out Subsystem (ROS); it also performs trigger data preprocessing and transmission to the Level-1 Calorimeter trigger system (L1Calo)[4].

## 3.2. ARM-based Processing Unit (PU)

The ARM-based Processing unit tries to address the problem of High Volume throughput computing, by arranging ARM system on chips (SoCs) in cluster configuration. This configuration enhances the performance of the PU, it can process at least 40 GB/s of raw data fed through the I/O interface (PCI-Express, XAUI or bonded SFP+Connectors) [5]

## 3.3. ADC Trigger Board

The ADC Trigger board is designed to condition and digitize analog trigger signals coming from the TileCal front-end adder cards. The board uses 12-bit ADC5271 8-channel ADC chips to sample data at 40 Mega Sample Per Second. Serialized data is sent at the rate of 480 Mbps per channel resulting in a total data flow of 7.68 Gbps. The board is powered by a 12V power supply, from which different voltages are created (+D3.3V, +-A3.3V and +-5V) to power differential amplifiers and ADC chips [6].

## 3.4. ATCA Framework

Because of the ATLAS Calorimeter Phase II upgrade, the frontend and backend electronics will be optimized to allow full data rate of 40 MHz to exit the detector. This optimization will include changing the current trigger system to digital signal that will be processed by digital electronics like the sROD. This calls for replacement for module manager (VME crates) by the Advanced Telecommunication Computing Architecture chassis. ATCA chassis is an intelligent shelf with high speed backend connectivity. It provides functionality which enable the integration of CERN's detector control system [7].

#### 4. BM@N DAQ system and Wits Proposed contrition

The Baryonic matter at Nuclotron (BM@N) project in the Nuclotron-Based Ion collider Facility (NICA) at the Joint Institute of Nuclear Research (JINR) is an experiment proposed to the study of AU+AU collision, with beam energy of  $\sqrt{S_{NN}} = 11 GeV/n$  [8]. The proposed particle detectors will be used to record particle produced by the fixed target experiment. The HEP group of the university of Witwatersrand has proposed sROD as a solution to the Trigger and Data acquisition system. The DAQ system will be responsible for transporting and assembling of event data all the way from the front-end buffer to the logging disk. Because of the large size of event and limited available storage size, trigger systems are employed for event data selection. The usual way of doing this is to move event data from the on-detector electronics into the front-end buffer at the bunch crossing rate of collision (20 to 100 kHZ for BM@N). While the event data are in buffer, trigger signals are used to move data to Read-out drivers where event building is done, the ROD also records data to storage disk.

Trigger systems are usually in hierarchies depending on the size of data output, the first level trigger (L1 trigger) is clock-driven, it reads data from on-detector electronics at some time interval. While the higher level trigger (second and third level trigger) are event driven, they are usually implemented in software by executing chains of reconstruction and signature algorithms to analyse the presence of interesting event.

For BM@N experiment, signal from central event would be read at 20 kHz, the approximate event size would be in order of 60Mbps. Minimum bias event size would be 600 Mbps at 100 kHz. The Level-1 trigger acceptance of the BM@N detector will be formed by signals from Zero Degree Calorimeter (ZDC) based on centrality of event. L1 trigger are produced withing 700 to 1000 nano seconds after interaction to initiate readout of all sub component of the BM@N.

#### References

[1] ATLAS Collaboration 2011 Eur. Phys. J. C721849. 63

- [2] ATLAS tile calorimeter interface card, K. Anderson, A. Sen-Gupta, J. E. Pilcher, H. Sanders, F. Tang, 256 R. Teuscher, and H. Wu, in 8th Workshop on Electronics for LHC Experiments.

- [3] K. Anderson, A. Gupta, F. Merritt, M. Oreglia, J. Pilcher, H. Sanders, M. Shochet, F. Tang, R. Teuscher, H. Wu, G. Blanchot, M. Cavalli-Sforza, I. Korolkov, Design of the front-end analog electronics for the ATLAS tile calorimeter, Nuclear Instruments and Methods in Physics Research, Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, Volume 551, Pages 469-473.

- [4] Carrio F, Castillo V, Ferrer A, Fiorini L, Hernandez Y, Higon E, Mellado B, March L, Moreno P, Reed R, Solans C, Valero A and Valla J 2013 ATLAS Collaboration JINST 9 (2014) C02019 2013-020

- [5] Cox M, Reed R, and Mellado B, 2015 The development of a general purpose ARM-based processing unit for the ATLAS TileCal sROD JINST C01007 10

- [6] A high data throughput ADC board for the PROMETEO test-bench of the ATLAS Tile Calorimeter, Matthew Spoor, Oscar Kureba, Charles Sandrock, to be published in the book of proceeding of HEPP 2015 workshop, iThemba Labs, February 2015.

- [7] Robert Reed, An ATCA framework for the upgrade ATLAS readout electronics at LHC, SA Institute of Physics, ISBN: 978-0-620-653916.

- [8] The data acquisition system for a fixed target experiment at NICA complex at JINR and its connection to the ATLAS TileCAl readout electronics. K. Tomiwa, I Slepnev, S Bazylev, to be published in the book of proceeding of HEPP 2015 workshop, iThemba Labs, February 2015.